Beruflich Dokumente

Kultur Dokumente

THAT 2150-Series Datasheet

Hochgeladen von

dCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

THAT 2150-Series Datasheet

Hochgeladen von

dCopyright:

Verfügbare Formate

T H A T Corporation IC Voltage-Controlled

Amplifiers

THAT 2151, 2150A, 2155

FEATURES APPLICATIONS

• Wide Dynamic Range: >116 dB • Faders

81 E

• Wide Gain Range: >130 dB • Panners

• Exponential (dB) Gain Control • Compressors

• Low Distortion: (0.008% @ 0 dB • Expanders

gain, 0.035% @15dB gain)

• Equalizers

T

• Wide Gain-Bandwidth: 6 MHz

• Filters

• Low Cost: $2.20 in ’000s (2155)

• Oscillators

• Single In-Line Package

• Automation Systems

80 E

)

• Dual Gain-Control Ports (pos/neg)

L Description

The THAT 2150 Series integrated-circuit voltage- quire minimal support circuitry. Fabricated in a

/21

controlled amplifiers (VCAs) are high-performance super low-noise process utilizing high hFE, comple-

current-in/current-out devices with two opposing- mentary NPN/PNP pairs, the 2150 Series VCAs

polarity, voltage-sensitive control ports. Based on combine high gain-bandwidth product with low

e O

dbx technology, they offer wide-range exponential noise, low distortion, and low offset to offer discrete

control of gain and attenuation with low signal dis- performance at IC prices. They are available in

tortion. The parts are housed in a space-efficient, three grades, selected for distortion, allowing the

plastic 8-pin single-in-line (SIP) package, and re- user to optimize cost vs. performance.

S

PIN 1 MODEL NO.

21

THAT H J

N E G L

M

TYP.

OB

BIAS CURRENT B F K

2

D I

COMPENSATION

C

A

3

ITEM MILLIMETERS INCHES

Vbe A 20.32 MAX. 0.8 MAX.

8

MULTI- B 1.1 MIN. 0.043 MIN.

C _ .1

+ 0.02 _

+ .004

PLIER 0.5

4

(se

1

D 0.25 0.01

E 2.54 0.1

6 F 1.27 MAX. 0.05 MAX.

G 0.51 MIN. 0.02 MIN.

H 5.08 MAX. 0.2 MAX.

+ .2

_ + .008

_

I 2.8 0.11

J 5.75 MAX. 0.227 MAX.

K 1.5 MAX. 0.058 MAX.

_ _.002

5 L 0.25 +.10 .04 0.01 +.004

+ .5

_ + .02

_

M 3.2 0.126

N 1.1 MIN. 0.043 MIN.

Figure 1. 2150 Series Equivalent Circuit Diagram Figure 2. 2150 Series Physical Outline

dbx is a registered trademark of Carillon Electronics Corporation

THAT Corporation; 734 Forest Street; Marlborough, Massachusetts 01752; USA

Tel: (508) 229-2500; Fax: (508) 229-2590; Web: http://www.thatcorp.com

Page 2 2150 Series IC VCAs

SPECIFICATIONS 1

Absolute-Maximum Ratings (T A = 25˚C)

Positive Supply Voltage (VCC) +18 V Power Dissipation (PD) (TA = 75˚C) 330 mW

Negative Supply Voltage (VEE) -18 V Operating Temperature Range (TOP) -20 to +75˚C

Supply Current (ICC) 10 mA Storage Temperature Range (TST) -40 to +125˚C

TE

Recommended Operating Conditions

2151 2150A 2155

Parameter Symbol Conditions Min Typ Max Min Typ Max Min Typ Max Units

Positive Supply Voltage VCC +5 +12 +15 +5 +12 +15 +5 +12 +15 V

Negative Supply Voltage VEE -5 -12 -15 -5 -12 -15 -5 -12 -15 V

Bias Current ISET VCC-VEE= 24 V — 2.4 4 — 2.4 4 — 2.4 4 mA

Signal Current IIN+IOUT ISET= 2.4 mA — 175 750 — 175 750 — 125 550 µArms

Parameter

Supply Current

Equiv. Input Bias Current

Symbol

ICC

IB

LE

Electrical Characteristics 2

Conditions

No Signal

No Signal

Min

—

—

2151

Typ Max

2.4

5

4

8

Min

—

—

2150A

Typ Max

2.4

5

4

8

Min

—

—

2155

Typ Max

2.4

5

4

8

Units

mA

nA

SO

Input Offset Voltage VOFF(IN) No Signal — +10 — — +10 — — +10 — mV

Output Offset Voltage VOFF(OUT) Rout=20 kΩ

0 dB gain — 1 3 — 1 3 — 1 3 mV

+15 dB gain — 2 3 — 2 3 — 2 3 mV

+40 dB gain — 5 15 — 7 15 — 10 15 mV

Gain Cell Idling Current IIDLE — 20 — — 20 — — 20 — µA

Gain-Control Constant TA=25˚C (TCHIP≅35˚C)

-60 dB < gain < +40 dB

EC+/Gain (dB) Pins 2 & 4 (Fig. 14) 6.0 6.1 6.2 6.0 6.1 6.2 6.0 6.1 6.2 mV/dB

OB

EC-/Gain (dB) Pin 3 -6.0 -6.1 -6.2 -6.0 -6.1 -6.2 -6.0 -6.1 -6.2 mV/dB

Gain-control TempCo ∆ EC / ∆ TCHIP Ref TCHIP= 27˚C — +0.33 — — +0.33 — — +0.33 — %/˚C

Gain-Control Linearity -60 to +40 dB gain — 0.5 2 — 0.5 2 — 0.5 2 %

Off Isolation (Fig. 14) EC+=-360mV, EC-=+360mV 110 115 — 110 115 110 115 — dB

Output Noise en(OUT) 20 Hz-20 kHz

Rout= 20kΩ

0 dB gain — -98 -97 — -98 -96 — -98 -96 dBV

+15 dB gain — -88 -86 — -88 -86 — -88 -86 dBV

1. All specifications subject to change without notice.

2. Unless otherwise noted, TA=25˚C, VCC = +15V, VEE= -15V. Test circuit is as shown in Figure 3. SYMADJ is ad-

justed for minimum THD @ Vin=1 V, 1 kHz, 0 dB gain.

THAT Corporation; 734 Forest Street; Marlborough, Massachusetts 01752; USA

Tel: (508) 229-2500; Fax: (508) 229-2590; Web: http://www.thatcorp.com

Rev. 10/25/96 Page 3

Electrical Characteristics (Cont’d.)

2151 2150A 2155

Parameter Symbol Conditions Min Typ Max Min Typ Max Min Typ Max Units

Total Harmonic Distortion THD IIN+ IOUT = 180 µA, 1 kHz

0 dB gain — 0.004 0.02 — 0.005 0.03 — — — %

±15 dB gain — 0.025 0.045 — 0.05 0.07 — — — %

IIN+ IOUT = 150 µA, 1 kHz

TE

0 dB gain — — — — — — — 0.006 0.03 %

±15 dB gain — — — — — — — 0.05 0.07 %

Symmetry Control Voltage VSYM AV= 0 dB, THD < 0.07% -1.6 0 +1.6 -2 0 +2 -2.5 0 +2.5 mV

Gain at 0 V Control Voltage EC– = 0 mV -0.1 0.0 +0.1 -0.15 0.0 +0.15 -0.2 0.0 +0.2 dB

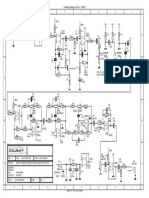

INPUT

10u

LE 20k

1

+15V

7

V+

-IN

V-

5

Ec-

GND

6

3

Ec-

Ec+

2

2150

Series

VCA

Ec+

4

OUT

8

-

+

47p

20k

LF351

+15V

OUTPUT

SO

5.1k Rsym 50k

51

SYM

150k

300k (2155) ADJ

390k (2150A)

470k (2151)

-15V -15V

Figure 3. Typical Application Circuit

OB

Figure 4. Frequency Response Vs. Gain (2150A) Figure 5. Noise (20kHz NBW) Vs. Gain (2150A)

THAT Corporation; 734 Forest Street; Marlborough, Massachusetts 01752; USA

Tel: (508) 229-2500; Fax: (508) 229-2590; Web: http://www.thatcorp.com

Page 4 2150 Series IC VCAs

Theory of Operation

The THAT 2150 Series VCAs are designed for high kT

VT is the thermal voltage, ; IC3 is the collector cur-

performance in audio-frequency applications requiring q

exponential gain control, low distortion, wide dynamic rent of Q3; and IS is the reverse-saturation current of

range and low dc bias modulation. These parts control Q3. It is assumed that D3 matches Q3 (and will be as-

gain by converting an input current signal to a bipolar sumed that they match Q4 and D4, as well).

logged voltage, adding a dc control voltage, and re-con-

In typical applications (see Figure 3, Page 3), pin 4

verting the summed voltage back to a current through

is connected to a voltage source at ground or nearly

TE

a bipolar antilog circuit.

ground potential. Pin 8 is connected to a virtual

Figure 6 presents a considerably simplified internal ground (usually the inverting input of an op amp with

circuit diagram of the IC. The ac input signal current negative feedback around it). With pin 4 near ground,

flows in pin 1, the input pin. The internal op amp and pin 8 at virtual ground, the voltage at the cathodes

works to maintain pin 1 at a virtual ground potential of D3 and D4 will cause an exponentially-related cur-

by driving the emitters of Q1 and (through the Voltage rent to flow in D4 and Q4, and out via pin 8. A similar

Bias Generator) Q3. For positive input currents (Iin de- equation governs this behavior:

fined as flowing into pin 1), the op amp drives the emit-

IC4

ter of Q1 negative, turning off its collector current, V3 = EC+ − 2VT ln .

IS

while simultaneously driving the emitter of Q3 nega-

IN

1

-

Ec+

2

D1

Q1

Q3

Voltage

Bias

Generator

LE

D2

Q2

Q4

3

4

Ec-

OUT

Exponential Gain Control

The similarity between the two preceeding equations

begs further exploration. Accordingly:

IC4

EC+ − EC− = 2VT ln − 2VT ln

I S

IC4

IC3

V3 = EC+ − 2VT ln = EC− − 2VT ln

IS

IC4

IS

IC3

IS

SO

Ec+

Iin = 2VT ln .

(SYM)

IC3

D3 D4 Rearranging terms,

EC+−EC−

IC4 = IC3 e 2VT .

V3

V- 5 If pin 3 and pin 4 are at ground potential, the cur-

rent in Q4/D4 will precisely mirror that in Q3/D3.

When pin 3 is positive with respect to pin 4, the voltage

across the base-emitter junction of Q3 is higher than

Figure 6. Simplified Internal Circuit Diagram

that across the base-emitter junction of Q4, so the

Q4/D4 current remains proportional to, but less than,

OB

tive, turning it on. The input signal current, therefore, the current in Q3/D3. In the same manner, a negative

is forced to flow through Q3 and D3. voltage at pin 3 with respect to pin 4 causes the

Q4/D4 current to be proportional to, but greater than

Logging & Antilogging that in Q3/D3.

Because the voltage across a base-emitter junction The ratio of currents is exponential with the differ-

is logarithmic with collector current, the voltage from ence in the voltages EC+ and EC–, providing convenient

the base of Q3 to the cathode of D3 is proportional to “deci-linear” control. Mathematically, this is:

the log of the positive input current. The voltage at the

EC+−EC−

cathodes of D3 and D4 is therefore proportional to the IC4

AV = =e 2VT , where AV is the current gain.

log of the positive input currents plus the voltage at IC3

pin 3, the negative control port. Mathematically,

For pin 4 at or very near ground, at room tempera-

IC3 ture (25˚C), allowing for a 10˚C internal temperature

V3 = EC− − 2VT ln ,

IS rise, and converting to a base of 10 for the exponential,

where V3 is the voltage at the junction of D3 and D4; this reduces to:

THAT Corporation; 734 Forest Street; Marlborough, Massachusetts 01752; USA

Tel: (508) 229-2500; Fax: (508) 229-2590; Web: http://www.thatcorp.com

Rev. 10/25/96 Page 5

−EC−

0.122

Transistor Matching

AV = 10 .

The bias current flows downwards in the core (from

When pin 3 is at O V, the current ratio is unity. Q1 to Q3, and from Q2 to Q4) so long as there is good

When pin 3 is at +122 mV, the output current (Q4) is matching between all four compound transistors (tran-

10 times (20 dB) less than the input current. At sistors plus diodes). Mismatches will cause a dc output

–122 mV, the output current is 10 times (20 dB) current to flow in pin 8, which will ultimately manifest

greater than the input current. Another way of ex- itself as a dc offset voltage. Static offsets are of little

pressing this relationship is: consequence in most audio applications, but any mis-

TE

match-caused dc output current will be modulated by

−EC−

Gain = , where Gain is the gain in decibels. gain commands, and may become audible as “thumps”

0.0061

if large, fast gain changes are commanded in the pres-

ence of significant mismatches.

Negative Input Currents

Transistor matching also affects distortion. If the

For negative input currents, Q1/D1 operate with

top half of the gain cell is perfectly matched, while the

Q2/D2 to mirror the lower-half-core behavior. Pin 2 is

bottom half is slightly off, then the gain commanded by

normally at or very near ground (see the section below

the voltage at pin 3 will affect the two halves of the core

on Symmetry Adjustment for more detail), so the same

differently. Since positive and negative halves of ac

gain scaling applied to the base of Q3 is applied to the

input signals are handled by separate parts of the core,

base of Q2. The polarity (positive/negative, in dB) of

LE

this gives rise to even-order distortion products.

the gain is the same for the top pair versus the bottom

pair of the four “core” transistors because their sexes

(NPN/PNP) are inverted in the top versus the bottom, Symmetry Adjustment

while the bases are cross-connected between the input The monolithic construction of the devices assures

(left) half and the output (right) half of each pair. relatively good matching between the paired transis-

tors, but even small VBE mismatches can cause unac-

The resulting control over gain is extremely consis-

ceptable asymmetries in the output. For this reason,

tent from unit to unit, since it derives from the physics

the bases of Q1 and Q4 are brought out separately to

of semiconductors. Figure 7 shows actual data from a

pin 2 and pin 4, respectively. This allows a small static

typical 2150 Series VCA, taken at 25˚C.

voltage differential to be applied to the two bases. The

SO

applied voltage must be set to equal the sum of the VBE

mismatches around the core (which varies from sample

to sample). Figure 3 (Page 3) includes a typical circuit

to apply this symmetry voltage. RSYM controls primarily

even-order harmonic distortion, and is usually ad-

justed for minimum THD at the output. Figure 8 plots

THD vs. the voltage between pins 2 and 4 (the two EC+

ports) for various gain settings of a typical part.

Opposite Polarity Control

As may be seen from the mathematics, the bases of

OB

Q1 and Q4 can also be used as an additional control

Figure 7. Gain Versus Control Voltage (Pin 3) at 25˚C

Core Bias Currents

A quiescent bias current in the core transistors is

established by the Voltage Bias Generator shown in

Figure 6. This current acts like crossover bias in the

output stage of a complementary class AB power am-

plifier, smoothing the transition between turning on

the top (PNP) pair and the bottom (NPN) pair of transis-

tors in the core. This lowers distortion greatly at some

cost to noise performance, as the current noise of the

core transistors (which run at approximately 20 µA) is

the dominant noise source in the 2150 Series VCAs. Figure 8. Typical THD Versus Symmetry Voltage

THAT Corporation; 734 Forest Street; Marlborough, Massachusetts 01752; USA

Tel: (508) 229-2500; Fax: (508) 229-2590; Web: http://www.thatcorp.com

Page 6 2150 Series IC VCAs

port, with an opposite sense of control from that at vent such dc terms, ac input coupling is strongly rec-

pin 3. To use this port, both pins must be driven with ommended. A plot of typical output offset voltage ver-

the control voltage, while a small differential voltage is sus gain for the circuit of Figure 3 is shown in

accommodated between the two pins. (Figure 14, Figure 9. (The LF351’s offset was adjusted to 0 V for

Page 9, shows the typical connection.) Either pin 3, or this plot.)

pins 2 and 4, or both ports together may be used for

gain control. Mathematically, this relationship is as fol-

lows:

EC+−EC−

TE

0.122

AV = 10 , where AV is the gain in volts/volt, or

Ec+ − Ec−

Gain = , where Gain is the gain in decibels.

0.0061

Control Port Source Impedance

The control ports (pins 2 through 4) are connected

directly to the bases of the logging and/or antilogging

transistors. As was implied in the earlier discussion on Figure 9. DC Offset Vs. Gain, After Symmetry

Logging and Antilogging (Page 4) the accuracy of the Adjustment

LE

logging and antilogging is dependent on the EC+ and

EC- voltages being exactly as desired to control gain.

The base current in the transistors will follow the col-

lector currents, of course. Since the collector currents

are signal-related, the base currents will also be signal-

related. Should the source impedance of the control

voltage(s) be large, the signal-related base currents will

cause signal-related voltages to appear at the control

ports, which will interfere with precise logging and

antilogging, in turn causing distortion.

Current Programming

The size of the current source at the bottom of the

core (Figure 6, Page 4) is programmed externally via

ISET, which is normally determined by a resistor from

pin 5 to V–. The voltage at pin 5 is typically –2.7 V. ISET

divides into two portions: approximately 400 µA is used

for internal biasing, and the rest is available for the

current source at the bottom of the core. ISET should

SO

The 2150 Series VCAs are designed to be operated therefore be 400 µA larger than the total of the peak

with zero source impedance at pins 2 and 3, and a 50Ω input and output signal currents.

source impedance at pin 4. (Pin 4 is intended for con-

Note that the output impedance of the internal op-

nection to the symmetry control, hence the higher de-

amp is approximately 2 kΩ, and under peak demands,

sign-center source impedance.) One can estimate the

the sum of the input and output currents plus ISET

distortion caused by a specific, non-zero source imped-

must be supplied through this impedance, lowering the

ance by determining the base voltage modulation due

voltage available to drive the core. For more informa-

to signal current based on a core-transistor β of ap-

tion, see the Power Supplies section on Page 8.

proximately 300 (NPN) or 100 (PNP), and converting the

resulting decibel gain modulation to a percentage.

Even 100Ω can spoil the good performance of these Headroom

OB

parts at high signal levels.

Maximum signal currents are also limited by the

logarithmic characteristics of the core transistors. In

DC Input Signals

the 2150 Series, these devices are specially con-

Any dc currents in the feedback loop of the internal structed to conform to an ideal log-linear curve over a

op amp will show up as dc terms in the output signal, wide range of currents, but they reach their limit at ap-

and will be modulated by gain commands. Input bias proximately 1 mA. The symptom of failing log confor-

currents will cause a dc current to flow in the feedback mance is increasing distortion with increasing current

loop provided by the input side of the core. For this levels. The onset of distortion is gradual at low current

reason, input bias currents in the internal op amp levels, and then more rapid as current becomes high.

must be kept very low. The bias current compensation Figures 10 through 12 show distortion versus signal

at the input stage provides excellent cancellation of the level for the three parts in the 2150 Series for -15 dB,

bias current required by the input differential ampli- 0 dB, and +15 dB gain. The acceptable distortion will

fier. Of course, this good performance can be negated determine the maximum signal level for a particular

by a dc current supplied from outside the VCA. To pre- design.

THAT Corporation; 734 Forest Street; Marlborough, Massachusetts 01752; USA

Tel: (508) 229-2500; Fax: (508) 229-2590; Web: http://www.thatcorp.com

Rev. 10/25/96 Page 7

TE

Figure 10. 1kHz THD+Noise Vs. Input, -15 dB Gain Figure 11. 1kHz THD+Noise Vs. Level, 0 dB Gain

LE

Figure 12. 1kHz THD+Noise Vs. Input, +15 dB Gain

SO

Applications

Input the open-loop gain naturally falls off at high frequen-

cies, asking for too much gain will lead to increased

As mentioned above, input and output signals are high-frequency distortion. For best results, this resis-

currents, not voltages. While this often causes some tor should be kept to 10 kΩ or above. Distortion vs. fre-

conceptual difficulty for designers first exposed to this quency for a 1 V signal at 0 dB gain with a 20 kΩ input

convention, the current input/output mode provides resistor is plotted in Figure 13.

great flexibility in application.

The quiescent dc voltage level at the input is ap-

The input pin (pin 1) is a virtual ground with nega- proximately +10 mV. As mentioned above, any dc input

tive feedback provided internally (see Figure 6, Page 4). currents will cause dc signals in the output which will

OB

The input resistor (shown as 20 kΩ in Figure 3, Page 3) be modulated by gain, causing audible thump. There-

should be scaled to convert the available ac input volt-

age to a current within the linear range of the device.

(Peak input currents should be kept under 1 mA for

best distortion performance.) An additional consider-

ation is stability: the internal op amp is intended for

operation with source impedances of less than 30 kΩ

at high frequencies. For most audio applications, this

will present no problem.

The choice of input resistor has an additional, sub-

tle effect on distortion. Since the feedback impedances

around the internal opamp (essentially Q1/D1 and

Q3/D3) are fixed, low values for the input resistor will

require more closed-loop gain from the opamp. Since Figure 13. THD Vs. Frequency, 0 dB Gain

THAT Corporation; 734 Forest Street; Marlborough, Massachusetts 01752; USA

Tel: (508) 229-2500; Fax: (508) 229-2590; Web: http://www.thatcorp.com

Page 8 2150 Series IC VCAs

fore, capacitive coupling is almost mandatory for qual- this source must supply the sum of the input and out-

ity audio applications. Choose a capacitor which will put signal currents, plus the bias to run the rest of the

give acceptable low frequency performance for the ap- IC. The minimum value for this current is 430 µA over

plication. the sum of the required signal currents. 2.4 mA is rec-

ommended for most pro audio applications where

Multiple signals may be summed by multiple resis-

+15 V supplies are common and headroom is import-

tors, just as with an inverting op amp configuration. In

ant.

such a case, a single coupling capacitor may be located

next to pin 1 rather than multiple capacitors at the Higher bias levels are of limited value, partly be-

TE

driven ends of the summing resistors. However, take cause the resistor mentioned in the positive supply dis-

care that the capacitor does not act as an antenna for cussion must supply all the current devoted to the

stray signals. core, and partly because the core transistors become

ineffective at logging and antilogging at currents over

1 mA.

Output

The output pin (pin 8) is intended to be connected to Since pin 5 is intended as a current supply, not a

a virtual ground node, so that current flowing in it may voltage supply, bypassing at pin 5 is not necessary.

be converted to a voltage (see Figures 3, 14, & 15). Pin 6 is used as a ground reference for the VCA. The

Choose the external op amp for good audio perfor- non-inverting input of the internal op amp is con-

mance. The feedback resistor should be chosen based

LE

nected here, as are various portions of the internal bias

on the desired current-to-voltage conversion constant. network. It may not be used as an additional input pin.

Since the input resistor determines the voltage-to-cur-

rent conversion at the input, the familiar ratio of Rf/Ri

Voltage Control

for an inverting op amp will determine the overall volt-

age gain when the VCA IC is set for 0 dB current gain. The primary voltage-control pin is pin 3. This point

Since the VCA performs best at settings near unity controls gain inversely with applied voltage: positive

gain, use the input and feedback resistors to provide voltage causes loss, negative voltage causes gain. As

design-center gain or loss, if necessary. described on Page 6, the current gain of the VCA is

unity when pin 3 is at 0 V with respect to pins 2 and 4,

A small feedback capacitor around the output op and varies with voltage at approximately -6.1 mV/dB,

SO

amp is necessary to cancel the output capacitance of at room temperature.

the VCA. Without it, this capacitance will destabilize

most op amps. The capacitance at pin 8 is typically As implied by the equation for AV (at the foot of

30 pf. Page 4), the gain is sensitive to temperature, in propor-

tion to the amount of gain or loss commanded. The

constant of proportionality is 0.33% of the decibel gain

Power Supplies

commanded, per degree Celsius, referenced to 27°C

The positive supply is connected directly to pin 7. (300°K). This means that at 0 dB gain, there is no

No special bypassing is necessary, but it is good prac- change in gain with temperature. However, at -122 mV,

tice to include a small (~1 µf) electrolytic close to the the gain will be +20 dB at room temperature, but will

VCA IC on the PCB. Performance is not particularly de- be 20.66 dB at a temperature 10˚C lower. The formula

pendent on supply voltage. The lowest permissible sup- is:

OB

ply voltage is determined by the sum of the input and

EC+−EC−

output currents plus ISET, which must be supplied Gain = ,

(0.0061) (1+0.0033) ∆T

through the resistor at the top of the core transistors

(see Figure 1) while still allowing enough voltage swing where EC is in volts, and ∆T is the difference between

to bias the internal op amp and the core transistors the actual temperature and room temperature (25˚C).

themselves. This resistor is approximately 2 kΩ. Re-

For most audio applications, this change with tem-

ducing signal currents may help accommodate low

perature is of little consequence. However, if necessary,

supply voltages.

it may be compensated by a resistor which varies its

The highest permissible supply voltage is fixed by value by .33%/˚C. Such parts are available from RCD

the process characteristics and internal power con- Components, Inc, 3301 Bedford St., Manchester, NH,

sumption. +15 V is the nominal limit. USA [(603) 669-0054], and KOA/Speer Electronics, PO

Box 547, Bradford, PA, 16701 USA [(814)362-5536].

The negative supply terminal is intended to be con-

nected to a resistive current source, which determines When pin 3 is used for voltage control, pin 2 is con-

the current available for the core. As mentioned before, nected to ground and pin 4 is used to apply a small

THAT Corporation; 734 Forest Street; Marlborough, Massachusetts 01752; USA

Tel: (508) 229-2500; Fax: (508) 229-2590; Web: http://www.thatcorp.com

Rev. 10/25/96 Page 9

symmetry voltage (<±2.5 mV) to correct for VBE mis- erwise required to command high attenuation

matches within the VCA IC. For this purpose, the 2150 (+610 mV for -100 dB gain at pin 3 alone, vs. ±305 mV

series devices were designed for optimum performance when using both pin 3 and pins 2 and 4).

with an impedance of approximately 50Ω at pin 4. A

trim pot is used to adjust the voltage between pin 4 Control Port Drive Impedance

and pin 2 as shown in Figure 3, Page 3. For supply

It has already been noted that the control port

voltages other than shown, scale RSYM to provide the

should be driven by a low source impedance for mini-

required adjustment range.

mum distortion. This often suggests driving the control

TE

It is also possible to use pin 2 and pin 4 together as port directly with an opamp (see below under Noise

an opposite-sense voltage control port. A typical circuit Considerations). However, the closed-loop output im-

using this approach is shown in Figure 14. Pin 3 may pedance of an opamp typically rises at high frequencies

be grounded, and pin 2 driven against the symmetry- due to falling loop gain. The output impedance is

adjustment voltage. The change in voltage at pin 4 therefore inductive at high frequencies. Excessive in-

does have a small effect on the symmetry voltage, but ductance in the control port source impedance can

this is of little practical consequence in most applica- cause the VCA to oscillate internally. In such cases, a

tions. Using the opposite sense of control can some- 51 Ω resistor in series with a 1.5 nf capacitor from the

times save an inverter in the control path. control port to ground will usually suffice to prevent

the instability.

It is also possible (and advantageous) to combine

LE

both control ports with differential drive (see Fig-

ure 15). While the driving circuitry is more complex,

this configuration offers better performance at high

attentuation levels (<-90 dB) where the single-control-

port circuits begin to saturate Q1 (for EC– drive) or Q3

(for EC+ drive). When either of these transistors satu-

rates, the internal opamp will accomodate the change

in current demand by responding with a small change

in its input offset voltage. This leads to an accumula-

tion of charge on the input capacitor, which in turn

Noise Considerations

It is second nature among good audio designers to

consider the effects of noisy devices on the signal path.

As is well known, this includes not only active devices

such as op amps and transistors, but extends to the

choice of impedance levels as well. High value resistors

have inherent thermal noise associated with them, and

the noise performance of an otherwise quiet circuit can

be easily spoiled by the wrong choice of impedance lev-

SO

els.

can cause thump when the high attenuation is sud-

denly removed (e.g., when a muted channel is opened). Less well known, however, is the effect of noisy cir-

Differential control drive avoids the large dc levels oth- cuitry and high impedance levels in the control path of

+15V

47p

2150

2150

Series

Series 7

20k

VCA

VCA V+ 3

Ec- OUT

INPUT 1

-IN Ec+ -

8

OB

Ec+

GND 4 LF351 OUTPUT

2

10u 20k V-

6 +

5

+15V

51

Rsym

5.1k 50k

SYM

240k ADJ

300k (2155)

390k (2150A)

Ec+ 470k (2151)

-15V

-15V

Figure 14. Positive Control Port Using Pins 2 and 4

THAT Corporation; 734 Forest Street; Marlborough, Massachusetts 01752; USA

Tel: (508) 229-2500; Fax: (508) 229-2590; Web: http://www.thatcorp.com

Page 10 2150 Series IC VCAs

voltage-control circuitry. The 2150 Series VCAs act like To avoid excessive noise, one must take care to use

double-balanced multipliers: when no signal is present quiet electronics throughout the control-voltage cir-

at the signal input, noise at the control input is re- cuitry. One useful technique is to process control volt-

jected. So, when measuring noise (in the absence of ages at a multiple of the eventual control constant

signal — as most everyone does), even very noisy con- (e.g., 61 mV/dB — ten times higher than the VCA re-

trol circuitry often goes unnoticed. However, noise at quires), and then attenuate the control signal just be-

the control port of these parts will cause noise modula- fore the final drive amplifier. With careful attention to

tion of the signal. This can become significant if care impedance levels, relatively noisy op amps may be

is not taken to drive the control ports with quiet sig- used for all but the final stage.

E

nals.

The 2150 Series VCAs have a small amount of in-

Closing Thoughts

herent noise modulation because of its class AB bias- The design and application of Voltage-Controlled

ing scheme, where the shot noise in the core Amplifiers has traditionally been partly black art, in-

transistors reaches a minimum with no signal, and in- volving as much magic as science. We hope that the

ET

creases with the square root of the instantaneous sig- foregoing discussion will help to de-mystify the subject.

nal current. However, in an optimum circuit, the noise

THAT Corporation welcomes comments, questions

floor rises only to -94 dBV with a 50 µA signal at unity

and suggestions regarding these devices, their design

gain — 4 dB of noise modulation. By contrast, if a

and application. Please feel free to contact us with your

unity-gain connected, inverting 5534 opamp is used to

thoughts.

directly drive the control port, the noise floor will rise

to 92 dBV — 6 dB of noise modulation.

S OL

+15V

2150 47p

2150

Series

Series

7

VCA

VCA 20k

V+ 3

Ec-

OB

OUT

INPUT 1

-IN Ec+ -

Ec+

8

GND 4 LF351 OUTPUT

V- 2

10u 20k 6 +

5

+15V

+

51

Rsym

- 5.1k 50k

SYM

150k

240k

300k (2155) ADJ

390k (2150A)

1k 1k

Ec+ 470k (2151)

-15V

-15V

Figure 15. Using Both Control Ports (Differential Drive)

THAT Corporation; 734 Forest Street; Marlborough, Massachusetts 01752; USA

Tel: (508) 229-2500; Fax: (508) 229-2590; Web: http://www.thatcorp.com

Das könnte Ihnen auch gefallen

- Audio Cyclopedia 2ndDokument1.762 SeitenAudio Cyclopedia 2ndd100% (2)

- Lab 1 ReportDokument10 SeitenLab 1 Reportsherub wangdiNoch keine Bewertungen

- Experiment 5Dokument16 SeitenExperiment 5Ravi Kanth M N33% (3)

- Data Sheet 2n2222Dokument3 SeitenData Sheet 2n2222Jesus SanchezNoch keine Bewertungen

- Manual On Design of LNA Using ADSDokument33 SeitenManual On Design of LNA Using ADSThabasum Aara SNoch keine Bewertungen

- Corporation: Pre-Trimmed IC Voltage Controlled AmplifiersDokument8 SeitenCorporation: Pre-Trimmed IC Voltage Controlled AmplifiersJuan CarlosNoch keine Bewertungen

- THAT 2181-Series DatasheetDokument12 SeitenTHAT 2181-Series Datasheetjiren the winerNoch keine Bewertungen

- Semiconductor FTC2383: Technical DataDokument3 SeitenSemiconductor FTC2383: Technical DataTecnico GenioNoch keine Bewertungen

- MPSA05Dokument1 SeiteMPSA05Ghalielectrosoft GesNoch keine Bewertungen

- Not Recommended For New Design USE: Hall Effect Latch For High TemperatureDokument9 SeitenNot Recommended For New Design USE: Hall Effect Latch For High TemperatureAnonymous cD6Hx2gNoch keine Bewertungen

- Feature: NPN Silicon General Purpose Transistor Elektronische BauelementeDokument1 SeiteFeature: NPN Silicon General Purpose Transistor Elektronische BauelementeRichard Hernandez RuizNoch keine Bewertungen

- OP227 - Analog DevicesDokument17 SeitenOP227 - Analog DevicesVinicius Mastelaro RodriguesNoch keine Bewertungen

- KTB 1260Dokument3 SeitenKTB 1260Suman NayalNoch keine Bewertungen

- KTC3203Dokument2 SeitenKTC3203Lourencosud SudNoch keine Bewertungen

- Wide Input Voltage 3.0 A Step Down Regulator: Features and Benefits DescriptionDokument10 SeitenWide Input Voltage 3.0 A Step Down Regulator: Features and Benefits DescriptionFarouq BendjimiNoch keine Bewertungen

- KTC4373Dokument3 SeitenKTC4373hyungjinNoch keine Bewertungen

- Ina118 PDFDokument31 SeitenIna118 PDFAbu alwardNoch keine Bewertungen

- 2A, 380 KHZ Step-Down Converter: The Future of Analog Ic TechnologyDokument10 Seiten2A, 380 KHZ Step-Down Converter: The Future of Analog Ic TechnologyAnonymous aP1FSUPoNoch keine Bewertungen

- Features: 115ma, 60V, R 4 N-CH Small Signal MOSFET With ESD Protection Elektronische BauelementeDokument4 SeitenFeatures: 115ma, 60V, R 4 N-CH Small Signal MOSFET With ESD Protection Elektronische BauelementeseggurNoch keine Bewertungen

- KTC3200 KecDokument2 SeitenKTC3200 KecyamahaNoch keine Bewertungen

- Features: Elektronische Bauelemente 2A, 50V P Plastic Encapsulated TransistorDokument2 SeitenFeatures: Elektronische Bauelemente 2A, 50V P Plastic Encapsulated TransistorLuis FigueroaNoch keine Bewertungen

- Autonics KN1000 DatasheetDokument12 SeitenAutonics KN1000 DatasheetManh VuNoch keine Bewertungen

- Features: Elektronische Bauelemente 115ma, 60V N-Channel Enhancement Mode Power MOSFETDokument3 SeitenFeatures: Elektronische Bauelemente 115ma, 60V N-Channel Enhancement Mode Power MOSFETvipinNoch keine Bewertungen

- 〈Small-Signal Transistor〉: Isahaya Electronics CorporationDokument2 Seiten〈Small-Signal Transistor〉: Isahaya Electronics CorporationFernando José Luzardo FernándezNoch keine Bewertungen

- Wide Input Voltage 3.0 A Step-Down Regulator: Features and Benefits DescriptionDokument10 SeitenWide Input Voltage 3.0 A Step-Down Regulator: Features and Benefits DescriptionCiprian UngureanuNoch keine Bewertungen

- KTD 1302Dokument2 SeitenKTD 1302otniel garciaNoch keine Bewertungen

- Semiconductor KTC3200: Technical DataDokument2 SeitenSemiconductor KTC3200: Technical DataBuitinės Technikos RemontasNoch keine Bewertungen

- TDP UkDokument10 SeitenTDP UkSüleymanŞentürkNoch keine Bewertungen

- CK100Dokument3 SeitenCK100Sankar SelvarajNoch keine Bewertungen

- V571D/M Linear Integrated Circuit: CompanderDokument30 SeitenV571D/M Linear Integrated Circuit: CompanderStef LNANoch keine Bewertungen

- Datasheet - HK cn1016 1227640Dokument2 SeitenDatasheet - HK cn1016 1227640Reinaldo KoslowskiNoch keine Bewertungen

- CT200 LittlefuseDokument2 SeitenCT200 LittlefuseHugo Dennis Mattos EspinozaNoch keine Bewertungen

- 1 User Guide: 2408 I Indicator and Alarm UnitDokument12 Seiten1 User Guide: 2408 I Indicator and Alarm UnitFernando BarraganNoch keine Bewertungen

- ATS177 Hall Effect DatasheetDokument10 SeitenATS177 Hall Effect DatasheetAnonymous oyUAtpKNoch keine Bewertungen

- Op 285Dokument16 SeitenOp 285api-3825669Noch keine Bewertungen

- STT8205S: DescriptionDokument4 SeitenSTT8205S: DescriptionspotNoch keine Bewertungen

- CSD 1489Dokument3 SeitenCSD 1489vijay singh sonkarNoch keine Bewertungen

- Low Power Dual Voltage Comparators: DescriptionDokument11 SeitenLow Power Dual Voltage Comparators: DescriptionAlexsander MeloNoch keine Bewertungen

- 2SB1132Dokument2 Seiten2SB1132NelsonNoch keine Bewertungen

- NE46100 / NE46134: NPN Medium Power Microwave TransistorDokument10 SeitenNE46100 / NE46134: NPN Medium Power Microwave TransistorYunus KoçNoch keine Bewertungen

- 2n6520 TV SamsungDokument2 Seiten2n6520 TV Samsungjavier venturaNoch keine Bewertungen

- MPS651YDokument3 SeitenMPS651YCarlos RobertoNoch keine Bewertungen

- BU208 BU208A High Voltage NPN Silicon Power Transistor DescriptionDokument2 SeitenBU208 BU208A High Voltage NPN Silicon Power Transistor DescriptionLeonardoMartinNoch keine Bewertungen

- Semiconductor KTA1271: Technical DataDokument2 SeitenSemiconductor KTA1271: Technical DataErnesto Raphael Magallanes BorjasNoch keine Bewertungen

- Semiconductor KTA1271: Technical DataDokument2 SeitenSemiconductor KTA1271: Technical DataLoengrinMontillaNoch keine Bewertungen

- Low Cost, Zero-Drift In-Amp With Filter and Fixed Gain AD8293G80/AD8293G160Dokument16 SeitenLow Cost, Zero-Drift In-Amp With Filter and Fixed Gain AD8293G80/AD8293G160Muhammad Qasim RaufNoch keine Bewertungen

- TD 310Dokument9 SeitenTD 310Paresh PanchalNoch keine Bewertungen

- Semiconductor: Technical DataDokument6 SeitenSemiconductor: Technical Datagotcha75Noch keine Bewertungen

- Not For New Design, USE MMBT3904: NPN Small Signal Transistor FeaturesDokument2 SeitenNot For New Design, USE MMBT3904: NPN Small Signal Transistor FeaturesRanfis Rojas BorgesNoch keine Bewertungen

- T12M5T600BDokument6 SeitenT12M5T600BTartaro AltamiranoNoch keine Bewertungen

- KTA1270Dokument3 SeitenKTA1270IsaiasAvilesNoch keine Bewertungen

- Leem MT-8R Operating ManualDokument8 SeitenLeem MT-8R Operating ManualiljicsNoch keine Bewertungen

- 2N3478Dokument2 Seiten2N3478sas999333Noch keine Bewertungen

- Synchronous Rectification National Power Designer 112Dokument8 SeitenSynchronous Rectification National Power Designer 112sivasankartikkuNoch keine Bewertungen

- KN2222 A PDFDokument4 SeitenKN2222 A PDFRONIBAEL CORDOVANoch keine Bewertungen

- AD8613 AD8617 AD8619: Low Cost Micropower, Low Noise CMOS Rail-to-Rail, Input/Output Operational AmplifiersDokument16 SeitenAD8613 AD8617 AD8619: Low Cost Micropower, Low Noise CMOS Rail-to-Rail, Input/Output Operational AmplifiersGideon samsonNoch keine Bewertungen

- MC79M00 Series 500 Ma Negative Voltage RegulatorsDokument8 SeitenMC79M00 Series 500 Ma Negative Voltage RegulatorsEugene JayNoch keine Bewertungen

- Ne856 2sc5011 2sc5006 2sc4226 2sc3355 2sc3603 2sc3356 2sc3357 2sc3603 2sc4093Dokument25 SeitenNe856 2sc5011 2sc5006 2sc4226 2sc3355 2sc3603 2sc3356 2sc3357 2sc3603 2sc4093JourneyNoch keine Bewertungen

- 2SC2458 GRDokument3 Seiten2SC2458 GRisaiasvaNoch keine Bewertungen

- As Shown: Connect To 230Dokument1 SeiteAs Shown: Connect To 230Dash FarnacioNoch keine Bewertungen

- 1 μA Micropower CMOS Operational Amplifiers AD8502/AD8504: Features Pin ConfigurationsDokument16 Seiten1 μA Micropower CMOS Operational Amplifiers AD8502/AD8504: Features Pin ConfigurationsBilles GatesNoch keine Bewertungen

- CA3100TDokument7 SeitenCA3100THisham MehremNoch keine Bewertungen

- Dig Pot App NoteDokument7 SeitenDig Pot App NotedNoch keine Bewertungen

- Eden WT800 Service NotesDokument22 SeitenEden WT800 Service NotesdNoch keine Bewertungen

- PDF Created With Pdffactory Pro Trial VersionDokument6 SeitenPDF Created With Pdffactory Pro Trial VersiondNoch keine Bewertungen

- Current Lover: Based On The EHX® Electric Mistress™Dokument14 SeitenCurrent Lover: Based On The EHX® Electric Mistress™dNoch keine Bewertungen

- TheirDogsWereAstronauts ToreroDokument5 SeitenTheirDogsWereAstronauts TorerodNoch keine Bewertungen

- Pork Barrel 2019: New For 2019Dokument11 SeitenPork Barrel 2019: New For 2019dNoch keine Bewertungen

- Ibanez BCL TC10 Schematic PDFDokument1 SeiteIbanez BCL TC10 Schematic PDFdNoch keine Bewertungen

- Trace Elliot: Service Manual No. Sm00011 Issue 1Dokument15 SeitenTrace Elliot: Service Manual No. Sm00011 Issue 1dNoch keine Bewertungen

- Ibanez rc99 PDFDokument1 SeiteIbanez rc99 PDFdNoch keine Bewertungen

- Capacitance Meter: Theory & DesignDokument3 SeitenCapacitance Meter: Theory & DesigndNoch keine Bewertungen

- Ibanez tk999 UsDokument1 SeiteIbanez tk999 UsdNoch keine Bewertungen

- PDF Created With Pdffactory Pro Trial Version: Coron Jet - Utsch - SheetDokument1 SeitePDF Created With Pdffactory Pro Trial Version: Coron Jet - Utsch - SheetdNoch keine Bewertungen

- Ibanez tk999 JapaneseDokument1 SeiteIbanez tk999 JapanesedNoch keine Bewertungen

- Diminished Arpeggio: Root 1st Inv 2nd InvDokument1 SeiteDiminished Arpeggio: Root 1st Inv 2nd InvdNoch keine Bewertungen

- Naka Zora PentatonicDokument1 SeiteNaka Zora PentatonicdNoch keine Bewertungen

- Augmented Arpeggio: Any Inv Any InvDokument1 SeiteAugmented Arpeggio: Any Inv Any InvdNoch keine Bewertungen

- Pink Panther Bass Tab PDFDokument1 SeitePink Panther Bass Tab PDFdNoch keine Bewertungen

- Major 7#5 Arpeggio: 3rd Inv. 2nd Inv. 1st Inv. RootDokument1 SeiteMajor 7#5 Arpeggio: 3rd Inv. 2nd Inv. 1st Inv. RootdNoch keine Bewertungen

- Diminished 7 ArpeggioDokument1 SeiteDiminished 7 ArpeggiodNoch keine Bewertungen

- Dominant 7b5 Arpeggio: 1st & 3rd Inv. Root & 2nd InvDokument1 SeiteDominant 7b5 Arpeggio: 1st & 3rd Inv. Root & 2nd InvdNoch keine Bewertungen

- Minor/Major 7 Arpeggio: 3rd Inv. 2nd Inv. 1st Inv. RootDokument1 SeiteMinor/Major 7 Arpeggio: 3rd Inv. 2nd Inv. 1st Inv. RootdNoch keine Bewertungen

- Mixolydian PentatonicDokument1 SeiteMixolydian PentatonicdNoch keine Bewertungen

- Major 7 b5 Arpeggio: 3rd Inv. 2nd Inv. 1st Inv. RootDokument1 SeiteMajor 7 b5 Arpeggio: 3rd Inv. 2nd Inv. 1st Inv. RootdNoch keine Bewertungen

- Dominant 7sus4 Arpeggio: 3rd Inv. 2nd Inv. 1st Inv. RootDokument1 SeiteDominant 7sus4 Arpeggio: 3rd Inv. 2nd Inv. 1st Inv. RootdNoch keine Bewertungen

- Dominant PentatonicDokument1 SeiteDominant PentatonicdNoch keine Bewertungen

- Kumoi PentatonicDokument1 SeiteKumoi PentatonicdNoch keine Bewertungen

- Minor 7b5 Arpeggio: 3rd Inv. 2nd Inv. 1st Inv. RootDokument1 SeiteMinor 7b5 Arpeggio: 3rd Inv. 2nd Inv. 1st Inv. RootdNoch keine Bewertungen

- Dominant 7 #5 Arpeggio: 3rd Inv. 2nd Inv. 1st Inv. RootDokument1 SeiteDominant 7 #5 Arpeggio: 3rd Inv. 2nd Inv. 1st Inv. RootdNoch keine Bewertungen

- Minor 7 Arpeggio PDFDokument1 SeiteMinor 7 Arpeggio PDFdNoch keine Bewertungen

- EC8361 - Analog and Digital Circuits Laboratory Manual - by LearnEngineering - inDokument82 SeitenEC8361 - Analog and Digital Circuits Laboratory Manual - by LearnEngineering - inPavithra PrakashNoch keine Bewertungen

- Mohammad Reza Safari Tirtashi PDFDokument120 SeitenMohammad Reza Safari Tirtashi PDFdearnaka24Noch keine Bewertungen

- Nujira MIPI PresentationDokument20 SeitenNujira MIPI PresentationjeremyhendyNoch keine Bewertungen

- User Manual For GSM900 Band Selective Pico Repeater PDFDokument31 SeitenUser Manual For GSM900 Band Selective Pico Repeater PDFAnh HoàngNoch keine Bewertungen

- Line 6 Spider2 Hd75 SMDokument90 SeitenLine 6 Spider2 Hd75 SMAmin SantanaNoch keine Bewertungen

- G22LWK and 22LWK Service ManualDokument44 SeitenG22LWK and 22LWK Service ManualBogus MalogusNoch keine Bewertungen

- Feb. 3, 1970 L. D. Seader Et Al 3,493,882: A/G 2 Leonard D. Seader by James E. SterrettDokument4 SeitenFeb. 3, 1970 L. D. Seader Et Al 3,493,882: A/G 2 Leonard D. Seader by James E. Sterrettefremofe7394Noch keine Bewertungen

- AEC BitDokument5 SeitenAEC BitThil PaNoch keine Bewertungen

- BKtel Combined DatasheetsDokument27 SeitenBKtel Combined DatasheetsMadison Technologies100% (1)

- Audio Transistor AmplifierDokument12 SeitenAudio Transistor Amplifierkaran007_mNoch keine Bewertungen

- Ee 352 Ec Ii LabDokument61 SeitenEe 352 Ec Ii LabSatya SandeepNoch keine Bewertungen

- Nokia Ultrasite Mha SystemDokument71 SeitenNokia Ultrasite Mha SystemАнатолий Петьков80% (5)

- A 12-m 2.5-Gb/s Lighting Compatible Integrated Receiver For OOK Visible Light Communication LinksDokument8 SeitenA 12-m 2.5-Gb/s Lighting Compatible Integrated Receiver For OOK Visible Light Communication LinksmilianNoch keine Bewertungen

- Tda 7438Dokument18 SeitenTda 7438sontuyet82Noch keine Bewertungen

- ADA-1023 ManualDokument4 SeitenADA-1023 ManualmystrieNoch keine Bewertungen

- Sedra Smith Microelectronic Circuits 8Th Edition by Adel S Sedra Author Full Download ChapterDokument51 SeitenSedra Smith Microelectronic Circuits 8Th Edition by Adel S Sedra Author Full Download Chapterandrea.johnson263100% (16)

- EC8351 Electronic Circuits I IQDokument20 SeitenEC8351 Electronic Circuits I IQRekha SharmilyNoch keine Bewertungen

- Design of Ribbon MicrophoneDokument9 SeitenDesign of Ribbon MicrophonemerrickNoch keine Bewertungen

- DBX 786 Mic PreDokument8 SeitenDBX 786 Mic PreSimon WalkerNoch keine Bewertungen

- Negative Feedback AmplifiersDokument19 SeitenNegative Feedback AmplifiersJames Lee IlaganNoch keine Bewertungen

- HP Journal - July, 1962Dokument8 SeitenHP Journal - July, 1962raduroNoch keine Bewertungen

- A 77-GHz CMOS Automotive Radar TransceiverDokument9 SeitenA 77-GHz CMOS Automotive Radar TransceiverAbderrahimNoch keine Bewertungen

- UT SlidesDokument58 SeitenUT SlidesY ShameyaNoch keine Bewertungen

- La 76070Dokument27 SeitenLa 76070Francisco AntonioNoch keine Bewertungen

- Field Strength Vs Radiated PowerDokument2 SeitenField Strength Vs Radiated PowerwormingNoch keine Bewertungen

- A Panalog Pa SystemsDokument11 SeitenA Panalog Pa SystemsJoeannamaryDeguzmanNoch keine Bewertungen

- Rqa 0009 TXDDokument22 SeitenRqa 0009 TXDserga333Noch keine Bewertungen