Beruflich Dokumente

Kultur Dokumente

Computer Organization & Assembly Language: Instructions To Candidates

Hochgeladen von

TaimoorOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Computer Organization & Assembly Language: Instructions To Candidates

Hochgeladen von

TaimoorCopyright:

Verfügbare Formate

15781 15781 15781 15781 15781 15781 15781 15781 15781

15781 Roll No.

15781 15781 15781 15781 15781 Total15781

No. of Pages

15781 : 02 15781

Total No. of Questions : 09

MCA (2015 Batch) (Sem.–1)

15781 15781 15781 15781 15781 15781 15781 15781 15781

COMPUTER ORGANIZATION & ASSEMBLY LANGUAGE

Subject Code : MCA-103

Paper ID : [72709]

15781 15781 15781 15781 15781 15781 15781 15781 15781

Time : 3 Hrs. Max. Marks : 60

INSTRUCTIONS TO CANDIDATES :

m

15781 15781

1. 15781

SECTIONS-A, B, C &15781

D contains 15781 15781each carrying

T WO questions 15781 T EN marks

15781 each 15781

and students has to attempt any ONE question from each SECTION.

2.

o

SECTION-E is COMPULSORY consisting of T EN questions carrying T WENT Y

.r c

marks in all.

15781 15781 15781 15781 15781 15781 15781 15781 15781

15781 15781

1.

15781

pe

15781

SECTION-A

15781 15781

o m

15781 15781

Discuss the various addressing modes of the machine you are familiar with the help of

15781

a .r c

examples. What is an effective address or offset?

15781 2.

15781 Compare

15781

r p

RISC and CISC

15781 architectures.

15781

e

15781 15781 15781 15781

15781 15781

b

15781 15781 15781

a p

15781 15781 15781 15781

rp

SECTION-B

3. Define Pipelining. What are the types of pipelining? What are the various problems and

15781 15781

4.

performance

15781 issues in15781

b

pipelining? 15781 15781 15781 15781

What is DMA data transfer? In what circumstances this scheme of data transfer is

employed? What are burst mode and cycle stealing in DMA scheme?

15781

15781 15781 15781 15781 15781 15781 15781 15781 15781

15781 15781 15781 15781 SECTION-C

15781 15781 15781 15781 15781

5. What are the similarities and differences between paging and segmentation schemes of

memory management?

15781 15781 15781 15781 15781 15781 15781 15781 15781

6. Define Cache memory. What are the various memory mapping procedures involving

cache memory? Explain.

15781 15781 15781 15781 15781 15781 15781 15781 15781

1 | M-72709 (S6)-2983

15781 15781 15781 15781 15781 15781 15781 15781 15781

15781 15781 15781 15781 15781 15781 15781 15781 15781

15781 15781 15781 15781 15781 15781 15781 15781 15781

SECTION-D

15781 15781 15781 15781 15781 15781 15781 15781 15781

7. What is Multiprocessing? What is the difference between multiprocessing and parallel

processing? Explain in detail the memory and resource sharing and inter- processor

15781 15781 communication

15781 in multiprocessor

15781 computers.

15781 15781 15781 15781 15781

8. Discuss the various types of instructions used in a typical assembly language.

15781 15781 15781 15781 15781 15781 15781 15781 15781

SECTION-E

m

15781 15781 15781 15781 15781 15781 15781 15781 15781

9. Write briefly :

o

.r c

a. What is Instruction cycle?

15781 15781 15781 15781 15781 15781 15781 15781 15781

b. What is a Reverse Polish notation? What is its purpose?

15781 15781 c. What

15781

pe

do you mean15781

by micro-programmed

15781 control?

15781

o m

15781 15781 15781

a

d. What are Array processors?

p .r c

r e

15781 15781 15781 15781 15781 15781 15781 15781 15781

e. Differentiate between isolated I/O and memory-mapped I/O.

15781 15781

b

15781 15781 15781

a p

f. Write the major differences between CPU and Peripheral devices.

15781 15781 15781 15781

rp

g. Briefly discuss the programmed I/O mode.

15781 15781

i.

15781 15781

What is Associative memory? b

h. What do you mean by priority interrupt?

15781 15781 15781 15781 15781

15781 15781 j. What is Cache coherence?

15781 15781 15781 15781 15781 15781 15781

15781 15781 15781 15781 15781 15781 15781 15781 15781

15781 15781 15781 15781 15781 15781 15781 15781 15781

15781 15781 15781 15781 15781 15781 15781 15781 15781

2 | M-72709 (S6)-2983

15781 15781 15781 15781 15781 15781 15781 15781 15781

15781 15781 15781 15781 15781 15781 15781 15781 15781

Das könnte Ihnen auch gefallen

- Radio Shack TRS-80 Expansion Interface: Operator's Manual Catalog Numbers: 26-1140, 26-1141, 26-1142Von EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual Catalog Numbers: 26-1140, 26-1141, 26-1142Noch keine Bewertungen

- Digital Signal Processing: Instructio Ns To CandidatesDokument2 SeitenDigital Signal Processing: Instructio Ns To CandidatesRatish NairNoch keine Bewertungen

- Internal Combustion Engines: Instruction To CandidatesDokument2 SeitenInternal Combustion Engines: Instruction To Candidatesdkhurana10Noch keine Bewertungen

- Statistical Process Control Study: Data Collection: - Sample D2 A2 D4Dokument2 SeitenStatistical Process Control Study: Data Collection: - Sample D2 A2 D4Sridharan VenkatNoch keine Bewertungen

- Basic Water and Wastewater Treatment: Butterworths Basic SeriesVon EverandBasic Water and Wastewater Treatment: Butterworths Basic SeriesBewertung: 4.5 von 5 Sternen4.5/5 (8)

- IV B.Tech Pre Submission Seminar Schedule-1Dokument66 SeitenIV B.Tech Pre Submission Seminar Schedule-1Sasi Kumar ReddyNoch keine Bewertungen

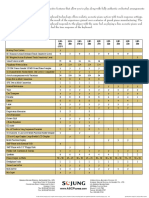

- Sejung Digital PianoDokument4 SeitenSejung Digital PianoRobbert GroenendijkNoch keine Bewertungen

- Paper Old Information SecurityDokument2 SeitenPaper Old Information SecurityJitender BansalNoch keine Bewertungen

- Mathematics Blue Print I Puc 2023-24 PDFDokument2 SeitenMathematics Blue Print I Puc 2023-24 PDFPrakash ReddyNoch keine Bewertungen

- Helloween - A Tale That Wasn't Right (Full)Dokument36 SeitenHelloween - A Tale That Wasn't Right (Full)Andres HuertasNoch keine Bewertungen

- Nokia SAR-X ChassisDokument1 SeiteNokia SAR-X ChassisIrfan AzizNoch keine Bewertungen

- Single Sheet Room WiseDokument34 SeitenSingle Sheet Room WisebachandeepNoch keine Bewertungen

- ST 618 Rev BDokument3 SeitenST 618 Rev Bsetra.razanamparanyNoch keine Bewertungen

- BOM For HPCL Phase 13 ProjectDokument5 SeitenBOM For HPCL Phase 13 ProjectGilbarcoNoch keine Bewertungen

- L7800 Series: Positive Voltage RegulatorsDokument34 SeitenL7800 Series: Positive Voltage RegulatorsPolo Soldas Polo SoldasNoch keine Bewertungen

- SB-16-86-12 5EAT TCM ReprogrammingDokument3 SeitenSB-16-86-12 5EAT TCM ReprogrammingossoskiNoch keine Bewertungen

- L7800 Series: Positive Voltage RegulatorsDokument35 SeitenL7800 Series: Positive Voltage Regulatorsimendoza17Noch keine Bewertungen

- IC65N Schneider BreakersDokument4 SeitenIC65N Schneider Breakersdabs_orangejuice0% (1)

- Cheyenne Airplane Service ManualDokument1.437 SeitenCheyenne Airplane Service ManualTríade MusicNoch keine Bewertungen

- GR 12 2015 February-March Paper 2Dokument32 SeitenGR 12 2015 February-March Paper 2Nhloniey SnowieNoch keine Bewertungen

- Mechanical Vibrations: Instructions To CandidatesDokument3 SeitenMechanical Vibrations: Instructions To CandidatesJose Amaro JovaNoch keine Bewertungen

- Mitsubishi Manuals TRA8AL PDFDokument31 SeitenMitsubishi Manuals TRA8AL PDFFernando SabogalNoch keine Bewertungen

- COMAT Timer CatalogueDokument7 SeitenCOMAT Timer CatalogueSamNoch keine Bewertungen

- ch08 Part1Dokument20 Seitench08 Part1onepiece93Noch keine Bewertungen

- Switchgear BOMDokument38 SeitenSwitchgear BOMsrc_srcNoch keine Bewertungen

- Toshiba Photocouplers and Photo RelaysDokument77 SeitenToshiba Photocouplers and Photo RelaysEhab Anwar ElnagdyNoch keine Bewertungen

- Disaster Management: Instruction To CandidatesDokument2 SeitenDisaster Management: Instruction To CandidatesArbaz HusainNoch keine Bewertungen

- 06 TR 78Dokument7 Seiten06 TR 78MarcolinoNoch keine Bewertungen

- Obsolete Product(s) - Obsolete Product(s) Obsolete Product(s) - Obsolete Product(s)Dokument16 SeitenObsolete Product(s) - Obsolete Product(s) Obsolete Product(s) - Obsolete Product(s)Martin MirandaNoch keine Bewertungen

- Easily Convert The 4L80E To Full Manual Control: They Say Necessity Is The Mother of InventionDokument8 SeitenEasily Convert The 4L80E To Full Manual Control: They Say Necessity Is The Mother of InventionDaniel GonzalezNoch keine Bewertungen

- Tabela de Transistores Saida HorizontalDokument6 SeitenTabela de Transistores Saida HorizontalRogério CunhaNoch keine Bewertungen

- Smartrack Side Panel Latch Installation: Owner'S Manual AddendumDokument1 SeiteSmartrack Side Panel Latch Installation: Owner'S Manual AddendumJavier EspinosaNoch keine Bewertungen

- Tea19162 (Ea19162)Dokument30 SeitenTea19162 (Ea19162)Adilson SilvérioNoch keine Bewertungen

- Secondary and High School TranscriptDokument2 SeitenSecondary and High School TranscriptGROUP COMBONoch keine Bewertungen

- Daily Time Sheet KontainerDokument1 SeiteDaily Time Sheet KontainerFebriyanti Wulan puspitaNoch keine Bewertungen

- Podem - Spare Parts - Electric Wire Rope Hoists, T Series (EN)Dokument24 SeitenPodem - Spare Parts - Electric Wire Rope Hoists, T Series (EN)Luka BornaNoch keine Bewertungen

- Technical Manual en Outdoor TVR Mini DC 220v 4tvh SN 07092021Dokument73 SeitenTechnical Manual en Outdoor TVR Mini DC 220v 4tvh SN 07092021Singh BaldevNoch keine Bewertungen

- Accounting For Management: Instruction To CandidatesDokument2 SeitenAccounting For Management: Instruction To CandidatesƎɯox SatíshNoch keine Bewertungen

- Tabel Acuan Mapping Pengapian ECU BRTDokument3 SeitenTabel Acuan Mapping Pengapian ECU BRTJunaidi75% (8)

- SMART UNO/Refarm RET Cabling & Naming Convention: (Needs Site Testing and Verification Before Taken in Use!)Dokument19 SeitenSMART UNO/Refarm RET Cabling & Naming Convention: (Needs Site Testing and Verification Before Taken in Use!)ismuwahyudiNoch keine Bewertungen

- GT161 EngDokument82 SeitenGT161 EngpiotrbpmNoch keine Bewertungen

- Transcript 1Dokument1 SeiteTranscript 1GROUP COMBONoch keine Bewertungen

- Rank Teamid Position N Userid Cumulative ProfitDokument2 SeitenRank Teamid Position N Userid Cumulative ProfitAnmol BaijalNoch keine Bewertungen

- Electronics Blueprint 1puc 2023 - 24Dokument3 SeitenElectronics Blueprint 1puc 2023 - 24sanjaykashiNoch keine Bewertungen

- Confidential: IT8783E/FDokument204 SeitenConfidential: IT8783E/FSomendra SinghNoch keine Bewertungen

- Manual - Mini-Triton 2 HD - EN 2Dokument24 SeitenManual - Mini-Triton 2 HD - EN 2Theo klNoch keine Bewertungen

- Production and Operations Management: Instruction To CandidatesDokument2 SeitenProduction and Operations Management: Instruction To CandidatesTobalynti TiewsohNoch keine Bewertungen

- Pa31t, Pa-31t1, Pa-31t2Dokument1.437 SeitenPa31t, Pa-31t1, Pa-31t2Maicon Franca100% (1)

- IJTAG Tutorial FINAL Circuitnet PDFDokument9 SeitenIJTAG Tutorial FINAL Circuitnet PDFSairam Prasad MarataNoch keine Bewertungen

- Automatic Transfer Switch: GencontrolDokument2 SeitenAutomatic Transfer Switch: GencontrolDonny G0% (1)

- CA3081, CA3082: General Purpose High Current NPN Transistor Arrays FeaturesDokument6 SeitenCA3081, CA3082: General Purpose High Current NPN Transistor Arrays FeaturesaburizqiNoch keine Bewertungen

- Cyf PLC Tta1Dokument1 SeiteCyf PLC Tta1yomar villcasNoch keine Bewertungen

- Compresor Ingersoll-Rand p185Dokument190 SeitenCompresor Ingersoll-Rand p185bacilevu92% (38)

- Taimoor CCN Assignment 4Dokument7 SeitenTaimoor CCN Assignment 4TaimoorNoch keine Bewertungen

- Algoritma Genetika Dalam MatlabDokument94 SeitenAlgoritma Genetika Dalam MatlabTomo Siagian50% (2)

- Jahangir 004Dokument1 SeiteJahangir 004TaimoorNoch keine Bewertungen

- Temp DefecttrackinglogDokument2 SeitenTemp DefecttrackinglogTaimoorNoch keine Bewertungen

- Notes of StatisitcsDokument30 SeitenNotes of StatisitcsTaimoorNoch keine Bewertungen

- Course OutlineDokument4 SeitenCourse OutlineTaimoorNoch keine Bewertungen

- Eligibility CriteriaDokument6 SeitenEligibility CriteriaShawala AzharNoch keine Bewertungen

- Computer Architecture and Assembly Language Programming - CS401Fall 2004 Final Term PaperDokument2 SeitenComputer Architecture and Assembly Language Programming - CS401Fall 2004 Final Term PaperTaimoorNoch keine Bewertungen

- Online Shopping Uml ExamplesDokument12 SeitenOnline Shopping Uml ExamplesPLegendTiger67% (3)

- BtechDokument46 SeitenBtechTaimoorNoch keine Bewertungen

- CS330 Software Engineering: Software Requirements Specifications DocumentDokument29 SeitenCS330 Software Engineering: Software Requirements Specifications DocumentSumant LuharNoch keine Bewertungen

- DS-KV6113-WPE1B Villa-Door-Station Datasheet V1.0 20201022Dokument3 SeitenDS-KV6113-WPE1B Villa-Door-Station Datasheet V1.0 20201022pablosargNoch keine Bewertungen

- Timers and Time Base Generation: Experiment 10Dokument7 SeitenTimers and Time Base Generation: Experiment 10Suleman SaleemNoch keine Bewertungen

- Image ClassificationDokument16 SeitenImage ClassificationMona SinghNoch keine Bewertungen

- Annexure H - Roll Out Checklist For Post OfficeDokument3 SeitenAnnexure H - Roll Out Checklist For Post OfficeAvinash YadavNoch keine Bewertungen

- JANMEJAY SINGH PROJECT CS - Sanjai SinghDokument24 SeitenJANMEJAY SINGH PROJECT CS - Sanjai SinghHungry-- JoyNoch keine Bewertungen

- IdeaPad 5 15IAL7Dokument2 SeitenIdeaPad 5 15IAL7Miguel Gaibor MestanzaNoch keine Bewertungen

- C Programming VIVA QuestionsDokument2 SeitenC Programming VIVA QuestionsPrajwal khanalNoch keine Bewertungen

- OpendTect Administrators ManualDokument112 SeitenOpendTect Administrators ManualKarla SantosNoch keine Bewertungen

- Operating Systems Course Code: 3330701Dokument6 SeitenOperating Systems Course Code: 3330701Monil SolankiNoch keine Bewertungen

- Importing Data From Excel Into SPSSDokument10 SeitenImporting Data From Excel Into SPSSLayan MohammadNoch keine Bewertungen

- HikCentral Professional - System Requirements and Performance - V2.3 - 20220713Dokument25 SeitenHikCentral Professional - System Requirements and Performance - V2.3 - 20220713TestingtoolNoch keine Bewertungen

- Wireless Sensor Networks For Agriculture: The State-of-the-Art in Practice and Future ChallengesDokument25 SeitenWireless Sensor Networks For Agriculture: The State-of-the-Art in Practice and Future Challengesalita betta100% (1)

- Gym Management System ReportDokument17 SeitenGym Management System ReportjonNoch keine Bewertungen

- The Design and Research of The Control System of Automatic Intelligent Rice Cooker, Based On STM32Dokument7 SeitenThe Design and Research of The Control System of Automatic Intelligent Rice Cooker, Based On STM32Asteraceae ChrysanthNoch keine Bewertungen

- PyeconDokument326 SeitenPyeconEdu MerinoNoch keine Bewertungen

- CISA Practice Exam QuestionsDokument12 SeitenCISA Practice Exam QuestionsAmiraNoch keine Bewertungen

- Template Nilai Akhir Mata Pelajaran Teknologi Layanan Jaringan Kelas XI TKJ 1Dokument23 SeitenTemplate Nilai Akhir Mata Pelajaran Teknologi Layanan Jaringan Kelas XI TKJ 1Akhmad JuhairiNoch keine Bewertungen

- Menus, Sub Procedures and Sub FunctionsDokument28 SeitenMenus, Sub Procedures and Sub Functionsflower boomNoch keine Bewertungen

- CS331 System Software Lab CSE Syllabus-Semesters - 5Dokument2 SeitenCS331 System Software Lab CSE Syllabus-Semesters - 5RONIN TNoch keine Bewertungen

- Chapter 4. Everything Can Be AutomatedDokument20 SeitenChapter 4. Everything Can Be AutomatedCHUA CHONG SHENNoch keine Bewertungen

- Proceedings of The Sixth IEEE International Conference On Fuzzy Systems - Volume IDokument20 SeitenProceedings of The Sixth IEEE International Conference On Fuzzy Systems - Volume IFrancisca SotoNoch keine Bewertungen

- Summer Training in NTPC Rihand Nagar at IT DeptDokument23 SeitenSummer Training in NTPC Rihand Nagar at IT DeptRoop ChandNoch keine Bewertungen

- Introduction To Computer VirusesDokument31 SeitenIntroduction To Computer Virusesaafy92% (12)

- Project Report of Operating SystemDokument14 SeitenProject Report of Operating Systemijgour77% (13)

- BendixKing First-time-downloader-CURRENTv2Dokument4 SeitenBendixKing First-time-downloader-CURRENTv2Tovonirina RakotomalalaNoch keine Bewertungen

- Introduction To The PyboardDokument61 SeitenIntroduction To The Pyboardolawale gbadeboNoch keine Bewertungen

- EcoStruxure For Data Center (BMS & EPMS)Dokument32 SeitenEcoStruxure For Data Center (BMS & EPMS)Yoga SamNoch keine Bewertungen

- In The Name of Allah, The All-Merciful, The Mercy-GivingDokument35 SeitenIn The Name of Allah, The All-Merciful, The Mercy-GivingMuhammad AnasNoch keine Bewertungen

- Curriculum Syllabus Btech Ece Data Science Reg 2018Dokument122 SeitenCurriculum Syllabus Btech Ece Data Science Reg 2018praveenembd1Noch keine Bewertungen

- Soft DeskDokument5 SeitenSoft DeskDharamvir DasNoch keine Bewertungen

- Chip War: The Quest to Dominate the World's Most Critical TechnologyVon EverandChip War: The Quest to Dominate the World's Most Critical TechnologyBewertung: 4.5 von 5 Sternen4.5/5 (227)

- Chip War: The Fight for the World's Most Critical TechnologyVon EverandChip War: The Fight for the World's Most Critical TechnologyBewertung: 4.5 von 5 Sternen4.5/5 (82)

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsVon EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsBewertung: 5 von 5 Sternen5/5 (2)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Von EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Bewertung: 5 von 5 Sternen5/5 (2)

- Unlock Any Roku Device: Watch Shows, TV, & Download AppsVon EverandUnlock Any Roku Device: Watch Shows, TV, & Download AppsNoch keine Bewertungen

- CompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Von EverandCompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Bewertung: 5 von 5 Sternen5/5 (1)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Von EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Bewertung: 5 von 5 Sternen5/5 (2)

- CompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Von EverandCompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Bewertung: 5 von 5 Sternen5/5 (2)

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Von EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Bewertung: 5 von 5 Sternen5/5 (1)

- Windows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertVon EverandWindows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertBewertung: 3.5 von 5 Sternen3.5/5 (6)

- How to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideVon EverandHow to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideBewertung: 1 von 5 Sternen1/5 (1)

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XVon EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XBewertung: 3 von 5 Sternen3/5 (2)

- Amazon Web Services (AWS) Interview Questions and AnswersVon EverandAmazon Web Services (AWS) Interview Questions and AnswersBewertung: 4.5 von 5 Sternen4.5/5 (3)

- Computer Science: A Concise IntroductionVon EverandComputer Science: A Concise IntroductionBewertung: 4.5 von 5 Sternen4.5/5 (14)

- Mastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFVon EverandMastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFNoch keine Bewertungen

- Raspberry Pi for Python Programmers Cookbook - Second EditionVon EverandRaspberry Pi for Python Programmers Cookbook - Second EditionNoch keine Bewertungen

- Essential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XVon EverandEssential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XBewertung: 5 von 5 Sternen5/5 (1)

- Amazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesVon EverandAmazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesNoch keine Bewertungen

- Raspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesVon EverandRaspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesNoch keine Bewertungen

- Real-Time UML Workshop for Embedded SystemsVon EverandReal-Time UML Workshop for Embedded SystemsBewertung: 3.5 von 5 Sternen3.5/5 (2)

![Catalan's Constant [Ramanujan's Formula]](https://imgv2-2-f.scribdassets.com/img/word_document/399691191/149x198/f7e96de7ef/1668683798?v=1)

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-2-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1714829744?v=1)