Beruflich Dokumente

Kultur Dokumente

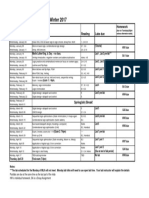

CS2420 - Introduction To Digital Logic Design: 2017/18 Tentative Lecture Schedule

Hochgeladen von

Koetlisi Makhaola Elliott Theko0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

14 Ansichten1 Seitegood

Originaltitel

CS2420 Calendar

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldengood

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

14 Ansichten1 SeiteCS2420 - Introduction To Digital Logic Design: 2017/18 Tentative Lecture Schedule

Hochgeladen von

Koetlisi Makhaola Elliott Thekogood

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 1

CS2420 – Introduction to Digital Logic Design

2017/18 Tentative Lecture schedule

DATE JANUARY February MARCH APRIL

st

1 Sunday

nd

2 Class Test 1 Arithmetic ccts 2 Easter Monday

rd

3 Introduction Saturday Saturday No Lab

th

4 Introduction Sunday Sunday Registers 2

th

5 Introduction Programmable logic devs 1 SHORT BREAK

th

6 Saturday Tutorial 2 SHORT BREAK Counters (sync)

th

7 Sunday Programmable logic devs 2 SHORT BREAK Saturday

th

8 Binary Numbers SHORT BREAK Sunday

th

9 No Lab Programmable logic devs 3 SHORT BREAK Counter design 1

th

10 Logic gates and networks Saturday Saturday Lab 4

th

11 Sunday Sunday Counter design 2

th

12 Boolean Algebra intro Karnaugh Map 1 variable Combinational ccts

th

13 Saturday Lab 1 Lab 3 Circuit design task

th

14 Sunday Karnaugh Map 2 & 3 variable Multiplexers Saturday

th

15 The Venn Diagram Sunday

th

16 No Lab Karnaugh maps multiple vars Multiplexers Revision

th

17 Synthesis using gates Saturday Saturday Lab 4 demo

th

18 Sunday Sunday Revision

th

19 Sums-of-products form Multiple output circuits Decoders

th

20 Saturday Lab 2 Class Test 2 Lectures End

st

21 Sunday Multilevel circuits Latches Saturday

nd

22 Product-of-sums form Sunday

rd

23 Tutorial 1 Unsigned integers Flip-flops (D-Type) SWOT WEEK

th

24 Product-of-sums cont. Saturday Saturday SWOT WEEK

th

25 Sunday Sunday SWOT WEEK

th

26 NAND and NOR circuits Arithmetic circuits 1 Flip-flops (JK) SWOT WEEK

th

27 Saturday Tutorial 3 SWOT WEEK

th

28 Sunday Signed numbers Registers 1 Saturday

th

29 NAND and NOR circuits Sunday

th

30 Class Test 1 Good Friday

st

31 Design Example MUX ccts Saturday

EXAMINATIONS PERIOD: Monday, 7th May 2018 to Sunday, 20th May 2018

Das könnte Ihnen auch gefallen

- Sheiko 13week Beginner ProgramDokument16 SeitenSheiko 13week Beginner ProgramAnders DahlNoch keine Bewertungen

- Dry Docking QuotationDokument4 SeitenDry Docking Quotationboen jayme100% (1)

- Archaeology - October 2016 PDFDokument72 SeitenArchaeology - October 2016 PDFOmer CetinkayaNoch keine Bewertungen

- Motivational QuotesDokument39 SeitenMotivational QuotesNarayanan SubramanianNoch keine Bewertungen

- Ee460m Lab ManualDokument106 SeitenEe460m Lab Manualganga_ch1Noch keine Bewertungen

- CMPE344F2023 - Syllabus NDokument2 SeitenCMPE344F2023 - Syllabus NDağlar TekşenNoch keine Bewertungen

- Weekly Assignments Semester 1 Math 10c 2019-2020Dokument6 SeitenWeekly Assignments Semester 1 Math 10c 2019-2020api-302976262Noch keine Bewertungen

- EE2026 L0 IntroDokument34 SeitenEE2026 L0 IntrovidyaNoch keine Bewertungen

- Course Outline DLD (EE-225)Dokument2 SeitenCourse Outline DLD (EE-225)Ali ShahabNoch keine Bewertungen

- Program Calendar - DS C50 - November 2022 - Sheet1Dokument3 SeitenProgram Calendar - DS C50 - November 2022 - Sheet1Alakesh Coldplay KalitaNoch keine Bewertungen

- Lecture 11 - Finite State Machines - Digital DesignDokument31 SeitenLecture 11 - Finite State Machines - Digital DesignPatrick LustyNoch keine Bewertungen

- Gate 2021 Testseries ScheduleDokument8 SeitenGate 2021 Testseries ScheduleAlamuru SrinidhiNoch keine Bewertungen

- EEE4134 CO Spring2021Dokument4 SeitenEEE4134 CO Spring2021Abdullah Al SakibNoch keine Bewertungen

- EPGP SD April'21 Student CalendarDokument24 SeitenEPGP SD April'21 Student CalendarKapilNoch keine Bewertungen

- SMA LAb Course HandoutDokument4 SeitenSMA LAb Course HandoutrajNoch keine Bewertungen

- EE2026 L0 ModuleIntroDokument24 SeitenEE2026 L0 ModuleIntrokewlkidsstreetsNoch keine Bewertungen

- Lab 10Dokument5 SeitenLab 10Aafaq khanNoch keine Bewertungen

- MolbaysDokument10 SeitenMolbaysZOHORE BATRANINoch keine Bewertungen

- Digital (Iit Kharagpur)Dokument853 SeitenDigital (Iit Kharagpur)Sourabh YadavNoch keine Bewertungen

- DE 2022 VikasDokument6 SeitenDE 2022 VikasSRC ExamNoch keine Bewertungen

- DLD Lesson PlanDokument3 SeitenDLD Lesson Planjy yusufiNoch keine Bewertungen

- Open Electives 2013-14aDokument4 SeitenOpen Electives 2013-14aRajalearn2 Ramlearn2Noch keine Bewertungen

- 108105132Dokument900 Seiten108105132Soumya Ranjan BeheraNoch keine Bewertungen

- ECE241 Syllabus Fall 2014Dokument7 SeitenECE241 Syllabus Fall 2014Tetteh SamuelNoch keine Bewertungen

- Digital Electronics Lab ManualDokument35 SeitenDigital Electronics Lab ManualrickyreddyNoch keine Bewertungen

- s19 ArchitectureDokument11 Seitens19 ArchitecturePhu Phan ThanhNoch keine Bewertungen

- CSE369 Lab3 Wi22Dokument3 SeitenCSE369 Lab3 Wi22Deniz Melek TürkNoch keine Bewertungen

- ECE-EEE-INSTR-CS F215 - DD - Sem-1 2021-22 HODokument3 SeitenECE-EEE-INSTR-CS F215 - DD - Sem-1 2021-22 HOUrvi ModiNoch keine Bewertungen

- Course Outline 2Dokument1 SeiteCourse Outline 2jolo cunananNoch keine Bewertungen

- Prelim Exam 22-23 DSBDADokument2 SeitenPrelim Exam 22-23 DSBDAmohamed mowafeyNoch keine Bewertungen

- DLD Lab Report 2Dokument7 SeitenDLD Lab Report 2Talha TufailNoch keine Bewertungen

- STLD LP - VparDokument4 SeitenSTLD LP - VparVenkat ChadalavadaNoch keine Bewertungen

- Agustus Minggu Senin SelasaDokument15 SeitenAgustus Minggu Senin SelasaAmelNoch keine Bewertungen

- Elec 578 - Integrated Circuit DesignDokument4 SeitenElec 578 - Integrated Circuit DesignVishnu 3333Noch keine Bewertungen

- DLD Course OulineDokument2 SeitenDLD Course OulineSarangNoch keine Bewertungen

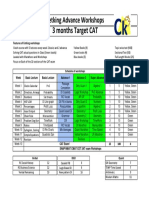

- 2 Months Target CAT - 21 Sept Batch: Cetking Advance WorkshopsDokument1 Seite2 Months Target CAT - 21 Sept Batch: Cetking Advance WorkshopsjoNoch keine Bewertungen

- ECE 385 Digital Systems Laboratory: SyllabusDokument2 SeitenECE 385 Digital Systems Laboratory: Syllabuspeter19960124Noch keine Bewertungen

- EE&EC Batch Doc (Updated)Dokument6 SeitenEE&EC Batch Doc (Updated)Deepak PraiseNoch keine Bewertungen

- Syllabus For CSCI 631 - Foundations of Computer VisionDokument1 SeiteSyllabus For CSCI 631 - Foundations of Computer VisionddkkNoch keine Bewertungen

- Syllabus For CSCI 631 - Foundations of Computer VisionDokument1 SeiteSyllabus For CSCI 631 - Foundations of Computer VisionddkkNoch keine Bewertungen

- 241 CSM-4 - Digital Logic-Course SpecificationDokument7 Seiten241 CSM-4 - Digital Logic-Course SpecificationahmedNoch keine Bewertungen

- ME119 Schedule Course Contents Policies PDFDokument7 SeitenME119 Schedule Course Contents Policies PDFPriyanshu MeshramNoch keine Bewertungen

- Logic Designing and Switching Theory BookDokument41 SeitenLogic Designing and Switching Theory BookAli Shan Rajput67% (3)

- EECS 270 Class Schedule: Winter 2017: HomeworkDokument1 SeiteEECS 270 Class Schedule: Winter 2017: HomeworkscribdyoyohoneysinghNoch keine Bewertungen

- Bahria University, Lahore Campus: Department of Computer SciencesDokument5 SeitenBahria University, Lahore Campus: Department of Computer SciencesAbdul BasitNoch keine Bewertungen

- Microprocessor Systems: Lecture 1: Course Overview Digital Logic ReviewDokument31 SeitenMicroprocessor Systems: Lecture 1: Course Overview Digital Logic ReviewzhopaaaNoch keine Bewertungen

- Colegio de Sta. Teresa de AvilaDokument3 SeitenColegio de Sta. Teresa de AvilaHarold LuceroNoch keine Bewertungen

- Digital Design Lab Course Code:-Cse256PDokument38 SeitenDigital Design Lab Course Code:-Cse256PYash JaiswalNoch keine Bewertungen

- Computer ScienceDokument8 SeitenComputer ScienceAriyan MalikNoch keine Bewertungen

- Six Months Training in NI Lab VIEW Syllabus DetailsDokument3 SeitenSix Months Training in NI Lab VIEW Syllabus DetailsgudduNoch keine Bewertungen

- CAT 2020 32 Weeks Schedule Weekly TimetableDokument1 SeiteCAT 2020 32 Weeks Schedule Weekly TimetableAyaat AttarNoch keine Bewertungen

- CSE369 Lab1&2 Wi22Dokument5 SeitenCSE369 Lab1&2 Wi22Deniz Melek TürkNoch keine Bewertungen

- NU (DIGITTAL ELECTRONICS AND INSTRUMENTS) LatestDokument2 SeitenNU (DIGITTAL ELECTRONICS AND INSTRUMENTS) Latestkhushalee.chavadaNoch keine Bewertungen

- Weekly Assignments Semester 1 Math 30-2 2019-2020Dokument6 SeitenWeekly Assignments Semester 1 Math 30-2 2019-2020api-302976262Noch keine Bewertungen

- 2023spring DSA SyllabusDokument9 Seiten2023spring DSA SyllabusUmud AbutalibovNoch keine Bewertungen

- 3 Months Target CAT: Cetking Advance WorkshopsDokument1 Seite3 Months Target CAT: Cetking Advance WorkshopsmyeyeNoch keine Bewertungen

- Green University of Bangladesh Department of Computer Science and Engineering (CSE)Dokument6 SeitenGreen University of Bangladesh Department of Computer Science and Engineering (CSE)jljlNoch keine Bewertungen

- Digital Design Course SyllabusDokument2 SeitenDigital Design Course SyllabusDahlia ZamoraNoch keine Bewertungen

- Ktu Asst (Academic) 2692 2018Dokument4 SeitenKtu Asst (Academic) 2692 2018Anonymous QlZBYqlSqZNoch keine Bewertungen

- CO204 - Design of Digital Systems Lab (B. Tech, 3 Semester) : X y X yDokument4 SeitenCO204 - Design of Digital Systems Lab (B. Tech, 3 Semester) : X y X yKeerti ChaudharyNoch keine Bewertungen

- EEE 100 1s1819 Class SyllabusDokument3 SeitenEEE 100 1s1819 Class SyllabusEmman Joshua BustoNoch keine Bewertungen

- Lab Workbook: Design and Analysis of AlgorithmsDokument50 SeitenLab Workbook: Design and Analysis of Algorithmsyaswanth ramNoch keine Bewertungen

- DLD Lab ManualDokument59 SeitenDLD Lab ManualF223272 Minahil MohsinNoch keine Bewertungen

- A Survey of Computational Physics: Introductory Computational ScienceVon EverandA Survey of Computational Physics: Introductory Computational ScienceNoch keine Bewertungen

- School Management System MCS 2010Dokument14 SeitenSchool Management System MCS 2010Koetlisi Makhaola Elliott ThekoNoch keine Bewertungen

- 7 Web PDFDokument2 Seiten7 Web PDFKoetlisi Makhaola Elliott ThekoNoch keine Bewertungen

- ProectDokument12 SeitenProectKoetlisi Makhaola Elliott ThekoNoch keine Bewertungen

- Lab 6 PolymorphismDokument6 SeitenLab 6 PolymorphismKoetlisi Makhaola Elliott ThekoNoch keine Bewertungen

- Lecture 4 EMADokument36 SeitenLecture 4 EMAYai IbrahimNoch keine Bewertungen

- GutsDokument552 SeitenGutsroparts cluj100% (1)

- Scan 03-Jan-2020 PDFDokument2 SeitenScan 03-Jan-2020 PDFPavanSharmaNoch keine Bewertungen

- Effect of Social Economic Factors On Profitability of Soya Bean in RwandaDokument7 SeitenEffect of Social Economic Factors On Profitability of Soya Bean in RwandaMarjery Fiona ReyesNoch keine Bewertungen

- Cultivation and Horticulture of SandalwoodDokument2 SeitenCultivation and Horticulture of SandalwoodAnkitha goriNoch keine Bewertungen

- Questions 1Dokument3 SeitenQuestions 1krp_212003Noch keine Bewertungen

- Somanabolic+Muscle+Maximizer+PDF+ +eBook+Free+Download+Kyle+LeonDokument34 SeitenSomanabolic+Muscle+Maximizer+PDF+ +eBook+Free+Download+Kyle+LeonAaron BarclayNoch keine Bewertungen

- Position Trading Maximizing Probability of Winning TradesDokument91 SeitenPosition Trading Maximizing Probability of Winning Tradescarlo bakaakoNoch keine Bewertungen

- Danielson Observation FormDokument5 SeitenDanielson Observation Formapi-242909722Noch keine Bewertungen

- Egalitarianism As UK: Source: Hofstede Insights, 2021Dokument4 SeitenEgalitarianism As UK: Source: Hofstede Insights, 2021kamalpreet kaurNoch keine Bewertungen

- Listening 3b Skills Test 1aDokument3 SeitenListening 3b Skills Test 1aPticaSelicaNoch keine Bewertungen

- Exercise Chapter 4 This Is How You Do ItDokument10 SeitenExercise Chapter 4 This Is How You Do ItAgustina WidiyantiNoch keine Bewertungen

- UW Mathematics Professor Evaluations For Fall 2011Dokument241 SeitenUW Mathematics Professor Evaluations For Fall 2011DPNoch keine Bewertungen

- Physics Unit 3 Practice Test Dynamics5Dokument5 SeitenPhysics Unit 3 Practice Test Dynamics5StephanieNoch keine Bewertungen

- User Manual For Scanbox Ergo & Banquet Line: Ambient (Neutral), Hot and Active Cooling. Scanbox Meal Delivery CartsDokument8 SeitenUser Manual For Scanbox Ergo & Banquet Line: Ambient (Neutral), Hot and Active Cooling. Scanbox Meal Delivery CartsManunoghiNoch keine Bewertungen

- Tele-Medicine: Presented by Shyam.s.s I Year M.SC NursingDokument12 SeitenTele-Medicine: Presented by Shyam.s.s I Year M.SC NursingShyamNoch keine Bewertungen

- What Is StevedoringDokument10 SeitenWhat Is StevedoringMinhaj KmNoch keine Bewertungen

- Network Models For Seat Allocation On Flights: Moshe Dror,?Dokument12 SeitenNetwork Models For Seat Allocation On Flights: Moshe Dror,?Isabel VillaNoch keine Bewertungen

- Sap Business Objects Edge Series 3.1 Install Windows enDokument104 SeitenSap Business Objects Edge Series 3.1 Install Windows enGerardoNoch keine Bewertungen

- ACI 318M-11 RC Bracket and Corbel Design - v0.03 - 2017-04-10Dokument5 SeitenACI 318M-11 RC Bracket and Corbel Design - v0.03 - 2017-04-10arken123Noch keine Bewertungen

- Jerehy's ReportDokument65 SeitenJerehy's Reportkupetroleum3Noch keine Bewertungen

- Pset 2Dokument13 SeitenPset 2rishiko aquinoNoch keine Bewertungen

- Fastener Torque Charts: Phone: 1-800-558-2808 Fax: 1-800-553-8769Dokument2 SeitenFastener Torque Charts: Phone: 1-800-558-2808 Fax: 1-800-553-8769KOMATSU SHOVELNoch keine Bewertungen

- 1422-Article Text-3684-1-10-20211104Dokument57 Seiten1422-Article Text-3684-1-10-20211104f.kpobi1473Noch keine Bewertungen

- Markov Decision Processes For Path Planning in Unpredictable EnvironmentDokument8 SeitenMarkov Decision Processes For Path Planning in Unpredictable EnvironmentVartolomeiDumitruNoch keine Bewertungen

- Healthy Body CompositionDokument18 SeitenHealthy Body CompositionSDasdaDsadsaNoch keine Bewertungen