Beruflich Dokumente

Kultur Dokumente

GSET3 Cours Machines A Etats 1

Hochgeladen von

raafateOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

GSET3 Cours Machines A Etats 1

Hochgeladen von

raafateCopyright:

Verfügbare Formate

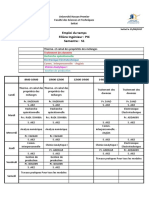

UNIVERSITE HASSAN II CASABLANCA

FACULTE DES SCIENCES & TECHNIQUES MOHAMMEDIA

Département Génie Electrique

Filière d’Ingénieurs : Génie Electrique & Télécommunications GET3

Les machines d’états permettent d’effectuer la synthèse de systèmes numériques séquentiels,

généralement synchrones (mais la synthèse de systèmes asynchrones est possible) à partir d’un

cahier des charges. Quelques exemples vont permettre de nous familiariser avec cette notion.

Exemple 1 : moteur pas à pas à sens de rotation unique.

Synthétisons dans ce premier exemple le séquenceur destiné à la commande d’un moteur pas à pas,

unipolaire 4 phases, à un seul sens de rotation, en fonctionnement pas entier deux phases (voir le

principe de fonctionnement d’un tel moteur en annexe). Nous avons ci-après les signaux recherchés

S0, S1, S2 et S3 pour la commande des phases en fonction de l’horloge H :

On note 4 états possibles en sortie, s’enchaînant inconditionnellement dans l’ordre E1, E2, E3, E4,

E1…au rythme de l’horloge H.

A partir de ce cahier des charges, on peut en déduire le diagramme (ou diagramme à bulles) suivant ;

Ce diagramme représente les différents états du système, en précisant éventuellement les niveaux

logiques correspondants en sortie, et les conditions de passage d’un état à l’autre. Dans notre cas très

simple, à chaque coup d’horloge, on passe inconditionnellement à l’état suivant.

La machine doit toujours se trouver au moins dans un état, et dans un seul état.

Avant l’apparition des langages HDL (Hardware circuits Description Language) de programmation,

la synthèse d’une machine d’état impliquait la recherche des équations des entrées des bascules de

mémorisation des états. Aujourd’hui, il est possible de retranscrire directement le diagramme d’état

en programme ; voici par exemple, un fichier VHLD associé à ce diagramme :

library ieee;

use ieee.std_logic_1164.all;

entity cde_mot_2 is

port( H : in std_logic;

Machine à Etats avec VHDL Page 1

FSTM Génie Electrique & Télécommunications GSET3

SORTIES : out std_logic_vector (3 downto 0));

end cde_mot_2;

architecture ARC_CDE OF cde_mot_2 is

type TYPE_ETAT is (E1, E2, E3, E4);

signal X:TYPE_ETAT;

begin

process(H)

begin

if H'event and H = '1' then

case X is

when E1 => X <= E2;

when E2 => X <= E3;

when E3 => X <= E4;

when others => X <= E1;

end case;

end if;

end process;

with X select

SORTIES <= "1001" when E1,

"1010" when E2,

"0110" when E3,

"0101" when E4;

end ARC_CDE;

L’architecture du programme comprend deux parties distincts : l’instruction « process » gère le

passage d’un état au suivant à chaque coup d’horloge, tandis l’instruction « with select » affecte aux

sorties les valeurs correspondant à chaque état.

Remarques : le programme aurait pu être simplifié ( et les ressources du circuit cible économisées)

en remarquant que les sorties étaient complémentaires deux à deux.

On notera que tous les états possibles des sorties n’ont pas été traités dans le diagramme d’état, afin

de ne pas l’alourdir. Dans la description VHDL cependant, les états imprévus conduisent à l’état E1

(instruction « when others ») au coup d’horloge suivant. Cette solution n’est pas toujours la plus

intéressante, un état imprévu conduisant alors à un fonctionnement aléatoire difficile à détecter et à

supprimer ; il est parfois préférable d’avoir une panne franche, en prévoyant par exemple un état «

Erreur ».

Exemple 2 : moteur pas à pas à double sens de rotation.

Reprenons le premier exemple en introduisant cette fois une commande S permettant de choisir le

sens de rotation. Nous supposerons cette commande synchrone dans un premier temps.

Les chronogrammes recherchés sont alors :

Ce qui nous conduit au diagramme d’état suivant :

Machines à Etats (FSM) avec VHDL Page 2

FSTM Génie Electrique & Télécommunications GSET3

Remarques :

lorsque plusieurs entrées interviennent dans un diagramme d’état, on suppose qu’une seule

est susceptible de changer à un instant donné ;

lorsque les conditions ne sont pas réalisées, l’état ne change pas (dans notre exemple, les

conditions étant complémentaires, elles sont toujours réalisées) ;

lorsque plusieurs branchements sont possibles à partir d’un état, les conditions ne doivent pas

être vraies en même temps ;

la présence de l’horloge est implicite, le passage d’un état à l’autre ne peut se faire qu’au

front actif de l’horloge.

Une description VHDL possible est alors donnée ci-après :

entity cde_mot_2Sens is

port( H,S : in std_logic;

SORTIES : out std_logic_vector (3 downto 0));

end cde_mot_2Sens;

architecture ARC_CDE OF cde_mot_2Sens is

type TYPE_ETAT is (E1, E2, E3, E4);

signal X : TYPE_ETAT;

begin

process (H)

begin

if H'event and H = '1' then

case X is

when E1 =>

if S='1' then X <= E2; else X <=E4;end if;

when E2 =>

if S='1' then X <= E3; else X <=E1; end if;

when E3 =>

if S='1' then X <= E4; else X <=E2; end if;

when others =>

if S='1' then X <= E1; else X <=E3; end if;

end case;

end if;

end process;

with X select

SORTIES <= "1001" when E1,

"1010" when E2,

"0110" when E3,

"0101" when E4;

end ARC_CDE;

Exemple 3 : diviseur de fréquence.

Le nombre d’états d’un système n’est pas lié au nombre d’états possibles des sorties. Considérons

par exemple un diviseur de fréquence fournissant une impulsion en sortie toutes les quatre

impulsions du signal d’horloge.

Pour synthétiser un tel diviseur, il ne suffit évidemment pas de prendre en compte les deux états

possibles de la sortie, mais tous les états intermédiaires du système.

Machines à Etats (FSM) avec VHDL Page 3

FSTM Génie Electrique & Télécommunications GSET3

Un exemple de programme est donné ci-après :

library ieee;

use ieee.std_logic_1164.all;

entity div4 is

port( H : in std_logic;

S : out std_logic);

end div4;

architecture ARC_div OF div4 is

type TYPE_ETAT is (E1, E2, E3, E4);

signal X:TYPE_ETAT;

begin

process (H)

begin

if H'event and H = '1' then

case X is

when E1 => X <= E2;

when E2 => X <= E3;

when E3 => X <= E4;

when others => X <= E1;

end case;

end if;

end process;

S <= '1' when X=E4 else '0';

end ARC_div;

Description d’une machine d’état à l’aide de l’utilitaire de Quartus

Le logiciel Quartus nous permet de décrire directement graphiquement notre fonctionnement par une

machine d’état.

Il est cependant important de comprendre qu’il ne s’agit que d’une aide, dont le but est de générer un

fichier HDL (Hardware Description Language), par exemple en VHDL, fichier qui servira de base de

départ aux différentes simulations et compilations.

La syntaxe générée par l’éditeur de machine d’état de Quartus est un peu différente de celle que nous

avons étudiée précédemment, le programme suivant correspondant à notre première description

d’une commande de moteur pas à pas à un seul sens de rotation :

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY ME IS

PORT ( clock : IN STD_LOGIC;

reset : IN STD_LOGIC := '0';

SORTIES : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END ME;

ARCHITECTURE BEHAVIOR OF ME IS

TYPE type_fstate IS (ETAT1,ETAT2,ETAT3,ETAT4);

SIGNAL fstate : type_fstate;

SIGNAL reg_fstate : type_fstate;

BEGIN

PROCESS (clock,reg_fstate)

BEGIN

IF (clock='1' AND clock'event) THEN fstate <= reg_fstate; END IF;

END PROCESS;

PROCESS (fstate,reset)

BEGIN

IF (reset='1') THEN reg_fstate <= ETAT1; SORTIES <= "0000"; ELSE SORTIES <= "0000";

CASE fstate IS

WHEN ETAT1 => reg_fstate <= ETAT2; SORTIES <= "0001";

WHEN ETAT2 => reg_fstate <= ETAT3; SORTIES <= "0010";

WHEN ETAT3 => reg_fstate <= ETAT4; SORTIES <= "0100";

WHEN ETAT4 => reg_fstate <= ETAT1; SORTIES <= "1000";

WHEN OTHERS => SORTIES <= "XXXX";

report "Reach undefined state";

END CASE; END IF;

END PROCESS;

END BEHAVIOR; END PROCESS; END BEHAVIOR;

Machines à Etats (FSM) avec VHDL Page 4

FSTM Génie Electrique & Télécommunications GSET3

On notera la déclaration de deux registre d’état, le premier « fstate » mémorisant l’état présent, le

second « reg_fstate » mémorisant l’état futur en fonction d’éventuelles entrées. L’état futur devient

l’état présent à chaque coup d’horloge dans le premier « process ».

Exemple d’utilisation

Reprenons la commande d’un moteur pas à pas, de quatre phases unipolaire décrit en annexe. Nous

allons synthétiser une machine d’état proposant ces deux modes de fonctionnement pour les deux

sens de rotation, en fonction de deux entrées :

S pour le sens ;

P pour un fonctionnement pas entier une phase ou demi-pas.

Si P est au NL1 on passe par tous les états 1, 2, 3, 4, 5, 6, 7, 8, 1… dans cet ordre ou l’inverse suivant

la valeur de S.

Si P est au NL0, seuls les états pairs seront actifs, dans l’ordre 2, 4, 6, 8, 2… ou l’inverse suivant la

valeur de S.

1001 1000 1010

0001 0010

0101(Début) 0100

0110

On pourrait imaginer aussi une entrée proposant un mode demi-pas deux phases, où seuls les états

impairs seraient actifs.

Après avoir ouvert un projet par les méthodes habituelles, ouvrir une feuille de description de

machine d’état par « file » « new » puis « States Machine File » :

Il est alors possible de décrire notre machine, soit directement sur la feuille à partir des outils

proposés, soit à l’aide de l’assistant « State Machine Wizard » de la barre d’outils, comme nous

allons le faire :

Machines à Etats (FSM) avec VHDL Page 5

FSTM Génie Electrique & Télécommunications GSET3

L’assistant propose, soit de créer une nouvelle machine (notre option pour l’instant), soit d’en

modifier une existante ; il sera en effet toujours possible de modifier notre description, soit à l’aide

de l’assistant, soit par les outils classiques.

Préciser ensuite que l’on souhaite une machine synchrone, avec une réinitialisation active à l’état bas

(l’appui sur les boutons poussoirs de la carte DE2 provoque un NL0) et des sorties mémorisées dans

un registre.

Dans la fenêtre suivant, commencer par déclarer tous les états possibles de E1 à E8 (pour déclarer un

nouvel état, faire un double clic dans la case correspondante) :

Déclarer ensuite les ports d’entrée (par défaut « clock » et « reset » existent déjà), puis les transitions

permettant de passer d’un état à l’autre.

Règles de syntaxes :

- un bus de N bits en entrée ou en sortie peut être déclaré par « Bus[N-1 :0] » ;

- dans les transitions les opérations logiques s’écrivent :

o ~ pour le NON (Alt Gr 2) ;

Machines à Etats (FSM) avec VHDL Page 6

FSTM Génie Electrique & Télécommunications GSET3

o & pour le ET ;

o | pour le OU (Alt Gr 6) ;

o ^ pour le OU EXCLUSIF ;

- la valeur d’un bus est par défaut en décimal, mais peut s’écrire en binaire par « ‘b00111001 »

par exemple ou en hexadécimal par « ‘h3A » par exemple ;

- les conditions de transition peuvent être des comparaisons :

o == pour égal ;

o != pour différent ;

o > pour supérieur ;

o < pour inférieur ;

o >= pour supérieur ou égal ;

o <= pour inférieur ou égal.

Entrer ensuite les différentes transitions pour passer d’un état à l’autre (il est conseillé, vu la syntaxe

un peu lourde, d’utiliser le « copier coller ») :

L’étape suivante consiste à déclarer les sorties et préciser leurs valeurs pour chaque état :

Nous déclarerons une sortie destinée à commander les phases du moteur « PH[3 :0] » et une

permettant éventuellement de visualiser sur la carte DE2 l’état actif (sous réserve de l’afficher via un

décodeur sur un des afficheurs 7 segments par exemples, et sous réserve que l’horloge soit

suffisamment lente pour permettre une lecture).

La dernière page récapitule les états, les entrées et les sorties.

Le diagramme d’état résultant s’affiche alors (il est parfois nécessaire d’arranger un peu

l’agencement des états et transitions pour avoir un schéma lisible) :

Machines à Etats (FSM) avec VHDL Page 7

FSTM Génie Electrique & Télécommunications GSET3

On peut noter une flèche pointant vers l’état E1, indiquant que la remise à 0 de la machine rendra cet

état actif par défaut, car c’est le premier que nous avons déclaré. Si cette situation ne convient pas, il

est possible de modifier par l’onglet « States » de la zone « State Table » (la faire éventuellement

apparaître avec l’outil approprié de la barre d’outils).

Une fois le résultat satisfaisant, il est ensuite nécessaire de générer le fichier HDL pour programmer

le circuit, en précisant que l’on souhaite une description VHDL (Menu « Tools » puis la commande

« Generate HDL File…. ):

Le fichier VHDL s’ouvre alors ; il est parfois nécessaire de le vérifier. Dans notre cas par exemple,

l’action du « reset » a pour effet de mettre la machine dans l’état E1 comme convenu, mais

également de mettre tous les bits des bus PH[3 :0] et ETAT[3 :0] au NL0.

Il est possible de modifier le programme à volonté, pour changer la valeur des sorties lors de

l’initialisation par exemple :

BEGIN

Machines à Etats (FSM) avec VHDL Page 8

FSTM Génie Electrique & Télécommunications GSET3

IF (reset='0') THEN reg_fstate <= E1; reg_PH <= "0101"; reg_ETAT <= "0001";

ELSE reg_PH <= "0101"; reg_ETAT <= "0001"; CASE fstate IS

WHEN E1 =>

Il sera maintenant nécessaire d’effectuer les opérations habituelles sur ce type de projet (vérification,

simulation, génération de symbole, compilation etc…) pour finaliser le projet.

Remarque importante :

La machine d’état est incrémentée par une horloge « clock » qui doit être de fréquence faible

(quelques kHz maximum) pour commander un moteur pas à pas.

Si on utilise la carte DE2 avec ses horloges à 27 et 50 MHz, il sera nécessaire d’implanter un

diviseur

de fréquence.

Il est impératif, pour que le système reste synchrone et ne génère pas systématiquement des états

aléatoires, d’ajouter une entrée de validation d’horloge « C_EN » par exemple. Le diviseur fera

passer C_EN au NL1 tous les N coups de l’horloge principale (si on souhaite un pas par secondes

avec l’horloge à 50 MHz, alors N vaudra 50 millions).

Il suffit alors d’ajouter « & C_EN » à toutes les conditions de transition de notre machine d’état pour

obtenir un fonctionnement correct.

Autrement…

QUARTUS dispose d’un outil de développement graphique de description par machine à

états. Après le dessin, la machine à états est codée par QUARTUS en langage de haut niveau (VHDL

ou VERILOG).

La validation du comptage ou du décomptage des véhicules entrant dans le parking (le projet

support) nécessite un séquencement particulier avec une réaction sur front montant, le transfert d’une

impulsion de comptage ou décomptage si le nombre de place le permet. Aussi des états finis d’un

compteur particulier peut etre décrit par le développement graphique de description par machine à

états.

A- Résoudre un problème séquentiel par MAE dans QUARTUS II

On désire réaliser la logique d’une commande de moteur pas à pas avec la possibilité d’effectuer la

rotation en pas entier ou en demi-pas. Le moteur tournera uniquement dans le sens horaire.

Machines à Etats (FSM) avec VHDL Page 9

FSTM Génie Electrique & Télécommunications GSET3

Phases de commande des 4 bobines du moteur, le problème est similaire avec un moteur bipolaire.

Pas entier :

Demi-pas

Les chronogrammes ci-dessus font apparaitre les quatre phases du mode pas entier et les huit phases

du mode demi-pas.

B- Description par machine à état : commande de moteur pas à pas

Créer un projet Quartus appelé motpp_mae pour un FPGA EP2C35672C6.

Cliquer « File – New » ou puis sélectionner «State Machine File » Une fenêtre de l’éditeur graphique

de machine à état est créé.

Machines à Etats (FSM) avec VHDL Page 10

FSTM Génie Electrique & Télécommunications GSET3

En suivant l’architecture ci-dessus :

- Créer l’entrée DP qui permettra le choix entre pas entier et demi-pas (Symbole vert)

- Créer les quatre sorties pour les bobines (Symboles jaunes)

- Placer les 8 états de la machines (cercle rose) et les renommer (double clic), l’état P1 possède

par défaut une flèche sur la gauche, c’est l’état après la remise à zéro de la machine.

- Placer les liens entre les états (icône lacet), certaines transitions sont conditionnelles, double-

clic sur le lien permet d’éditer les conditions.

ex :

DP : la transistion est valide pour DP = 1

~DP : la transistion est valide pour DP = 0

OPERATEURS

= = : Est égale Pour créer un bus (ex :BDT) en entrée ou en

! = : Est diffèrent sortie :

<= : Est inférieur ou égal BDT[7:0] (donc ici 8bits).

< : Est strictement inférieur

>= : Est supérieur ou égal

> : Est strictement supérieur

& : Et logique

| : Ou logique

^ : Ou exclusif

~& : NAND

~| : NOR

~^ : NON Ou exclusif Il est alors possible de créer des conditions de

~ : NON transition sur ce bus.

Ex : BDT==128 ou BDT>= ‘b010011100

Indiquer l’état des sorties pour chaque état de la machine,

conformément aux chronogrammes ci-dessus.

Double clic sur l’état puis onglet « action ».

La machine à états est terminée, créer le fichier VHDL

correspondant, en cliquant sur Generate HDL File du menu

Tools.

Le fichier généré sera utilisé lors de la simulation, dans le cas

d’un

projet ayant de multiples sources il est nécessaire de faire

apparaitre ce fichier dans le projet.

Dans le project Navigator, onglet Files, Clic-Droit sur Files

puis ajouter le fichier motpp.vhd.

Il est indispensable de vérifier la description VHDL, des

Machines à Etats (FSM) avec VHDL Page 11

FSTM Génie Electrique & Télécommunications GSET3

connaissances minimum du langage sont donc nécessaires.

L’analyse d’une machine à état est relativement simple,

identifier dans le programme ci-dessous :

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY motpp_mae IS

PORT (

reset : IN STD_LOGIC := '0';

clock : IN STD_LOGIC;

DP : IN STD_LOGIC := '0';

BA1 : OUT STD_LOGIC;

BA2 : OUT STD_LOGIC;

BB1 : OUT STD_LOGIC;

BB2 : OUT STD_LOGIC

);

END motpp_mae;

ARCHITECTURE BEHAVIOR OF motpp_mae IS

TYPE type_fstate IS (P1,P2,P3,P4,P5,P6,P7,P8);

SIGNAL fstate : type_fstate;

SIGNAL reg_fstate : type_fstate;

BEGIN

PROCESS (clock,reg_fstate)

BEGIN

IF (clock='1' AND clock'event) THEN

fstate <= reg_fstate;

END IF;

END PROCESS;

PROCESS (fstate,reset,DP)

BEGIN

IF (reset='0') THEN reg_fstate <= P1; BA1 <= '0'; BA2 <= '0'; BB1 <= '0'; BB2 <= '0';

ELSE BA1 <= '0'; BA2 <= '0'; BB1 <= '0'; BB2 <= '0';

CASE fstate IS

WHEN P1 => IF ((DP = '1')) THEN reg_fstate <= P2;

ELSIF (NOT((DP = '1'))) THEN reg_fstate <= P3;

-- Inserting 'else' block to prevent latch inference

ELSE reg_fstate <= P1;

END IF;

BA1 <= '0'; BB1 <= '0'; BB2 <= '1'; BA2 <= '0';

WHEN P2 => reg_fstate <= P3; BA1 <= '1'; BB1 <= '0'; BB2 <= '1'; BA2 <= '0';

WHEN P3 => IF ((DP = '1')) THEN reg_fstate <= P4;

ELSIF (NOT((DP = '1'))) THEN reg_fstate <= P5;

-- Inserting 'else' block to prevent latch inference

ELSE reg_fstate <= P3;

END IF;

BA1 <= '1'; BB1 <= '0'; BB2 <= '0'; BA2 <= '0';

WHEN P4 => reg_fstate <= P5; BA1 <= '1'; BB1 <= '0'; BB2 <= '0'; BA2 <= '1';

WHEN P5 => IF ((DP = '1')) THEN reg_fstate <= P6;

ELSIF (NOT((DP = '1'))) THEN reg_fstate <= P7;

-- Inserting 'else' block to prevent latch inference

ELSE reg_fstate <= P5;

END IF;

BA1 <= '0'; BB1 <= '0'; BB2 <= '0'; BA2 <= '1';

WHEN P6 => reg_fstate <= P7; BA1 <= '0'; BB1 <= '1'; BB2 <= '0'; BA2 <= '1';

WHEN P7 => IF ((DP = '1')) THEN reg_fstate <= P8;

ELSIF (NOT((DP = '1'))) THEN reg_fstate <= P1;

-- Inserting 'else' block to prevent latch inference

ELSE reg_fstate <= P7;

END IF;

BA1 <= '0'; BB1 <= '1'; BB2 <= '0'; BA2 <= '0';

WHEN P8 => reg_fstate <= P1; BA1 <= '0'; BB1 <= '1'; BB2 <= '1'; BA2 <= '0';

WHEN OTHERS => BA1 <= 'X'; BA2 <= 'X'; BB1 <= 'X'; BB2 <= 'X';

report "Reach undefined state";

END CASE;

END IF;

END PROCESS;

END BEHAVIOR;

Machines à Etats (FSM) avec VHDL Page 12

FSTM Génie Electrique & Télécommunications GSET3

C- Structure logique de la machine à état.

Tools – Netlist Viewvers –RTL Viewer affiche le schéma de la structure fonctionnelle

(comportementale ou behavior).

Un double clic sur la machine à état (fstate) permet de retrouver la description initiale.

D- Structure synthétisée dans le FPGA de la machine à état.

Tools – Netlist Viewvers –Technologie Map Viewer affiche le schéma de la structure synthétisée.

Machines à Etats (FSM) avec VHDL Page 13

Das könnte Ihnen auch gefallen

- Le Moniteur - Routes Et Voiries Contruction Et MaintenanceDokument34 SeitenLe Moniteur - Routes Et Voiries Contruction Et MaintenancejimmydisereNoch keine Bewertungen

- Chapitre 2 Theorie Des Langages Et AutomatesDokument8 SeitenChapitre 2 Theorie Des Langages Et AutomatesMichelle Willis100% (1)

- Corrigé Partiel VHDL FPGA M1 ELN SE 2020Dokument6 SeitenCorrigé Partiel VHDL FPGA M1 ELN SE 2020yasmine hmn100% (1)

- Devoir VHDL 2Dokument34 SeitenDevoir VHDL 2Simi NeNoch keine Bewertungen

- Grille Intelligente: Échange d'électricité et d'informations entre les maisons et les centrales électriquesVon EverandGrille Intelligente: Échange d'électricité et d'informations entre les maisons et les centrales électriquesNoch keine Bewertungen

- VhdlexDokument10 SeitenVhdlexSoukaina NJNoch keine Bewertungen

- École Polytechnique de Montréal Page 1/12 Département de Génie Informatique Et Génie LogicielDokument383 SeitenÉcole Polytechnique de Montréal Page 1/12 Département de Génie Informatique Et Génie LogicielMahmoud CherfaouiNoch keine Bewertungen

- Electricité Bâtiment - FicheDokument1 SeiteElectricité Bâtiment - Fiche4geniecivilNoch keine Bewertungen

- PerçageDokument19 SeitenPerçagemliki mohamedNoch keine Bewertungen

- Dimensionnement Des Voiles en BA PDFDokument29 SeitenDimensionnement Des Voiles en BA PDFBen Hanane100% (1)

- Perspective ConiqueDokument60 SeitenPerspective ConiquezxhmnzaoNoch keine Bewertungen

- TD Fpga Cs 2015Dokument5 SeitenTD Fpga Cs 2015hakim100% (1)

- 1C02Dokument3 Seiten1C02Makrem CherifNoch keine Bewertungen

- RtosDokument12 SeitenRtosPer PersoNoch keine Bewertungen

- Serie TD4Dokument5 SeitenSerie TD4Sarah NourNoch keine Bewertungen

- Exercices VHDLDokument3 SeitenExercices VHDLKamel Sahraoui100% (1)

- TD1: Synthèse VHDL: Exercice 1Dokument2 SeitenTD1: Synthèse VHDL: Exercice 1Mohamed Aziz Ben RomdhaneNoch keine Bewertungen

- Examen VHDL +correction 1ere Session 2009Dokument12 SeitenExamen VHDL +correction 1ere Session 2009Walid LELLOUCHINoch keine Bewertungen

- Serie TD5Dokument9 SeitenSerie TD5Sarah NourNoch keine Bewertungen

- Exam 2017Dokument8 SeitenExam 2017Mohammed Chamseddine KadriNoch keine Bewertungen

- RapportDokument4 SeitenRapportDenner PaganotiNoch keine Bewertungen

- Eléments-De-Correction Eval Type CodesignDokument4 SeitenEléments-De-Correction Eval Type CodesignhurnelNoch keine Bewertungen

- Exam2011 2012Dokument6 SeitenExam2011 2012محمد الأمير الحازميNoch keine Bewertungen

- Examen VHDL +correction 1ere Session 2008Dokument5 SeitenExamen VHDL +correction 1ere Session 2008nesrine ninaNoch keine Bewertungen

- Examen Final CLPDokument4 SeitenExamen Final CLPtemp.kahajiNoch keine Bewertungen

- TD 01 FPGA CorrectionDokument2 SeitenTD 01 FPGA CorrectionAmal BarhoumNoch keine Bewertungen

- TP1 VHDLDokument9 SeitenTP1 VHDLID AbdelNoch keine Bewertungen

- Compte-Rendu FinalDokument10 SeitenCompte-Rendu FinalDhafer MezghaniNoch keine Bewertungen

- VhdlexDokument10 SeitenVhdlexRiyadh Ben AbdallahNoch keine Bewertungen

- Serie TD1Dokument5 SeitenSerie TD1Sarah NourNoch keine Bewertungen

- Corigé Type Eln.-num.-Av.-fpgAVHDL M1-InST Électronique NumériqueDokument5 SeitenCorigé Type Eln.-num.-Av.-fpgAVHDL M1-InST Électronique Numériques240% (1)

- TD 2021Dokument4 SeitenTD 2021elhaoudar.nassima100% (1)

- Compte Rendu Assembleur 1Dokument3 SeitenCompte Rendu Assembleur 1El Oufir El MehdiNoch keine Bewertungen

- DS VHDL Nov 2015 CORRDokument5 SeitenDS VHDL Nov 2015 CORRHadi Ben SaïdNoch keine Bewertungen

- Serie TD3Dokument2 SeitenSerie TD3Lahcene ZietNoch keine Bewertungen

- TP Fpga Cyclone2Dokument3 SeitenTP Fpga Cyclone2red-allNoch keine Bewertungen

- TP Sin 2018 2017 PDFDokument21 SeitenTP Sin 2018 2017 PDFyapNoch keine Bewertungen

- Serie1 TD STR 2021 2022Dokument15 SeitenSerie1 TD STR 2021 2022Abdel MAJID ED-DAHBINoch keine Bewertungen

- Cours de Systèmes EmbarquésDokument12 SeitenCours de Systèmes EmbarquésAristide De Mantsala IfiakeNoch keine Bewertungen

- Fascicule de TP FpgaDokument32 SeitenFascicule de TP FpgaHichem HamdiNoch keine Bewertungen

- Chapitre 3 Architecture Et Composant Des IoTDokument24 SeitenChapitre 3 Architecture Et Composant Des IoTSarah JouiniNoch keine Bewertungen

- TP 3Dokument8 SeitenTP 3DixNoch keine Bewertungen

- Cours VHDLDokument62 SeitenCours VHDLBrice Albin Fotso GhomdimNoch keine Bewertungen

- TD3: Synthèse VHDL: Exercice 1Dokument5 SeitenTD3: Synthèse VHDL: Exercice 1Mohamed Aziz Ben RomdhaneNoch keine Bewertungen

- 02 Debut Structurelle ComportementaleDokument5 Seiten02 Debut Structurelle ComportementaleFabrice FotsoNoch keine Bewertungen

- tp1 Ing 2015 PDFDokument3 Seitentp1 Ing 2015 PDFyapNoch keine Bewertungen

- Cours Sys Temps ReelDokument13 SeitenCours Sys Temps ReelghwaidiakNoch keine Bewertungen

- Correction TD 4 1Dokument17 SeitenCorrection TD 4 1Kouraichi Zeineb100% (1)

- TP Asservissement Et RégulationDokument2 SeitenTP Asservissement Et RégulationM NaimNoch keine Bewertungen

- Cours VHDL 10 Partie8 Test BenchesDokument14 SeitenCours VHDL 10 Partie8 Test BenchesSalahe LaouarNoch keine Bewertungen

- 7segments VHDLDokument5 Seiten7segments VHDLSoufiane BoulachgourNoch keine Bewertungen

- Correction VHDLDokument5 SeitenCorrection VHDLReal MadridNoch keine Bewertungen

- Compte Rendu Du TP PIC16F877 Par AIMANE BOURASSDokument13 SeitenCompte Rendu Du TP PIC16F877 Par AIMANE BOURASSAyman Brs100% (1)

- Cours System On ChipDokument55 SeitenCours System On ChipBehij ben amorNoch keine Bewertungen

- TD2 VHDL Mars 2019Dokument2 SeitenTD2 VHDL Mars 2019Belkhiri MohammedNoch keine Bewertungen

- Exercice Feux de CarrefourDokument2 SeitenExercice Feux de CarrefourOussama SimourNoch keine Bewertungen

- TP STR n1Dokument1 SeiteTP STR n1Mouh Mab67% (3)

- Chapitre 2: Le Microcontrôleur Pic 18F45K22.: 1 PrésentationDokument11 SeitenChapitre 2: Le Microcontrôleur Pic 18F45K22.: 1 PrésentationAbderrahman Amelougou100% (1)

- Chap6 VHDLDokument34 SeitenChap6 VHDLMahi M SalahNoch keine Bewertungen

- TP 1Dokument2 SeitenTP 1Khaled LahianiNoch keine Bewertungen

- 3-I2C Exos CorrDokument2 Seiten3-I2C Exos CorrFatiha HAMDINoch keine Bewertungen

- tp1 Reseaux Des Capteurs-ConvertiDokument5 Seitentp1 Reseaux Des Capteurs-ConvertiRaed SassiNoch keine Bewertungen

- TD N 4 (Supplemetaire) FpgaDokument2 SeitenTD N 4 (Supplemetaire) FpgaLE BARONNoch keine Bewertungen

- Le Langage VHDL ELKARIDokument112 SeitenLe Langage VHDL ELKARIAhmed DoghmiNoch keine Bewertungen

- Série - N3 - LFI - 2015 - ModifieDokument2 SeitenSérie - N3 - LFI - 2015 - ModifieBehij ben amorNoch keine Bewertungen

- Rtos Poly TP Sate 2016 PDFDokument79 SeitenRtos Poly TP Sate 2016 PDFEylul MoodNoch keine Bewertungen

- M441 ACE Catalogue Pricipale 2018 FRDokument260 SeitenM441 ACE Catalogue Pricipale 2018 FRJihen BoukadidaNoch keine Bewertungen

- CH IV Pompecentrifuge23Dokument64 SeitenCH IV Pompecentrifuge23Rouaa khaledNoch keine Bewertungen

- ECV10C Ic 10 FR ManualDokument110 SeitenECV10C Ic 10 FR ManualPhilippe Fabro-joaoNoch keine Bewertungen

- Emploi Du Temps Fi 1ere Annee 2017 2018Dokument5 SeitenEmploi Du Temps Fi 1ere Annee 2017 2018Mohcine RouessiNoch keine Bewertungen

- Exercice Cor8rigé Sur La Théorème de ThéveninDokument7 SeitenExercice Cor8rigé Sur La Théorème de ThéveninTalel Missaoui100% (1)

- Cours Asservissement Regulation PDFDokument7 SeitenCours Asservissement Regulation PDFWassim Djennane100% (1)

- CHAPITRE3APPLICATIONDokument24 SeitenCHAPITRE3APPLICATIONMounir LiazidiNoch keine Bewertungen

- Campingcar-Infos Areas EspanhaDokument31 SeitenCampingcar-Infos Areas EspanhasusalexandrNoch keine Bewertungen

- Examen Matériaux Métalliques 15 16Dokument3 SeitenExamen Matériaux Métalliques 15 16zyad l-fNoch keine Bewertungen

- En 12390-4Dokument16 SeitenEn 12390-4MOHAMMADNoch keine Bewertungen

- Pensamiento SistemicoDokument4 SeitenPensamiento SistemicofcomarNoch keine Bewertungen

- Saffire PRO 24 DSP - Mode D'emploiDokument35 SeitenSaffire PRO 24 DSP - Mode D'emploiGeorges GranvilleNoch keine Bewertungen

- 12336877Dokument200 Seiten12336877Tarik AzziNoch keine Bewertungen

- Catalogue Proviteq 2Dokument144 SeitenCatalogue Proviteq 2Sylvestre OlanloNoch keine Bewertungen

- BT 8602Dokument16 SeitenBT 8602etskacedNoch keine Bewertungen

- Calcul Pied de PoteauDokument10 SeitenCalcul Pied de Poteautbn3320Noch keine Bewertungen

- Silent Flow IngersolDokument40 SeitenSilent Flow IngersoltangouzeNoch keine Bewertungen

- B&G Catalogue 2011 FRDokument35 SeitenB&G Catalogue 2011 FRClaude BouillotNoch keine Bewertungen

- Integra HP Tech Data Sheet FR 2023Dokument14 SeitenIntegra HP Tech Data Sheet FR 2023alt.ha-dom478q9Noch keine Bewertungen

- DS Electronique 3GE Iset Nabeul DEC2005 PDFDokument2 SeitenDS Electronique 3GE Iset Nabeul DEC2005 PDFGhaith HamdiNoch keine Bewertungen

- ExamCorrigVF PDFDokument40 SeitenExamCorrigVF PDFJames XgunNoch keine Bewertungen

- Enoncé Mini Projet POODokument2 SeitenEnoncé Mini Projet POOyassine gabsi100% (1)