Beruflich Dokumente

Kultur Dokumente

Common Drain Stage (Source Follower) : Jayant Charthad Stanford University Jayantc@stanford - Edu

Hochgeladen von

Elizabeth ColeOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Common Drain Stage (Source Follower) : Jayant Charthad Stanford University Jayantc@stanford - Edu

Hochgeladen von

Elizabeth ColeCopyright:

Verfügbare Formate

Lecture 11

Common Drain Stage

(Source Follower)

Jayant Charthad

Stanford University

jayantc@stanford.edu

A. Arbabian, R. Dutton, B. Murmann EE114/214A L11- 1

Common Drain Stage

VDD

Cgd+Cgb

vi

Vi

+

vgs Cgs ro gmvgs -gmbvo

Vo -

vo

IB RL CL RL Csb+CL

Cgd+Cgb

vi

+

vgs Cgs ro gmvgs -gmbvo

-

vo

Cgd+Cgb

RL Csb+CL

gmbvo

A. Arbabian, R. Dutton, B. Murmann EE114/214A L11- 2

CD Voltage Transfer (1)

æ 1 ö

vi

vo çç sCLtot + sCgs + ÷÷ - vi sCgs - g m (vi - vo ) = 0

è RLtot ø

+

vgs Cgs gmvgs vo g m + sCgs

=

- vi g + sC + sC + 1

Cgd+Cgb vo m gs Ltot

RLtot

CLtot RLtot

sCgs

1+

vo gm gm

= ×

vi g + 1 s (C gs + C Ltot )

m 1 +

1 RLtot 1

C Ltot = C L + Csb RLtot = RL || || ro gm +

g mb RLtot

A. Arbabian, R. Dutton, B. Murmann EE114/214A L11- 3

Low Frequency Gain

gm 1

av 0 = RLtot = RL || || ro

1 g mb

gm +

RLtot

• Interesting cases

– RL®¥, ro®¥, gmb=0 av 0 = 1

• PMOS, source tied to body, ideal current source

VDD VDD

gm

– RL®¥, ro®¥, gmb¹0 Vi av 0 =

Vo RLtot=1/gmb g m + g mb

Vi • NMOS, ideal current source) Vo

CL (typically @ 0.8)

Yin IB RL CL

gm

– ro®¥, gmb=0, RL finite av 0 =

1

• PMOS, source tied to body, load resistor gm +

RL

A. Arbabian, R. Dutton, B. Murmann EE114/214A L11- 4

High Frequency Gain

s 1

1- g gm +

v

av (s ) = o = av 0 × z z=- m RLtot

vi s C gs p=-

1- C gs + C Ltot

p

• Three scenarios

|z|<|p| |z|>|p| |z|=|p|

|av(s)| |av(s)| |av(s)|

f f f

(infinite bandwidth !?)

A. Arbabian, R. Dutton, B. Murmann EE114/214A L11- 5

CD Input Impedance

Hint*:

I=Cgs(vi-vo) • By inspection*

vi

Yin = s (C gd + C gb ) + sC gs (1 - av ( s ))

Yin +

vgs Cgs gmvgs

- • Gain term av(s) is real and close to

Cgd+Cgb vo

unity up to fairly high frequencies

CLtot RLtot

• Hence, up to moderate

frequencies, we see a capacitor

looking into the input

– A fairly small one, Cgd + Cgb,

PS--Insight from Miller Theorem, plus a fraction of Cgs

p. 9 Lec#8 is consistent

*Really, try and be brave. This is important to having insight as a designer

A. Arbabian, R. Dutton, B. Murmann EE114/214A L11- 6

PMOS Stage with Body-Source Tie

• Gate-body capacitance is in

VDD parallel with Cgs

• gmb generator inactive

– Low frequency gain very

Vo

close to unity

Vi

CL • Very small input capacitance

Yin

Yin = sCgd + s(C gs + C gb )(1 - av ( s ))

Yin @ sCgd

A. Arbabian, R. Dutton, B. Murmann EE114/214A L11- 7

CD Output Impedance (1)

• Let's first look at an analytically

simple case

– Input driven by ideal voltage

+

source

vgs Cgs gmvgs

-

• By inspection*

vo

Cgd+Cgb

1 1

Zout Z out =

g m + g mb s(C gs + Csb )

Csb 1/gmb

• Low output impedance

– Resistive up to very high

frequencies

*Really, try and be brave. This is important to having insight as a designer

A. Arbabian, R. Dutton, B. Murmann EE114/214A L11- 8

CD Output Impedance (2)

• Now include finite source resistance

vg

Ri

Cgs gm(vg-vo)

Zx Zout

Cgd+Cgb vo

ix Csb 1/gmb

v ix = (vo - vg )(g m + sCgs ) vg Ri

Zx = o =

ix æ vg ö 1

÷÷(g m + sCgs )

vo + Ri

= vo çç1 -

è vo ø sC gs

A. Arbabian, R. Dutton, B. Murmann EE114/214A L11- 9

CD Output Impedance (3)

1 (1 + sRi C gs )

Zx @

gm æ sC gs ö

çç1 + ÷÷

è g m ø

• Two interesting cases

Ri < 1/gm Ri > 1/gm

|Zx(s)| |Zx(s)|

1/gm 1/gm

f f

Inductive behavior!

A. Arbabian, R. Dutton, B. Murmann EE114/214A L11- 10

Equivalent Circuit for Ri > 1/gm

Zx Zout

1

R1

R1 || R2 =

gm

R2 Csb 1/gmb R2 = Ri

L Ri2C gs

L=

g m Ri - 1

• This circuit is prone to ringing!

– L forms an LC tank with any capacitance at the output

A. Arbabian, R. Dutton, B. Murmann EE114/214A L11- 11

Inclusion of Parasitic Input Capacitance*

• What happens to this result if we don’t neglect Ci=Cgd+Cgb?

*Hint: on p. 10 1 (1 + sRi {C gs + Ci })

replace Ri with: Zx =

gm æ sC gs ö

Ri çç1 + ÷÷(1 + sRi Ci )

Zi = è g m ø

Ri + sC i Ri

1 gm 1 1 1 g

< < < < m

Ri {Cgs + Ci } Cgs Ri Ci Ri {Cgs + Ci } Ri Ci Cgs

|Zx(s)| |Zx(s)|

1/gm 1/gm

f f

A. Arbabian, R. Dutton, B. Murmann EE114/214A L11- 12

Application 1: Level Shifter

VDD

Vi

VGS=Vt+Vov @ const.

Vo

IB

• Output quiescent point is roughly Vt+Vov lower than input

quiescent point

A. Arbabian, R. Dutton, B. Murmann EE114/214A L11- 13

Application 2: Buffer

VDD

Rbig

Vo

Vi

IB Rsmall

• Low frequency voltage gain of the above circuit is ~gmRbig

– Would be ~gm(Rsmall||Rbig) without CD buffer stage

A. Arbabian, R. Dutton, B. Murmann EE114/214A L11- 14

Issues

• Several sources of nonlinearity

– Vt is a function of Vo (NMOS, without S to B connection)

– ID and thus Vov changes with Vo

• Gets worse with small RL

• Reduced input and output voltage swing

– Consider e.g. VDD=1V, Vt=0.3V, VOV=0.2V

• CD buffer stage consumes 50% of supply headroom!

– In low VDD applications that require large output swing, using

a CD buffer is often not possible

– CD buffers are more frequently used when the required

swing is small

• E.g. pre-amplifiers or LNAs that turn µV into mV at the output

A. Arbabian, R. Dutton, B. Murmann EE114/214A L11- 15

Application 3: Load Device

VDD • Advantages compared to resistor load

Added term vs.

previous PS – "Ratiometric"

examples

M2 • Gain depends on ratio of similar

1/(gm2+gmb2)

parameters

• Reduced process and

Vo temperature variations

Vi – First order cancellation of

M1 nonlinearities

• Disadvantage

– Reduced swing

g m1

av 0 =

g m 2 + g mb 2

A. Arbabian, R. Dutton, B. Murmann EE114/214A L11- 16

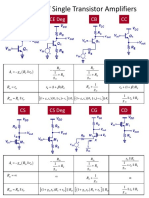

Summary – Elementary Transistor Stages

• Common source

– VCCS, makes a good voltage amplifier when terminated with

a high impedance

• Common gate

– Typically low input impedance, high output impedance

– Can be used to improve the intrinsic voltage gain of a

common source stage

• "Cascode" stage

• Common drain

– Typically high input impedance, low output impedance

– Great for shifting the DC operating point of signals

– Useful as a voltage buffer when swing and nonlinearity are

not an issue

A. Arbabian, R. Dutton, B. Murmann EE114/214A L11- 17

Das könnte Ihnen auch gefallen

- BJT Conf Notes 13 2Dokument3 SeitenBJT Conf Notes 13 2rk433Noch keine Bewertungen

- Analysis and Design of Analog Integrated Circuits Differential AmplifiersDokument17 SeitenAnalysis and Design of Analog Integrated Circuits Differential AmplifiersAndrea FasatoNoch keine Bewertungen

- Lecture22-High Frequency ResponseDokument8 SeitenLecture22-High Frequency ResponseSHAIK MUSTHAFANoch keine Bewertungen

- Chap 6Dokument28 SeitenChap 6GagneNoch keine Bewertungen

- Lec 21Dokument18 SeitenLec 21Edwin HapsahNoch keine Bewertungen

- RF Small Signal Amplifier DesignDokument58 SeitenRF Small Signal Amplifier DesignjaoudeNoch keine Bewertungen

- Amplifiers 21Dokument57 SeitenAmplifiers 21api-3750190Noch keine Bewertungen

- WH ITd Ti Fdlza IXmmDokument36 SeitenWH ITd Ti Fdlza IXmmSarinNoch keine Bewertungen

- 60Dokument1 Seite60ragupaNoch keine Bewertungen

- 12, Tut-4Dokument4 Seiten12, Tut-4Jatin SharmaNoch keine Bewertungen

- ZLB Appendix PDFDokument28 SeitenZLB Appendix PDFLord Vilis LMNoch keine Bewertungen

- Lecture23-Amplifier Frequency Response PDFDokument12 SeitenLecture23-Amplifier Frequency Response PDFMuhammad Mubashar AwaisiNoch keine Bewertungen

- chapter 7Dokument22 Seitenchapter 7louischen1228Noch keine Bewertungen

- Quick Reference: Amplifier Equations: 2.1 Common-Source Input ResistanceDokument9 SeitenQuick Reference: Amplifier Equations: 2.1 Common-Source Input ResistanceMax MarkNoch keine Bewertungen

- Michael H. Perrott (C) 2002: Open Circuit Time Constant Calculations 6.301 - Spring 2002Dokument2 SeitenMichael H. Perrott (C) 2002: Open Circuit Time Constant Calculations 6.301 - Spring 2002Andrea FasatoNoch keine Bewertungen

- Compensation Design From LinearDokument39 SeitenCompensation Design From LinearTrung Nguyen ChiNoch keine Bewertungen

- Transistor Amplifier SummaryDokument1 SeiteTransistor Amplifier SummaryJhonNoch keine Bewertungen

- Transistor Amplifiers Lecture: Common-Drain and Common-Gate Amplifier StagesDokument17 SeitenTransistor Amplifiers Lecture: Common-Drain and Common-Gate Amplifier StagesharbikNoch keine Bewertungen

- Final 2016 AnswerDokument3 SeitenFinal 2016 AnswerLLANoch keine Bewertungen

- 14 Cascode StagesDokument39 Seiten14 Cascode Stages陳浚維Noch keine Bewertungen

- Dr. Abhijit R. Asati Abhijit - Asati@bits-Pilani - Ac.inDokument21 SeitenDr. Abhijit R. Asati Abhijit - Asati@bits-Pilani - Ac.inraghavbhatiaNoch keine Bewertungen

- G U C C + + + - U - : M Gs Ul TDokument5 SeitenG U C C + + + - U - : M Gs Ul ThsrfeasdgNoch keine Bewertungen

- ENG 571 - Lecture - Notes - Week - 7 - Part - 1Dokument8 SeitenENG 571 - Lecture - Notes - Week - 7 - Part - 1Vinod KumarNoch keine Bewertungen

- Slide06 AmplifierII2022Dokument43 SeitenSlide06 AmplifierII2022yackinNoch keine Bewertungen

- MIT6 012S09 Lec23Dokument12 SeitenMIT6 012S09 Lec23tinashembofana84Noch keine Bewertungen

- Analisa Sistem TenagaDokument67 SeitenAnalisa Sistem TenagaMuhammad Irwan R.Noch keine Bewertungen

- Part 2 CircuitsDokument4 SeitenPart 2 CircuitskhashyapNoch keine Bewertungen

- Lecture 4 - Bilinear TF - 2Dokument12 SeitenLecture 4 - Bilinear TF - 2Nathan KingoriNoch keine Bewertungen

- MalysiaICRETS (2015)Dokument6 SeitenMalysiaICRETS (2015)Dr. D. V. KamathNoch keine Bewertungen

- Active ComponentsDokument55 SeitenActive ComponentsdharmNoch keine Bewertungen

- 04 - Comparators and Offset Cancellation TechniquesDokument68 Seiten04 - Comparators and Offset Cancellation Techniquesjosh100% (2)

- Module IIIDokument27 SeitenModule IIIKinoti Mugiira NtundaNoch keine Bewertungen

- Final 2013 AnswerDokument2 SeitenFinal 2013 AnswerLLANoch keine Bewertungen

- Lec17 Cascade AmplifiersDokument7 SeitenLec17 Cascade AmplifiersJai KumarNoch keine Bewertungen

- EE105 - How to Increase Voltage Gain in Microelectronic DevicesDokument7 SeitenEE105 - How to Increase Voltage Gain in Microelectronic DevicesVarunKaradesaiNoch keine Bewertungen

- Y Y RF M R D F Q R D F Q R D RR Ar G R D F Q R D F Q R D RR Ar G D R F M F QRF QR RR Ar G D V R VM QQ B R Q Rar R RR R RRDokument4 SeitenY Y RF M R D F Q R D F Q R D RR Ar G R D F Q R D F Q R D RR Ar G D R F M F QRF QR RR Ar G D V R VM QQ B R Q Rar R RR R RRmn4webNoch keine Bewertungen

- Transmission Lines With Reactive TerminationsDokument6 SeitenTransmission Lines With Reactive TerminationsTauqueer AlamNoch keine Bewertungen

- Frequency Response of Transistor Amplifiers: Simplest Case: CE Short-Circuit Current Gain A (J As A Function of FrequencyDokument12 SeitenFrequency Response of Transistor Amplifiers: Simplest Case: CE Short-Circuit Current Gain A (J As A Function of Frequencysunilkmch505682Noch keine Bewertungen

- MOS amplifier gain formulasDokument38 SeitenMOS amplifier gain formulasraghavbhatiaNoch keine Bewertungen

- Servo AlgorithmDokument20 SeitenServo AlgorithmhuseyintopcuNoch keine Bewertungen

- 12 - L-16 (NKD) (Pe) ( (Ee) Nptel)Dokument1 Seite12 - L-16 (NKD) (Pe) ( (Ee) Nptel)CharkNoch keine Bewertungen

- Cationic PolymerizationDokument14 SeitenCationic PolymerizationHikmət ŞabanNoch keine Bewertungen

- Modelling and Control of Multiterminal HVDC Transmission Systems For Large Offshore Wind FarmsDokument37 SeitenModelling and Control of Multiterminal HVDC Transmission Systems For Large Offshore Wind FarmsRaimundo LimaNoch keine Bewertungen

- Case No., Edge Restraints Boundary Values Special CasesDokument4 SeitenCase No., Edge Restraints Boundary Values Special Casesmn4webNoch keine Bewertungen

- Optimal Non-Coherent Demodulation TechniquesDokument5 SeitenOptimal Non-Coherent Demodulation TechniquesNaser ElmisbahNoch keine Bewertungen

- Module - 4-4 - Multi-Stage AmplifiersDokument24 SeitenModule - 4-4 - Multi-Stage AmplifiersshoukatawaisaliNoch keine Bewertungen

- Trigonometrie Teorie M1Dokument2 SeitenTrigonometrie Teorie M1Șerban FilipNoch keine Bewertungen

- Trigonometrie Teorie M1Dokument2 SeitenTrigonometrie Teorie M1Șerban FilipNoch keine Bewertungen

- Mining Example LagrangianDokument7 SeitenMining Example LagrangianMax ShervingtonNoch keine Bewertungen

- CONTROL SYSTEM FORMULA SHEETDokument9 SeitenCONTROL SYSTEM FORMULA SHEETMukesh KumarNoch keine Bewertungen

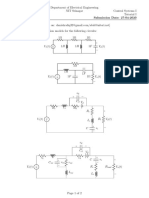

- B. Tech Control Systems I Tutorial I Spring 2019Dokument2 SeitenB. Tech Control Systems I Tutorial I Spring 2019ApoorvNoch keine Bewertungen

- Simulation and Implementation of Servo Motor Control With Sliding Mode Control (SMC) Using Matlab and LabviewDokument30 SeitenSimulation and Implementation of Servo Motor Control With Sliding Mode Control (SMC) Using Matlab and Labviewmjohn87Noch keine Bewertungen

- Lect13 PDFDokument9 SeitenLect13 PDFSHAIK MUSTHAFANoch keine Bewertungen

- 0.1 BJT Transistor at High Frequency: G V R R VDokument4 Seiten0.1 BJT Transistor at High Frequency: G V R R VSimone MolinaroNoch keine Bewertungen

- 10 High Frequency Transistor ModelsDokument38 Seiten10 High Frequency Transistor Models吳心Noch keine Bewertungen

- Buck Converter Circuit AnalysisDokument5 SeitenBuck Converter Circuit AnalysisselageaalinNoch keine Bewertungen

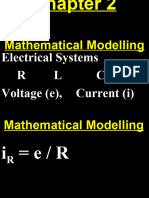

- Chapter 2 ConsysDokument188 SeitenChapter 2 Consysbilbotarly69Noch keine Bewertungen

- Solution Manual for an Introduction to Equilibrium ThermodynamicsVon EverandSolution Manual for an Introduction to Equilibrium ThermodynamicsNoch keine Bewertungen

- Answers to Selected Problems in Multivariable Calculus with Linear Algebra and SeriesVon EverandAnswers to Selected Problems in Multivariable Calculus with Linear Algebra and SeriesBewertung: 1.5 von 5 Sternen1.5/5 (2)

- Backgate Effect Common Gate Stage: Jayant Charthad Stanford University Jayantc@stanfordDokument26 SeitenBackgate Effect Common Gate Stage: Jayant Charthad Stanford University Jayantc@stanfordElizabeth ColeNoch keine Bewertungen

- Operating Point Calculations A Look at The Inner Workings of SpiceDokument18 SeitenOperating Point Calculations A Look at The Inner Workings of SpiceElizabeth ColeNoch keine Bewertungen

- 05 Gain and Ro PDFDokument27 Seiten05 Gain and Ro PDFElizabeth ColeNoch keine Bewertungen

- 03 Cs Small SigDokument24 Seiten03 Cs Small SigElizabeth ColeNoch keine Bewertungen

- ScribdDokument1 SeiteScribdElizabeth ColeNoch keine Bewertungen

- North South University: Lab 3: Loading Effect of Voltage Divider CircuitDokument3 SeitenNorth South University: Lab 3: Loading Effect of Voltage Divider CircuitNazmul Hasan 1911742042Noch keine Bewertungen

- Alinco DX 70 Service ID5792Dokument116 SeitenAlinco DX 70 Service ID5792Václav LojíkNoch keine Bewertungen

- 3.2 Active Filters: I1 gV2 - I2 gV1 V2 V1Dokument42 Seiten3.2 Active Filters: I1 gV2 - I2 gV1 V2 V1Sasith WickramasingheNoch keine Bewertungen

- MODULE 4 - Flip Flop & RegistersDokument27 SeitenMODULE 4 - Flip Flop & RegistersChaitanya J S ReddyNoch keine Bewertungen

- Hourly Chime Fun GenDokument1 SeiteHourly Chime Fun GenKaranpal Singh100% (1)

- Lab ManualDokument57 SeitenLab ManualSwapnil GourkarNoch keine Bewertungen

- Maharashtra State Board of Technical Education, MumbaiDokument18 SeitenMaharashtra State Board of Technical Education, MumbaiŠhùbhãm Pàťìľ75% (8)

- LM 2904 AhDokument19 SeitenLM 2904 AhlyndondrNoch keine Bewertungen

- Experiment 7Dokument8 SeitenExperiment 7Joseph ZamoraNoch keine Bewertungen

- Design of 6T, 5T and 4T SRAM Cell On Various Performance MetricsDokument6 SeitenDesign of 6T, 5T and 4T SRAM Cell On Various Performance MetricsNeha TripathiNoch keine Bewertungen

- 25 Watt MosFet Audio AmplifierDokument3 Seiten25 Watt MosFet Audio Amplifiermcm200Noch keine Bewertungen

- Capacitors MCQ & AnsDokument6 SeitenCapacitors MCQ & AnsMMBDONNoch keine Bewertungen

- DSD Lab ReportDokument70 SeitenDSD Lab ReportJinesh KbNoch keine Bewertungen

- Function GeneratorDokument12 SeitenFunction Generatordineshpadhiyar0% (1)

- Digital Electronics Counter Schematics and OperationDokument44 SeitenDigital Electronics Counter Schematics and Operationtaufiqridz100% (1)

- Presentation2 Chapter 9Dokument21 SeitenPresentation2 Chapter 9soethurein227Noch keine Bewertungen

- TDA2003 stereo amplifier schematic to PCB designDokument7 SeitenTDA2003 stereo amplifier schematic to PCB designSiegrique Ceasar A. JalwinNoch keine Bewertungen

- Adjusting The DESAT ThresholdDokument5 SeitenAdjusting The DESAT Thresholdgjhsky gaoNoch keine Bewertungen

- CB 2 CleDokument4 SeitenCB 2 CleJosé Antonio Montanares ZambranoNoch keine Bewertungen

- 5 BPF, BRF1Dokument7 Seiten5 BPF, BRF1anandhmc100% (1)

- Low Power Clock Gates Optimization For Clock Tree DistributionDokument5 SeitenLow Power Clock Gates Optimization For Clock Tree DistributionNguyen Van ToanNoch keine Bewertungen

- Digital Microprocessor Lab Manual 5th SemDokument26 SeitenDigital Microprocessor Lab Manual 5th SemRonit ChowdhuryNoch keine Bewertungen

- LC Filters PDFDokument5 SeitenLC Filters PDFcolorado wildernessNoch keine Bewertungen

- ECE429 Laboratory 4 NAND Schematic: Bapu A20489420 21/09/2021Dokument14 SeitenECE429 Laboratory 4 NAND Schematic: Bapu A20489420 21/09/2021Prasanna NalawarNoch keine Bewertungen

- Low Pass Filters PDFDokument15 SeitenLow Pass Filters PDFSheharyar MunirNoch keine Bewertungen

- References: Department of Electrical, Electronic & Computer Engineering University of PretoriaDokument16 SeitenReferences: Department of Electrical, Electronic & Computer Engineering University of Pretoria陳一束Noch keine Bewertungen

- Digital CMOS Logic CircuitsDokument84 SeitenDigital CMOS Logic CircuitsPulkit AggarwalNoch keine Bewertungen

- Virtual University Cs302 Final Term Solved Mega FileDokument39 SeitenVirtual University Cs302 Final Term Solved Mega Filesoftlizer100% (1)

- 20-Parallel Adder - Subtractor, Carry Look Ahead Adder-14-02-2023 PDFDokument13 Seiten20-Parallel Adder - Subtractor, Carry Look Ahead Adder-14-02-2023 PDFBack upNoch keine Bewertungen

- ECE 334-Lecture 30-nMOS - Inverter-DepletionloadDokument7 SeitenECE 334-Lecture 30-nMOS - Inverter-DepletionloadBretuoba Nana Yaw YeboahNoch keine Bewertungen