Beruflich Dokumente

Kultur Dokumente

modEEGamp v1.1 PDF

Hochgeladen von

cik4Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

modEEGamp v1.1 PDF

Hochgeladen von

cik4Copyright:

Verfügbare Formate

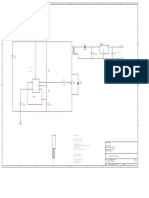

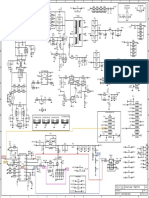

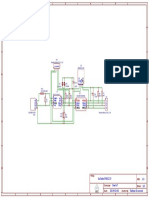

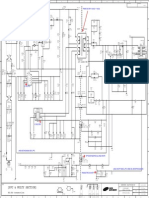

Electrode

DC checkpoint

ESD protection

PAD201

HF rejection and user current limiter

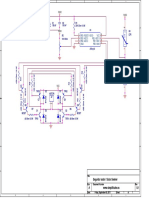

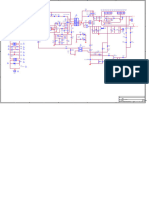

Channel 2 - CH2- R202 R208 R207 G=12.2 +5V/2 G=40

Electrode

2k2 2k2 2k2 IC202

HP 1 pole fc=0.16 Hz

G=6..100 G=16 C234

Q205 Q201 2

100pF

33nF 5%

C205

3

BC547 BC557 R214 1µF

2 2 1 IC205A C229 R232 R228 IC205B

6 3 5

2k2

C209

10pF

ADIN1

1 1

1 1

1 7

R215

R224

C220 1µF 10k 15k

220nF 5%

C231

VGND 8 2 6

1M

2 2 5 C217 TLC277P TLC277P +5V/2

R231

100pF 2k2

C204

3 7 100nF

1M

Q207 Q203 V+

3

BC547 BC557 4 C214

100nF

R220 VGND

2

100nF R221 R229 R230

C227

V-

CH2+ 2k2 3 1

VCC

Channel 2 + 2k2 2k2

INA114P

8

Electrode 3 1 100k 8.2k 100k

R201 R205 R206 AGND VGND 1k

P202 VGND C232 IC205PWR

C225

IC204B

100nF

20k C222

R219 5 VGND VGND

GND

4

Input Voltage Full Scale (10 Bit) = 512uVpp 7 1nF

6 1nF

Input Voltage Resolution (1 LSB) = 0.5 uVpp 10k TLC277P 3rd order "Besselworth" filter, fc = 59 Hz.

Total gain = 7812.5 The 3rd pole is located on the digital board.

Input can handle up to +/-100mV DC electrode offset Electrode AGND

DC checkpoint

PAD202

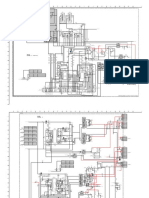

Channel 1 - CH1- R204 R212 R211 G=12.2 +5V/2 G=40

Electrode

2k2 2k2 2k2 IC203

HP 1 pole fc=0.16 Hz

G=6..100 G=16 C236

Q206 Q202 2

100pF

33nF 5%

C207

BC547 BC557 R216 1µF

2 2 1 IC206A C228 R237 R233 IC206B

2k2 6 3 5

C210

10pF

ADIN0

1 1

1 1

1 7

R226

R217 C221 1µF 10k 15k

220nF 5%

C235

VGND 8 2 6

1M

2 2 2k2 5 C218 TLC277P TLC277P +5V/2

R236

100pF

C206

3 7 100nF

1M

Q208 Q204 V+

3

BC547 BC557 4 C215

100nF

R222 VGND

2

100nF R225 R234 R235

C230

2k2 V-

2k2 2k2 3 1

VCC

Channel 1 + CH1+

INA114P

8

Electrode 3 1 100k 8.2k 100k

R203 R209 R210 AGND VGND 1k

PAD205 P203 VGND C233 IC206PWR

C223

+5V/2

100nF

COM 20k C224

VGND VGND

GND

100nF

4

PAD206 1nF 1nF

AGND C226

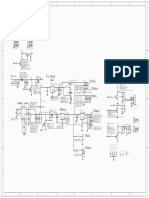

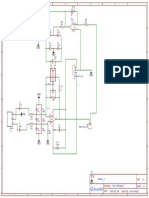

right leg driver AGND

VCC

IC204A

8

AGND

C216 R218 3

1 VGND +5V/2

IC204PWR

2

1nF 10k TLC277P C211

GND

R_LEG Only insert IC201 on _one_ board

4

IC201A

Right Leg R213 TLC277P 6 VGND when using 2 or 3 amplifier boards

8

R_LEG 2.0V

Electrode 7 100nF 3

C202

5 C219 1

1

C203 10nF

200k

1

2

P201

20k

C212 IC201B 2 VGND ref. voltage TLC277P

10nF

C213

+

47µF

100nF +5V/2

3

C208

4

AGND +2V, buffered

100nF

3

1nF simulates electrode impedance +

Vcc analog

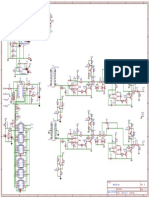

Right-leg driver (DRL) notes: AGND C201

PAD204 R238

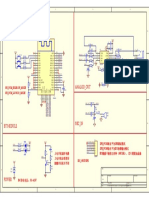

ADIN0

ADIN1

P201 is not needed when INA114 instrumentation amplifiers are used. 47µF tan 1ohm

You may replace it with a short wire from pin 2 and pin 1 (VGND). Cal_GND 10k 2.0V

J201

If P201 is needed, adjust potentiometer so DRL=0mV (referred to VGND) AGND 1 2

when _all_ amplifier inputs are shorted to the DRL output (R_LEG). R240 2.0V buf 3 4 1 2 SJ201

100

u cal

5 6 1 2 SJ202

Important usage instructions for the DRL. Ground plane is VGND 7 8 1 2 SJ203

PAD203 R239 R227 R223 9 10 1 2 SJ204

If you only want to use one channel, never let the other channel float. 11 12 1 2 SJ205

Always connect the unused terminals to VGND, or the DRL will not work properly. U_cal AGND 13 14 1 2 SJ206

10k 1M 1M 15 16

The solder-jumpers (SJ201 - SJ206) 17 18

voltage divider 1:20000 to the right, are used for channel 19 20

DRL design from http://www.biosemi.com/publications/artikel7.htm, fig.3 5Vp-p +/-10% => 250µVp-p +/-10% mapping. This allows multiple amplifier 21 22

boards to share the same connector. 23 24

See http://openeeg.sf.net for more information.

250µVpp +/-10%, 0.1 .. 100Hz 25 26

Authors: Moritz v. Buttlar, Joerg Hansmann, Andreas R 2 channels must be selected on each 27 28

Square wave Calibration Signal board by closing two jumper gaps with 29 30 PWM

solder. 31 32

modEEGamp_v1_1_Rev. A Use SJ201 and SJ204 for the first board.

33 34

PINHD-2X17

Olimex LTD, Bulgaria, 2013 PWM cal (PB1)

https://www.olimex.com Output Voltage Full Scale (10 Bit) = 4.000 Vp-p (Range 0..4V)

=> 3.9mV bitstep at 10 bit resolution.

This hardware design by Olimex LTD is licensed under a Creative Commons Attribution-ShareAlike 3.0 Unported License.

Das könnte Ihnen auch gefallen

- Schematic - LMR SDR V 1.5.A - 2021-11-23Dokument3 SeitenSchematic - LMR SDR V 1.5.A - 2021-11-23pajrulnetNoch keine Bewertungen

- Schematic PrintsDokument1 SeiteSchematic PrintsDân Kỹ Thuật100% (1)

- MicroNX UcD 400W 4 Ohm Ver.1Dokument2 SeitenMicroNX UcD 400W 4 Ohm Ver.1Hilal Bocah Elektro50% (2)

- Input Balance With GainDokument2 SeitenInput Balance With Gainchanomi613Noch keine Bewertungen

- Schematic - IRS20957 FB - Sheet - 1 - 20190930201554Dokument1 SeiteSchematic - IRS20957 FB - Sheet - 1 - 20190930201554jean grangeonNoch keine Bewertungen

- UntitledDokument1 SeiteUntitledDeepak AnandNoch keine Bewertungen

- Ecualizador PeaveyDokument5 SeitenEcualizador PeaveyJavier Ventura ValenciaNoch keine Bewertungen

- 5V From +5V Power SuppyDokument1 Seite5V From +5V Power SuppySuny Khan100% (1)

- Schematic - D1K5 Dual Feedback 2 Msfet - 2021-10-06Dokument1 SeiteSchematic - D1K5 Dual Feedback 2 Msfet - 2021-10-06An NguyênNoch keine Bewertungen

- KaRadio 32 PCM5102 1,8 LCDDokument1 SeiteKaRadio 32 PCM5102 1,8 LCDAndy DanteNoch keine Bewertungen

- Input Balance With Signal IndicatorDokument1 SeiteInput Balance With Signal IndicatorMafia BetawiNoch keine Bewertungen

- Nguyenly PDFDokument1 SeiteNguyenly PDFThanh Nguyễn Văn100% (1)

- 50 Watt Mono Amplifier TDA1514A Technical MrigankaDokument2 Seiten50 Watt Mono Amplifier TDA1514A Technical MrigankaNataly DavalosNoch keine Bewertungen

- Invertor LCD OZ9601SDokument1 SeiteInvertor LCD OZ9601SRenatoMaia100% (1)

- Seguidor SolarDokument1 SeiteSeguidor SolarNestor Daniel Puyen MateoNoch keine Bewertungen

- Ufo ChaserDokument1 SeiteUfo Chaserbitu&piutaNoch keine Bewertungen

- Arcam dv135 dv137 dv139 SCHDokument1 SeiteArcam dv135 dv137 dv139 SCHRobert ParishNoch keine Bewertungen

- Arcam dv139 SCHDokument22 SeitenArcam dv139 SCHRobert ParishNoch keine Bewertungen

- Schematic - MP2639 Lithium Charging and Discharging - 2020-05-15 - 14-29-38Dokument1 SeiteSchematic - MP2639 Lithium Charging and Discharging - 2020-05-15 - 14-29-38Colin HwangNoch keine Bewertungen

- PWM 5a SCHDokument1 SeitePWM 5a SCHNgọc Hưng TạNoch keine Bewertungen

- 250 Watt Mono Amplifier Technical MrigankaDokument2 Seiten250 Watt Mono Amplifier Technical MrigankaK. RAJA SEKAR100% (1)

- Laney Prism - Series p20 SCHDokument9 SeitenLaney Prism - Series p20 SCHgabriel_lazarescu2005Noch keine Bewertungen

- CVMV26L-G Schematic DiagramDokument6 SeitenCVMV26L-G Schematic DiagrambelajartvkuNoch keine Bewertungen

- Schematic Sumsour+8586+pcb Sheet 1 20200406014319Dokument1 SeiteSchematic Sumsour+8586+pcb Sheet 1 20200406014319jheyson_mogollonNoch keine Bewertungen

- Sakura AV-735 - XertronsDokument9 SeitenSakura AV-735 - XertronsBoune Wakanda100% (3)

- DIY一个简易单管电磁炉 感应加热 电磁炉驱动板Dokument3 SeitenDIY一个简易单管电磁炉 感应加热 电磁炉驱动板ijgoiesfefNoch keine Bewertungen

- Schematics-478020 RouterDokument5 SeitenSchematics-478020 RouterALFONZO DANIELNoch keine Bewertungen

- Panasonic PSU+LED DriverDokument2 SeitenPanasonic PSU+LED DriverAnil BpsNoch keine Bewertungen

- 17ips11 R4Dokument1 Seite17ips11 R4zokiNoch keine Bewertungen

- 17ips11-R4 mp3394Dokument18 Seiten17ips11-R4 mp3394laboratorio fercorNoch keine Bewertungen

- Schematic - PhiDAC Hex 5.26Dokument1 SeiteSchematic - PhiDAC Hex 5.26Not TELLIN YouNoch keine Bewertungen

- File Merged By: Alu Tiit: (Acr) 576pinoy - Tech / 2 Inputs Mic With Echo / Dec. 8, 2018Dokument5 SeitenFile Merged By: Alu Tiit: (Acr) 576pinoy - Tech / 2 Inputs Mic With Echo / Dec. 8, 2018rea sonerNoch keine Bewertungen

- 2 Inputs Mic With Echo SCHDokument5 Seiten2 Inputs Mic With Echo SCHrea soner100% (1)

- Banana Pi BPI-D1 - SCHDokument1 SeiteBanana Pi BPI-D1 - SCHTuan Anh100% (1)

- 2 Inputs Mic With Echo - SCHDokument1 Seite2 Inputs Mic With Echo - SCHMuhammad YousafNoch keine Bewertungen

- Schematic - Pre Balance 1kpro Flaship - 2022!03!29Dokument1 SeiteSchematic - Pre Balance 1kpro Flaship - 2022!03!29Komal KesariyaNoch keine Bewertungen

- GND GND: Caixa Multi Uso Pre Ampli + FonteDokument2 SeitenGND GND: Caixa Multi Uso Pre Ampli + FonteLuis BagarelliNoch keine Bewertungen

- Schematic - YAXUN 881D+ - 2022-01-01Dokument1 SeiteSchematic - YAXUN 881D+ - 2022-01-01Murilo de Andrade Melo89% (9)

- Schematic - DIY Battery (Li-Ion) Capacity Tester - 2020-04-21 - 16-58-56Dokument1 SeiteSchematic - DIY Battery (Li-Ion) Capacity Tester - 2020-04-21 - 16-58-56Kien TrungNoch keine Bewertungen

- UcD FD1K Full Discrete Class D Amplifir Ver.1 - Feb2021Dokument1 SeiteUcD FD1K Full Discrete Class D Amplifir Ver.1 - Feb2021Azzuhry Miftman100% (1)

- Bit3105 Push PullDokument1 SeiteBit3105 Push PullServis SonicesNoch keine Bewertungen

- Diy MicDokument1 SeiteDiy MicnickcasalNoch keine Bewertungen

- Sony - g3l - Smps SchematicDokument4 SeitenSony - g3l - Smps Schematicகுமார்Noch keine Bewertungen

- Sine Wave Inverter SchematicDokument1 SeiteSine Wave Inverter SchematicRiyan AditiaNoch keine Bewertungen

- Llittle Bear B-1 SchematicDokument1 SeiteLlittle Bear B-1 SchematicFernando CostaNoch keine Bewertungen

- Schematic Isolated-INA219 Sheet-1 20190330172040Dokument1 SeiteSchematic Isolated-INA219 Sheet-1 2019033017204031482Noch keine Bewertungen

- Ref SchematicDokument1 SeiteRef Schematiczathya dark100% (1)

- B DC1459B - A / B: Customer NoticeDokument1 SeiteB DC1459B - A / B: Customer NoticemhemaraNoch keine Bewertungen

- Schematic - Echo PT2399 Circuit - Sheet - 1 - 20200213181745Dokument1 SeiteSchematic - Echo PT2399 Circuit - Sheet - 1 - 20200213181745Ronaldo SidneiNoch keine Bewertungen

- Inverter EsqDokument1 SeiteInverter EsqkoNoch keine Bewertungen

- Semiconducting III–V Compounds: International Series of Monographs on SemiconductorsVon EverandSemiconducting III–V Compounds: International Series of Monographs on SemiconductorsNoch keine Bewertungen

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsVon EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNoch keine Bewertungen

- Solution Manual for an Introduction to Equilibrium ThermodynamicsVon EverandSolution Manual for an Introduction to Equilibrium ThermodynamicsNoch keine Bewertungen

- Anais Do Workshop De Micro-ondasVon EverandAnais Do Workshop De Micro-ondasNoch keine Bewertungen

- Microwave Devices, Circuits and Subsystems for Communications EngineeringVon EverandMicrowave Devices, Circuits and Subsystems for Communications EngineeringBewertung: 4 von 5 Sternen4/5 (1)

- Adafruit INA219 Current Sensor Breakout: Created by Lady AdaDokument33 SeitenAdafruit INA219 Current Sensor Breakout: Created by Lady Adacik4Noch keine Bewertungen

- Z NoiseDokument16 SeitenZ NoiserjpfunkNoch keine Bewertungen

- Zhang2021 Chapter EEG-BasedEmotionClassificationusingentropyfeaturesandMLDokument12 SeitenZhang2021 Chapter EEG-BasedEmotionClassificationusingentropyfeaturesandMLcik4Noch keine Bewertungen

- Tayeb Gumpy Jne DistilledDokument26 SeitenTayeb Gumpy Jne Distilledcik4Noch keine Bewertungen

- Capacitive Touch Building Security System Equipment Using Msp430™ Microcontrollers With Captivate™ TechnologyDokument2 SeitenCapacitive Touch Building Security System Equipment Using Msp430™ Microcontrollers With Captivate™ Technologycik4Noch keine Bewertungen

- CMRR by Analog DevicesDokument3 SeitenCMRR by Analog Devicesofir485Noch keine Bewertungen

- MT 042Dokument14 SeitenMT 042cik4Noch keine Bewertungen

- Easy Neural Networks With FANNDokument6 SeitenEasy Neural Networks With FANNRoberto SolanoNoch keine Bewertungen

- SMDGuide 03Dokument1 SeiteSMDGuide 03cik4Noch keine Bewertungen

- Mathematics For The How eDokument219 SeitenMathematics For The How erameshg1971Noch keine Bewertungen

- Mathematics For The How eDokument3 SeitenMathematics For The How ecik4Noch keine Bewertungen

- NARP Guidelines To The Applicant 2019Dokument3 SeitenNARP Guidelines To The Applicant 2019cik4Noch keine Bewertungen

- Fieldkit Manual v1.0Dokument103 SeitenFieldkit Manual v1.0cik4Noch keine Bewertungen

- LM 10Dokument37 SeitenLM 10alexanderNoch keine Bewertungen

- Snosbz9c 316723Dokument20 SeitenSnosbz9c 316723cik4Noch keine Bewertungen

- Ragnar's Guide To Home and Recreational Use of High ExplosivesDokument63 SeitenRagnar's Guide To Home and Recreational Use of High Explosivestorontogoat100% (2)

- Ina 129Dokument29 SeitenIna 129cik4Noch keine Bewertungen

- 358 DatasheetDokument38 Seiten358 DatasheetJual PsuNoch keine Bewertungen

- SpikerBox V 1 3c InstructionsDokument5 SeitenSpikerBox V 1 3c Instructionscik4Noch keine Bewertungen

- Development of Gamma-Phase Hot-Pressing of UraniumDokument20 SeitenDevelopment of Gamma-Phase Hot-Pressing of Uraniumcik4Noch keine Bewertungen

- S e Gontarski What It Is To Have Been Bergson and Beckett On Movement Multiplicity and RepresentationDokument12 SeitenS e Gontarski What It Is To Have Been Bergson and Beckett On Movement Multiplicity and Representationcik4Noch keine Bewertungen

- Thermal Analysis of PlutoniumDokument16 SeitenThermal Analysis of Plutoniumcik4Noch keine Bewertungen

- Zabelina Robinson 2010bDokument8 SeitenZabelina Robinson 2010bcik4Noch keine Bewertungen

- What Does It Mean To You? What Kind of Art Do You Make?Dokument1 SeiteWhat Does It Mean To You? What Kind of Art Do You Make?cik4Noch keine Bewertungen

- Difficult ConversationsDokument26 SeitenDifficult Conversationscik4Noch keine Bewertungen

- Poetry and Finance - BifoDokument9 SeitenPoetry and Finance - Bifocik4Noch keine Bewertungen

- Challenging Conversations and How To Manage Them APRIL-2012Dokument24 SeitenChallenging Conversations and How To Manage Them APRIL-2012cik4Noch keine Bewertungen

- Adrian Piper Introduction2 PDFDokument10 SeitenAdrian Piper Introduction2 PDFcik4Noch keine Bewertungen

- The Painter of Modern Life and Other Essays, by Charles BaudelaireDokument16 SeitenThe Painter of Modern Life and Other Essays, by Charles BaudelaireFrank Hobbs0% (1)

- PotentiometryDokument6 SeitenPotentiometryCrissalyn AyentoNoch keine Bewertungen

- DL24P Schematic DiagramDokument1 SeiteDL24P Schematic DiagramLAN JR HOUSE0% (1)

- An Adaptive Hy Steresis-Band Current Control Technique of A Voltage-Fed PWM Inverter For Machine Drive SystemDokument7 SeitenAn Adaptive Hy Steresis-Band Current Control Technique of A Voltage-Fed PWM Inverter For Machine Drive SystemJandfor Tansfg Errott100% (1)

- DF50 Auto Hematology Analyzer Operator's Manual-1Dokument225 SeitenDF50 Auto Hematology Analyzer Operator's Manual-1faiz71% (7)

- Soliphant M FTM51 - Final Inspection Protocol - SERNR - R705FB0107A (En)Dokument1 SeiteSoliphant M FTM51 - Final Inspection Protocol - SERNR - R705FB0107A (En)Ahmad DagamsehNoch keine Bewertungen

- Flextec 350X ConnectDokument180 SeitenFlextec 350X ConnectRigoberto Delgado100% (1)

- T400HW02-V5-AUO Samsung 40 Pol PDFDokument30 SeitenT400HW02-V5-AUO Samsung 40 Pol PDFRubia De SouzaNoch keine Bewertungen

- Development of Power Factor Meter Using ArduinoDokument4 SeitenDevelopment of Power Factor Meter Using ArduinoSam SureshNoch keine Bewertungen

- Residential Commercial and Industrial Electrical Systems JGWDJDokument4 SeitenResidential Commercial and Industrial Electrical Systems JGWDJaa0% (2)

- Fix 10 Minute BanDokument1.051 SeitenFix 10 Minute BanYãsmëèñ Kháñ60% (5)

- Oil Burner Controls Type BHO 64 and LOA 44 - DanfossDokument12 SeitenOil Burner Controls Type BHO 64 and LOA 44 - Danfossr_cristiNoch keine Bewertungen

- Service Manual Audio Car Philips CEM250-55Dokument32 SeitenService Manual Audio Car Philips CEM250-55Alexandre Pereira NunesNoch keine Bewertungen

- Ower Lectronics (: Soft Switching (L40 - L41)Dokument7 SeitenOwer Lectronics (: Soft Switching (L40 - L41)Mayank KashyapNoch keine Bewertungen

- Neo Neon General Catalog 2017-2018 PDFDokument20 SeitenNeo Neon General Catalog 2017-2018 PDFAhmad Nasrulloh IlyasNoch keine Bewertungen

- EC5 Ampleo/R: QES000089F - REV. E - 11/2007Dokument8 SeitenEC5 Ampleo/R: QES000089F - REV. E - 11/2007AmiroucheBenlakehalNoch keine Bewertungen

- Flash MemoryDokument15 SeitenFlash MemoryCRT07Noch keine Bewertungen

- 1 GeneratorDokument17 Seiten1 GeneratorSuparnoWitoradyoNoch keine Bewertungen

- Attenuation and DispersionDokument92 SeitenAttenuation and Dispersionscribd01Noch keine Bewertungen

- Speed Up Demanding Workloads, Save Admin Hassle, and Maximize Storage Capacity With A Dell EMC Isilon All-Flash Storage SystemDokument20 SeitenSpeed Up Demanding Workloads, Save Admin Hassle, and Maximize Storage Capacity With A Dell EMC Isilon All-Flash Storage SystemPrincipled TechnologiesNoch keine Bewertungen

- Luminus SST-20-WxS DatasheetDokument15 SeitenLuminus SST-20-WxS Datasheetunder attack (UnderAttack69)Noch keine Bewertungen

- See Unique Features of Rockwell Hardness Tester - Duramin 160Dokument2 SeitenSee Unique Features of Rockwell Hardness Tester - Duramin 160AimilNoch keine Bewertungen

- BMW ScannerDokument13 SeitenBMW ScannerscorpiusssNoch keine Bewertungen

- 5008S Fresenuis Service ManualDokument318 Seiten5008S Fresenuis Service ManualEslam Karam100% (10)

- MAX86140/ MAX86141 Best-in-Class Optical Pulse Oximeter and Heart-Rate Sensor For Wearable HealthDokument90 SeitenMAX86140/ MAX86141 Best-in-Class Optical Pulse Oximeter and Heart-Rate Sensor For Wearable Healthmaria jose rodriguez lopezNoch keine Bewertungen

- Modern Power Electronics and AC Drives by Bimal K Bose PDFDokument738 SeitenModern Power Electronics and AC Drives by Bimal K Bose PDFsurendrNoch keine Bewertungen

- (PFC & Multy Section) : Tranf - de Stby 5.3Vcd Y 13VcdDokument2 Seiten(PFC & Multy Section) : Tranf - de Stby 5.3Vcd Y 13Vcdcentauro2013100% (1)

- Automatic Brake Failure IndicatorDokument15 SeitenAutomatic Brake Failure IndicatorThirumal Valavan100% (1)

- Serial + Crack READ MEDokument2 SeitenSerial + Crack READ MEtoza74100% (1)

- IBM Power 570 Replacement ProcedureDokument346 SeitenIBM Power 570 Replacement Procedure26cristinaNoch keine Bewertungen

- AVAGO Transistor Selection GuideDokument156 SeitenAVAGO Transistor Selection GuidefahkingmoronNoch keine Bewertungen