Beruflich Dokumente

Kultur Dokumente

1.2.4.AK SequentialLogicDesign - Counters - DMS

Hochgeladen von

Vince MOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

1.2.4.AK SequentialLogicDesign - Counters - DMS

Hochgeladen von

Vince MCopyright:

Verfügbare Formate

1.2.3.

AK Binary Numbers & Conversion

Introduction

Along with combinational logic, sequential logic is a fundamental building block of digital

electronics. The output values of sequential logic depend not only on the current input values

(i.e., combinational logic), but also on previous output values. Thus, sequential logic requires

a clock signal to control sequencing and memory and to retain previous outputs.

In this activity we will use the D flip-flop introduced in the previous lesson. We are limiting our

use to this type of flip-flop in this introductory unit because of its simplicity and ease of use.

The D flip-flop is just one of many different types of flip-flops that can be used to implement

sequential logic circuits.

Equipment

Circuit Design Software (CDS)

(2) - 74LS74 Integrated Circuits (ICs)

#22 Gauge solid wire

Breadboard

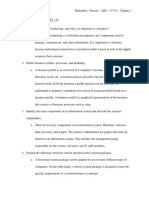

D Flip-Flop Example Circuit: Binary Counter

© 2014 Project Lead The Way, Inc.

Digital Electronics ANSWER KEY 1.2.4 Sequential Logic Design (DMS) – Page 1

Procedure

Let’s begin the study of sequential logic by reviewing the basic operations of the D flip-flop.

1. Using the Circuit Design Software (CDS), create the circuit below.

a) Start the simulation.

b) Set the input switches P and C to 5v. Again, since PR and CLR are active low

inputs, this will make them both inactive. Toggle the input T several times. The

circuit should behave exactly like the circuit in Activity 1.1.6

c) Set the input switch P to GROUND and C to 5v.

What is the state of the two outputs?

Que is on. NOT Que is off.

d) Toggle the input T several times.

Record what effect this has on the two outputs.

No change. The flip-flop is “preset” to “1”.

e) Set the input switch P to 5v and C to GROUND.

What is the state of the two outputs?

Que is off. NOT Que is on.

f) Toggle the input T several times.

Record what effect this has on the two outputs.

No change. The flip-flop is “cleared” to “0”.

© 2014 Project Lead The Way, Inc.

Digital Electronics ANSWER KEY 1.2.4 Sequential Logic Design (DMS) – Page 2

2. Let us examine a simple binary counter. Counters are one of the most common

applications of flip-flops. The circuit that we will be observing is called a two-bit binary

counter. The counter will count from zero (00 in binary) to three (11 in binary).

3. Using the Circuit Design Software (CDS), enter the two-bit binary counter shown

below. Use a switch for the input Clock-In and probes for the outputs A and B.

a) Start the simulation.

b) In Activity 1.1.6 we learned that the output on the first flip-flop (A) changes only

when the Clock-In goes from low to high. Toggle the input Clock-In (switch T)

until both outputs A and B are both low and switch T is low. Now cycle

switch T (Cycle means to toggle from low to high back to low) and record what

effect this has on the two outputs in the table below.

Clock-In A B

Initial Values 0 0

1st Cycle of switch T 0 1

2nd Cycle of switch T 1 0

3rd Cycle of switch T 1 1

4th Cycle of switch T 0 0

5th Cycle of switch T 0 1

6th Cycle of switch T 1 0

7th Cycle of switch T 1 1

8th Cycle of switch T 0 0

9th Cycle of switch T 0 1

Based on these results, explain the pattern that you observe in the two outputs.

The clock changes A, and output from A changes B.

The outputs create a binary count from 0 to 3 (002 to 112).

© 2014 Project Lead The Way, Inc.

Digital Electronics ANSWER KEY 1.2.4 Sequential Logic Design (DMS) – Page 3

4. Using the Circuit Design Software (CDS), modify the circuit used in step (1) so that it

matches that shown below.

a. The first modification is to replace the switch input with a CLOCK_VOLTAGE.

This change will result in the input being continuously toggled. Be sure the

CLOCK_VOLTAGE is set to 5 volts, 50% duty cycle, 60 Hz.

b. The second modification is to add a four-channel oscilloscope set up to view the

four signals A, B, Clock-In.

c. Be sure to set the oscilloscope’s time-base to 20ms/div and the vertical bases

of the four channels to 10volts/div. Also, adjust the Y position of the three

channels such that the four signals are all clearly visible.

CLK

© 2014 Project Lead The Way, Inc.

Digital Electronics ANSWER KEY 1.2.4 Sequential Logic Design (DMS) – Page 4

d. Start the simulation and let it run until you have captured several periods of

each signal.

e. Using the oscilloscope’s markers, measure the period of the three signals. Use

this data to calculate the frequency for each signal. Record your data in the

table below. Be sure to use the correct units.

Signal Period Frequency

Clock-In 16.7 ms 60 HZ

B 33.4 ms 30 HZ

A 66.7 ms 15 HZ

f. Based on these results, explain the relationship of the period and frequency

between the three signals. Was this expected?

Frequency and period are inversely related. The frequency gets cut in half

each time a flip-flop is added to the design.

5. Analyze the 4-bit binary counter shown below to determine the frequency and period

for the signals A, B, C, and D. Use the table shown below to record your answers.

Signal Period Frequency

Clock-In 1 ms 1000 Hz

D 2 ms 500 HZ

C 4 ms 250 HZ

B 8 ms 125 HZ

A 16 ms 62.5 HZ

6. With such a fast clock speed (1kHz) it is very difficult to see the binary count. Change

the clock frequency to something that allows you to see the 4 probes transition more

slowly in the simulation. Can you count to 15 in binary? What was the clock frequency

that was best for you?

© 2014 Project Lead The Way, Inc.

Digital Electronics ANSWER KEY 1.2.4 Sequential Logic Design (DMS) – Page 5

7. Using the pin diagram on the datasheet for the 74LS74 D flip-flop, create the 4-Bit

counter you explored in this activity on your protoboard. Wire the four outputs to (Y3,

Y2, Y1, Y0) of your protoboard. Wire the DIO3 to the CLK input of the first flip-flop.

Using the myDAQ to generate a clock signal.

8. With the protoboard plugged into the myDAQ, the myDAQ provides a number of

instruments that assist with design and measurement. We will use the NI ELVISmx

Digital Writer “DigOut” to generate a clock signal

9. Open National Instruments > NI ELVISmx Instrument Launcher. Select “DigOut”.

10. Settings:

a. Lines to Write (0-3)

b. Pattern (Ramp 0-15)

c. Run Continuously

11. When you select “Run” the Digital Writer will

send a signal that can be used as a clock signal to DIO3.

12. To utilize a faster frequency, switch to DIO2 DIO1 or DIO0.

13. Have your instructor verify the counter if functioning.

© 2014 Project Lead The Way, Inc.

Digital Electronics ANSWER KEY 1.2.4 Sequential Logic Design (DMS) – Page 6

Conclusion

1. The 2-Bit and 4-Bit counters you explored in this activity are referred to as “divide by

two” counters. Explain the relationship between each consecutive flip flop and the

order in which they are laid out in the design from right to left that creates a binary

count.

The frequency gets cut in half each time a flip-flop is added to the design.

If the outputs are arranged from lowest frequency to highest frequency from left

to right, the outputs create a binary count.

With 4 flip-flips the count is 0 to 15 (00002 to 11112).

2. If you added a 5th bit, what would you guess is the highest number you could count to?

With 5 flip-flips the count is 0 to 31 (000002 to 111112).

16 + 8 + 4 + 2 + 1 = 3

3. Can you think of 3-5 everyday items/products that might have a counter incorporated

in them?

Answers may vary.

Virtually all circuits in practical digital devices have a mixture of combinational

and sequential logic.

Vending Machines

Security Alarms

Thermostats

Electronic Battleship

Anything requiring memory

© 2014 Project Lead The Way, Inc.

Digital Electronics ANSWER KEY 1.2.4 Sequential Logic Design (DMS) – Page 7

Das könnte Ihnen auch gefallen

- Digital TransmissionDokument59 SeitenDigital TransmissionNeslynNoch keine Bewertungen

- Communications Lab Manual Amplitude Modulation and DSB-SCDokument85 SeitenCommunications Lab Manual Amplitude Modulation and DSB-SCMohamedKadry67% (3)

- Cmos Inverter CharacteristicsDokument5 SeitenCmos Inverter CharacteristicsRichu Jose CyriacNoch keine Bewertungen

- Commsys Lab EXPERIMENT 8 Full ReportDokument8 SeitenCommsys Lab EXPERIMENT 8 Full ReportShaarveen RajNoch keine Bewertungen

- Activity 3.1.1 Sequential Logic - D Flip-Flops and JK Flip-Flops PDFDokument5 SeitenActivity 3.1.1 Sequential Logic - D Flip-Flops and JK Flip-Flops PDFChris Ronald CherestalNoch keine Bewertungen

- Lotus and F1 EnginesDokument10 SeitenLotus and F1 EnginesshahrizalNoch keine Bewertungen

- Vectortechtex I-Series: Cutting Quality & PerformanceDokument2 SeitenVectortechtex I-Series: Cutting Quality & Performanceperro perezNoch keine Bewertungen

- Chapter 4 Sequential Logic CircuitsDokument50 SeitenChapter 4 Sequential Logic Circuitsjuber mullaNoch keine Bewertungen

- Unit-5 Asynchronus Sequential LogicDokument61 SeitenUnit-5 Asynchronus Sequential LogicjhalakNoch keine Bewertungen

- 2 Chapter 12 Algorithmic State MachineDokument16 Seiten2 Chapter 12 Algorithmic State MachinekaosadNoch keine Bewertungen

- Slide 7 FilterDokument66 SeitenSlide 7 FiltermusaNoch keine Bewertungen

- PSK Modulator: Experiment #Dokument6 SeitenPSK Modulator: Experiment #Kumar Adithya Myla0% (1)

- Digital Modulation 2. Digital Transmission 3. Multiple Access MethodsDokument39 SeitenDigital Modulation 2. Digital Transmission 3. Multiple Access MethodsFarah AryaNoch keine Bewertungen

- Sequential Logic BasicsDokument20 SeitenSequential Logic Basicskhairalla mohamedNoch keine Bewertungen

- Introduction To Communication System Chapter Two Analog Modulation TechniquesDokument47 SeitenIntroduction To Communication System Chapter Two Analog Modulation Techniqueshenok getachewNoch keine Bewertungen

- Experiment Manual For PCM ModulatorDokument6 SeitenExperiment Manual For PCM Modulatorrajivsharma1610Noch keine Bewertungen

- Digital TransmissionDokument26 SeitenDigital TransmissionAnum ShaukatNoch keine Bewertungen

- Digital TransmissionDokument17 SeitenDigital TransmissionDave MaghinayNoch keine Bewertungen

- 3 MarchDokument35 Seiten3 MarchAhmedNoch keine Bewertungen

- Unit 2: Digital TransmissionDokument91 SeitenUnit 2: Digital TransmissionAbhishek NaikNoch keine Bewertungen

- 3 - CMOS InverterDokument32 Seiten3 - CMOS Inverterroxy8marie8chanNoch keine Bewertungen

- Solar & Energy StorageDokument10 SeitenSolar & Energy StorageEku EmmanuelNoch keine Bewertungen

- Finite State MachineDokument57 SeitenFinite State MachinedoomachaleyNoch keine Bewertungen

- Pulse Modulation Consists Essentially of Sampling Analog Information Signals and Then ConvertingDokument40 SeitenPulse Modulation Consists Essentially of Sampling Analog Information Signals and Then ConvertingDaniel LoNoch keine Bewertungen

- 2 Bit Comparator PDFDokument12 Seiten2 Bit Comparator PDFSunith CkNoch keine Bewertungen

- Passive Filters Report LabDokument18 SeitenPassive Filters Report LableisllyNoch keine Bewertungen

- Active and Passive Filter CircuitsDokument10 SeitenActive and Passive Filter CircuitsDavid.R.Gilson88% (8)

- Courses in Electrical Engineering: Digital Electronics Chapter Two: Logic GatesDokument19 SeitenCourses in Electrical Engineering: Digital Electronics Chapter Two: Logic GatesNGOUNENoch keine Bewertungen

- ECE448 Lecture6 FSMDokument77 SeitenECE448 Lecture6 FSMHoàng Việt CườngNoch keine Bewertungen

- Chapter 5 Boolean Algebra and Logic GatesDokument34 SeitenChapter 5 Boolean Algebra and Logic GatesJontex 254Noch keine Bewertungen

- Pulse ModulationDokument12 SeitenPulse ModulationhlrwNoch keine Bewertungen

- FSK Modulator (DCS 6000 07)Dokument26 SeitenFSK Modulator (DCS 6000 07)maafkoroNoch keine Bewertungen

- AskDokument8 SeitenAskchiko12345Noch keine Bewertungen

- Sequential Circuits PDFDokument8 SeitenSequential Circuits PDFXavier SebastiaoNoch keine Bewertungen

- Analog To Digital ConverterDokument7 SeitenAnalog To Digital ConverterRavi Patel100% (1)

- FSKDokument10 SeitenFSKJyotirmoy DekaNoch keine Bewertungen

- Sequential Logic CircuitsDokument10 SeitenSequential Logic CircuitsAlinChanNoch keine Bewertungen

- ShannonDokument16 SeitenShannonSai Ram Bachu0% (1)

- 5 Sequential Logic Digital Logic DesigningDokument19 Seiten5 Sequential Logic Digital Logic DesigningabdullahNoch keine Bewertungen

- Principle of Communications System.Dokument31 SeitenPrinciple of Communications System.Tayyab ShahzadNoch keine Bewertungen

- 2a. Filter NetworksDokument12 Seiten2a. Filter NetworksDarren MaxNoch keine Bewertungen

- Sequential Logic CircuitsDokument18 SeitenSequential Logic CircuitsMona SayedNoch keine Bewertungen

- Practical: 11 To Study Sequential Circuits: Logic Circuits Have SomeDokument4 SeitenPractical: 11 To Study Sequential Circuits: Logic Circuits Have SomeSohil VohraNoch keine Bewertungen

- Unit 6 I ADCDokument29 SeitenUnit 6 I ADCcacaNoch keine Bewertungen

- Operational Amplifiers Questions and AnswersDokument4 SeitenOperational Amplifiers Questions and AnswersSuresh L100% (1)

- Analog Pulse ModulationDokument5 SeitenAnalog Pulse ModulationMohamedKadry100% (1)

- Two Wire Versus Four Wire: By: Rey Millikent N. Alamis Michael John BarcelonaDokument8 SeitenTwo Wire Versus Four Wire: By: Rey Millikent N. Alamis Michael John BarcelonaMelvin John Habla BanzueloNoch keine Bewertungen

- Encoders&DecodersDokument14 SeitenEncoders&DecodersAlex BongNoch keine Bewertungen

- PT3 - 13 - FSK Modulator PDFDokument20 SeitenPT3 - 13 - FSK Modulator PDFTempaNoch keine Bewertungen

- Module 4 Boolean Algebra and Digital LogicDokument34 SeitenModule 4 Boolean Algebra and Digital Logicnik occKNoch keine Bewertungen

- Final Digital Logic Design PPTDokument140 SeitenFinal Digital Logic Design PPTGHULAM MOHIUDDINNoch keine Bewertungen

- SPM Logic GatesDokument64 SeitenSPM Logic GatesRoy Roy SteinNoch keine Bewertungen

- Sequential Logic CircuitsDokument34 SeitenSequential Logic CircuitsRockRahilNoch keine Bewertungen

- Basic Principles of Communication Engineering-Est-AmpoloquioDokument5 SeitenBasic Principles of Communication Engineering-Est-AmpoloquioENRICO SANORIA PALER, M.A.Noch keine Bewertungen

- DSPDokument94 SeitenDSPRasha Hassan0% (1)

- Lab Manual DAC-SignedDokument10 SeitenLab Manual DAC-Signedabidrk_21789100% (2)

- Analog To Digital ConvertorDokument77 SeitenAnalog To Digital ConvertorDarshan ValaNoch keine Bewertungen

- Chapter 3 Sequential Logic and CircuitsDokument70 SeitenChapter 3 Sequential Logic and CircuitsCharul DeshpandeNoch keine Bewertungen

- 1.2.4.AK SequentialLogicDesign - Counters - DLBDokument7 Seiten1.2.4.AK SequentialLogicDesign - Counters - DLBSean MonahanNoch keine Bewertungen

- 1 2 4 Ak Sequentiallogicdesign Counters DLBDokument7 Seiten1 2 4 Ak Sequentiallogicdesign Counters DLBapi-290804719100% (1)

- Lab 6: Generating A Square Wave of Desired Frequency: 1. ObjectivesDokument4 SeitenLab 6: Generating A Square Wave of Desired Frequency: 1. ObjectivesVINAY YADAVNoch keine Bewertungen

- Digital LabDokument51 SeitenDigital LabBala SubramanianNoch keine Bewertungen

- ECE4719Dokument17 SeitenECE4719Vince MNoch keine Bewertungen

- Osstmm 3Dokument213 SeitenOsstmm 3Ben ZiriNoch keine Bewertungen

- Osstmm PDFDokument39 SeitenOsstmm PDFVince MNoch keine Bewertungen

- Melendrez CIS2 Chapter 8 BDokument5 SeitenMelendrez CIS2 Chapter 8 BVince MNoch keine Bewertungen

- Melendrez CIS2 Chapter 7 ADokument4 SeitenMelendrez CIS2 Chapter 7 AVince MNoch keine Bewertungen

- Melendrez CIS2 Chapter 5 ADokument5 SeitenMelendrez CIS2 Chapter 5 AVince MNoch keine Bewertungen

- Database Systems: Design, Implementation, and ManagementDokument51 SeitenDatabase Systems: Design, Implementation, and ManagementSalax Bu Khatir JigibaanNoch keine Bewertungen

- CIS2 Chapter 2Dokument7 SeitenCIS2 Chapter 2Vince MNoch keine Bewertungen

- CIS2 Chapter 1Dokument8 SeitenCIS2 Chapter 1Vince MNoch keine Bewertungen

- System Analysis and Design Chapter 1Dokument45 SeitenSystem Analysis and Design Chapter 1Randy Lamarca Alabab100% (1)

- YuriyDokument1 SeiteYuriyVince MNoch keine Bewertungen

- Fate Hubris and Truth The Downfall of OeDokument4 SeitenFate Hubris and Truth The Downfall of OeVince MNoch keine Bewertungen

- Africa DBQDokument2 SeitenAfrica DBQVince MNoch keine Bewertungen

- 1.1.4 Component IdentificationDokument3 Seiten1.1.4 Component IdentificationVince MNoch keine Bewertungen

- Fact Sheet CellD 300 en PDFDokument2 SeitenFact Sheet CellD 300 en PDFCharmer JiaNoch keine Bewertungen

- ErrorDokument28 SeitenErrorバネガス ネストルNoch keine Bewertungen

- User Manual Headset LG HBM-220 EngDokument9 SeitenUser Manual Headset LG HBM-220 Engrobnov7529Noch keine Bewertungen

- Aluminium ProfileDokument23 SeitenAluminium ProfileRobert CedeñoNoch keine Bewertungen

- Static Timing AnalysisDokument4 SeitenStatic Timing AnalysisballisticanaNoch keine Bewertungen

- Kanban: CEN 4010 Intro To Software Engineering Professor Alex RoqueDokument25 SeitenKanban: CEN 4010 Intro To Software Engineering Professor Alex RoquespringleeNoch keine Bewertungen

- Apache 2.0 Hardening GuideDokument13 SeitenApache 2.0 Hardening GuideLovelyn ArokhamoniNoch keine Bewertungen

- The Motherboard NotesDokument5 SeitenThe Motherboard NotesPritima RamalinggamNoch keine Bewertungen

- Duralife CeDokument2 SeitenDuralife CeVade ilustreNoch keine Bewertungen

- Core EdifDokument2 SeitenCore EdifOsama ElfadniNoch keine Bewertungen

- Phy 104 Lab ReportDokument6 SeitenPhy 104 Lab ReportMd. Abdullah ZishanNoch keine Bewertungen

- Manual de Servicio Ventilador Bear Cub 750psvDokument64 SeitenManual de Servicio Ventilador Bear Cub 750psvVladimir BorjaNoch keine Bewertungen

- Chapter 01Dokument62 SeitenChapter 01Rap JaviniarNoch keine Bewertungen

- Visvesvaraya Technological University Belagavi - 590018: Developments in Solar Dryers, Collectors and Absorber MaterialsDokument1 SeiteVisvesvaraya Technological University Belagavi - 590018: Developments in Solar Dryers, Collectors and Absorber MaterialsM.A rajaNoch keine Bewertungen

- Endress-Hauser Cerabar PMP11 ENDokument4 SeitenEndress-Hauser Cerabar PMP11 ENSensortecsa SensortecsaNoch keine Bewertungen

- A Data Pipeline Should Address These Issues:: Topics To StudyDokument10 SeitenA Data Pipeline Should Address These Issues:: Topics To StudyDerive XyzNoch keine Bewertungen

- Pro 5632Dokument9 SeitenPro 5632Phat HoangNoch keine Bewertungen

- SQT Group 10 FinalDokument18 SeitenSQT Group 10 FinalRoselynNoch keine Bewertungen

- Sap CommandsDokument2 SeitenSap CommandsAmbrish NigamNoch keine Bewertungen

- HI-1573, HI-1574: MIL-STD-1553 3.3V Monolithic Dual TransceiversDokument11 SeitenHI-1573, HI-1574: MIL-STD-1553 3.3V Monolithic Dual TransceiverscetibegizNoch keine Bewertungen

- Module 1: Introduction To Operating System: Need For An OSDokument15 SeitenModule 1: Introduction To Operating System: Need For An OSNiresh MaharajNoch keine Bewertungen

- Exam Flashcards: by Jonathan DonadoDokument520 SeitenExam Flashcards: by Jonathan Donadosolarstuff100% (1)

- Type No. 430-211-011 Clubsport: Basic Unit Ags Family IiDokument4 SeitenType No. 430-211-011 Clubsport: Basic Unit Ags Family IibruceNoch keine Bewertungen

- Renold Transmission Chain Catalogue ENG 0112Dokument94 SeitenRenold Transmission Chain Catalogue ENG 0112nataliaNoch keine Bewertungen

- Lab Manual Computer Organization and Hardware MaintenanceDokument28 SeitenLab Manual Computer Organization and Hardware Maintenanceanshroy7373Noch keine Bewertungen

- Canara - Epassbook - 2023-10-10 202024.654466Dokument49 SeitenCanara - Epassbook - 2023-10-10 202024.654466Kamal Hossain MondalNoch keine Bewertungen

- Miss Komal Ranvir: ObjectiveDokument1 SeiteMiss Komal Ranvir: ObjectiveKomal RanvirNoch keine Bewertungen