Beruflich Dokumente

Kultur Dokumente

S /D P C: Witching Ynamic Ower Onsumption

Hochgeladen von

Dr. Sampatrao L PinjareOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

S /D P C: Witching Ynamic Ower Onsumption

Hochgeladen von

Dr. Sampatrao L PinjareCopyright:

Verfügbare Formate

SWITCHING/DYNAMIC POWER

CONSUMPTION

Prof. Kaushik Roy

@ Purdue Univ.

Switching Power

• Signal properties

– Signal probability, Pi, - probability of a signal being logic ONE

– Signal activity, ai, - probability of signal switching(0->1, or 1->0)

• Energy dissipated per transition

dvout

EVDD iVDD (t )VDD dt VDD C L dt

0 0

dt

VDD

C LVDD dvout C LVDD

2

0

DD V

dvout

EC iVDD (t )vout dt C L vout dt C L vout dvout C LVDD

2

/2

0 0

dt 0

2

Source: Intel

Energy dissipated for 1->0 or 0->1 transition: C LVDD /2

Prof. Kaushik Roy

@ Purdue Univ.

Pdynamic = CL.VDD2.f

• Example

– 1.2m CMOS chip

– 100 MHz clock rate

– Average load capacitance of 30 fF/gate

– 5V power supply

• Power consumption/gate = 75 mW

• Design with 200,000 gates: 15W !

• Pessimistic evaluation: not all gates switch at the

full rate

• Have to consider the activity factor a: Effective

switching capacitance = aCL

Source: Intel

• Reducing VDD has a quadratic effect on Pdynamic

Prof. Kaushik Roy

@ Purdue Univ.

Estimation of Average Number of Transitions

Switching at internal nodes depends on input signals.

Model input signals as stochastic process. Each signal having some properties:

- Signal probability

- Signal activity

Source: Intel

Prof. Kaushik Roy

@ Purdue Univ.

Das könnte Ihnen auch gefallen

- Low PowerDokument67 SeitenLow PowerRajesh PylaNoch keine Bewertungen

- Lec4.4 Power DescipationDokument17 SeitenLec4.4 Power Descipationnadeem47Noch keine Bewertungen

- MC14513B BCD-To-Seven Segment Latch/Decoder/Driver: Cmos Msi (Low-Power Complementary MOS)Dokument12 SeitenMC14513B BCD-To-Seven Segment Latch/Decoder/Driver: Cmos Msi (Low-Power Complementary MOS)Panagiotis PanagosNoch keine Bewertungen

- Effect of Variation of Threshold Voltage On Power Consumption, Delay and Area of A 32x32 Bit Array MultiplierDokument14 SeitenEffect of Variation of Threshold Voltage On Power Consumption, Delay and Area of A 32x32 Bit Array MultiplierhneelakantNoch keine Bewertungen

- S - C P C: Hort Ircuit Ower OnsumptionDokument7 SeitenS - C P C: Hort Ircuit Ower OnsumptionDr. Sampatrao L PinjareNoch keine Bewertungen

- Low Power Vlsi Design 2Dokument70 SeitenLow Power Vlsi Design 2Rajesh PylaNoch keine Bewertungen

- Cmos Digital Vlsi Design: Power Analysis-IDokument29 SeitenCmos Digital Vlsi Design: Power Analysis-ISrikanth PasumarthyNoch keine Bewertungen

- Chapter 7 Mosfets in Ics - Scaling, Leakage, and Other TopicsDokument43 SeitenChapter 7 Mosfets in Ics - Scaling, Leakage, and Other Topicsmorcov19Noch keine Bewertungen

- Lecture 2: Computer Technology & Abstractions - Last Time: Review: Don't Forget The Simple ViewDokument16 SeitenLecture 2: Computer Technology & Abstractions - Last Time: Review: Don't Forget The Simple ViewFazal JadoonNoch keine Bewertungen

- Iec 61850 Mics Sel-351s 20120220Dokument7 SeitenIec 61850 Mics Sel-351s 20120220Adilson Leite ProençaNoch keine Bewertungen

- Buck ConvertersDokument15 SeitenBuck Convertersחי לוגסיNoch keine Bewertungen

- SMPSDokument46 SeitenSMPSNimsiri AbhayasingheNoch keine Bewertungen

- SLC 7015Dokument1 SeiteSLC 7015Дмитрий КопышевNoch keine Bewertungen

- Analog Electronics GATE IES PSU Study Materials PDFDokument17 SeitenAnalog Electronics GATE IES PSU Study Materials PDFDharmveer SinghNoch keine Bewertungen

- Power Analysis: Prof. Jagannadha Naidu KDokument23 SeitenPower Analysis: Prof. Jagannadha Naidu KParth VijayNoch keine Bewertungen

- Vlsid 06Dokument72 SeitenVlsid 06andreeeearaNoch keine Bewertungen

- Chenming Hu ch7 SlidesDokument43 SeitenChenming Hu ch7 SlideseleenaamohapatraNoch keine Bewertungen

- ASIC/FPGA Chip Design: Power DissipationDokument27 SeitenASIC/FPGA Chip Design: Power DissipationNguyen Yen NhiNoch keine Bewertungen

- Power Electronics (KWiki - Ch3 - Choppers) PDFDokument63 SeitenPower Electronics (KWiki - Ch3 - Choppers) PDFmadivala nagarajaNoch keine Bewertungen

- Overview of High-Speed Logic Families (08 Hours) : Doece, SvnitDokument109 SeitenOverview of High-Speed Logic Families (08 Hours) : Doece, SvnitJay KadelNoch keine Bewertungen

- FALLSEM2020-21 ECE3002 ETH VL2020210102012 Reference Material I 07-Sep-2020 Power Dissipation 8Dokument22 SeitenFALLSEM2020-21 ECE3002 ETH VL2020210102012 Reference Material I 07-Sep-2020 Power Dissipation 8SMNoch keine Bewertungen

- PowerDokument29 SeitenPowerAdamNoch keine Bewertungen

- The Boost ConverterDokument5 SeitenThe Boost ConverterKhafizuddin AzaziNoch keine Bewertungen

- Diode Models: March 2018Dokument3 SeitenDiode Models: March 2018Jarome G. OblenaNoch keine Bewertungen

- Power: Ref: Weste-HarrisDokument30 SeitenPower: Ref: Weste-HarrisNahid IslamNoch keine Bewertungen

- Advanced Digital Systems Design: 02/10/2002 EE6471 (KR) 1Dokument41 SeitenAdvanced Digital Systems Design: 02/10/2002 EE6471 (KR) 1mohammed zubairNoch keine Bewertungen

- DC DC Boost PPT SeminarDokument16 SeitenDC DC Boost PPT SeminarNishant Yadav100% (1)

- Design Tradeoffs: 6.004x Computation Structures Part 1 - Digital CircuitsDokument24 SeitenDesign Tradeoffs: 6.004x Computation Structures Part 1 - Digital Circuitslufer0528Noch keine Bewertungen

- MIP2K20MS Panasonic PDFDokument6 SeitenMIP2K20MS Panasonic PDFnita_alecsandruNoch keine Bewertungen

- CSE2210-Lab ManualDokument15 SeitenCSE2210-Lab ManualMaruf RumanNoch keine Bewertungen

- IntroductionDokument42 SeitenIntroductionKaltoum Robleh jiirNoch keine Bewertungen

- 04 Diode Models and CircuitsDokument35 Seiten04 Diode Models and Circuits陳浚維Noch keine Bewertungen

- Logic Families NotesDokument90 SeitenLogic Families NotesRajat KumarNoch keine Bewertungen

- Lect05 PDFDokument15 SeitenLect05 PDFVan GoldbergNoch keine Bewertungen

- Circuit Theory: Two-Port CircuitsDokument21 SeitenCircuit Theory: Two-Port CircuitsJhon ValenciaNoch keine Bewertungen

- Ch3 PowerBasicsDokument31 SeitenCh3 PowerBasicsGianfrancesco FlorioNoch keine Bewertungen

- Lec11 DiodesDokument59 SeitenLec11 DiodescgchydtrainingNoch keine Bewertungen

- Technical Data: Diode Gate - TREND SeriesDokument2 SeitenTechnical Data: Diode Gate - TREND SeriesAhmed El Emir Akkah AkkahNoch keine Bewertungen

- EPE3301 Power Electronics - 3. DC-DC ConvertersDokument66 SeitenEPE3301 Power Electronics - 3. DC-DC ConvertersBryan KekNoch keine Bewertungen

- Data Sheet: 74LVC2G07Dokument13 SeitenData Sheet: 74LVC2G07Le DungNoch keine Bewertungen

- Classical and Predictive Control Applied To A DC/DC Boost ConverterDokument7 SeitenClassical and Predictive Control Applied To A DC/DC Boost ConverterSantiago Cortes PerdomoNoch keine Bewertungen

- BTS 141Dokument11 SeitenBTS 141RM MódulosNoch keine Bewertungen

- Elektronika Daya Dan PenerapannyaDokument30 SeitenElektronika Daya Dan PenerapannyaMuhammad AfdalNoch keine Bewertungen

- Analytical Design Procedure For ResonantInductively Coupled Wireless Power Transfer SystemWith Class-DE Inverter and Class-E RectifierDokument4 SeitenAnalytical Design Procedure For ResonantInductively Coupled Wireless Power Transfer SystemWith Class-DE Inverter and Class-E Rectifierjuan8aNoch keine Bewertungen

- Presentation Emtp PDFDokument27 SeitenPresentation Emtp PDFManiraj PerumalNoch keine Bewertungen

- EE230 Lab 0Dokument8 SeitenEE230 Lab 0AnnirudhNoch keine Bewertungen

- MC14511B BCD-to-Seven Segment Latch/Decoder/DriverDokument10 SeitenMC14511B BCD-to-Seven Segment Latch/Decoder/DriverJaume Pulido TorresNoch keine Bewertungen

- Hu Hao Liu Yang Zhang JianhuaDokument8 SeitenHu Hao Liu Yang Zhang JianhuaMagraoui AbdelkadirNoch keine Bewertungen

- Power Electronics: DC-DC Converters (Choppers)Dokument35 SeitenPower Electronics: DC-DC Converters (Choppers)aswardi8756Noch keine Bewertungen

- ISSCC2011Visuals T3Dokument74 SeitenISSCC2011Visuals T3hello worldNoch keine Bewertungen

- Analysis of DC Fault For Dual Active Bridge DC/DC Converter Including Prototype VerificationDokument13 SeitenAnalysis of DC Fault For Dual Active Bridge DC/DC Converter Including Prototype VerificationKarthikkeyan SNoch keine Bewertungen

- Esc201: Introduction To Electronics: Amit Verma Dept. of Electrical Engineering Iit KanpurDokument31 SeitenEsc201: Introduction To Electronics: Amit Verma Dept. of Electrical Engineering Iit KanpurPrakhar chhalotreNoch keine Bewertungen

- Ideal SwitchDokument19 SeitenIdeal SwitchSubhash MurkuteNoch keine Bewertungen

- Overlap 1Dokument11 SeitenOverlap 1abcdefgNoch keine Bewertungen

- Research On The Characteristics of TEV When Disconnector Operating in UHV GISDokument7 SeitenResearch On The Characteristics of TEV When Disconnector Operating in UHV GISBalajiNoch keine Bewertungen

- Low Drop Dual Power Operational Amplifiers: DescriptionDokument10 SeitenLow Drop Dual Power Operational Amplifiers: DescriptionAmirNoch keine Bewertungen

- Low Drop Dual Power Operational Amplifiers: DescriptionDokument10 SeitenLow Drop Dual Power Operational Amplifiers: DescriptionAmirNoch keine Bewertungen

- Modeling and Simulation of A Single Phase Induction Motor With Adjustable Switched CapacitorDokument6 SeitenModeling and Simulation of A Single Phase Induction Motor With Adjustable Switched CapacitorMarcos Roberto ReinertNoch keine Bewertungen

- A DSP: L - P, U E P, & E R: Pplication TO OW Ower Nequal Rror Rotection Rror EsiliencyDokument11 SeitenA DSP: L - P, U E P, & E R: Pplication TO OW Ower Nequal Rror Rotection Rror EsiliencyDr. Sampatrao L PinjareNoch keine Bewertungen

- Canonical Signed Digits (CSD)Dokument5 SeitenCanonical Signed Digits (CSD)Dr. Sampatrao L PinjareNoch keine Bewertungen

- Actorization AND Pproximation: Prof. Kaushik Roy at Purdue UnivDokument7 SeitenActorization AND Pproximation: Prof. Kaushik Roy at Purdue UnivDr. Sampatrao L PinjareNoch keine Bewertungen

- Approximate Full Adder CellsDokument11 SeitenApproximate Full Adder CellsDr. Sampatrao L PinjareNoch keine Bewertungen

- A - C L P - Application Domain: Multi-Media Systems, Recognition, Mining, SynthesisDokument4 SeitenA - C L P - Application Domain: Multi-Media Systems, Recognition, Mining, SynthesisDr. Sampatrao L PinjareNoch keine Bewertungen

- R D R C C R: Educing THE Ynamic Ange OF Omputation AND Omplexity EductionDokument6 SeitenR D R C C R: Educing THE Ynamic Ange OF Omputation AND Omplexity EductionDr. Sampatrao L PinjareNoch keine Bewertungen

- L - P Vlsi S P: L C D: OW Ower Ignal Rocessing OW Omplexity EsignDokument8 SeitenL - P Vlsi S P: L C D: OW Ower Ignal Rocessing OW Omplexity EsignDr. Sampatrao L PinjareNoch keine Bewertungen

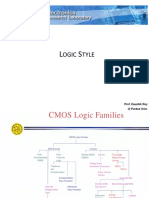

- Ogic Tyle: Prof. Kaushik Roy at Purdue UnivDokument10 SeitenOgic Tyle: Prof. Kaushik Roy at Purdue UnivDr. Sampatrao L PinjareNoch keine Bewertungen

- Lock Ating: Prof. Kaushik Roy at Purdue UnivDokument8 SeitenLock Ating: Prof. Kaushik Roy at Purdue UnivDr. Sampatrao L PinjareNoch keine Bewertungen

- Ulti Upply Oltage: Prof. Kaushik Roy at Purdue UnivDokument5 SeitenUlti Upply Oltage: Prof. Kaushik Roy at Purdue UnivDr. Sampatrao L PinjareNoch keine Bewertungen

- A Bit-Serial Adder Using Partially Reversible LogicDokument9 SeitenA Bit-Serial Adder Using Partially Reversible LogicDr. Sampatrao L PinjareNoch keine Bewertungen

- Analog Layout UTLDokument3 SeitenAnalog Layout UTLDr. Sampatrao L PinjareNoch keine Bewertungen

- E - C RCC: B I E R: Nergy Onsumption IN Ircuits A Rief Ntroduction TO Nergy EcoveryDokument8 SeitenE - C RCC: B I E R: Nergy Onsumption IN Ircuits A Rief Ntroduction TO Nergy EcoveryDr. Sampatrao L PinjareNoch keine Bewertungen

- Estimation of Average Number of Transitions: Source: IntelDokument2 SeitenEstimation of Average Number of Transitions: Source: IntelDr. Sampatrao L PinjareNoch keine Bewertungen

- Ariable Upply Oltage: Prof. Kaushik Roy at Purdue UnivDokument7 SeitenAriable Upply Oltage: Prof. Kaushik Roy at Purdue UnivDr. Sampatrao L PinjareNoch keine Bewertungen

- Overview of MEMSDokument152 SeitenOverview of MEMSDr. Sampatrao L PinjareNoch keine Bewertungen

- VLSI Implementation of Artificial Neural NetworkDokument26 SeitenVLSI Implementation of Artificial Neural NetworkDr. Sampatrao L PinjareNoch keine Bewertungen

- MicrothrusterDokument1 SeiteMicrothrusterDr. Sampatrao L PinjareNoch keine Bewertungen

- Design of CMOS Low Dropout Voltage RegulatorDokument32 SeitenDesign of CMOS Low Dropout Voltage RegulatorDr. Sampatrao L PinjareNoch keine Bewertungen

- Introduction To Analog Design: Dr. S. L. PinjareDokument65 SeitenIntroduction To Analog Design: Dr. S. L. PinjareDr. Sampatrao L Pinjare100% (1)

- Triggering Circuits of SCRDokument4 SeitenTriggering Circuits of SCRJPR EEENoch keine Bewertungen

- Easy Technical Guide To Understand PC Motherboard, Troubleshoot Problems and Its Repair: PART - IIIDokument3 SeitenEasy Technical Guide To Understand PC Motherboard, Troubleshoot Problems and Its Repair: PART - IIIAnonymous lPvvgiQjRNoch keine Bewertungen

- TouchGFX AtollicDokument14 SeitenTouchGFX Atollichanifmohammed85Noch keine Bewertungen

- 1 - Basic Table Io Operations With The Jde Oneworld Report Design AidDokument3 Seiten1 - Basic Table Io Operations With The Jde Oneworld Report Design Aidfarheen.sultansNoch keine Bewertungen

- GW - SDT G2 4-15K - Datasheet-EN PDFDokument2 SeitenGW - SDT G2 4-15K - Datasheet-EN PDFMuhammad FarhanNoch keine Bewertungen

- Fundamentals of Power Electronics: Robert W. Erickson University of Colorado, BoulderDokument35 SeitenFundamentals of Power Electronics: Robert W. Erickson University of Colorado, BoulderAhmedoNoch keine Bewertungen

- Finite State Machine Implementation: Prith Banerjee Ece C03 Advanced Digital Design Spring 1998Dokument31 SeitenFinite State Machine Implementation: Prith Banerjee Ece C03 Advanced Digital Design Spring 1998Hemant SaraswatNoch keine Bewertungen

- RC Servo Motor Control Using PWMDokument12 SeitenRC Servo Motor Control Using PWMsameer khanNoch keine Bewertungen

- XNC Modbus MasterDokument12 SeitenXNC Modbus Masterjgr77Noch keine Bewertungen

- Ids Ips Audit ChecklistDokument1 SeiteIds Ips Audit Checklisthakim hbNoch keine Bewertungen

- ITIL Change Control Form TemplateDokument2 SeitenITIL Change Control Form TemplateSergio TNoch keine Bewertungen

- CAT 910 Basic CircuiteDokument6 SeitenCAT 910 Basic CircuiteYober Emilio Nato AcostaNoch keine Bewertungen

- Cics AbendDokument3 SeitenCics AbendBalakrishna SambariNoch keine Bewertungen

- BJT Terminal CharacteristicsDokument11 SeitenBJT Terminal CharacteristicsTowsifTaherNoch keine Bewertungen

- Ins 24 DVR 02Dokument78 SeitenIns 24 DVR 02Pupung FlashNoch keine Bewertungen

- Pemeliharaan Proteksi, Scada Dan TelkomDokument18 SeitenPemeliharaan Proteksi, Scada Dan TelkomhanifzuraidaNoch keine Bewertungen

- Leading Cloud Service, Semiconductor, and System Providers Unite To Form Ultra Ethernet ConsortiumDokument1 SeiteLeading Cloud Service, Semiconductor, and System Providers Unite To Form Ultra Ethernet ConsortiumAnton ShilovNoch keine Bewertungen

- ChatLog Pega Batch 9 AM 2021 - 07 - 19 10 - 21Dokument5 SeitenChatLog Pega Batch 9 AM 2021 - 07 - 19 10 - 21Mahesh WaghNoch keine Bewertungen

- Apple Computer Inc. v. Burst - Com, Inc. - Document No. 78Dokument30 SeitenApple Computer Inc. v. Burst - Com, Inc. - Document No. 78Justia.comNoch keine Bewertungen

- Hefshine Softwares Recruitment Praposal by Akshayt ParamaneDokument8 SeitenHefshine Softwares Recruitment Praposal by Akshayt ParamaneAvinash JadhavNoch keine Bewertungen

- Career Opportunities in Electronics CommunicationDokument3 SeitenCareer Opportunities in Electronics CommunicationK K SHARMANoch keine Bewertungen

- 8251 - UsartDokument24 Seiten8251 - UsartAvanish NiranjanNoch keine Bewertungen

- Modbus RTU TCP/IP: HMI SettingDokument2 SeitenModbus RTU TCP/IP: HMI SettingGeorge GaitanakisNoch keine Bewertungen

- Practical Applications and Solutions Usi PDFDokument486 SeitenPractical Applications and Solutions Usi PDFSajjad AliNoch keine Bewertungen

- Python - Tutorial: #!/usr/bin/python Print "Hello, Python!"Dokument174 SeitenPython - Tutorial: #!/usr/bin/python Print "Hello, Python!"ankitNoch keine Bewertungen

- 22:33:58Dokument185 Seiten22:33:58BENEDIC OLDIE SIMARMATANoch keine Bewertungen

- IManager NetEco1000S ManualDokument356 SeitenIManager NetEco1000S ManualMARKING TELNoch keine Bewertungen

- ECEG-4221 VLSI Design: Addis Ababa Institute of Technology (AAIT) Department of Electrical and Computer EngineeringDokument18 SeitenECEG-4221 VLSI Design: Addis Ababa Institute of Technology (AAIT) Department of Electrical and Computer EngineeringNuhamin BirhanuNoch keine Bewertungen

- Digital Signal Processing Using Smart Biometric SolutionsDokument11 SeitenDigital Signal Processing Using Smart Biometric SolutionsMuhammed JaleelNoch keine Bewertungen

- It 3rd Year SllabusDokument50 SeitenIt 3rd Year Sllabushifzan786Noch keine Bewertungen