Beruflich Dokumente

Kultur Dokumente

VHDL Code For Flipflop

Hochgeladen von

LuisOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

VHDL Code For Flipflop

Hochgeladen von

LuisCopyright:

Verfügbare Formate

VHDL Code for Flipflop – D,JK,SR,T | 1

All flip-flops can be divided into four basic types: SR, JK, D and T. They differ in the number

of inputs and in the response invoked by different value of input signals.

Contents

1 SR FlipFlop

2 VHDL Code for SR FlipFlop

3 D FlipFlop

4 VHDL Code for D FlipFlop

5 JK FlipFlop

6 VHDL Code for JK FlipFlop

7 T FlipFlop

8 VHDL Code for T FlipFlop

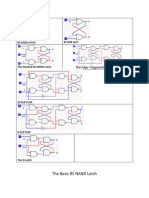

SR FlipFlop

A flip-flop circuit can be constructed from two NAND gates or two NOR gates. These flip-

flops are shown in Figure. Each flip-flop has two outputs, Q and Q’, and two inputs, set and

reset. This type of flip-flop is referred to as an SR flip-flop.

SR Flipflop truth table

All About FPGA www.allaboutfpga.com

VHDL Code for Flipflop – D,JK,SR,T | 2

VHDL Code for SR FlipFlop

library ieee;

use ieee. std_logic_1164.all;

use ieee. std_logic_arith.all;

use ieee. std_logic_unsigned.all;

entity SR_FF is

PORT( S,R,CLOCK: in std_logic;

Q, QBAR: out std_logic);

end SR_FF;

Architecture behavioral of SR_FF is

begin

PROCESS(CLOCK)

variable tmp: std_logic;

begin

if(CLOCK='1' and CLOCK'EVENT) then

if(S='0' and R='0')then

tmp:=tmp;

elsif(S='1' and R='1')then

tmp:='Z';

elsif(S='0' and R='1')then

All About FPGA www.allaboutfpga.com

VHDL Code for Flipflop – D,JK,SR,T | 3

tmp:='0';

else

tmp:='1';

end if;

end if;

Q <= tmp;

QBAR <= not tmp;

end PROCESS;

end behavioral;

D FlipFlop

The D flip-flop shown in figure is a modification of the clocked SR flip-flop. The D input goes

directly into the S input and the complement of the D input goes to the R input. The D input

is sampled during the occurrence of a clock pulse. If it is 1, the flip-flop is switched to

the set state (unless it was already set). If it is 0, the flip-flop switches to the clear state.

D Flipflop truth table

All About FPGA www.allaboutfpga.com

VHDL Code for Flipflop – D,JK,SR,T | 4

VHDL Code for D FlipFlop

library ieee;

use ieee. std_logic_1164.all;

use ieee. std_logic_arith.all;

use ieee. std_logic_unsigned.all;

entity D_FF is

PORT( D,CLOCK: in std_logic;

Q: out std_logic);

end D_FF;

architecture behavioral of D_FF is

begin

process(CLOCK)

begin

if(CLOCK='1' and CLOCK'EVENT) then

Q <= D;

end if;

end process;

end behavioral;

JK FlipFlop

A JK flip-flop is a refinement of the SR flip-flop in that the indeterminate state of the SR type

is defined in the JK type. Inputs J and K behave like inputs S and R to set and clear the flip-

flop (note that in a JK flip-flop, the letter J is for set and the letter K is for clear).

All About FPGA www.allaboutfpga.com

VHDL Code for Flipflop – D,JK,SR,T | 5

JK Flipflop truth table

VHDL Code for JK FlipFlop

library ieee;

use ieee. std_logic_1164.all;

All About FPGA www.allaboutfpga.com

VHDL Code for Flipflop – D,JK,SR,T | 6

use ieee. std_logic_arith.all;

use ieee. std_logic_unsigned.all;

entity JK_FF is

PORT( J,K,CLOCK: in std_logic;

Q, QB: out std_logic);

end JK_FF;

Architecture behavioral of JK_FF is

begin

PROCESS(CLOCK)

variable TMP: std_logic;

begin

if(CLOCK='1' and CLOCK'EVENT) then

if(J='0' and K='0')then

TMP:=TMP;

elsif(J='1' and K='1')then

TMP:= not TMP;

elsif(J='0' and K='1')then

TMP:='0';

else

TMP:='1';

end if;

end if;

Q<=TMP;

Q <=not TMP;

end PROCESS;

end behavioral;

T FlipFlop

The T flip-flop is a single input version of the JK flip-flop. As shown in figure, the T flip-flop is

obtained from the JK type if both inputs are tied together. The output of the T flip-flop

“toggles” with each clock pulse.

All About FPGA www.allaboutfpga.com

VHDL Code for Flipflop – D,JK,SR,T | 7

T Flipflop truth table

VHDL Code for T FlipFlop

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity T_FF is

port( T: in std_logic;

Clock: in std_logic;

Q: out std_logic);

end T_FF;

architecture Behavioral of T_FF is

signal tmp: std_logic;

All About FPGA www.allaboutfpga.com

VHDL Code for Flipflop – D,JK,SR,T | 8

begin

process (Clock)

begin

if Clock'event and Clock='1' then

if T='0' then

tmp <= tmp;

elsif T='1' then

tmp <= not (tmp);

end if;

end if;

end process;

Q <= tmp;

end Behavioral;

All About FPGA www.allaboutfpga.com

Das könnte Ihnen auch gefallen

- Anais Do Workshop De Micro-ondasVon EverandAnais Do Workshop De Micro-ondasNoch keine Bewertungen

- VHDL Code For Flipflop – D, JK, SR, TDokument12 SeitenVHDL Code For Flipflop – D, JK, SR, TSaurabh BhiseNoch keine Bewertungen

- VHDL Code For Flipflop D, JK, SR, TDokument7 SeitenVHDL Code For Flipflop D, JK, SR, TPeter HerreraNoch keine Bewertungen

- Mod 5 - FLIPFLOPS and Its TypesDokument28 SeitenMod 5 - FLIPFLOPS and Its TypesRavi CharanNoch keine Bewertungen

- Unit V Flip FlopsDokument8 SeitenUnit V Flip FlopsFLOWERNoch keine Bewertungen

- DSD Unit-5Dokument43 SeitenDSD Unit-5R.c.Raghavendra ReddyNoch keine Bewertungen

- DSD Module 5Dokument81 SeitenDSD Module 5Abinesh RNoch keine Bewertungen

- Flip-Flop DDokument7 SeitenFlip-Flop DEdwin GavilanezNoch keine Bewertungen

- Flip-Flop and Memory (12328)Dokument14 SeitenFlip-Flop and Memory (12328)red100% (1)

- Exp-6 20pec005Dokument8 SeitenExp-6 20pec005ajay nareshNoch keine Bewertungen

- Flip FlopsDokument11 SeitenFlip FlopsZakaria JubarnNoch keine Bewertungen

- Siddhi - E23cseu2200 - Assignment 8Dokument7 SeitenSiddhi - E23cseu2200 - Assignment 8chipichipichapachapa2121Noch keine Bewertungen

- Experiment:-6 Implementation of All The Flip-Flops 6 (A) SR Flip-FlopDokument12 SeitenExperiment:-6 Implementation of All The Flip-Flops 6 (A) SR Flip-Floptechworld611Noch keine Bewertungen

- Flip FlopsDokument21 SeitenFlip Flopsmangla bhullar100% (1)

- Computer Organization-Flip FlopsDokument19 SeitenComputer Organization-Flip Flopskamatamsandeepkumar20001305Noch keine Bewertungen

- Flip Flops VHDLDokument4 SeitenFlip Flops VHDLSriram Sarath NandulaNoch keine Bewertungen

- VHDL SequentialDokument5 SeitenVHDL SequentialSAKETSHOURAVNoch keine Bewertungen

- Lec # 06 - DLDDokument30 SeitenLec # 06 - DLDSunny 17Noch keine Bewertungen

- Project ReportDokument11 SeitenProject Reportamiethurgat100% (2)

- Chandigarh University, GharuanDokument5 SeitenChandigarh University, GharuanAnkit KumarNoch keine Bewertungen

- VHDL Codes For Flip FlopsDokument7 SeitenVHDL Codes For Flip FlopsAnil KumarNoch keine Bewertungen

- Expt 12Dokument5 SeitenExpt 12Dhrrishith VikalNoch keine Bewertungen

- Experiment-7: Aim Write A VHDL Program For A FLIP-FLOP and Check The Waveforms and The Hardware GeneratedDokument2 SeitenExperiment-7: Aim Write A VHDL Program For A FLIP-FLOP and Check The Waveforms and The Hardware GeneratedRishi Raj YadavNoch keine Bewertungen

- The J-K Flip Flop: ObjectivesDokument2 SeitenThe J-K Flip Flop: ObjectivesALviNoch keine Bewertungen

- Expt No.9Dokument5 SeitenExpt No.9Rithika 318030Noch keine Bewertungen

- Date: 06-10-2020, 8AM-9 AM Branch: CS/2 Year Topic: Flip FlopsDokument14 SeitenDate: 06-10-2020, 8AM-9 AM Branch: CS/2 Year Topic: Flip FlopsTech guru MaheshwariNoch keine Bewertungen

- Exp 6Dokument7 SeitenExp 6ajay nareshNoch keine Bewertungen

- Module 5 - Counter Design Problems and Flip-Flops - Oct 8thDokument65 SeitenModule 5 - Counter Design Problems and Flip-Flops - Oct 8thRavi CharanNoch keine Bewertungen

- Diseño Lógico Secuencial Mediante VHDL: Objetivo Diseñar Flip-Flops y Registros Con VHDLDokument7 SeitenDiseño Lógico Secuencial Mediante VHDL: Objetivo Diseñar Flip-Flops y Registros Con VHDLMa Del Rocio PalizNoch keine Bewertungen

- VHDokument2 SeitenVHleonardo perezNoch keine Bewertungen

- Lecture 7Dokument27 SeitenLecture 7rahulNoch keine Bewertungen

- D Flip-Flop: VHDL CodeDokument37 SeitenD Flip-Flop: VHDL CodeVenkata Nagasai2000Noch keine Bewertungen

- New Text DocumentDokument3 SeitenNew Text DocumentNaveen NegiNoch keine Bewertungen

- Flip FlopDokument34 SeitenFlip Flopqwrr rewqNoch keine Bewertungen

- Flip FlopDokument30 SeitenFlip FlopZen SeloveresNoch keine Bewertungen

- VHDL For SR Flip-FlopDokument4 SeitenVHDL For SR Flip-FlopAdiHasanNoch keine Bewertungen

- E Cad Lab ManualDokument51 SeitenE Cad Lab ManualRajesh DoradlaNoch keine Bewertungen

- Asynchronous Down Counter OBJECTIVE: To Design and Simulate The Asynchronous Down CounterDokument20 SeitenAsynchronous Down Counter OBJECTIVE: To Design and Simulate The Asynchronous Down CounterKalagadda BikshaluNoch keine Bewertungen

- Digital Lab Cs 6211 VHDL ProgramsDokument13 SeitenDigital Lab Cs 6211 VHDL ProgramsMurugan GNoch keine Bewertungen

- Experiment No 3Dokument20 SeitenExperiment No 3Ako C SeanNoch keine Bewertungen

- The Clocked RS Flip-FlopDokument4 SeitenThe Clocked RS Flip-Flopabhisheksikka17Noch keine Bewertungen

- 005 - K. C. Chang - Digital Systems - 4 A 15Dokument13 Seiten005 - K. C. Chang - Digital Systems - 4 A 15Rooster MXNoch keine Bewertungen

- Lab 7 - COADokument3 SeitenLab 7 - COAABHYANSH SHRIVASTAVANoch keine Bewertungen

- Flip Flops and Registers: Bca 5 SemesterDokument19 SeitenFlip Flops and Registers: Bca 5 SemesterDevi Sharan PrajapatiNoch keine Bewertungen

- VHDLDokument13 SeitenVHDLSrijeeta SenNoch keine Bewertungen

- Practical: 14 To Study J - K Flip Flop: Sohil Vohra (Lecturer - Shri K.J. Polytechnic College, Bharuch (C.E. Deptt) )Dokument5 SeitenPractical: 14 To Study J - K Flip Flop: Sohil Vohra (Lecturer - Shri K.J. Polytechnic College, Bharuch (C.E. Deptt) )Sohil VohraNoch keine Bewertungen

- Flip Flop Play HokeyDokument7 SeitenFlip Flop Play HokeyCherryPratamaNoch keine Bewertungen

- Lab 5 - FlipflopDokument34 SeitenLab 5 - Flipflopgokul sNoch keine Bewertungen

- Flipflops: Technical Seminar ReportDokument16 SeitenFlipflops: Technical Seminar ReportrachitNoch keine Bewertungen

- For Each Question Use Template in Student Database System!!!Dokument4 SeitenFor Each Question Use Template in Student Database System!!!Mehmethan Ayrım0% (1)

- Flip-Flops: S R Q Q' 1 0 1 0 Set 0 0 1 0 Previous Condition 0 1 0 1 Reset 0 0 0 1 Previous Condition 1 1 0 0 JammedDokument5 SeitenFlip-Flops: S R Q Q' 1 0 1 0 Set 0 0 1 0 Previous Condition 0 1 0 1 Reset 0 0 0 1 Previous Condition 1 1 0 0 JammedMatt PrestonNoch keine Bewertungen

- Flip-Flops and Latches: ElektronikDokument8 SeitenFlip-Flops and Latches: ElektronikbilgefNoch keine Bewertungen

- pp07 FloydDokument42 Seitenpp07 Floydsss0% (1)

- Sequential Code: ProcessDokument10 SeitenSequential Code: ProcessChutiyaNoch keine Bewertungen

- VHDL Code For D Flip-FlopDokument2 SeitenVHDL Code For D Flip-FloppoorviNoch keine Bewertungen

- Basics and Overview of Flip FlopsDokument5 SeitenBasics and Overview of Flip FlopsMariaNoch keine Bewertungen

- Practical: 13 To Study D Flip Flop: Sohil Vohra (Lecturer - Shri K.J. Polytechnic College, Bharuch (C.E. Deptt) )Dokument4 SeitenPractical: 13 To Study D Flip Flop: Sohil Vohra (Lecturer - Shri K.J. Polytechnic College, Bharuch (C.E. Deptt) )Sohil VohraNoch keine Bewertungen

- DSD Print 1Dokument11 SeitenDSD Print 1FS TamimNoch keine Bewertungen

- Day 11psnewDokument19 SeitenDay 11psnewEffecure HealthcareNoch keine Bewertungen

- ProjectDokument22 SeitenProjectSandeep SharmaNoch keine Bewertungen

- Acer Travelmate 6292Dokument104 SeitenAcer Travelmate 6292Uda SamatNoch keine Bewertungen

- Blue and White Corporate Illustrated Blue Connections PresentationDokument26 SeitenBlue and White Corporate Illustrated Blue Connections PresentationveroNoch keine Bewertungen

- As 400+Command+Line+Commands+ +supportDokument6 SeitenAs 400+Command+Line+Commands+ +supporthilgie2004Noch keine Bewertungen

- Iec 61850 Mms Client DatasheetDokument2 SeitenIec 61850 Mms Client DatasheetRishi DhimanNoch keine Bewertungen

- Installation Manual: Latest Update: 12/22/05Dokument28 SeitenInstallation Manual: Latest Update: 12/22/05casaharkonnenNoch keine Bewertungen

- Mine ManagementDokument24 SeitenMine ManagementsunilsinghmNoch keine Bewertungen

- Adobe IllustratorDokument56 SeitenAdobe IllustratorAbdul Raheym AhmadNoch keine Bewertungen

- Manual - Toll Information SystemDokument16 SeitenManual - Toll Information SystemSeth RockNoch keine Bewertungen

- Systems CN Storage San B-Type San40b-4 TSD03040USENDokument6 SeitenSystems CN Storage San B-Type San40b-4 TSD03040USENMona EvangelistaNoch keine Bewertungen

- DifferencesDokument7 SeitenDifferencesTheCodeTime TimeNoch keine Bewertungen

- Mantis Bug Tracking Tool - Step by Step ProceedureDokument186 SeitenMantis Bug Tracking Tool - Step by Step ProceedureTony Crown100% (1)

- 4 Manimagudam 01Dokument0 Seiten4 Manimagudam 01Sidran EdnihsNoch keine Bewertungen

- Cs Fie 2Dokument32 SeitenCs Fie 2abhinischal121Noch keine Bewertungen

- How To Setup LVM Hot SpareDokument1 SeiteHow To Setup LVM Hot SpareraviguruNoch keine Bewertungen

- Dewan Mohammad Mahbubur RahmanDokument3 SeitenDewan Mohammad Mahbubur RahmanMustafa Hussain100% (1)

- Maximo 61 UsersDokument520 SeitenMaximo 61 UsersMelisaNoch keine Bewertungen

- PHP Exercise 2013Dokument4 SeitenPHP Exercise 2013Helloworld King0% (1)

- Finite Element Modelling of Civil & Mining Excavations: SSR Analysis Using RS3Dokument1 SeiteFinite Element Modelling of Civil & Mining Excavations: SSR Analysis Using RS3innermanifestoNoch keine Bewertungen

- Nextcloud ManualDokument101 SeitenNextcloud Manualengineer rcpNoch keine Bewertungen

- UNIX Concepts: 1. How Are Devices Represented in UNIX?Dokument15 SeitenUNIX Concepts: 1. How Are Devices Represented in UNIX?api-3764166Noch keine Bewertungen

- Summer Internship Project Report On Web Development: Bachelor of Computer ApplicationsDokument19 SeitenSummer Internship Project Report On Web Development: Bachelor of Computer Applicationsits me Deepak yadavNoch keine Bewertungen

- LabVIEW-Core-1-Exercises-Manual (Exercise 2 - 1) Jonathan Juan Manuel Fiscal MalagaDokument7 SeitenLabVIEW-Core-1-Exercises-Manual (Exercise 2 - 1) Jonathan Juan Manuel Fiscal MalagaJonathan FiiscalNoch keine Bewertungen

- ICT 9 SummativeDokument2 SeitenICT 9 SummativeRamlede BenosaNoch keine Bewertungen

- Operating System AssignmentDokument13 SeitenOperating System AssignmentMarc AndalloNoch keine Bewertungen

- Huawei RTN Microwave DCN Solutions V1.3 (20101115)Dokument43 SeitenHuawei RTN Microwave DCN Solutions V1.3 (20101115)Gossan Anicet100% (2)

- Muhammad Ali: Career Objectives SkillsDokument2 SeitenMuhammad Ali: Career Objectives SkillsMaryam ZahraNoch keine Bewertungen

- Trasformadores para Sistema de Salida de AudioDokument17 SeitenTrasformadores para Sistema de Salida de AudioPedro BancayanNoch keine Bewertungen

- Mutual Fund Investments With Aadhaar Based Ekyc - FaqsDokument2 SeitenMutual Fund Investments With Aadhaar Based Ekyc - FaqsJnanam ShahNoch keine Bewertungen

- ReadmeDokument3 SeitenReadmeMiguel Juaniquina LimachiNoch keine Bewertungen