Beruflich Dokumente

Kultur Dokumente

Lab6a 2-Out-Of-5 To BCD Code Converter and Display Circuit

Hochgeladen von

MustafaAsimOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Lab6a 2-Out-Of-5 To BCD Code Converter and Display Circuit

Hochgeladen von

MustafaAsimCopyright:

Verfügbare Formate

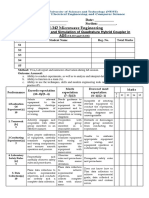

Faculty Member: _____________ Date: ___________

.

Semester: _______________ Section: __________ .

EE221 – Digital Logic Design Grp No.

Assessment Rubrics for Lab 5: Design of 2-out-of-5 to BCD Code Converter with Display

(CLO4, P4)

S. No. Student Name Reg. No. Total Marks

S1

S2

S3

S4

Method: Viva, Lab report and instructor evaluation and observation during lab session.

Outcome Assessed:

a. Ability to conduct experiments, as well as to analyze and interpret data (P).

b. Ability to function in a team (A).

c. Ability to use the techniques, skills and modern engineering tools necessary for engineering

practice (P).

Does not meet Marks

Exceeds expectation Meets expectation

Performance expectation

(10--9)/(5) (8--5)/(4-3)

(4--1)/(2--1) S1 S2 S3 S4

Selects relevant equipment

Needs guidance to select Incapable of selecting relevant

1. Realization to the experiment, develops

relevant equipment to the equipment to conduct the

Of setup diagrams of

experiment and to develop experiment, equipment

Experiment [c] equipment connections or

equipment connection or connection or wiring diagrams

10 wiring.

wiring diagrams. are unrecognizable.

Actively engages and

2. Teamwork Cooperates with other Distracts or discourages other

cooperates with other group

[b] group members in a group members from

members in an effective

5 reasonable manner. conducting the experiment.

manner.

Does proper calibration of

Calibrates equipment,

3. Conducting equipment, carefully Unable to calibrate appropriate

examines equipment and

Experiment [a] examines equipment and equipment and wiring, and

wiring of components and

5 wiring components, and equipment operation is

operates the equipment

ensures smooth operation substantially wrong.

with minor error.

and process.

4. Laboratory Respectfully and carefully Observes safety rules and

Disregards safety rules and

Safety Rules [a] observes safety rules and procedures With minor

procedures.

5 procedures. deviation.

Plans data collection to Plans data collection to Does not know how to Plan

5. Data achieve experimental achieve experimental data collection to achieve

Collection [a] objectives, and conducts an objectives, and collects experimental goals; data

10 orderly and a complete data complete data with minor collected is incomplete and

collection. error. contain errors.

EE-221: Digital Logic Design Page 1

Lab 6: Design of 2-out-of-5 to BCD Code Converter with Display

Lab 6: Part (a): Hardware implementation of 2-out-of-5 to BCD Code

Converter with Display

Lab6: Part (b): Gate-level Modeling in Verilog

This Lab Activity has been designed to familiarize the student with design and working of a 2-out-

of-5 to BCD Code Converter and numeric Display

Objectives:

Simplification of Boolean functions using Five-Variable map

Design of Code Converter block using Two-Level NAND gates.

System integration with BCD-to-Seven-Segment Decoder and Numeric readout for display.

Understanding the difference between common cathode and common anode displays

Lab Instructions

This lab activity comprises three parts, namely Pre-lab, Lab tasks, and Post-Lab Viva

session.

The lab report will be uploaded on LMS three days before scheduled lab date. The

students will get hard copy of lab report, complete the Pre-lab task before coming to

the lab and deposit it with teacher/lab engineer for necessary evaluation.

The students will start lab task and demonstrate design steps separately for step-wise

evaluation( course instructor/lab engineer will sign each step after ascertaining

functional verification)

Remember that a neat logic diagram with pins numbered coupled with nicely patched

circuit will simplify trouble-shooting process.

After the lab, students are expected to unwire the circuit and deposit back components

before leaving.

The Total duration for the lab is 3 hrs. After lab duration, a deduction of 5 marks

per day will be done for late submission.

A lab with in-complete lab tasks will not be accepted.

The students will complete lab task and submit complete report to Lab Engineer before

leaving lab.

There are related questions at the end of this activity. Give complete answers.

EE-221: Digital Logic Design Page 2

Pre-Lab Tasks: (4 marks)

1. What do you mean by non-weighted codes? Explain with Examples.

2. 7-Segment LED Displays are commonly used for displaying decimal Numbers (0 to 9). It can

also be used for displaying alphabets. A 7-Segment LED Displays essentially consist of

7 LEDs configured as shown below to display numbers. It comes in two configurations.

Common Cathode and Common Anode. Draw the diagram showing connections to drivers

and power source and ground for both configurations and highlight differences between

the two. Also give signal logic level required to light up the LEDs in the segment in each

configuration:

EE-221: Digital Logic Design Page 3

3. Complete the following table.

Inputs (2-out-of-5) Output(BCD)

A B C D E w x y z

4. Simplify the output functions w, x, y, and z using map method. Try to take maximum

advantage of don’t care conditions.

EE-221: Digital Logic Design Page 4

5. Draw logic diagram of the simplified expression

6. Draw logic diagram of the simplified expression (using NAND gates only)

EE-221: Digital Logic Design Page 5

Lab Tasks: (6 marks)

Lab Task 1

1. Implement the above circuit in hardware using minimum number of NAND gates at Two-

Levels and show the results to Teacher/Lab-Instructor.

2. Give complete schematics for your design including BCD-to-Seven-Segment driver IC and

read out. A Schematic is a logic diagram with pin numbering and IC Labeling on each gate.

EE-221: Digital Logic Design Page 6

3. Mention which configuration of 7-Segment Display did you use in Lab? If you were to use

the other configuration what change would you need in your circuit?

EE-221: Digital Logic Design Page 7

Lab Task 2:

4. Design and simulate the gate-level model of the circuit you patched. Give the code in the

space provided below.

module GR5(a,b,c,d,e,w,x,y,z);

input a,b,c,d,e;

output w,x,y,z;

wire w1,w2,w3,w4,w5,w6,w7,w8,w9,n1;

nand(w1,a,c);

nand(w2,a,d);

nand(w,w1,w2);

not(n1,a);

nand(w3,n1,b);

nand(w4,a,e);

nand(x,w3,w4);

nand(w5,n1,c);

nand(w6,a,e);

nand(y,w5,w6);

nand(w7,n1,d);

nand(w8,a,e);

nand(w9,a,c);

nand(z,w7,w8,w9);

endmodule

module testgr5();

EE-221: Digital Logic Design Page 8

reg A,B,C,D,E;

wire W,X,Y,Z;

GR5 testgr5(A,B,C,D,E,W,X,Y,Z);

initial

begin

A=1'b1;B=1'b1;C=1'b0;D=1'b0;E=1'b0;

#10 A=1'b0;B=1'b0;C=1'b0;D=1'b1;E=1'b1;

#10 A=1'b0;B=1'b0;C=1'b1;D=1'b0;E=1'b1;

#10 A=1'b0;B=1'b0;C=1'b1;D=1'b1;E=1'b0;

#10 A=1'b0;B=1'b1;C=1'b0;D=1'b0;E=1'b1;

#10 A=1'b0;B=1'b1;C=1'b0;D=1'b1;E=1'b0;

#10 A=1'b0;B=1'b1;C=1'b1;D=1'b0;E=1'b0;

#10 A=1'b1;B=1'b0;C=1'b0;D=1'b0;E=1'b1;

#10 A=1'b1;B=1'b0;C=1'b0;D=1'b1;E=1'b0;

#10 A=1'b1;B=1'b0;C=1'b1;D=1'b0;E=1'b0;

end

endmodule

EE-221: Digital Logic Design Page 9

EE-221: Digital Logic Design Page 10

Comments/Observations

EE-221: Digital Logic Design Page 11

Das könnte Ihnen auch gefallen

- Method Statement of Pipeline WorksDokument13 SeitenMethod Statement of Pipeline Worksमनिसभेटुवाल86% (21)

- ET410 Scope of The Capstone ProjectDokument5 SeitenET410 Scope of The Capstone ProjectGrantham UniversityNoch keine Bewertungen

- Practical Workbook (DSD)Dokument33 SeitenPractical Workbook (DSD)ayeshaNoch keine Bewertungen

- Dsplabmanual-By 22Dokument64 SeitenDsplabmanual-By 22debasnan singh100% (1)

- WS500 Operator WorkstationDokument2 SeitenWS500 Operator WorkstationNayants GuzmánNoch keine Bewertungen

- Awp Course FileDokument24 SeitenAwp Course FilevijaykannamallaNoch keine Bewertungen

- AWP Important Questions VipDokument2 SeitenAWP Important Questions VipdktcNoch keine Bewertungen

- DIP MCQsDokument4 SeitenDIP MCQsvijayaNoch keine Bewertungen

- Assessment of Rubrics For LAB Work (KSA-Model)Dokument1 SeiteAssessment of Rubrics For LAB Work (KSA-Model)Syed Hamza ArifNoch keine Bewertungen

- CS 510-Design and Analysis of Algorithms-Imdad Ullah KhanDokument3 SeitenCS 510-Design and Analysis of Algorithms-Imdad Ullah KhanASIMNoch keine Bewertungen

- Experiment No 1: 1. Study of Arm Evaluation SystemDokument30 SeitenExperiment No 1: 1. Study of Arm Evaluation SystemAshok KumarNoch keine Bewertungen

- FORMAT FOR 6th SEMESTER BTECH SYNOPSISDokument4 SeitenFORMAT FOR 6th SEMESTER BTECH SYNOPSISMahima DewanganNoch keine Bewertungen

- FDP BrochureDokument2 SeitenFDP BrochureajbioinfoNoch keine Bewertungen

- Feedback and Control Systems: Activity No. 2 - Time Response of Dynamic SystemsDokument15 SeitenFeedback and Control Systems: Activity No. 2 - Time Response of Dynamic SystemsYvesExequielPascuaNoch keine Bewertungen

- Ec3354-Signals and Systems-858759966-Ss QB - 2023-06-10T151453.626Dokument41 SeitenEc3354-Signals and Systems-858759966-Ss QB - 2023-06-10T151453.626Music LoverNoch keine Bewertungen

- Ec8691 - Microprocessors and Microcontrollers: Question BankDokument5 SeitenEc8691 - Microprocessors and Microcontrollers: Question Bankrkkumar07Noch keine Bewertungen

- C++ Output Based Questions - Set 2 CL1.1C++Dokument24 SeitenC++ Output Based Questions - Set 2 CL1.1C++Lakshay ChauhanNoch keine Bewertungen

- DAA Lab Manual VTUDokument41 SeitenDAA Lab Manual VTUManohar NV100% (2)

- Lab 5 Best First Search For SchedulingDokument3 SeitenLab 5 Best First Search For SchedulingchakravarthyashokNoch keine Bewertungen

- CAD & Design Flow: Motivation: Microelectronics Design EfficiencyDokument18 SeitenCAD & Design Flow: Motivation: Microelectronics Design EfficiencyJubin JainNoch keine Bewertungen

- Lab Report 1 PDFDokument6 SeitenLab Report 1 PDFmr xyzNoch keine Bewertungen

- Machine Learning Unit 2 MCQDokument17 SeitenMachine Learning Unit 2 MCQHarsh Preet SinghNoch keine Bewertungen

- CS 2255 Control Systems Question BankDokument62 SeitenCS 2255 Control Systems Question BankreporterrajiniNoch keine Bewertungen

- Hardware Software Codesign Question PaperDokument2 SeitenHardware Software Codesign Question PaperRaviNoch keine Bewertungen

- Baseband Pulse Transmission: Presented by Asst. Professor ECE DepartmentDokument47 SeitenBaseband Pulse Transmission: Presented by Asst. Professor ECE DepartmentImran BashaNoch keine Bewertungen

- Be B.tech 2001 20.01.05Dokument16 SeitenBe B.tech 2001 20.01.05Madhu SundarNoch keine Bewertungen

- Co-Po Big Data AnalyticsDokument41 SeitenCo-Po Big Data AnalyticssuniNoch keine Bewertungen

- Multistage BackwardDokument13 SeitenMultistage BackwardRama SugavanamNoch keine Bewertungen

- Electroma: News LetterDokument5 SeitenElectroma: News LetterKhushi SinghNoch keine Bewertungen

- Model QP - MPMC Lab - Wo Split UpDokument3 SeitenModel QP - MPMC Lab - Wo Split Upsujaganesan20090% (1)

- SCILAB DSP Lab Manual Scilab (12-13)Dokument70 SeitenSCILAB DSP Lab Manual Scilab (12-13)Akkonduru KumarNoch keine Bewertungen

- Rr311901 Digital Systems DesignDokument8 SeitenRr311901 Digital Systems DesignSrinivasa Rao GNoch keine Bewertungen

- 21mat31 Model Question Paper VTU 3rd Sem 21 SchemeDokument4 Seiten21mat31 Model Question Paper VTU 3rd Sem 21 Schemeyoung flierNoch keine Bewertungen

- Me2255 Electronics and Microprocessor Anna University Question BankDokument6 SeitenMe2255 Electronics and Microprocessor Anna University Question BankMayakannan RNoch keine Bewertungen

- Embedded System Lab ManualDokument67 SeitenEmbedded System Lab Manualsaim100% (1)

- CH 2 Raster Scan GraphicsDokument23 SeitenCH 2 Raster Scan GraphicskanchangawndeNoch keine Bewertungen

- TLW Question PapersDokument6 SeitenTLW Question PapersManjunath ShimogaNoch keine Bewertungen

- BMS Institute of Technology PDFDokument53 SeitenBMS Institute of Technology PDFKaruna nidhan tiwari ECE-2016-20Noch keine Bewertungen

- Genetic AlgorithmDokument33 SeitenGenetic Algorithmsuhas199Noch keine Bewertungen

- Internship PPT FormatDokument11 SeitenInternship PPT FormatDhanush V NNoch keine Bewertungen

- Accreditation and Outcome Based Learning: WWW - Ide.iitkgp - Ernet.inDokument32 SeitenAccreditation and Outcome Based Learning: WWW - Ide.iitkgp - Ernet.inUma Shankar YaligarNoch keine Bewertungen

- Microprocessor ProgramDokument97 SeitenMicroprocessor ProgramPaulNoch keine Bewertungen

- Computer Science and Engineering 1st YearDokument11 SeitenComputer Science and Engineering 1st YearGolamSarwarNoch keine Bewertungen

- Neural Network Two Mark Q.BDokument19 SeitenNeural Network Two Mark Q.BMohanvel2106Noch keine Bewertungen

- Computer Organization and ArchitectureDokument3 SeitenComputer Organization and ArchitectureAnil MarsaniNoch keine Bewertungen

- BM2406 Digital Image Processing Lab ManualDokument107 SeitenBM2406 Digital Image Processing Lab ManualDeepak DennisonNoch keine Bewertungen

- DS Lab Manual-1Dokument63 SeitenDS Lab Manual-1Amogh SkNoch keine Bewertungen

- Ecad Lab ManualDokument55 SeitenEcad Lab Manualjeravi84100% (3)

- Packed BCD To Unpacked BCDDokument5 SeitenPacked BCD To Unpacked BCDRajveer JainNoch keine Bewertungen

- R7411009-Artificial Neural NetworksDokument4 SeitenR7411009-Artificial Neural NetworkssivabharathamurthyNoch keine Bewertungen

- LectureNotes Antennas DR - SerkanaksoyDokument13 SeitenLectureNotes Antennas DR - SerkanaksoyRahil HusainNoch keine Bewertungen

- Epl Electronics Lab ManualDokument40 SeitenEpl Electronics Lab ManualSivarama Krishnan SNoch keine Bewertungen

- 1st - PPT Fire FightingDokument18 Seiten1st - PPT Fire FightingsuprajaNoch keine Bewertungen

- MCQDokument7 SeitenMCQ19himaniNoch keine Bewertungen

- OBE For Students of SSUETDokument26 SeitenOBE For Students of SSUETAnilaSaghirNoch keine Bewertungen

- DWT PPTDokument16 SeitenDWT PPTnaveensilveri100% (2)

- CMC - Important QuestionsDokument4 SeitenCMC - Important QuestionsVenkatesh Patnala SoniNoch keine Bewertungen

- Relational Data Model A Complete Guide - 2020 EditionVon EverandRelational Data Model A Complete Guide - 2020 EditionNoch keine Bewertungen

- Lab 6 - 2-Out-Of-5 To BCD Code Converter With DisplayDokument8 SeitenLab 6 - 2-Out-Of-5 To BCD Code Converter With DisplaySanan yaqoobNoch keine Bewertungen

- Lab Report 10Dokument5 SeitenLab Report 10Samir KhanNoch keine Bewertungen

- Algebra and FuntionsDokument22 SeitenAlgebra and FuntionsMustafaAsimNoch keine Bewertungen

- c2 Important Points Revision CardsDokument1 Seitec2 Important Points Revision CardsMustafaAsimNoch keine Bewertungen

- Sketching CurvesDokument33 SeitenSketching CurvesMustafaAsimNoch keine Bewertungen

- Core 1 Revision CardsDokument16 SeitenCore 1 Revision CardsMustafaAsimNoch keine Bewertungen

- Sequence and Series RevisionDokument1 SeiteSequence and Series RevisionMustafaAsimNoch keine Bewertungen

- InventoryOverview HN (08.05.2023)Dokument15 SeitenInventoryOverview HN (08.05.2023)Văn Thế NamNoch keine Bewertungen

- Plumbing Fixture CatalogueDokument10 SeitenPlumbing Fixture CatalogueNoemi D. BreñaNoch keine Bewertungen

- Manual PSW 2600Dokument18 SeitenManual PSW 2600Jc C. GomezNoch keine Bewertungen

- PDFDokument255 SeitenPDFwrite2arshad_mNoch keine Bewertungen

- Metalco Valve TianjinDokument20 SeitenMetalco Valve TianjinsathishNoch keine Bewertungen

- Pile Cap Design 4pilesDokument6 SeitenPile Cap Design 4pilesabshawNoch keine Bewertungen

- Pace Power System Presentation - 0Dokument15 SeitenPace Power System Presentation - 0everetteNoch keine Bewertungen

- KEDDCO BinderDokument74 SeitenKEDDCO BinderWillian FigueroaNoch keine Bewertungen

- Below Which Not More Than 5 Percent of The Test Results Are Expected To Fall"Dokument13 SeitenBelow Which Not More Than 5 Percent of The Test Results Are Expected To Fall"shravan iitmNoch keine Bewertungen

- Exception Handling Notes For Vtu StudentsDokument42 SeitenException Handling Notes For Vtu StudentshelloNoch keine Bewertungen

- Tutorial Questions and Answers - 2011Dokument10 SeitenTutorial Questions and Answers - 2011Jan ScarNoch keine Bewertungen

- XCMG Construction Machinery Co., LTDDokument4 SeitenXCMG Construction Machinery Co., LTD余Noch keine Bewertungen

- Pile Foundations in Engineering Practice by S - by Civildatas - Blogspot.inDokument784 SeitenPile Foundations in Engineering Practice by S - by Civildatas - Blogspot.inTatiana RodríguezNoch keine Bewertungen

- Códigos de Falhas Hyundai R3607ADokument13 SeitenCódigos de Falhas Hyundai R3607AGuemep GuemepNoch keine Bewertungen

- 16PPE723Dokument2 Seiten16PPE723DrArun KaliappanNoch keine Bewertungen

- Customizing The ADFS Sign-In PagesDokument4 SeitenCustomizing The ADFS Sign-In Pagesmicu0% (1)

- Advanced Techniques in Power System Protective Relaying PDFDokument332 SeitenAdvanced Techniques in Power System Protective Relaying PDFshashikant yadavNoch keine Bewertungen

- Bomba de Vácuo Sotorbilt 4mrDokument12 SeitenBomba de Vácuo Sotorbilt 4mrWormInchNoch keine Bewertungen

- Tension Capacity of PileDokument8 SeitenTension Capacity of Pilenimal179100% (1)

- ECE320 Chapter 3 PDFDokument23 SeitenECE320 Chapter 3 PDFAhsan NisarNoch keine Bewertungen

- Sample Electrical LayoutDokument1 SeiteSample Electrical LayoutBentesais Bente UnoNoch keine Bewertungen

- PDRXDokument4 SeitenPDRXNeel AdwaniNoch keine Bewertungen

- 592-A2GA DesbloqueadoDokument27 Seiten592-A2GA DesbloqueadoVicktor GranadosNoch keine Bewertungen

- Investigate The Natural Time Period, Base Shear, Displacement, Story Drift, Story Stiffness by Etabs and Staad ProDokument4 SeitenInvestigate The Natural Time Period, Base Shear, Displacement, Story Drift, Story Stiffness by Etabs and Staad ProEditor IJTSRDNoch keine Bewertungen

- Know It BrochureDokument8 SeitenKnow It BrochureSonali SinhaNoch keine Bewertungen

- 02 Chain Surveying PDFDokument47 Seiten02 Chain Surveying PDFch_nadeemhussain50% (2)

- Starboard Strategies Issue 13-MinDokument28 SeitenStarboard Strategies Issue 13-MinkrishnamrutamNoch keine Bewertungen

- Jaybird Bluebuds X ManualDokument1 SeiteJaybird Bluebuds X Manualeduardi7720Noch keine Bewertungen