Beruflich Dokumente

Kultur Dokumente

Isl 83202

Hochgeladen von

prithivirajOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Isl 83202

Hochgeladen von

prithivirajCopyright:

Verfügbare Formate

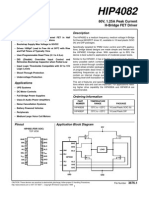

DATASHEET

ISL83202 FN6382

55V, 1A Peak Current H-Bridge FET Driver Rev.0.00

December 20, 2006

The ISL83202 is a medium-frequency H-Bridge FET driver Features

capable of 1A (typ) of peak drive current that is designed to

drive high- and low-side N-Channel MOSFETs in medium- • Independently Drives 4 N-Channel FETs in Half Bridge or

Full Bridge Configurations

voltage applications. Optimized for PWM motor control and

uninterruptible power supply systems, the ISL83202 enables • Bootstrap Supply Max Voltage: 70VDC

simple and flexible bridge-based design. With typical input-

• Drives a 1000pF Load in Free Air at +50°C with Rise and

to-output propagation delays as low as 25ns and with a user- Fall Times of 15ns (typ)

programmable dead-time range of 0.1µs to 4.5µs, the

ISL83202 is ideal for switching frequencies up to 200kHz. • User-Programmable Dead Time from 0.1 to 4.5s

The dead-time of the ISL83202 is programmable via a single • DIS (Disable) Overrides Input Control and Refreshes

Bootstrap Capacitor when Pulled Low

resistor. The ISL83202's four independent driver control

inputs (ALI, AHI, BLI, and BHI) allow driving of every • Input Logic Thresholds Compatible with 5V to 15V Logic

possible switch combination except those that would cause Levels

a shoot-through condition. A global disable input, DIS, • Shoot-Through Protection

overrides input control and causes the ISL83202 to refresh

the bootstrap capacitor when pulled low. Integrated • Undervoltage Protection

undervoltage protection and shoot-through protection ensure • Pb-Free Plus Anneal Available (RoHS Compliant)

reliable system operation.

The ISL83202 is available in compact 16 Ld SOIC and 16 Ld

Applications

PDIP packages and operates over the range of -55°C to • UPS Systems

+125°C.

• DC Motor Controls

Ordering Information • Full Bridge Power Supplies

PART PART TEMP. PKG. • Switching Power Amplifiers

NUMBER MARKING RANGE (°C) PACKAGE DWG. #

• Noise Cancellation Systems

ISL83202IBZ 83202IBZ -55 to +125 16 Ld SOIC (N) M16.15

(Note) (Pb-free) • Battery Powered Vehicles

ISL83202IBZT 16 Ld SOIC (N) Tape and Reel M16.15 • Peripherals

(Note) (Pb-free)

• Medium/Large Voice Coil Motors

ISL83202IPZ ISL83202IPZ -55 to +125 16 Ld PDIP** E16.3

(Note) (Pb-free)

• Related Literature

- TB363, Guidelines for Handling and Processing

NOTE: Intersil Pb-free plus anneal products employ special Pb-free Moisture Sensitive Surface Mount Devices (SMDs)

material sets; molding compounds/die attach materials and 100%

matte tin plate termination finish, which are RoHS compliant and

compatible with both SnPb and Pb-free soldering operations. Intersil

Pinout

Pb-free products are MSL classified at Pb-free peak reflow ISL83202

temperatures that meet or exceed the Pb-free requirements of IPC/ (PDIP, SOIC)

JEDEC J STD-020. TOP VIEW

**Pb-free PDIPs can be used for through hole wave solder processing

only. They are not intended for use in Reflow solder processing BHB 1 16 BHO

applications.

BHI 2 15 BHS

BLI 3 14 BLO

ALI 4 13 ALO

DEL 5 12 VDD

VSS 6 11 AHS

AHI 7 10 AHO

DIS 8 9 AHB

FN6382 Rev.0.00 Page 1 of 12

December 20, 2006

ISL83202

Application Block Diagram

55V

12V

BHO

BHS

LOAD

BHI BLO

BLI

ISL83202

ALI ALO

AHI AHS

AHO

GND GND

Functional Block Diagram

9 AHB BHB 1

DRIVER DRIVER

LEVEL LEVEL

U/V 10 AHO BHO 16 U/V

SHIFT SHIFT

BHI 2

11 AHS BHS 15

AHI 7 TURN-ON TURN-ON

DELAY DELAY

DIS 8

VDD

DETECTOR DRIVER DRIVER

VDD 12 UNDERVOLTAGE TURN-ON TURN-ON

DELAY 13 ALO BLO 14

DELAY

ALI 4

DEL 5

BLI 3

VSS 6

FN6382 Rev.0.00 Page 2 of 12

December 20, 2006

ISL83202

Typical Application (PWM Mode Switching)

55V

1 BHB BHO 16

12V 2 BHI BHS 15

BLO 14 LOAD

3 BLI

PWM

4 ALI ALO 13

INPUT

12V

5 DEL VDD 12

DELAY RESISTOR 6 VSS AHS 11

7 AHI AHO 10

DIS 8 DIS AHB 9

FROM GND

OPTIONAL

OVERCURRENT

LATCH

RDIS

TO OPTIONAL +

CURRENT CONTROLLER OR -

OVERCURRENT LATCH

RSH

GND

FN6382 Rev.0.00 Page 3 of 12

December 20, 2006

ISL83202

Absolute Maximum Ratings Thermal Information

Supply Voltage, VDD . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to 16V Thermal Resistance JA (°C/W)

Logic I/O Voltages . . . . . . . . . . . . . . . . . . . . . . . -0.3V to VDD +0.3V SOIC Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Voltage on AHS, BHS . . . . -6V (Transient) to 65V (-55°C to+150°C) PDIP Package* . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Voltage on AHB, BHB . . . . . . . . VAHS, BHS -0.3V to VAHS, BHS +VDD Maximum Power Dissipation. . . . . . . . . . . . . . . . . . . . . . . . See Curve

Voltage on ALO, BLO. . . . . . . . . . . . . . . . . . VSS -0.3V to VDD +0.3V Storage Temperature Range . . . . . . . . . . . . . . . . . .-65°C to +150°C

Voltage on AHO, BHO . . . VAHS, BHS -0.3V to VAHB, BHB +0.3V Input Operating Max. Junction Temperature. . . . . . . . . . . . . . . . . . +150°C

Current, DEL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -5mA to 0mA Lead Temperature (Soldering 10s) . . . . . . . . . . . . . . . . . . . . +300°C

Phase Slew Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20V/ns (For SOIC - Lead Tips Only))

NOTE: All voltages are relative VSS unless otherwise specified. *Pb-free PDIPs can be used for through hole wave solder

processing only. They are not intended for use in Reflow solder

Operating Conditions processing applications.

Supply Voltage, VDD . . . . . . . . . . . . . . . . . . . . . . . . . +8.5V to +15V

Voltage on VSS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -1.0V to +1.0V

Voltage on AHB, BHB . . . . . . . . . . . . . . . . . . . . . . . . . . -1V to +55V

Voltage on AHB, BHB . . . . . . . . VAHS, BHS +7.5V to VAHS, BHS +VDD

Input Current, DEL . . . . . . . . . . . . . . . . . . . . . . . . . -4mA to -100A

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

+150°C max junction temperature is intended for short periods of time to prevent shortening the lifetime. Operation close to +150°C junction may trigger the shutdown of

the device even before +150°C, since this number is specified as typical.

Electrical Specifications VDD = VAHB = VBHB = 12V, VSS = VAHS = VBHS = 0V, RDEL = 100k

TJ = -55°C

TJ = +25°C TO +150°C

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX MIN MAX UNITS

SUPPLY CURRENTS AND UNDER VOLTAGE PROTECTION

VDD Quiescent Current IDD All inputs = 0V, RDEL = 100k 1.2 2.3 3.5 0.85 4 mA

All inputs = 0V, RDEL = 10k 2.2 4.0 5.5 1.9 6.0 mA

VDD Operating Current IDDO f = 50kHz, no load 1.5 2.6 4.0 1.1 4.2 mA

50kHz, no load, RDEL = 10k 2.5 4.0 6.4 2.1 6.6 mA

AHB, BHB Off Quiescent Current IAHBL, IBHBL AHI = BHI = 0V 0.5 1.0 1.5 0.4 1.6 mA

AHB, BHB On Quiescent Current IAHBH, IBHBH AHI = BHI = VDD 65 145 240 40 250 A

AHB, BHB Operating Current IAHBO, IBHBO f = 50kHz, CL = 1000pF .65 1.1 1.8 .45 2.0 mA

AHS, BHS Leakage Current IHLK VAHS = VBHS = 55V - - 1.0 - - A

VAHB = VBHB = 70V

VDD = Not Connected

VDD Rising Undervoltage Threshold VDDUV+ 6.8 7.6 8.25 6.5 8.5 V

VDD Falling Undervoltage Threshold VDDUV- 6.5 7.1 7.8 6.25 8.1 V

Undervoltage Hysteresis UVHYS 0.17 0.4 0.75 0.15 0.90 V

AHB, BHB Undervoltage Threshold VHBUV Referenced to AHS and BHS 5 6.0 7 4.5 7.5 V

INPUT PINS: ALI, BLI, AHI, BHI, and DIS

Low Level Input Voltage VIL Full Operating Conditions - - 1.0 - 0.8 V

High Level Input Voltage VIH Full Operating Conditions 2.5 - - 2.7 V

Input Voltage Hysteresis - 35 - - - mV

Low Level Input Current IIL VIN = 0V, Full Operating Conditions -145 -100 -60 -150 -50 A

High Level Input Current IIH VIN = 5V, Full Operating Conditions -1 - +1 -10 +10 A

TURN-ON DELAY PIN DEL

Dead Time TDEAD RDEL = 100k 2.5 4.5 8.0 2.0 8.5 s

RDEL = 10k 0.27 0.5 0.75 0.2 0.85 s

FN6382 Rev.0.00 Page 4 of 12

December 20, 2006

ISL83202

Electrical Specifications VDD = VAHB = VBHB = 12V, VSS = VAHS = VBHS = 0V, RDEL = 100k (Continued)

TJ = -55°C

TJ = +25°C TO +150°C

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX MIN MAX UNITS

GATE DRIVER OUTPUT PINS: ALO, BLO, AHO, and BHO

Low Level Output Voltage VOL IOUT = 50mA 0.65 1.1 0.5 1.2 V

High Level Output Voltage VDD-VOH IOUT = -50mA 0.7 1.2 0.5 1.3 V

Peak Pullup Current IO + VOUT = 0V 1.0 0.6 2.0 A

Peak Pulldown Current IO - VOUT = 12V 1.0 0.6 2.0 A

Switching Specifications VDD = VAHB = VBHB = 12V, VSS = VAHS = VBHS = 0V, RDEL= 100k, CL = 1000pF.

TJ = -55°C TO

TJ = +25°C +150°C

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX MIN MAX UNITS

Lower Turn-off Propagation Delay TLPHL - 25 50 - 70 ns

(ALI-ALO, BLI-BLO)

Upper Turn-off Propagation Delay THPHL - 55 80 - 100 ns

(AHI-AHO, BHI-BHO)

Lower Turn-on Propagation Delay TLPLH - 40 85 - 100 ns

(ALI-ALO, BLI-BLO)

Upper Turn-on Propagation Delay THPLH - 75 110 - 150 ns

(AHI-AHO, BHI-BHO)

Rise Time TR - 9 20 - 25 ns

Fall Time TF - 9 20 - 25 ns

Minimum Input Pulse Width TPWIN-ON/OFF 50 - - 50 - ns

Output Pulse Response to 50ns Input Pulse TPWOUT 63 80 ns

Disable Turn-off Propagation Delay TDISLOW - 50 80 - 90 ns

(DIS - Lower Outputs)

Disable Turn-off Propagation Delay TDISHIGH - 75 100 - 125 ns

(DIS - Upper Outputs)

Disable Turn-on Propagation Delay TDLPLH - 40 70 - 100 ns

(DIS - ALO and BLO)

Disable Turn-on Propagation Delay TDHPLH RDEL = 10k - 1.2 2 - 3 s

(DIS- AHO and BHO)

Refresh Pulse Width (ALO and BLO) TREF-PW 375 580 900 350 950 ns

TRUTH TABLE

INPUT OUTPUT

ALI, BLI AHI, BHI VDDUV VHBUV DIS ALO, BLO AHO, BHO

X X X X 1 0 0

X X 1 X X 0 0

0 X 0 1 0 0 0

1 X 0 X 0 1 0

0 1 0 0 0 0 1

0 0 0 0 0 0 0

NOTE: X signifies that input can be either a “1” or “0”.

FN6382 Rev.0.00 Page 5 of 12

December 20, 2006

ISL83202

Pin Descriptions

PIN

NUMBE

R SYMBOL DESCRIPTION

1 BHB B High-side Bootstrap supply. External bootstrap diode and capacitor are required. Connect cathode of bootstrap diode

and positive side of bootstrap capacitor to this pin.

2 BHI B High-side Input. Logic level input that controls BHO driver (Pin 16). BLI (Pin 3) high level input overrides BHI high level

input to prevent half-bridge shoot-through, see Truth Table. DIS (Pin 8) high level input overrides BHI high level input. The

pin can be driven by signal levels of 0V to 15V (no greater than VDD).

3 BLI B Low-side Input. Logic level input that controls BLO driver (Pin 14). If BHI (Pin 2) is driven high or not connected externally

then BLI controls both BLO and BHO drivers, with dead time set by delay currents at DEL (Pin 5). DIS (Pin 8) high level

input overrides BLI high level input. The pin can be driven by signal levels of 0V to 15V (no greater than VDD).

4 ALI A Low-side Input. Logic level input that controls ALO driver (Pin 13). If AHI (Pin 7) is driven high or not connected externally

then ALI controls both ALO and AHO drivers, with dead time set by delay currents at DEL (Pin 5). DIS (Pin 8) high level

input overrides ALI high level input. The pin can be driven by signal levels of 0V to 15V (no greater than VDD).

5 DEL Turn-on DELay. Connect resistor from this pin to VSS to set timing current that defines the dead time between drivers. All

drivers turn-off with no adjustable delay, so the DEL resistor guarantees no shoot-through by delaying the turn-on of all

drivers. The voltage across the DEL resistor is approximately VDD -2V.

6 VSS Chip negative supply, generally will be ground.

7 AHI A High-side Input. Logic level input that controls AHO driver (Pin 10). ALI (Pin 4) high level input overrides AHI high level

input to prevent half-bridge shoot-through, see Truth Table. DIS (Pin 8) high level input overrides AHI high level input. The

pin can be driven by signal levels of 0V to 15V (no greater than VDD).

8 DIS DISable input. Logic level input that when taken high sets all four outputs low. DIS high overrides all other inputs. When

DIS is taken low the outputs are controlled by the other inputs. The pin can be driven by signal levels of 0V to 15V (no

greater than VDD).

9 AHB A High-side Bootstrap supply. External bootstrap diode and capacitor are required. Connect cathode of bootstrap diode

and positive side of bootstrap capacitor to this pin.

10 AHO A High-side Output. Connect to gate of A High-side power MOSFET.

11 AHS A High-side Source connection. Connect to source of A High-side power MOSFET. Connect negative side of bootstrap

capacitor to this pin.

12 VDD Positive supply to control logic and lower gate drivers. De-couple this pin to VSS (Pin 6).

13 ALO A Low-side Output. Connect to gate of A Low-side power MOSFET.

14 BLO B Low-side Output. Connect to gate of B Low-side power MOSFET.

15 BHS B High-side Source connection. Connect to source of B High-side power MOSFET. Connect negative side of bootstrap

capacitor to this pin.

16 BHO B High-side Output. Connect to gate of B High-side power MOSFET.

FN6382 Rev.0.00 Page 6 of 12

December 20, 2006

ISL83202

Timing Diagrams

X = A OR B, A AND B HALVES OF BRIDGE CONTROLLER ARE INDEPENDENT

TLPHL THPHL

DIS=0

and UV

XLI

XHI

XLO

XHO

THPLH TLPLH TR TF

(10% - 90%) (10% - 90%)

FIGURE 1. INDEPENDENT MODE

DIS=0

and UV

XLI

XHI = HI OR NOT CONNECTED

XLO

XHO

FIGURE 2. BISTATE MODE

TDLPLH TDIS

TREF-PW

DIS or UV

XLI

XHI

XLO

XHO

TDHPLH

FIGURE 3. DISABLE FUNCTION

FN6382 Rev.0.00 Page 7 of 12

December 20, 2006

ISL83202

Performance Curves

3.5 16

15 200kHz

3.25

VDD = 16V 14

IDD SUPPLY CURRENT (mA)

IDD SUPPLY CURRENT (mA)

VDD = 15V

3 13

12

2.75

11

2.5 VDD = 12V 10 100kHz

9

2.25 VDD = 10V 8

7 50kHz

2

6

1.75 VDD = 8V

5 10kHz

1.5 4

-60 -40 -20 0 20 40 60 80 100 120 140 -60 -40 -20 0 20 40 60 80 100 120 140

JUNCTION TEMPERATURE (°C) JUNCTION TEMPERATURE (°C)

FIGURE 4. IDD SUPPLY CURRENT vs TEMPERATURE AND FIGURE 5. VDD SUPPLY CURRENT vs TEMPERATURE AND

VDD SUPPLY VOLTAGE SWITCHING FREQUENCY (1000pF LOAD)

8 2

LOADED, NL BIAS CURRENTS (mA)

7

1.75

PEAK GATE CURRENT (A)

6

1.5

5

4 1.25

1000pF LOAD SOURCE and SINK

3 1

NO LOAD

2

0.75

1

0.5

0 8 9 10 11 12 13 14 15

0 50 100 150 200 BIAS

FREQUENCY (kHz) BIAS SUPPLY VOLTAGE (V) AT +25°C

FIGURE 6. FLOATING (IXHB) BIAS CURRENT vs FIGURE 7. GATE SOURCE/SINK PEAK CURRENT vs BIAS

FREQUENCY AND LOAD SUPPLY VOLTAGE AT +25°C

1.2

1.4

-40°C

SINK/SOURCE CURRENT (A)

1.1 0°C

-55°C +25°C

1.2

NORMALIZED GATE

VDD-VOH (V)

1 1

+125°C +150°C

0.8

0.9

0.6

0.8

-75 -50 -25 0 25 50 75 100 125 150 8 9 10 11 12 13 14 15

JUNCTION TEMPERATURE (°C) VDD SUPPLY VOLTAGE (V)

FIGURE 8. GATE CURRENT vs TEMPERATURE, FIGURE 9. VDD-VOH vs BIAS VOLTAGE TEMPERATURE

NORMALIZED TO +25°C

FN6382 Rev.0.00 Page 8 of 12

December 20, 2006

ISL83202

Performance Curves (Continued)

8

1.4 LOWER U/V RESET

VDD, BIAS SUPPLY VOLTAGE (V)

7.5

1.2

7

-40°C 0°C LOWER U/V SET

-55°C +25°C

VOL (V)

1 6.5

0.8 6

+125°C UPPER U/V SET/RESET

+150°C 5.5

0.6

5

8 9 10 11 12 13 14 15 -60 -40 -20 0 20 40 60 80 100 120 140 160

VDD SUPPLY VOLTAGE (V) JUNCTION TEMPERATURE (°C)

FIGURE 10. VOL vs BIAS VOLTAGE AND TEMPERATURE FIGURE 11. UNDERVOLTAGE TRIP VOLTAGES vs

TEMPERATURE

100 104

90 DIS TO TURN-ON/OFF TIME (ns)

PROPAGATION DELAYS (ns)

80 UPPER tON DISHTON

1000

70

60 UPPER tOFF

50 LOWER tON

100 DISHTOFF

40

30 LOWER tOFF DISLOFF

DISLTON

20 10

-60 -40 -20 0 20 40 60 80 100 120 140 160 -60 -40 -20 0 20 40 60 80 100 120 140 160

JUNCTION TEMPERATURE (°C) JUNCTION TEMPERATURE (°C)

FIGURE 12. UPPER LOWER TURN-ON / TURN-OFF FIGURE 13. UPPER/LOWER DIS(ABLE) TO TURN-ON/OFF vs

PROPAGATION DELAY vs TEMPERATURE TEMPERATURE (°C)

2 2.5

TOTAL POWER DISSIPATION (W)

LEVEL-SHIFT CURRENT (mA)

1.5 16 PIN DIP

1.5

SOIC

1

1

0.5

QUIESCENT BIAS COMPONENT

0.5 0

0 20 40 60 80 100 -60 -30 0 30 60 90 120 150

SWITCHING FREQUENCY (kHz) AMBIENT TEMPERATURE (°C)

FIGURE 14. FULL BRIDGE LEVEL-SHIFT CURRENT vs FIGURE 15. MAXIMUM POWER DISSIPATION vs AMBIENT

FREQUENCY (kHz) TEMPERATURE

FN6382 Rev.0.00 Page 9 of 12

December 20, 2006

ISL83202

Performance Curves (Continued)

104

VDD = 15V

DEAD TIME (ns)

VDD = 12V

1000 VDD = 9V

100

0 10 20 30 40 50 60 70 80 90 100

DEAD TIME RESISTANCE (k)

FIGURE 16. DEAD-TIME vs DEL RESISTANCE AND BIAS SUPPLY (VDD) VOLTAGE

FN6382 Rev.0.00 Page 10 of 12

December 20, 2006

ISL83202

Dual-In-Line Plastic Packages (PDIP)

N

E16.3 (JEDEC MS-001-BB ISSUE D)

E1 16 LEAD DUAL-IN-LINE PLASTIC PACKAGE

INDEX

AREA 1 2 3 N/2

INCHES MILLIMETERS

-B- SYMBOL MIN MAX MIN MAX NOTES

-A- A - 0.210 - 5.33 4

D E

BASE A1 0.015 - 0.39 - 4

PLANE A2

-C- A A2 0.115 0.195 2.93 4.95 -

SEATING

PLANE B 0.014 0.022 0.356 0.558 -

L C

L

B1 0.045 0.070 1.15 1.77 8, 10

D1 A1 eA

D1

B1 e C 0.008 0.014 0.204 0.355 -

eC C

B D 0.735 0.775 18.66 19.68 5

eB

0.010 (0.25) M C A B S

D1 0.005 - 0.13 - 5

NOTES: E 0.300 0.325 7.62 8.25 6

1. Controlling Dimensions: INCH. In case of conflict between English and E1 0.240 0.280 6.10 7.11 5

Metric dimensions, the inch dimensions control.

e 0.100 BSC 2.54 BSC -

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Symbols are defined in the “MO Series Symbol List” in Section 2.2 of eA 0.300 BSC 7.62 BSC 6

Publication No. 95. eB - 0.430 - 10.92 7

4. Dimensions A, A1 and L are measured with the package seated in JE- L 0.115 0.150 2.93 3.81 4

DEC seating plane gauge GS-3.

N 16 16 9

5. D, D1, and E1 dimensions do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.010 inch (0.25mm). Rev. 0 12/93

6. E and eA are measured with the leads constrained to be perpendic-

ular to datum -C- .

7. eB and eC are measured at the lead tips with the leads unconstrained.

eC must be zero or greater.

8. B1 maximum dimensions do not include dambar protrusions. Dambar

protrusions shall not exceed 0.010 inch (0.25mm).

9. N is the maximum number of terminal positions.

10. Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3,

E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

FN6382 Rev.0.00 Page 11 of 12

December 20, 2006

ISL83202

Small Outline Plastic Packages (SOIC)

N M16.15 (JEDEC MS-012-AC ISSUE C)

INDEX 16 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

AREA H 0.25(0.010) M B M

E INCHES MILLIMETERS

SYMBOL MIN MAX MIN MAX NOTES

-B-

A 0.0532 0.0688 1.35 1.75 -

1 2 3 A1 0.0040 0.0098 0.10 0.25 -

L

B 0.013 0.020 0.33 0.51 9

SEATING PLANE

C 0.0075 0.0098 0.19 0.25 -

-A-

D A h x 45° D 0.3859 0.3937 9.80 10.00 3

E 0.1497 0.1574 3.80 4.00 4

-C- e 0.050 BSC 1.27 BSC -

e H 0.2284 0.2440 5.80 6.20 -

A1

C

h 0.0099 0.0196 0.25 0.50 5

B 0.10(0.004)

L 0.016 0.050 0.40 1.27 6

0.25(0.010) M C A M B S

N 16 16 7

NOTES: 0° 8° 0° 8° -

1. Symbols are defined in the “MO Series Symbol List” in Section 2.2 of Rev. 1 6/05

Publication Number 95.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Dimension “D” does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006

inch) per side.

4. Dimension “E” does not include interlead flash or protrusions. Interlead

flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

5. The chamfer on the body is optional. If it is not present, a visual index

feature must be located within the crosshatched area.

6. “L” is the length of terminal for soldering to a substrate.

7. “N” is the number of terminal positions.

8. Terminal numbers are shown for reference only.

9. The lead width “B”, as measured 0.36mm (0.014 inch) or greater above

the seating plane, shall not exceed a maximum value of 0.61mm

(0.024 inch).

10. Controlling dimension: MILLIMETER. Converted inch dimensions are

not necessarily exact.

© Copyright Intersil Americas LLC 2006. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted

in the quality certifications found at www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such

modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are

current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its

subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN6382 Rev.0.00 Page 12 of 12

December 20, 2006

Das könnte Ihnen auch gefallen

- 55V, 1A Peak Current H-Bridge FET Driver Features: December 20, 2006 Data Sheet FN6382.0Dokument12 Seiten55V, 1A Peak Current H-Bridge FET Driver Features: December 20, 2006 Data Sheet FN6382.0Bharat AdvaniNoch keine Bewertungen

- Icl 7667Dokument11 SeitenIcl 7667De JeanNoch keine Bewertungen

- 80V, 1.25A Peak Current H-Bridge FET Driver: FeaturesDokument14 Seiten80V, 1.25A Peak Current H-Bridge FET Driver: FeaturesPiotr WłaźlińskiNoch keine Bewertungen

- ISL6314Dokument32 SeitenISL6314SURESH CHANDRA ROUTNoch keine Bewertungen

- Features: 0.5Mhz, Low Supply Voltage, Low Input Current Bimos Operational AmplifierDokument5 SeitenFeatures: 0.5Mhz, Low Supply Voltage, Low Input Current Bimos Operational AmplifierAlexandre Correa100% (1)

- Icl7667 1528911Dokument12 SeitenIcl7667 1528911Trung Nguyên VõNoch keine Bewertungen

- Hip 4082Dokument12 SeitenHip 4082flo724Noch keine Bewertungen

- AP62200/AP62201/AP62200T: 4.2V To 18V Input, 2A Low Iq Synchronous Buck ConverterDokument24 SeitenAP62200/AP62201/AP62200T: 4.2V To 18V Input, 2A Low Iq Synchronous Buck ConverterAarsol AdvanceNoch keine Bewertungen

- Is31pm7212 DSDokument12 SeitenIs31pm7212 DSdavid.gjeorgevskiNoch keine Bewertungen

- 1Mhz, All-Ceramic, 3A PWM Buck DC/DC Converter: Global Mixed-Mode Technology IncDokument1 Seite1Mhz, All-Ceramic, 3A PWM Buck DC/DC Converter: Global Mixed-Mode Technology IncLeonardo FusserNoch keine Bewertungen

- Tiny Package, High Performance, Constant Current Switching Regulator For White LEDDokument15 SeitenTiny Package, High Performance, Constant Current Switching Regulator For White LEDFahed AlmaktariNoch keine Bewertungen

- CATV/TV/Cable Modem Upconverter Mmic: FeaturesDokument8 SeitenCATV/TV/Cable Modem Upconverter Mmic: FeaturesaledangieNoch keine Bewertungen

- Aoz1212ai PDFDokument18 SeitenAoz1212ai PDF060279Noch keine Bewertungen

- 6A, 23V Synchronous Step-Down Converter With 3.3V/5V LDO: RT6256B/CDokument20 Seiten6A, 23V Synchronous Step-Down Converter With 3.3V/5V LDO: RT6256B/CkiryanoffNoch keine Bewertungen

- 4 / Digit, BCD Output, A/D Converter Features: Data Sheet August 28, 2007Dokument15 Seiten4 / Digit, BCD Output, A/D Converter Features: Data Sheet August 28, 2007Erasmo Franco SNoch keine Bewertungen

- HIP6302CBDokument16 SeitenHIP6302CBterry panNoch keine Bewertungen

- Ic Fan73832Dokument18 SeitenIc Fan73832David CoronadoNoch keine Bewertungen

- Detector Power Management System With Horn Driver and CO Op AmpDokument24 SeitenDetector Power Management System With Horn Driver and CO Op Ampahmed chaouki ChamiNoch keine Bewertungen

- 80V, 300ma Three Phase High Side Driver Features: July 2004 Data Sheet FN4223.2Dokument10 Seiten80V, 300ma Three Phase High Side Driver Features: July 2004 Data Sheet FN4223.2leshaserviceNoch keine Bewertungen

- G5177CDokument9 SeitenG5177Cishtiaq ahmedNoch keine Bewertungen

- MC14008B DDokument8 SeitenMC14008B DAngela SilesNoch keine Bewertungen

- REN Isl6549 DST 20051027Dokument18 SeitenREN Isl6549 DST 20051027Jesus RodriguezNoch keine Bewertungen

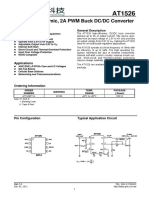

- AT1526 GlobalMixed ModetechnologyDokument2 SeitenAT1526 GlobalMixed ModetechnologyFafa MangstabNoch keine Bewertungen

- Features: High Performance Pin DriverDokument11 SeitenFeatures: High Performance Pin DriverЕвгений ИвановNoch keine Bewertungen

- ISL8560IRZ DatasheetzDokument17 SeitenISL8560IRZ Datasheetzpermadi uyeNoch keine Bewertungen

- Features: Single 12V Input Supply Dual Regulator - Synchronous Rectified Buck PWM and Linear Power ControllerDokument18 SeitenFeatures: Single 12V Input Supply Dual Regulator - Synchronous Rectified Buck PWM and Linear Power ControllerJesus RodriguezNoch keine Bewertungen

- Mosfet Potencia Sihlr014Dokument8 SeitenMosfet Potencia Sihlr014Jorge Martinez PerezNoch keine Bewertungen

- Datasheet PDFDokument12 SeitenDatasheet PDFomen0attaqiNoch keine Bewertungen

- Intermediate Bus PWM Controller Features: ISL6744ADokument18 SeitenIntermediate Bus PWM Controller Features: ISL6744AaliolleikNoch keine Bewertungen

- Bro Avag - HCPL 314jDokument14 SeitenBro Avag - HCPL 314jRomusNoch keine Bewertungen

- AOZ1282CIDokument13 SeitenAOZ1282CIBelalang TempurNoch keine Bewertungen

- Off-Line Quasi-Resonant Switching Regulators: STR-Y6763, STR-Y6765, and STR-Y6766Dokument13 SeitenOff-Line Quasi-Resonant Switching Regulators: STR-Y6763, STR-Y6765, and STR-Y6766Renato Luther escalanteNoch keine Bewertungen

- Datasheet Ic CE DEDokument15 SeitenDatasheet Ic CE DEBersama UkhuwahNoch keine Bewertungen

- Wide Range Fuel Gauge With Impedance Track™ For Lead-Acid BatteriesDokument49 SeitenWide Range Fuel Gauge With Impedance Track™ For Lead-Acid BatteriesLu HoaNoch keine Bewertungen

- ADuM5020 5028Dokument20 SeitenADuM5020 5028IulianCioarcaNoch keine Bewertungen

- IRS2092 InternationalRectifier PDFDokument17 SeitenIRS2092 InternationalRectifier PDFSD BappiNoch keine Bewertungen

- Mc74hct244a Cpu Display LCD CanonDokument8 SeitenMc74hct244a Cpu Display LCD CanonJRochaNoch keine Bewertungen

- Bd83a04efv M eDokument49 SeitenBd83a04efv M e1 Cutting Edge TechnologyNoch keine Bewertungen

- 74LVT16244 - 74LVTH16244 Low Voltage16-Bit Buffer/Line Driver With 3-STATE OutputsDokument7 Seiten74LVT16244 - 74LVTH16244 Low Voltage16-Bit Buffer/Line Driver With 3-STATE OutputsLelik GhhNoch keine Bewertungen

- AOZ1948AIDokument13 SeitenAOZ1948AIfox7878Noch keine Bewertungen

- Features: 600Khz/1.2Mhz PWM Step-Up RegulatorDokument12 SeitenFeatures: 600Khz/1.2Mhz PWM Step-Up RegulatorЕвгений ИвановNoch keine Bewertungen

- As5048 DS000298 4-00Dokument42 SeitenAs5048 DS000298 4-00mmm_gggNoch keine Bewertungen

- Features: Monolithic 600ma Step-Down Regulator With Low Quiescent CurrentDokument11 SeitenFeatures: Monolithic 600ma Step-Down Regulator With Low Quiescent CurrentЕвгений ИвановNoch keine Bewertungen

- AS5048A/AS5048B: Magnetic Rotary Encoder (14-Bit Angular Position Sensor)Dokument41 SeitenAS5048A/AS5048B: Magnetic Rotary Encoder (14-Bit Angular Position Sensor)alfredhimmokNoch keine Bewertungen

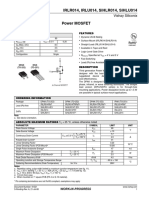

- Irlr024, Irlu024, Sihlr024, Sihlu024: Vishay SiliconixDokument11 SeitenIrlr024, Irlu024, Sihlr024, Sihlu024: Vishay SiliconixPabloNoch keine Bewertungen

- Isl6545 A PDFDokument17 SeitenIsl6545 A PDFdragoblaztrNoch keine Bewertungen

- ZXLD1370Dokument39 SeitenZXLD1370Iqbal Muzhaffar IsmailNoch keine Bewertungen

- CA2xx CA3xx CA4xx SY7208 SY7208BDokument5 SeitenCA2xx CA3xx CA4xx SY7208 SY7208BjbNoch keine Bewertungen

- ISL6612, ISL6613: Advanced Synchronous Rectified Buck MOSFET Drivers With Protection FeaturesDokument12 SeitenISL6612, ISL6613: Advanced Synchronous Rectified Buck MOSFET Drivers With Protection FeaturesAnonymous oyUAtpKNoch keine Bewertungen

- Sy7208 PDFDokument4 SeitenSy7208 PDFBuzatu GianiNoch keine Bewertungen

- TB62747AFG, TB62747AFNG: 16-Output Constant Current LED DriverDokument20 SeitenTB62747AFG, TB62747AFNG: 16-Output Constant Current LED DriverSaša DinčićNoch keine Bewertungen

- RT8057Dokument11 SeitenRT8057antonio carlos clementino cruzNoch keine Bewertungen

- 3A, 2Mhz, Synchronous Step-Down Converter: General Description FeaturesDokument13 Seiten3A, 2Mhz, Synchronous Step-Down Converter: General Description FeaturesKavinda Jayasinghege DonNoch keine Bewertungen

- TX2/RX2 Remote Controller With Five Functions: FeaturesDokument8 SeitenTX2/RX2 Remote Controller With Five Functions: FeaturesRambo333Noch keine Bewertungen

- AD7520, AD7521: 10-Bit, 12-Bit, Multiplying D/A Converters FeaturesDokument10 SeitenAD7520, AD7521: 10-Bit, 12-Bit, Multiplying D/A Converters FeaturesmoocomNoch keine Bewertungen

- uPD16510A RenesasDokument15 SeitenuPD16510A RenesasAnh Le NgocNoch keine Bewertungen

- AS5048A/AS5048B: Magnetic Rotary Encoder (14-Bit Angular Position Sensor)Dokument40 SeitenAS5048A/AS5048B: Magnetic Rotary Encoder (14-Bit Angular Position Sensor)ravellNoch keine Bewertungen

- Infineon IRS233 DS v02 00 enDokument39 SeitenInfineon IRS233 DS v02 00 enJanet WaldeNoch keine Bewertungen

- Icm7555 56Dokument13 SeitenIcm7555 56she rifNoch keine Bewertungen

- Bipolar Transistor: 30V, 1.5A, Low VCE (Sat), NPN Single PCPDokument8 SeitenBipolar Transistor: 30V, 1.5A, Low VCE (Sat), NPN Single PCProlandseNoch keine Bewertungen

- GPS Antenna: Installation GuideDokument2 SeitenGPS Antenna: Installation Guidegenaro guzmanNoch keine Bewertungen

- Chapter 2 DC Circuit TheoryDokument37 SeitenChapter 2 DC Circuit TheoryTynoh MusukuNoch keine Bewertungen

- Vacuum Circuit Breaker Test Report: 1.nameplateDokument2 SeitenVacuum Circuit Breaker Test Report: 1.nameplateErwin SambasNoch keine Bewertungen

- Biomagnetic Healing by Gary Null PDFDokument80 SeitenBiomagnetic Healing by Gary Null PDFYuldash100% (7)

- Radar Motion Detector For Automatic DoorsDokument4 SeitenRadar Motion Detector For Automatic DoorsIndustrial DoorsNoch keine Bewertungen

- Testers For Electric Motors and All Kinds of Windings: Product GuideDokument29 SeitenTesters For Electric Motors and All Kinds of Windings: Product GuideMohamedNoch keine Bewertungen

- 2.5 DisplayDokument34 Seiten2.5 DisplayJhonPaul TarazonaNoch keine Bewertungen

- Task 3 - Electromagnetic Waves in Guided Media Individual WorkDokument16 SeitenTask 3 - Electromagnetic Waves in Guided Media Individual WorkLeonardo Romero JimenezNoch keine Bewertungen

- iC60L Circuit Breakers (Curve B, C, K, Z)Dokument1 SeiteiC60L Circuit Breakers (Curve B, C, K, Z)Diego PeñaNoch keine Bewertungen

- DPT300 - Single Function Transducer - CeweDokument4 SeitenDPT300 - Single Function Transducer - CeweTeguh WaluyoNoch keine Bewertungen

- BCT 11Dokument16 SeitenBCT 11Jesu RajNoch keine Bewertungen

- VRX 775 VDDokument54 SeitenVRX 775 VDiljacksoniiiNoch keine Bewertungen

- Bushing Insulators: Other Medium Voltage EquipmentDokument4 SeitenBushing Insulators: Other Medium Voltage EquipmentjalilemadiNoch keine Bewertungen

- Design Implementation of Fire Alarm CircuitDokument51 SeitenDesign Implementation of Fire Alarm CircuitdgrsriNoch keine Bewertungen

- Manual de ScorbotDokument6 SeitenManual de ScorbotRafael G. MaciasNoch keine Bewertungen

- IRF540ZPBFDokument12 SeitenIRF540ZPBFJose M PeresNoch keine Bewertungen

- Autobiog of BenfranklinDokument30 SeitenAutobiog of Benfranklinalexos2012Noch keine Bewertungen

- Premium Gold Motor: TOSHIBA Top Runner MotorDokument17 SeitenPremium Gold Motor: TOSHIBA Top Runner MotorMOTORES, MOTORREDUCTORES Y COMPONENTES GUADALAJARANoch keine Bewertungen

- Multiple Choices Questions in Communications Engineering By: S. S. Cuervo & K. L. N. Suello 400 Solved Problems Transmission LinesDokument949 SeitenMultiple Choices Questions in Communications Engineering By: S. S. Cuervo & K. L. N. Suello 400 Solved Problems Transmission LinesEdmark AldeaNoch keine Bewertungen

- MX62 Manual GBDokument84 SeitenMX62 Manual GBMarcelo LeguizamonNoch keine Bewertungen

- Converting The Digitech Xp-100 To An XP-"All" Build InstructionsDokument66 SeitenConverting The Digitech Xp-100 To An XP-"All" Build InstructionsneonrenNoch keine Bewertungen

- MAX 50-100KTL3 LV - MV Quick Guide EN 202202Dokument2 SeitenMAX 50-100KTL3 LV - MV Quick Guide EN 202202emilNoch keine Bewertungen

- Training Report For Internship SemesterDokument61 SeitenTraining Report For Internship SemesterAkshaj SrivastavaNoch keine Bewertungen

- EV Connection Offering EV Charging As An Amenity To Zehn Bukit PantaiDokument3 SeitenEV Connection Offering EV Charging As An Amenity To Zehn Bukit PantaiyogapostNoch keine Bewertungen

- ASSIGN6Dokument5 SeitenASSIGN6Binod AdhikariNoch keine Bewertungen

- Synchronous Generator Transient AnalysisDokument19 SeitenSynchronous Generator Transient AnalysiskasunchamaraNoch keine Bewertungen

- ARUM432BTE5Dokument3 SeitenARUM432BTE5Omar JuradoNoch keine Bewertungen

- Including M17/176-00001 Twinaxial Data Bus Cable: The Importance of VSWR Sweep TestingDokument2 SeitenIncluding M17/176-00001 Twinaxial Data Bus Cable: The Importance of VSWR Sweep TestingPin KunthaNoch keine Bewertungen

- Specifications, 132A: Wireless 3-Axis Accelerometer: Performance - by Model: Vs +3.7VDC, TC +25°CDokument1 SeiteSpecifications, 132A: Wireless 3-Axis Accelerometer: Performance - by Model: Vs +3.7VDC, TC +25°Ctaehyun KimNoch keine Bewertungen