Beruflich Dokumente

Kultur Dokumente

Memory Structures DRAM Cells

Hochgeladen von

saigdv1978Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Memory Structures DRAM Cells

Hochgeladen von

saigdv1978Copyright:

Verfügbare Formate

Memory Structures:

DRAM cells

Ramon Canal

NCD - Master MIRI

NCD - Master MIRI 1

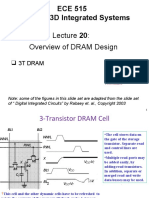

3-Transistor DRAM Cell

BL 1 BL 2

WWL

RWL WWL

M3 RWL

M1 X X V DD 2 V T

M2

V DD

CS BL 1

BL 2 V DD 2 V T DV

No constraints on device ratios

Reads are non-destructive

Value stored at node X when writing a “1” = V WWL-VTn

NCD - Master MIRI 2

3T-DRAM — Layout

BL2 BL1 GND

RWL

M3

M2

WWL

M1

NCD - Master MIRI 3

1-Transistor DRAM Cell

BL

WL Write 1 Read 1

WL

M1

X GND V DD 2 V T

CS

V DD

BL

V DD /2 V /2

sensing DD

CBL

Write: C S is charged or discharged by asserting WL and BL.

Read: Charge redistribution takes places between bit line and storage capacitance

CS

V = BL – V PRE = V BIT – V PRE

V ------------

C S + CBL

Voltage swing is small; typically around 250 mV.

NCD - Master MIRI 4

DRAM Cell Observations

1T DRAM requires a sense amplifier for each bit line, due to charge

redistribution read-out.

DRAM memory cells are single ended in contrast to SRAM cells.

The read-out of the 1T DRAM cell is destructive; read and refresh

operations are necessary for correct operation.

Unlike 3T cell, 1T cell requires presence of an extra capacitance that

must be explicitly included in the design.

When writing a “1” into a DRAM cell, a threshold voltage is lost.

This charge loss can be circumvented by bootstrapping the word lines

to a higher value than VDD

NCD - Master MIRI 5

Sense Amp Operation

V V(1)

BL

V PRE

D V(1)

V(0)

Sense amp activated t

Word line activated

NCD - Master MIRI 6

1-T DRAM Cell

Capacitor

M 1 word

line

Metal word line

SiO2

Poly

n+ n+ Field Oxide Diffused

bit line

Inversion layer

Poly

induced by Polysilicon Polysilicon

plate bias gate plate

Cross-section Layout

Uses Polysilicon-Diffusion Capacitance

Expensive in Area

NCD - Master MIRI 7

SEM of poly-diffusion capacitor 1T-DRAM

NCD - Master MIRI 8

Advanced 1T DRAM Cells

Word line

Cell plate Capacitor dielectric layer

Insulating Layer

Cell Plate Si

Transfer gate Isolation

Refilling Poly

Capacitor Insulator Storage electrode

Storage Node Poly

Si Substrate

2nd Field Oxide

Trench Cell Stacked-capacitor Cell

NCD - Master MIRI 9

Novel cell designs

• 4T cell – “A Reusable Embedded DRAM Macrocell”, P.W.Diodato

J.T.Clemens W.W.Troutman W.S.Lindenberger, IEEE 1997 Custom

Integrated Circuits Conference

• 2T1D - “A Novel Dynamic Memory Cell With Internal Voltage Gain”,

Wing K. Luk and Robert H. Dennard, IEEE Journal of Solid-State

Circuits, v. 40, n. 4, April 2005

• 3T1D – “A 3-Transistor DRAM Cell with Gated Diode for Enhanced

Speed and Retention Time”, Wing K. Luk, Jin Cai, Robert H.

Dennard, Michael J. Immediato, Stephen V. Kosonocky, IEEE 2006

Symposium on VLSI Circuits

NCD - Master MIRI 10

Novel cell designs

• 8T cell – “L. Chang, D. Fried and J. Hergenrother,

“Stable SRAM cell design for the 32 nm node and

beyond”, VLSI Technology, 2005. Digest of Technical

Papers. 2005 Symposium on, 2005, 128-129

NCD - Master MIRI 11

Introducing New Cells in CACTI

• CACTI is the most commonly used

memory structure characterization

programs.

• In this project, you will interact and modify

it to suit your needs.

NCD - Master MIRI 12

Introducing New Cells in CACTI

STEPS:

1. Download CACTI 6.5 http://www.hpl.hp.com/research/cacti/

2. Install it in your system and read the documentation

3. Chose a new cell design of the ones previously proposed in this

document (4T, 3T, 1T, 2T1D, 3T1D). Read about those cells,

justify the cell area assumptions and implement it in CACTI

(Watch out whether your cell is single or double endded!!)

4. Introduce the possibility of chosing the cell type in the command

line (either the available 6T SRAM cell) or your newly designed

cell.

5. Evaluate several configurations for delay (access time) and

power. 8KB-2MB caches, associativities from 1 to 8, and block

sizes from 32bytes to 128 bytes. (All variables increase in power

of 2 steps)

NCD - Master MIRI 13

Introducing New Cells in CACTI

Hand in (email) a PDF with:

1. Description of the cell implemented

2. Modifications made to CACTI

3. Evaluation of the configurations:

1. Effect of the associativity over power and delay

2. Effect of line-size over power and delay

3. Effect of size over power and delay

Hand in (email) the source CACTI code.

1. Be a nice programer and clearly mark your

modifications!

NCD - Master MIRI 14

Das könnte Ihnen auch gefallen

- 04-Memory Structures-2 PDFDokument14 Seiten04-Memory Structures-2 PDFImran100% (1)

- Overview of DRAM DesignDokument21 SeitenOverview of DRAM DesignAzim ShihabNoch keine Bewertungen

- MemoriesDokument7 SeitenMemoriesanushaNoch keine Bewertungen

- E D A Lab: High Performance Standard Cell Layout Synthesis For Advanced Nanometer Technology NodesDokument20 SeitenE D A Lab: High Performance Standard Cell Layout Synthesis For Advanced Nanometer Technology NodesVictor SahaNoch keine Bewertungen

- Lecture2 - Si CMOS BasicsDokument36 SeitenLecture2 - Si CMOS Basicseshwar_worldNoch keine Bewertungen

- Memory Design PDFDokument38 SeitenMemory Design PDFarammartNoch keine Bewertungen

- Class 1Dokument46 SeitenClass 1Naureen ButtNoch keine Bewertungen

- Design and Implementation of VLSI Systems (EN1600) : Lecture 30: Array Subsystems (DRAM/ROM)Dokument16 SeitenDesign and Implementation of VLSI Systems (EN1600) : Lecture 30: Array Subsystems (DRAM/ROM)ALEX SAGARNoch keine Bewertungen

- PowerDokument29 SeitenPowerAdamNoch keine Bewertungen

- MOS MemoryDokument53 SeitenMOS Memoryskh_1987100% (1)

- Power: Ref: Weste-HarrisDokument30 SeitenPower: Ref: Weste-HarrisNahid IslamNoch keine Bewertungen

- CH 05 PowerDokument49 SeitenCH 05 PowerTriếtCỏNoch keine Bewertungen

- Lect5 PowerDokument14 SeitenLect5 PowerIsmat JahanNoch keine Bewertungen

- Layout Lec 03 Overview v01Dokument35 SeitenLayout Lec 03 Overview v01Ahmed MetwalyNoch keine Bewertungen

- LectureDokument26 SeitenLectureKAMARUDHEEN KPNoch keine Bewertungen

- Analysis and Design of Analog Integrated Circuits Analog To Digital ConversionDokument32 SeitenAnalysis and Design of Analog Integrated Circuits Analog To Digital ConversionAndrea FasatoNoch keine Bewertungen

- Digital14.ppt (Autosaved)Dokument87 SeitenDigital14.ppt (Autosaved)abbcccddddNoch keine Bewertungen

- Gate Layouts: 1.5 CMOS Fabrication and LayoutDokument1 SeiteGate Layouts: 1.5 CMOS Fabrication and LayoutCarlos SaavedraNoch keine Bewertungen

- Evolution of DRAM 1kbit To 1gbit June 2004Dokument47 SeitenEvolution of DRAM 1kbit To 1gbit June 2004Peter GillinghamNoch keine Bewertungen

- Lec 18 Low PowerDokument24 SeitenLec 18 Low Powerapi-3864016Noch keine Bewertungen

- Imel7002 L3Dokument115 SeitenImel7002 L3就爱吃饭团Noch keine Bewertungen

- SRAM Design: MemoryDokument36 SeitenSRAM Design: MemoryChia-Cheng LiaoNoch keine Bewertungen

- Chapter 12Dokument107 SeitenChapter 12shivani1401Noch keine Bewertungen

- ECE 411 DRAM & Storage: ECE 411: Computer Organization & DesignDokument43 SeitenECE 411 DRAM & Storage: ECE 411: Computer Organization & DesignKafoorNoch keine Bewertungen

- EECS 150 - Components and Design Techniques For Digital Systems Lec 16 - Storage: DRAM, SDRAMDokument26 SeitenEECS 150 - Components and Design Techniques For Digital Systems Lec 16 - Storage: DRAM, SDRAMtestlogin21Noch keine Bewertungen

- Gate Level DesignDokument34 SeitenGate Level DesignYOGESWARI TOLIANoch keine Bewertungen

- Introduction To Cmos Vlsi Design: Package, Power, I/O and SkewDokument51 SeitenIntroduction To Cmos Vlsi Design: Package, Power, I/O and SkewPrasanna KNoch keine Bewertungen

- VLSI Ch4 DelayDokument27 SeitenVLSI Ch4 Delayជើងកាង ភូមិNoch keine Bewertungen

- DDR34 IO PaperDokument24 SeitenDDR34 IO PaperArsalan JawedNoch keine Bewertungen

- Transistors: Current (BJT) Voltage (FET)Dokument7 SeitenTransistors: Current (BJT) Voltage (FET)Qin LingNoch keine Bewertungen

- Digital Integrated Circuits: A Design PerspectiveDokument61 SeitenDigital Integrated Circuits: A Design PerspectiveDr. Aminul IslamNoch keine Bewertungen

- Introduction To Cmos Vlsi Design: Package, Power, and I/ODokument25 SeitenIntroduction To Cmos Vlsi Design: Package, Power, and I/OSabariNoch keine Bewertungen

- Class23-24 Vias Connectors and PackagesDokument76 SeitenClass23-24 Vias Connectors and PackagesspyeagleNoch keine Bewertungen

- On-Chip Switched-Capacitor DC-DC Converter in MEMORIESDokument5 SeitenOn-Chip Switched-Capacitor DC-DC Converter in MEMORIEShello worldNoch keine Bewertungen

- Illustrated Assembly Manual k8062Dokument12 SeitenIllustrated Assembly Manual k8062Richard LeiteNoch keine Bewertungen

- ARM Based ESD UNIT 1ADokument16 SeitenARM Based ESD UNIT 1AManu ManuNoch keine Bewertungen

- Mini & FlexyDokument3 SeitenMini & FlexyJeffNoch keine Bewertungen

- Lec4.4 Power DescipationDokument17 SeitenLec4.4 Power Descipationnadeem47Noch keine Bewertungen

- Unit 7Dokument5 SeitenUnit 7Raja VidyaNoch keine Bewertungen

- CH 04 Delay Part 01Dokument25 SeitenCH 04 Delay Part 01muneeb.abrarNoch keine Bewertungen

- Lecture 10Dokument10 SeitenLecture 10Aviral UpadhyayNoch keine Bewertungen

- Op17 PC CableDokument1 SeiteOp17 PC CablePeter UhuleNoch keine Bewertungen

- Lec 4 MOSFET IIDokument32 SeitenLec 4 MOSFET IIjishahaneeshNoch keine Bewertungen

- Class 18: Memories-Drams: Joseph A. Elias, PHDDokument13 SeitenClass 18: Memories-Drams: Joseph A. Elias, PHDshubham shindeNoch keine Bewertungen

- 2016 Ch4-DelayDokument31 Seiten2016 Ch4-Delayជើងកាង ភូមិNoch keine Bewertungen

- CMOS InverterDokument24 SeitenCMOS InverterM. Bilal NoorNoch keine Bewertungen

- A Seminar On: Semiconductor MemoriesDokument25 SeitenA Seminar On: Semiconductor MemoriesSambit ShreemanNoch keine Bewertungen

- Delay: Introduction To CMOS VLSI DesignDokument54 SeitenDelay: Introduction To CMOS VLSI DesignHuy TranNoch keine Bewertungen

- PM265 ch2Dokument47 SeitenPM265 ch2M. AhmedNoch keine Bewertungen

- Bd52exxx Bd53exxx Series r004 Rohm PDFDokument16 SeitenBd52exxx Bd53exxx Series r004 Rohm PDFJose Enrique Aguirre GuerreroNoch keine Bewertungen

- Part8 Memory - Small PDFDokument24 SeitenPart8 Memory - Small PDFkhaled mahmudNoch keine Bewertungen

- 004.2 Standard Power Terminations - STC ProjectsDokument1 Seite004.2 Standard Power Terminations - STC Projectsgantamahesh2407Noch keine Bewertungen

- Digital Integrated Circuits Cont'dDokument30 SeitenDigital Integrated Circuits Cont'dottoporNoch keine Bewertungen

- CMOS Devices BookDokument37 SeitenCMOS Devices Bookteddy leeNoch keine Bewertungen

- CHP 2 - Mos Design and LayoutDokument104 SeitenCHP 2 - Mos Design and Layoutkkece41Noch keine Bewertungen

- Data Sheet: Low-Voltage Variable Capacitance Double DiodeDokument8 SeitenData Sheet: Low-Voltage Variable Capacitance Double Diodevladimir tomicNoch keine Bewertungen

- Cost-Effective, Peak 3A Sink/Source Bus Termination RegulatorDokument13 SeitenCost-Effective, Peak 3A Sink/Source Bus Termination RegulatorTomy Aditya PratamaNoch keine Bewertungen

- Dem16215syh LyDokument17 SeitenDem16215syh Lyflo72afNoch keine Bewertungen

- Combinational DesignDokument22 SeitenCombinational DesignAnkur PatelNoch keine Bewertungen

- Linear Network Theory: The Commonwealth and International Library: Applied Electricity and Electronics DivisionVon EverandLinear Network Theory: The Commonwealth and International Library: Applied Electricity and Electronics DivisionNoch keine Bewertungen

- Assignment Week4Dokument3 SeitenAssignment Week4saigdv1978100% (2)

- VHDL Lab ManualDokument51 SeitenVHDL Lab Manualsaigdv1978Noch keine Bewertungen

- (Ercegovac Milos D., Lang Tomas) Digital Arithmeti (B-Ok - Xyz)Dokument731 Seiten(Ercegovac Milos D., Lang Tomas) Digital Arithmeti (B-Ok - Xyz)saigdv1978Noch keine Bewertungen

- 6th Central Pay Commission Salary CalculatorDokument15 Seiten6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Week 1 Lecture MaterialDokument96 SeitenWeek 1 Lecture Materialsaigdv1978Noch keine Bewertungen

- Week 2 Course MaterialDokument60 SeitenWeek 2 Course Materialsaigdv1978Noch keine Bewertungen

- Either Source or Destination Is One Of: CPU RegisterDokument81 SeitenEither Source or Destination Is One Of: CPU Registersaigdv1978Noch keine Bewertungen

- Wireless Sensor Networks SyllabusDokument3 SeitenWireless Sensor Networks Syllabussaigdv19780% (1)

- Arduino Based Home Automation System Using Bluetooth Through An Android Mobile PDFDokument72 SeitenArduino Based Home Automation System Using Bluetooth Through An Android Mobile PDFsaigdv197859% (17)

- Digital System Design & Digital Ic ApplicationsDokument4 SeitenDigital System Design & Digital Ic Applicationssaigdv1978Noch keine Bewertungen

- Ramachandra College of EngineeringDokument1 SeiteRamachandra College of Engineeringsaigdv1978Noch keine Bewertungen

- Embedded Software in C For ARM Cortex MDokument114 SeitenEmbedded Software in C For ARM Cortex MMohamedHassanNoch keine Bewertungen

- Ramachandra College of EngineeringDokument1 SeiteRamachandra College of Engineeringsaigdv1978Noch keine Bewertungen

- Switching Theory and Logic DesignDokument2 SeitenSwitching Theory and Logic Designsaigdv1978Noch keine Bewertungen

- Microprosser 8085Dokument15 SeitenMicroprosser 8085saigdv1978Noch keine Bewertungen

- GPRS and GPS Based Vehicle TrackingDokument1 SeiteGPRS and GPS Based Vehicle Trackingsaigdv1978Noch keine Bewertungen

- Electrical CertificateDokument6 SeitenElectrical CertificateMarios TheodoulouNoch keine Bewertungen

- VW T4 Campervan Wiring DiagramDokument2 SeitenVW T4 Campervan Wiring DiagramWhatton0% (1)

- Sr90 StandardDokument26 SeitenSr90 Standardflorin74Noch keine Bewertungen

- JSS 2 Basic Technology Week 6 Lesson 2Dokument3 SeitenJSS 2 Basic Technology Week 6 Lesson 2Adio Babatunde Abiodun CabaxNoch keine Bewertungen

- OnSemi The TL431 in The Control of Switching Power Supplies PDFDokument63 SeitenOnSemi The TL431 in The Control of Switching Power Supplies PDFFernando BotteronNoch keine Bewertungen

- Off-Line Insulation Testing and Diagnosis of HV MachinesDokument4 SeitenOff-Line Insulation Testing and Diagnosis of HV MachinesnaveenNoch keine Bewertungen

- CMX 022 Adjustable Frequency DriveDokument16 SeitenCMX 022 Adjustable Frequency DriveJESUSCALVILLO100% (2)

- Exp2 - DC Generators (2 Parts) (1) XXDokument16 SeitenExp2 - DC Generators (2 Parts) (1) XXLheidyy36Noch keine Bewertungen

- Adjustable Precision Zener Shunt Regulator: (Top View) 1 2 3 4 V GND V GND (Top View)Dokument9 SeitenAdjustable Precision Zener Shunt Regulator: (Top View) 1 2 3 4 V GND V GND (Top View)noahkrpgNoch keine Bewertungen

- Laporan Praktikum - Elektronika Dasar - Penyearah Setengah Gelombang.Dokument11 SeitenLaporan Praktikum - Elektronika Dasar - Penyearah Setengah Gelombang.Lasmaenita SiahaanNoch keine Bewertungen

- Mx150 ManualDokument28 SeitenMx150 ManualThiago BertiNoch keine Bewertungen

- Oleveon 236 E PC INOX: Offer Text Product Features and Key DataDokument1 SeiteOleveon 236 E PC INOX: Offer Text Product Features and Key Dataahmed saberNoch keine Bewertungen

- B44P04Dokument7 SeitenB44P04aldo_suviNoch keine Bewertungen

- 2SA1943Dokument7 Seiten2SA1943gotcha75Noch keine Bewertungen

- Electrical Interview Questions With AnsDokument16 SeitenElectrical Interview Questions With Ansvinoddeswal057100% (1)

- Keor Hpe 60 80 GB PDFDokument2 SeitenKeor Hpe 60 80 GB PDFUguudei ErdembilegNoch keine Bewertungen

- Djatiroto - Motor 950kWDokument2 SeitenDjatiroto - Motor 950kWandrieysyah2525Noch keine Bewertungen

- Philips EssentialLEDtube T8Dokument9 SeitenPhilips EssentialLEDtube T8Cristian FarinaNoch keine Bewertungen

- Dual Full-Bridge MOSFET Driver With Microstepping TranslatorDokument16 SeitenDual Full-Bridge MOSFET Driver With Microstepping TranslatorВладимир ЯткевичNoch keine Bewertungen

- 10-ITALRAY Generator Statix PDFDokument103 Seiten10-ITALRAY Generator Statix PDFNassima BELIL100% (5)

- GCM en ArabeDokument32 SeitenGCM en ArabeDjamel BoukredimiNoch keine Bewertungen

- Rewinding A BLDC MotorDokument22 SeitenRewinding A BLDC MotorUday WankarNoch keine Bewertungen

- Baylan Pdu (Power Distribution Unit) : Available Modular Type Extension SocketsDokument5 SeitenBaylan Pdu (Power Distribution Unit) : Available Modular Type Extension SocketsIftikhar AmjadNoch keine Bewertungen

- PAT Testing CertificateDokument4 SeitenPAT Testing CertificateD SmaleNoch keine Bewertungen

- User Manual Liebert PSL 650 2000vaDokument8 SeitenUser Manual Liebert PSL 650 2000vaMaykel Dela CruzNoch keine Bewertungen

- IM Series 1.5kVA InverterDokument2 SeitenIM Series 1.5kVA InverterJonathan SantanaNoch keine Bewertungen

- Siemslvbh3610 SpecDokument66 SeitenSiemslvbh3610 SpecLD Jr FrancisNoch keine Bewertungen

- Generator Excitation SystemDokument35 SeitenGenerator Excitation SystemNitin Sakpal100% (1)

- Revo E 5.5kW Solar Inverter Data SheetDokument2 SeitenRevo E 5.5kW Solar Inverter Data SheetMSA SolarNoch keine Bewertungen

- FuseDokument40 SeitenFuseAnonymous MBapZd8Noch keine Bewertungen