Beruflich Dokumente

Kultur Dokumente

2018 Lab 4B Digital To Analog Converter

Hochgeladen von

Patrick SibandaOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

2018 Lab 4B Digital To Analog Converter

Hochgeladen von

Patrick SibandaCopyright:

Verfügbare Formate

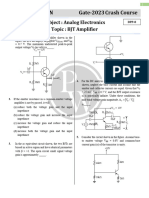

PH-315 Portland State University

DIGITAL TO ANALOG CONVERTER (DAC)

1. PURPOSE:

Construction of digital-to-analogue converters using different techniques, namely the

scaled resistors into summing junction, and the R-2R ladder.

Figure. 1 Digital vs analog signal processing.

2. CONVERTING DIGITAL TO ANALOG SIGNALS:

It is often necessary to convert analog signal to an accurate digital number, and vice versa.

For example, in applications where a microprocessor is controlling an experiment, the

analogue signal from a sensor needs to be converted into digital form so it can be

communicated to the microprocessor. After the processing takes place in the digital form,

the output from the microcontroller needs to be converted back to the analogue form to

communicate with the analogue world.

In this lab session we will consider the case of digital to analogue conversion (DAC). The

DAC techniques presented here are not aimed at developing skills in converter designs.

Instead, they aim at presenting the advantages and disadvantages of each method. In most

cases, when embarked in an electronic project, one rather buys commercially available chips

instead of building a converter from scratch. An understanding of DAC methods, however,

will guide you in selecting the more suitable one for the project at hand.

2.1 Scaled resistors into summing junction

Implement the circuit shown in Fig. 2.

a) Notice that the circuit has an input count from 0 (when all the inputs are OFF) to 15 (when

all the inputs are HIGH.)

b) Verify that the circuit generates an output voltage from zero to (almost) 5 Volts. The exact

value is estimated below.

EXACT CALCULATION

b1) Verify that the total maximum current through the gain resistor is given by,

1 1 1 1

I f Vref (1 2 3 )

10k 2 2 2

b2) Verify that the circuit generates an output voltage from zero to,

5 k 1 (1 / 2) 4

Vmax Vref

10 k 1 (1 / 2)

15

Vmax Vref

16

Vref = 5 Volt

MSB 23 10k, 1%

i3

5k, 1%

20k, 2%

22 If

i2 VCC

- Vout

40k, 4% i1 If + Analog

21 LM358AP

-VCC output

i0

80k, 8%

LSB 20

Digital input

Fig. 2 Four-bit DAC.

Example of a binary input: 1 0 1 0

MSB LSB

We need an experimental implementation that reflect the corresponding weight of the

binary digits,

23 23 23 23

Calibration voltage: Contribution to the total output voltage from bit,

5𝑉

𝑉𝑗,𝑜𝑢𝑡 = − 𝑅 5𝑘, j= 0, 1, 2, 3

𝑗

MSB 23 5V 10k, 1%

i3

5k, 1%

20k, 2%

22 0V If

i2 VCC

- Vout

5V 40k, 4% i1 If + Analog

21 LM358AP

-VCC output

i0

80k, 8%

LSB 20 0V

Theory Experimental implementation

Experimental implementation of the binary input: 1 0 1 0

c) GENERALIZATION (for n-bits DAC)

In Fig. 2, consider adding input bits on the left side (i.e. adding resistors whose values

increase by a factor of 2) until n inputs are completed.

Show that the maximum input count is 2n-1 (when all the n bits set to 1.)

Show analytically that the circuit generates output voltages from zero to

2n 1

Vmax Vref [ n ]

2

d) REQUIRED PRECISION of the RESITORS

d1) Show that for a given input of resistance R in the DAC circuit, the contribution (only

Vref

from that input) to the output voltage is Vout 5k .

R

Hence, a smaller resistance R produces larger currents (Vref/R) and has a larger

contribution to the output voltage.

This explains why in Fig. 2:

the input with smaller resistance (10 kin this case) is assigned to represent the

most-significant-bit (MSB); and

the input with higher resistance (80 kis assigned to represent the least-

significant-bit (LSB).

d2) If the value of the resistor “R” were to have an uncertainty R show that the

corresponding uncertainty in the out voltage Vout is given by,

Vout R

Vout R

Thus, for a given required precision in the output voltage, a higher value of R can

afford a larger R uncertainty (lower precision). Hence, the resistance at the MSB

input (lower resistance R) requires smaller R uncertainty (i. e. higher precision) in

the resistance value.

e) Make a table of the digital inputs in one column and the corresponding output voltage in

another column, and verify if the obtained experimental values correspond with the

predicted ones.

2.2 R-2R ladder

The scaled resistor technique becomes awkward for higher bits DAC. (A 12-bit converter

would need a 2000:1 range of resistor values) with corresponding precision in the MSB

input. This becomes impractical. The R-2R ladder, shown in Fig. 3 offers an elegant

alternative.

Only two resistor values are needed.

Although the resistors must be precisely matched, the actual value of the resistors is not

critical.

2i i i /2 i /4 i /8

VREF vin

R= 50k

= 5 Volts R R R 2R

2R 2R 2R 2R

50 k

If

VCC

- Vout

3 2 1 0 +

2 2 2 2 LM358AP Analog

output

MSB LSB -VCC

Fig. 2 Four-bit DAC.

a) Check if suggested distribution of currents along the network of resistance is correct.

b) Calculate and verify experimentally that the contribution to the output voltage from

the MSB is -2.5 V.

Verify that the contribution to the output voltage from the other inputs decrease by a

factor of 2, from bit to the next.

c) Make a table of the digital inputs in one column and the corresponding output voltage

in another column, and verify if the obtained experimental values correspond with the

predicted ones.

d) Calculate (show all your steps) and verify experimentally that the maximum

magnitude of the output voltage is Vref 15/16.

Das könnte Ihnen auch gefallen

- Digital To Analog Converter (Dac)Dokument3 SeitenDigital To Analog Converter (Dac)Shimaa BarakatNoch keine Bewertungen

- Gateeasy D To A PDFDokument3 SeitenGateeasy D To A PDFShubham kumarNoch keine Bewertungen

- Midterm 11 2022Dokument4 SeitenMidterm 11 2022kunghsiangyuNoch keine Bewertungen

- 4 Bit DacDokument4 Seiten4 Bit DacG Lokesh100% (1)

- BJT Amplifier Question Will Become A Cakewalk - DPP-07Dokument3 SeitenBJT Amplifier Question Will Become A Cakewalk - DPP-07altafAhmadNoch keine Bewertungen

- BJT Small-Signal Amplifier Lab ReportDokument8 SeitenBJT Small-Signal Amplifier Lab Reportمحمد ابو جرادNoch keine Bewertungen

- Experiment 3Dokument3 SeitenExperiment 3ugurgul123Noch keine Bewertungen

- Chapter 4Dokument22 SeitenChapter 4hadushNoch keine Bewertungen

- EC6411 CircuitsSimulation LABDokument98 SeitenEC6411 CircuitsSimulation LABJ.Gowri ShankarNoch keine Bewertungen

- Op-Amp Circuits Testing Understanding Feedback Gain CMRRDokument2 SeitenOp-Amp Circuits Testing Understanding Feedback Gain CMRRgebretsadkan abrhaNoch keine Bewertungen

- BJT Amplifier - 2 - DPP-08Dokument3 SeitenBJT Amplifier - 2 - DPP-0821bec091AnandMohanAryaNoch keine Bewertungen

- Lab 12: BJT Common Emitter Amplifier: 1. ObjectivesDokument4 SeitenLab 12: BJT Common Emitter Amplifier: 1. ObjectivesAnuj MishraNoch keine Bewertungen

- Stony Brook ESE 211 Lab on BJT Common Emitter AmplifierDokument4 SeitenStony Brook ESE 211 Lab on BJT Common Emitter AmplifierMert AçikelNoch keine Bewertungen

- Voltage Divider Biasing Lab ReportDokument6 SeitenVoltage Divider Biasing Lab ReportYu LoengNoch keine Bewertungen

- B.Sc. Engineering (Hons) Degree: Sri Lanka Institute of Information TechnologyDokument5 SeitenB.Sc. Engineering (Hons) Degree: Sri Lanka Institute of Information TechnologyThilina PereraNoch keine Bewertungen

- Chapter 6Dokument8 SeitenChapter 6Gizachew BalchaNoch keine Bewertungen

- Lab6 (Malvino Chapters 17 and 18)Dokument3 SeitenLab6 (Malvino Chapters 17 and 18)dirac90Noch keine Bewertungen

- Problems Theme 3 (BJT)Dokument11 SeitenProblems Theme 3 (BJT)erosceleste17Noch keine Bewertungen

- Lab 6 BJT DC and Ac Analysis BBN 10205 (Done)Dokument6 SeitenLab 6 BJT DC and Ac Analysis BBN 10205 (Done)Zhamir ZhakwanNoch keine Bewertungen

- Ac and DC Biasing-Bjts and Fet: Learning ObjectivesDokument24 SeitenAc and DC Biasing-Bjts and Fet: Learning ObjectiveskalyanNoch keine Bewertungen

- Applied Electronics CH2Dokument7 SeitenApplied Electronics CH2mesfin snowNoch keine Bewertungen

- ECE321 - 6th EXPDokument4 SeitenECE321 - 6th EXPمحمد ابراهيمNoch keine Bewertungen

- EEE308 Midterm Fall 2023Dokument3 SeitenEEE308 Midterm Fall 2023ANWAR SHADMANNoch keine Bewertungen

- Lab 1Dokument2 SeitenLab 1Minecraft BuilderNoch keine Bewertungen

- EE311 Analog Electronics Final Q1) (15 PTS.) A Class-A Emitter Follower Biased With A Constant Current Source Is Given in TheDokument6 SeitenEE311 Analog Electronics Final Q1) (15 PTS.) A Class-A Emitter Follower Biased With A Constant Current Source Is Given in TheburakNoch keine Bewertungen

- SKEE3263Excercise2 (Soln)Dokument7 SeitenSKEE3263Excercise2 (Soln)sawsheng59Noch keine Bewertungen

- Laboratory Instruction Sheet: Jabatan Pendidikan Kejuruteraan Fakulti Pendidikan Teknikal Dan VokasionalDokument4 SeitenLaboratory Instruction Sheet: Jabatan Pendidikan Kejuruteraan Fakulti Pendidikan Teknikal Dan VokasionalBlank BlankNoch keine Bewertungen

- Ece2201 SJB Lab7x Audio Inv PDFDokument7 SeitenEce2201 SJB Lab7x Audio Inv PDFxiditoNoch keine Bewertungen

- CAD Lab Manual KEC 653B (4mail)Dokument38 SeitenCAD Lab Manual KEC 653B (4mail)Piyush0% (1)

- Lab#2B: Half-Wave Rectifier Circuit Without and With FilterDokument5 SeitenLab#2B: Half-Wave Rectifier Circuit Without and With FilterHemanth GedelaNoch keine Bewertungen

- V, V, K U C W/L, V I, I, G, R: Unless Given SpecificallyDokument2 SeitenV, V, K U C W/L, V I, I, G, R: Unless Given SpecificallyraghavbhatiaNoch keine Bewertungen

- Chapter V - Problem Set P5.1Dokument15 SeitenChapter V - Problem Set P5.1Aaron MartinezNoch keine Bewertungen

- Assignment 03Dokument5 SeitenAssignment 03Akshay KumarNoch keine Bewertungen

- Investigation of Transistor Characteristics Common Emitter CircuitDokument2 SeitenInvestigation of Transistor Characteristics Common Emitter Circuitola pedensNoch keine Bewertungen

- Lab 9 Common Emitter Amplifier: Department of Electrical EngineeringDokument7 SeitenLab 9 Common Emitter Amplifier: Department of Electrical EngineeringKainat KhalidNoch keine Bewertungen

- sboa292aDokument6 Seitensboa292ajrmmelo03Noch keine Bewertungen

- Lab 3Dokument4 SeitenLab 3J SarduaNoch keine Bewertungen

- CHPTR 3 - Multistage Amplifier (I) Revision 2 Razel CorrectionDokument59 SeitenCHPTR 3 - Multistage Amplifier (I) Revision 2 Razel CorrectionTonmoy ChowdhuryNoch keine Bewertungen

- Multilevel Topologies. Josep PauDokument32 SeitenMultilevel Topologies. Josep PauJose ManuelNoch keine Bewertungen

- BIFPCL 2019 Electrical Engineer Recruitment Test QuestionsDokument3 SeitenBIFPCL 2019 Electrical Engineer Recruitment Test QuestionsA One ShoppersNoch keine Bewertungen

- Analog Electronics Lab. - Tarun - 05616412820Dokument38 SeitenAnalog Electronics Lab. - Tarun - 05616412820TarunNoch keine Bewertungen

- Electronic Fundamentals II: Coupling and Bypass CapacitorsDokument1 SeiteElectronic Fundamentals II: Coupling and Bypass Capacitorsusman---ali4585Noch keine Bewertungen

- 6.334 Power Electronics: Mit OpencoursewareDokument4 Seiten6.334 Power Electronics: Mit OpencoursewareLocalized Prayer AppNoch keine Bewertungen

- Sboa 290 CSHXGHDCXCFXDDCGDokument6 SeitenSboa 290 CSHXGHDCXCFXDDCGKarthik SuryaNoch keine Bewertungen

- Measuring Instrumentation Circuits TutorialDokument6 SeitenMeasuring Instrumentation Circuits Tutorialaditya narayan shuklaNoch keine Bewertungen

- Mert Terzi 150718061 LabReport4Dokument8 SeitenMert Terzi 150718061 LabReport4Mert TerziNoch keine Bewertungen

- Simple Logic Circuits Lab ExperimentDokument4 SeitenSimple Logic Circuits Lab ExperimentMalikAlrahabiNoch keine Bewertungen

- Assignment 5 f2016Dokument6 SeitenAssignment 5 f2016phoebezzNoch keine Bewertungen

- Sboa 221 ADokument4 SeitenSboa 221 Anupoorhit2126Noch keine Bewertungen

- Aec Lab ManualDokument33 SeitenAec Lab Manualganga_ch1Noch keine Bewertungen

- Power AmplifierDokument37 SeitenPower AmplifierSristick100% (6)

- Designing An Astable MultivibratorDokument7 SeitenDesigning An Astable Multivibratorjeyaganesh100% (3)

- 2SC2855, 2SC2856: Silicon NPN EpitaxialDokument10 Seiten2SC2855, 2SC2856: Silicon NPN Epitaxialzero cloudNoch keine Bewertungen

- ECD Lab 2Dokument6 SeitenECD Lab 2Maryam MahmoodNoch keine Bewertungen

- EECE 310 Sample BJT ProblemsDokument8 SeitenEECE 310 Sample BJT ProblemsALi AlawiehNoch keine Bewertungen

- TO-202 Silicon NPN Power Transistor SpecificationDokument3 SeitenTO-202 Silicon NPN Power Transistor Specificationade abangNoch keine Bewertungen

- Lab 1 EA1 2018Dokument5 SeitenLab 1 EA1 2018Vildrey J. GuerreroNoch keine Bewertungen

- Birla Institute of Technology and Science, Pilani, K.K. Birla Goa CampusDokument4 SeitenBirla Institute of Technology and Science, Pilani, K.K. Birla Goa CampusDevansh GuptaNoch keine Bewertungen

- Tut4 PHY101 2018Dokument1 SeiteTut4 PHY101 2018Patrick SibandaNoch keine Bewertungen

- PH-213 Chapter-33 Energy Transport and The Poynting VectorDokument6 SeitenPH-213 Chapter-33 Energy Transport and The Poynting VectorPatrick SibandaNoch keine Bewertungen

- PH-223 La Rosa Lecture 14 Part-BDokument48 SeitenPH-223 La Rosa Lecture 14 Part-BPatrick SibandaNoch keine Bewertungen

- 2018 Lab 5B Voltage-Controlled - OscillatorDokument4 Seiten2018 Lab 5B Voltage-Controlled - OscillatorPatrick SibandaNoch keine Bewertungen

- PH-213 Chapter-33 Index of Refraction Depends On FrequencyDokument18 SeitenPH-213 Chapter-33 Index of Refraction Depends On FrequencyPatrick SibandaNoch keine Bewertungen

- 2018 PH315 Mat Lab Simulator For RLC Circuits.Dokument1 Seite2018 PH315 Mat Lab Simulator For RLC Circuits.Patrick SibandaNoch keine Bewertungen

- Lecture Not on Final ExamDokument39 SeitenLecture Not on Final ExamPatrick SibandaNoch keine Bewertungen

- PH-213 Chapter-33 Energy Transport and The Poynting Vector PDFDokument20 SeitenPH-213 Chapter-33 Energy Transport and The Poynting Vector PDFPatrick SibandaNoch keine Bewertungen

- PH-213 Chapter-33 Energy Transport and The Poynting VectorDokument20 SeitenPH-213 Chapter-33 Energy Transport and The Poynting VectorPatrick SibandaNoch keine Bewertungen

- PH-223 La Rosa Lecture 14 Part-ADokument15 SeitenPH-223 La Rosa Lecture 14 Part-APatrick SibandaNoch keine Bewertungen

- Sample Exam 2 Phys 213Dokument8 SeitenSample Exam 2 Phys 213Patrick SibandaNoch keine Bewertungen

- Sample Exam-1 Phys-213 PDFDokument7 SeitenSample Exam-1 Phys-213 PDFPatrick SibandaNoch keine Bewertungen

- Notes 2013 Complex Numbers For Exp RLC SeriesDokument18 SeitenNotes 2013 Complex Numbers For Exp RLC SeriesPatrick SibandaNoch keine Bewertungen

- 2018 Exp RLC SeriesDokument19 Seiten2018 Exp RLC SeriesPatrick SibandaNoch keine Bewertungen

- 2018 Lab 5A Positive Feedback and Operational AmplifiersDokument2 Seiten2018 Lab 5A Positive Feedback and Operational AmplifiersPatrick SibandaNoch keine Bewertungen

- 2018 Lab 5A Positive Feedback and Operational AmplifiersDokument2 Seiten2018 Lab 5A Positive Feedback and Operational AmplifiersPatrick SibandaNoch keine Bewertungen

- Statutory Instruments 17: The Zambia Qualifications Authority Act, 2011Dokument19 SeitenStatutory Instruments 17: The Zambia Qualifications Authority Act, 2011Patrick SibandaNoch keine Bewertungen

- 2018 Lab 5A Positive Feedback and Operational AmplifiersDokument15 Seiten2018 Lab 5A Positive Feedback and Operational AmplifiersPatrick SibandaNoch keine Bewertungen

- NewtonDokument16 SeitenNewtonPatrick SibandaNoch keine Bewertungen

- IntroDokument18 SeitenIntroPatrick SibandaNoch keine Bewertungen

- Trigonometric Interpolation: Approximating Functions Using Fourier SeriesDokument52 SeitenTrigonometric Interpolation: Approximating Functions Using Fourier SeriesPatrick SibandaNoch keine Bewertungen

- KrylovDokument46 SeitenKrylovPatrick SibandaNoch keine Bewertungen

- CH 04Dokument77 SeitenCH 04Patrick SibandaNoch keine Bewertungen

- Introduction To Numerical Analysis II: Solving Linear SystemDokument28 SeitenIntroduction To Numerical Analysis II: Solving Linear SystemPatrick SibandaNoch keine Bewertungen

- CH 05Dokument46 SeitenCH 05Patrick SibandaNoch keine Bewertungen

- Chapter 11: Special Theory of Relativity: (Ref.: Marion & Heald, "Classical Electromagnetic Radiation," 3rd Ed., Ch. 14)Dokument73 SeitenChapter 11: Special Theory of Relativity: (Ref.: Marion & Heald, "Classical Electromagnetic Radiation," 3rd Ed., Ch. 14)Patrick SibandaNoch keine Bewertungen

- Hermite Interpolation and Piecewise Polynomial ApproximationDokument4 SeitenHermite Interpolation and Piecewise Polynomial ApproximationHarshavardhan ReddyNoch keine Bewertungen

- Introduction To Numerical Methods and Matlab Programming For EngineersDokument180 SeitenIntroduction To Numerical Methods and Matlab Programming For EngineersNeneNoch keine Bewertungen

- IntroductionDokument7 SeitenIntroductionPatrick SibandaNoch keine Bewertungen

- Water level indicator alerts users and saves waterDokument8 SeitenWater level indicator alerts users and saves waterRida FatimaNoch keine Bewertungen

- Kabete PolyDokument41 SeitenKabete PolyWekesa RobinsonNoch keine Bewertungen

- Esp32 Hardware Design Guidelines enDokument33 SeitenEsp32 Hardware Design Guidelines enPlayer TopNoch keine Bewertungen

- Articulo 4Dokument5 SeitenArticulo 4Alexander Pozo Rosero DHNoch keine Bewertungen

- JVC Lt-26da9bj Bu 26db9bd (SCH)Dokument53 SeitenJVC Lt-26da9bj Bu 26db9bd (SCH)liviucatalinNoch keine Bewertungen

- Parallel Generators SynchronizationDokument16 SeitenParallel Generators Synchronizationfelwood36100% (1)

- 99 IC Projects 1980Dokument116 Seiten99 IC Projects 1980Pedralhada100% (19)

- 100 Watts OTL Amplifier Circuit Using Transistor MJ15003Dokument7 Seiten100 Watts OTL Amplifier Circuit Using Transistor MJ15003metinprivat01Noch keine Bewertungen

- Type KAVR 100, 130: Multi-Shot Auto-Reclose and Check Synchronizing RelayDokument8 SeitenType KAVR 100, 130: Multi-Shot Auto-Reclose and Check Synchronizing RelayĐiệnLêHuyNoch keine Bewertungen

- SLA7032M/SLA7033M 2-Phase/1-2 Phase Excitation 2-Phase Stepper Motor Unipolar Driver ICsDokument8 SeitenSLA7032M/SLA7033M 2-Phase/1-2 Phase Excitation 2-Phase Stepper Motor Unipolar Driver ICsJasper ElectronicaNoch keine Bewertungen

- CIRATA Excitation System Operation and Maintenance ManualDokument41 SeitenCIRATA Excitation System Operation and Maintenance Manualmozaix man100% (1)

- RA80H1415M1 RF MOSFET Power AmplifierDokument11 SeitenRA80H1415M1 RF MOSFET Power AmplifierAbbas MaghazehiNoch keine Bewertungen

- Codigos de ErroresDokument31 SeitenCodigos de ErroresItseed CorcaNoch keine Bewertungen

- By: D. B. Kulkarni Day - 1Dokument138 SeitenBy: D. B. Kulkarni Day - 1Dilip KulkarniNoch keine Bewertungen

- IDDQ TestingDokument38 SeitenIDDQ TestingVeeranjaneyulu DhikondaNoch keine Bewertungen

- Material DicaDokument157 SeitenMaterial DicaganeshNoch keine Bewertungen

- Measurement and Instrumentation Lab ManualDokument148 SeitenMeasurement and Instrumentation Lab Manualsramiz_1987100% (1)

- Microwave CommunicationDokument37 SeitenMicrowave CommunicationAmos Fiesta100% (1)

- Reverse-Feed Circuit BreakersDokument8 SeitenReverse-Feed Circuit Breakersaxf9dtjhdNoch keine Bewertungen

- Arduino Projects Experiments Part12Dokument20 SeitenArduino Projects Experiments Part12denydi100% (1)

- Ica Lab Project ReportDokument6 SeitenIca Lab Project ReportVishith Reddy100% (1)

- NI Multisim and Ultiboard BrochureDokument6 SeitenNI Multisim and Ultiboard Brochuremail4jiyoNoch keine Bewertungen

- Geh 6005Dokument439 SeitenGeh 6005hartman_mdNoch keine Bewertungen

- En LG-A120 Service Manual 20100707Dokument180 SeitenEn LG-A120 Service Manual 20100707kela_hss86Noch keine Bewertungen

- k17 PDFDokument2 Seitenk17 PDFcracker01Noch keine Bewertungen

- Technical Product Guide: Tricon SystemsDokument78 SeitenTechnical Product Guide: Tricon SystemsAngela FasuyiNoch keine Bewertungen

- A Review of 018-spl Mum Full Adder Performances FoDokument12 SeitenA Review of 018-spl Mum Full Adder Performances FoShaik Abdul Salam BatchaNoch keine Bewertungen

- Microprocessors and MicrocontrollersDokument280 SeitenMicroprocessors and MicrocontrollersJustin Angelo SildoraNoch keine Bewertungen

- SCAP - Power InverterDokument14 SeitenSCAP - Power InverterFolorunso AbiodunNoch keine Bewertungen

- Digital LogicDokument6 SeitenDigital LogicLittle VoiceNoch keine Bewertungen