Beruflich Dokumente

Kultur Dokumente

THEVA12LVDR820 Manual Rev.1.00 E PDF

Hochgeladen von

Anarsinh SolankiOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

THEVA12LVDR820 Manual Rev.1.00 E PDF

Hochgeladen von

Anarsinh SolankiCopyright:

Verfügbare Formate

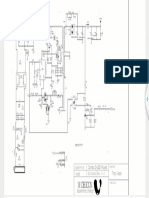

THine Electronics, Inc.

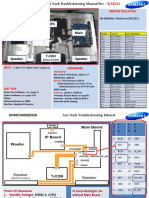

THEVA12LVDR820 Mode Setting & LVDS-Cable

2011/04/14

Description t=1.6mm

120mm

GND

FI-X30SSL-HF

RA201

RA202

RA203

RA204

RA205

RA206

+12V

THC63LVD824

THC63LVD823B

RA207

mm

120mm

RA208

R227

RA209

RA210

RA211

RES210

RES211

RES212

RES207

RES208

RES209

RES213

R233

RA217

RA218

RA219

RA220

←Low

FI-X30SSL-HF ←High

Tx MAP

Tx MAP

Tx MAP

Tx RS

Tx RS

DRVSEL

TEST5

TEST4

Tx PRBS

Rx R/F

Rx TESTO

Rx MODE1

Rx MODE0

Rx

Tx DDRN

Tx /PD

Tx

Tx

SW201 SW202 SW203

LVDS Cable Type

LVDS-Cable Type.

JAE JAE

↓ ↓

・

FI-X30HL

FI-X30HL

・

・

・

・

200mm

Copyright© 2011 THine Electronics

Electronics, Inc

Inc. 1/4 THEVA12LVDR820 manual Rev 1 00 E

THEVA12LVDR820_manual_Rev.1.00_E

THine Electronics, Inc.

THEVA12LVDR820 Mode Setting & LVDS-Cable

2011/04/14

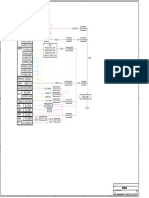

SW201 Setting * Def. : Default Setting

THC63LVD824

SW *

NodeName IC

Pin# Def. PinName Description

Pin#

Output Driverbility Select.

1 H RX DRVSEL 9 DRVSEL H : High power,

L : Low power.

Output Clock Triggering Edge Select.

2 H RX R/F 8 R/F H : Rising edge,

L : Falling edge.

3 L RX TESTO 7 GND Ground Pins for TTL outputs and digital circuitry.

Pixel Data Mode.

4 L RX MODE1 6 MODE1

MODE1 MODE0 Mode

L L Dual Link

5 L RX MODE0 5 MODE0 L H Single Link

H : Normal operation,

6 H RX /PD 4 /PDWN L : Power down (all outputs are pulled to ground)

7 L RX TEST1 3 GND Ground Pins for TTL outputs and digital circuitry.

8 H N/C - - Non Connected.

SW202 Setting * Def. : Default Setting

THC63LVD823B

SW * Node

IC PinName Description

Pin# Def. Name

Pin#

LVDS mapping table select.

1 L

SW-Pin#

RS Mapping Mode

1 2 3

2 H TX MAP 14 MAP L H(open) H(open) VIHM Mapping MODE1

H(open) L H(open) VIMM Mapping MODE2

H(open) H(open) L VILM Reserved

3 H

DDR function is active when

MODE<1:0> = HL(Single-in/Dual-out mode).

4 L TX DDRN 13 DDRN Open or H : DDR(Double Edge input) function disable.

L : DDR(Double Edge input) function enable.

LVDS swing mode, VREF select.

5 L

SW-Pin# Small Swing

RS LVDS Swing

5 6 7 Input Support

6 H TX RS 12 RS L H(open) H(open) VIHM 350mV N/A

H(open) L H(open) VIMM 350mV RS=VREFa

H(open) H(open) L VILM 200mV N/A

7 H a. VREF is Input Reference Voltage.

Input Clock Triggering Edge Select.

8 H TX RF 11 R/F H : Rising edge,

L : Falling edge

SW203 Setting * Def. : Default Setting

THC63LVD823B

SW *

NodeName IC

Pin# Def. PinName Description

Pin#

1 H TX TEST5 22 N/C Must be Open.

2 L TX TEST4 21 Reserved Must be tied to GND.

PRBS(Pseudo-Random Binary Sequence) generator is active in order to evaluate eye patterns when

MODE<1:0> = LL(Dual-in/Dual-out mode).

3 L TX PRBS 20 PRBS H : PRBS generator is enable.

L : Normal Operation

H : Normal operation,

4 H TX /PD 19 /PDWN L : Power down (all outputs are Hi-Z)

5 L TX 8/6 18 GND Ground Pins for TTL inputs and digital circuitry.

Output enable.

6 H TX OE 17 OE H:O Output

t t enable,

bl

L : Output disable (all outputs are Hi-Z).

Pixel Data Mode

7 L TX MODE0 16 MODE0 MODE1 MODE0 Mode

L L Dual Link(Dual-in/Dual-out)

H L Dual Link(Single-in/Dual-out)

L H Single Link(Dual-in/Single-out)

8 L TX MODE1 15 MODE1

H H Single Link(Single-in/Single-out)

Copyright© 2011 THine Electronics

Electronics, Inc

Inc. 2/4 THEVA12LVDR820 manual Rev 1 00 E

THEVA12LVDR820_manual_Rev.1.00_E

THine Electronics, Inc.

THEVA12LVDR820 Mode Setting & LVDS-Cable

2011/04/14

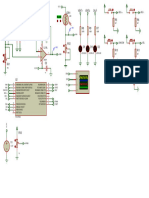

Measures Type

# Type Un-Mount 0Ω-Mount 33Ω-Mount

RES207 RA201 RA211

RES208 RA202 RA217

RES209 RA203 RA218

TTL-I/O

RES210 RA204 RA219

LVDS-input LVDS-output

RES211 RA205 RA220

1 THC63LVD823

THC63LVD824 RES212 RA206 R227

B RES213 RA207

R233 RA208

RA209

RA210

RES207 RA201 RA211

TTL-I/O

RES208 RA202 RA217

LVDS-input LVDS-output

THC63LVD823 RES209 RA203 RA218

THC63LVD824

B RES210 RA204 RA219

RES211 RA205 RA220

2

RES212 RA206 R227

RES213 RA207

R233 RA208

RA209

TTL-moniter

RA210

RES207 RA201 RA211

TTL-I/O THC63LVD823B

RES208 RA202 RA217

LVDS-input

THC63LVD823 RES209 RA203 RA218

THC63LVD824

B RES210 RA204 RA219

RES211 RA205 RA220

3

RES212 RA206 R227

RES213 RA207

R233 RA208

RA209

TTL-output

RA210

RA201 RA211 RES207

TTL-I/O

RA202 RA217 RES208

LVDS-output

THC63LVD823 RA203 RA218 RES209

THC63LVD824

B RA204 RA219 RES210

RA205 RA220 RES211

4

RA206 R227 RES212

RA207 RES213

RA208 R233

RA209

TTL-input

RA210

Copyright© 2011 THine Electronics

Electronics, Inc

Inc. 3/4 THEVA12LVDR820 manual Rev 1 00 E

THEVA12LVDR820_manual_Rev.1.00_E

THine Electronics, Inc.

THEVA12LVDR820 Mode Setting & LVDS-Cable

2011/04/14

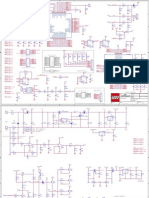

Notices and Requests

1. The product specifications described in this material are subject to change without prior notice.

2. The circuit diagrams

g described in this material are examples

p of the application

pp which may y not always

y

apply to the customer’s design. We are not responsible for possible errors and omissions in this material.

Please note if errors or omissions should be found in this material, we may not be able to correct them

3. This material contains our copy right, know-how or other proprietary. Copying or disclosing to third parties

the contents of this material without our prior permission is prohibited.

4. Note that if infringement of any third party's industrial ownership should occur by using this product, we will be

e e pted from

exempted o tthee responsibility

espo s b ty uunless

ess itt ddirectly

ect y relates

e ates to tthee production

p oduct o pprocess

ocess oor functions

u ct o s oof tthee pproduct.

oduct.

5. This product is presumed to be used for general electric equipment, not for the applications which require very hi

reliability (including medical equipment directly concerning people's life, aerospace equipment, or nuclear contro

equipment). Also, when using this product for the equipment concerned with the control and safety of the

transportation means, the traffic signal equipment, or various Types of safety equipment, please do it after applyin

appropriate measures to the product.

6. Despite our utmost efforts to improve the quality and reliability of the product, faults will occur with a certain

small probability, which is inevitable to a semi-conductor product. Therefore, you are encouraged to have suffici

redundant or error preventive design applied to the use of the product so as not to have our product cause any soc

or public damage.

7. Please note that this product is not designed to be radiation-proof.

8. Customers are asked, if required, to judge by themselves if this product falls under the category of strategic good

under the Foreign Exchange and Foreign Trade Control Law.

Law

THine Electronics, Inc.

sales@thine.co.jp

Copyright© 2011 THine Electronics, Inc. 4/4 THEVA12LVDR820_manual_Rev.1.00_E

Das könnte Ihnen auch gefallen

- V2164 PDFDokument10 SeitenV2164 PDFjoel marshallNoch keine Bewertungen

- Samsung UN40C5000QFXZA Fast TrackDokument4 SeitenSamsung UN40C5000QFXZA Fast TrackJustin NgNoch keine Bewertungen

- Trainning Material of PW PE371C4Dokument35 SeitenTrainning Material of PW PE371C4بوند بوندNoch keine Bewertungen

- LG 32LN520BDokument43 SeitenLG 32LN520Bboroda2410100% (6)

- LVDSDokument158 SeitenLVDSHemantkumar100% (1)

- PSU Guide Semi 25A2-E-0007 201903Dokument24 SeitenPSU Guide Semi 25A2-E-0007 201903crisplebeuNoch keine Bewertungen

- Cyberlux TV-20CX Chassis 34BIDokument1 SeiteCyberlux TV-20CX Chassis 34BIEzequiel Milá de la Roca100% (2)

- P6NC60FPDokument10 SeitenP6NC60FPJose Angel TorrealbaNoch keine Bewertungen

- Panasonic TH l32c8kDokument54 SeitenPanasonic TH l32c8kzachariah321100% (2)

- A Aiwa Service Manual CD MechanismDokument22 SeitenA Aiwa Service Manual CD MechanismcobrabrNoch keine Bewertungen

- Fallas Tv's Sony Mas de 1000Dokument130 SeitenFallas Tv's Sony Mas de 1000london33550% (2)

- LTA320AP05 SamsungDokument26 SeitenLTA320AP05 SamsungAndy AnsahNoch keine Bewertungen

- Manual Service LN40C550J1RDokument86 SeitenManual Service LN40C550J1RAngel Luciano Ramon GomezNoch keine Bewertungen

- Sony STR-De635 Ver 1.1Dokument58 SeitenSony STR-De635 Ver 1.1rumendm100% (1)

- AIWA AZG-D SvcMnlsDokument59 SeitenAIWA AZG-D SvcMnlsavrelecNoch keine Bewertungen

- Aiwa 3Cd-Player 4ZG-1 Service ManualDokument24 SeitenAiwa 3Cd-Player 4ZG-1 Service ManualMaria Aparecida AlmeidaNoch keine Bewertungen

- 21TS1020 3P66SN STR-W6554A TDA11145PS N3 LA78141 LA7840 TDA7266 5800 A3P660 000 CompletoDokument32 Seiten21TS1020 3P66SN STR-W6554A TDA11145PS N3 LA78141 LA7840 TDA7266 5800 A3P660 000 CompletoRonal Gutierrez100% (1)

- Service Manual: CX-JDS11Dokument64 SeitenService Manual: CX-JDS11German MoyaNoch keine Bewertungen

- Rsag2 820 6823 PDFDokument15 SeitenRsag2 820 6823 PDFPrint Image100% (1)

- 9441 Panasonic SA-AK15 Sistema Audio CD-Casette Manual de ServicioDokument69 Seiten9441 Panasonic SA-AK15 Sistema Audio CD-Casette Manual de ServicioJesus Antonio Gonzalez QuinteroNoch keine Bewertungen

- LG Plasma Panel Alignment GuideDokument170 SeitenLG Plasma Panel Alignment GuideJothi BaskarNoch keine Bewertungen

- Mainboard 35022968Dokument14 SeitenMainboard 35022968Manuel GarciaNoch keine Bewertungen

- Color TV TS2453 Alignment and Repair ManualDokument38 SeitenColor TV TS2453 Alignment and Repair Manualdmst6222Noch keine Bewertungen

- AKAI - LEA-22H03P Service Manual PDFDokument58 SeitenAKAI - LEA-22H03P Service Manual PDFJFIonienNoch keine Bewertungen

- Toshiba UM 32E200U 37E200U 40E200U Chasis E200U Manual EntrenamientoDokument38 SeitenToshiba UM 32E200U 37E200U 40E200U Chasis E200U Manual EntrenamientoPablo Acapulco GuerreroNoch keine Bewertungen

- 20mu14 PDFDokument24 Seiten20mu14 PDFOmar Cuellar BNoch keine Bewertungen

- Samsung Ln26!32!3740a330j1d Chassis N45a SMDokument173 SeitenSamsung Ln26!32!3740a330j1d Chassis N45a SMMario PérezNoch keine Bewertungen

- Le40f86bd PDFDokument278 SeitenLe40f86bd PDFMalcolm SandersNoch keine Bewertungen

- CM6800 Design GuideDokument34 SeitenCM6800 Design GuidedkelicNoch keine Bewertungen

- Tutorial para Fuentes de Poder LCDDokument37 SeitenTutorial para Fuentes de Poder LCDioham4715100% (1)

- TP VST59 PDokument1 SeiteTP VST59 PpedroNoch keine Bewertungen

- Panasonic TH42PX75U Chassis GP10DHU TV Plasma Service ManualDokument130 SeitenPanasonic TH42PX75U Chassis GP10DHU TV Plasma Service ManualPopa FlorinNoch keine Bewertungen

- Circuito de Controle Do Display TV Samsung Ln-26A330J: (PLACA T-CON V260-B1-C04)Dokument2 SeitenCircuito de Controle Do Display TV Samsung Ln-26A330J: (PLACA T-CON V260-B1-C04)ELECTRONICA J Y CENTRO ELECTRONICO100% (2)

- 42PW350 PDFDokument16 Seiten42PW350 PDFjorge furtado de freitasNoch keine Bewertungen

- Samsung Un32b6000 Un40b6000 Un46b6000 Un55b6000 Un6v Led Training PDFDokument117 SeitenSamsung Un32b6000 Un40b6000 Un46b6000 Un55b6000 Un6v Led Training PDFGilmar Ferreira100% (1)

- LCD TV General Troubleshooting and Tips To RCA L32WD22 FixDokument6 SeitenLCD TV General Troubleshooting and Tips To RCA L32WD22 Fixdfenncatman20% (1)

- LC320WXN Saa1Dokument39 SeitenLC320WXN Saa1ALex93Noch keine Bewertungen

- Sanyo Repair Tips CollectionDokument24 SeitenSanyo Repair Tips CollectionH3liax90% (10)

- Fuente Power Suppy 34008015 TV KonkaDokument2 SeitenFuente Power Suppy 34008015 TV KonkaAndres Ricardo Hernandez Gonzalez100% (3)

- LC470WX1-SLA_6870C-0143B PCB Schematic SectionsDokument35 SeitenLC470WX1-SLA_6870C-0143B PCB Schematic SectionsEveraldoNoch keine Bewertungen

- Manual Serviço - Aiwa NSX-D77, NSX-T76, NSX-T77Dokument48 SeitenManual Serviço - Aiwa NSX-D77, NSX-T76, NSX-T77fabioferraoNoch keine Bewertungen

- Manual de Servicio TV Toshiba 20ar20 - 30Dokument32 SeitenManual de Servicio TV Toshiba 20ar20 - 30Antonio José Montaña Pérez de Cristo100% (1)

- Derbot Master CCT, Post Book PubDokument2 SeitenDerbot Master CCT, Post Book PubSreekanth PolaNoch keine Bewertungen

- Circuito Control de Temperatura y MotorDokument1 SeiteCircuito Control de Temperatura y MotorCarlos GallardoNoch keine Bewertungen

- Ret&Tma SolutionDokument7 SeitenRet&Tma SolutionLuan DmNoch keine Bewertungen

- RS485 5 Click Schematic v103Dokument1 SeiteRS485 5 Click Schematic v103Lauro Da Silva100% (1)

- Appendix 1-LEGO Mind Storms NXT Hardware SchematicDokument4 SeitenAppendix 1-LEGO Mind Storms NXT Hardware SchematicAlfon DeLerín100% (1)

- Toshiba Sd-130esb, Sd-130ese Service ManualDokument70 SeitenToshiba Sd-130esb, Sd-130ese Service ManualsubisanNoch keine Bewertungen

- Tarea 2 AODokument5 SeitenTarea 2 AOChuz AlfaroNoch keine Bewertungen

- GE Fanuc CMMDokument6 SeitenGE Fanuc CMMmarcosNoch keine Bewertungen

- Koch Twintone I SN0631-0760Dokument4 SeitenKoch Twintone I SN0631-0760jazzyjoepassNoch keine Bewertungen

- HX8227Dokument41 SeitenHX8227vidoj47105Noch keine Bewertungen

- Schematic - Zigbee Stick 4.0 CH340CDokument1 SeiteSchematic - Zigbee Stick 4.0 CH340CSergey SuloevNoch keine Bewertungen

- CAN Schematics ModuleDokument1 SeiteCAN Schematics ModuleEssam AltamimiNoch keine Bewertungen

- MSTV2202-N1 Circuit Diagramv69Dokument9 SeitenMSTV2202-N1 Circuit Diagramv69Sagar KhadeNoch keine Bewertungen

- Soldering circuit diagram guideDokument1 SeiteSoldering circuit diagram guidesiogNoch keine Bewertungen

- Secondary Side Regulated Vs Primary Side Regulated: Flyback Converter Is Regulated in One of Two WaysDokument4 SeitenSecondary Side Regulated Vs Primary Side Regulated: Flyback Converter Is Regulated in One of Two WaysJuan Carlos Reyes RiveraNoch keine Bewertungen

- Greenchip Tea1761 Synchronous Rectification and Feedback ControllerDokument11 SeitenGreenchip Tea1761 Synchronous Rectification and Feedback Controllerdado0905Noch keine Bewertungen

- Afficheur de Scores SchemaDokument1 SeiteAfficheur de Scores SchemaSalah DAHOUATHINoch keine Bewertungen

- 50HP81SVMDokument101 Seiten50HP81SVMClinton McDadeNoch keine Bewertungen

- Soni Penal Information PDFDokument290 SeitenSoni Penal Information PDFAnarsinh Solanki100% (1)

- TFT Display by Shafi PDFDokument88 SeitenTFT Display by Shafi PDFAnarsinh Solanki100% (1)

- Vidiocon Combo Service Manual PDFDokument58 SeitenVidiocon Combo Service Manual PDFAnarsinh Solanki68% (40)

- Haier 40D2500 - MSD3393LU LCD TV SM PDFDokument51 SeitenHaier 40D2500 - MSD3393LU LCD TV SM PDFAnarsinh SolankiNoch keine Bewertungen

- White Paper ACF Bonding Technology 08 10 PDFDokument6 SeitenWhite Paper ACF Bonding Technology 08 10 PDFAnarsinh SolankiNoch keine Bewertungen

- TCL L32D10 MT23-LA LCD TV SM PDFDokument50 SeitenTCL L32D10 MT23-LA LCD TV SM PDFAnarsinh Solanki100% (2)

- Videocon Chassis mst6m181 LCD TV SM 1525414977620 PDFDokument61 SeitenVideocon Chassis mst6m181 LCD TV SM 1525414977620 PDFAnarsinh SolankiNoch keine Bewertungen

- Videocon Combo - 72318 - 1057 - Office - Lens PDFDokument1 SeiteVideocon Combo - 72318 - 1057 - Office - Lens PDFAnarsinh SolankiNoch keine Bewertungen

- SmpsDokument96 SeitenSmpsAnarsinh SolankiNoch keine Bewertungen

- 40E3500ADokument53 Seiten40E3500Asamsularief03Noch keine Bewertungen

- AUTOMATIC RAILWAY GATE CONTROLLER-reportDokument57 SeitenAUTOMATIC RAILWAY GATE CONTROLLER-reportAnarsinh Solanki75% (8)

- BJT Amplifier Circuit GuideDokument23 SeitenBJT Amplifier Circuit GuideJanko JaridicNoch keine Bewertungen

- Nuclear BatteryDokument20 SeitenNuclear BatteryAkhil Menon100% (4)

- Polyfuse: Seminar Report OnDokument26 SeitenPolyfuse: Seminar Report OnAnarsinh Solanki100% (3)

- Erp NDokument11 SeitenErp NPrateek MallNoch keine Bewertungen

- AutoCAD HotkeysDokument6 SeitenAutoCAD HotkeysKaryll Heart LayugNoch keine Bewertungen

- Section A QS1 (A) List Various Characteristics of A System. AS Characteristics of A SystemDokument18 SeitenSection A QS1 (A) List Various Characteristics of A System. AS Characteristics of A Systemsarabjit kaurNoch keine Bewertungen

- Memory Databook 1984Dokument468 SeitenMemory Databook 1984Marco SabbaNoch keine Bewertungen

- How To Recover Extreme Switch Username & Password - Extreme Networks Support CommunityDokument11 SeitenHow To Recover Extreme Switch Username & Password - Extreme Networks Support Communitylala123Noch keine Bewertungen

- Xenapp Xendesktop 7 17 PDFDokument990 SeitenXenapp Xendesktop 7 17 PDFBrad AndersonNoch keine Bewertungen

- Cidam EtechDokument12 SeitenCidam EtechGhil Tiongco50% (2)

- RAID Technology The OneDokument36 SeitenRAID Technology The OneAi Zil ZaczsNoch keine Bewertungen

- Alexandra Whitney Samuel Hacktivism and The Future of Political ParticipationDokument284 SeitenAlexandra Whitney Samuel Hacktivism and The Future of Political ParticipationSarahHawasNoch keine Bewertungen

- Machine Learning: Andrew NG's Course From Coursera: PresentationDokument4 SeitenMachine Learning: Andrew NG's Course From Coursera: PresentationDo Thu ThuyNoch keine Bewertungen

- Input Output FilesDokument63 SeitenInput Output FilesmattdmnNoch keine Bewertungen

- Intro To Cyber Security PresentationDokument31 SeitenIntro To Cyber Security Presentationredred121Noch keine Bewertungen

- GCC and Make: Compiling, Linking and Building C/C++ ApplicationsDokument11 SeitenGCC and Make: Compiling, Linking and Building C/C++ ApplicationssemabayNoch keine Bewertungen

- Ripple Connect Product SheetDokument10 SeitenRipple Connect Product SheetMlungisi Lu NdlovuNoch keine Bewertungen

- Microsemi TP5000 DatasheetDokument2 SeitenMicrosemi TP5000 DatasheetMartinNoch keine Bewertungen

- Srf's BetterTouchTool GesturesDokument5 SeitenSrf's BetterTouchTool GesturesBrady FernandezNoch keine Bewertungen

- Cisco Aironet 3800 Series Access PointsDokument5 SeitenCisco Aironet 3800 Series Access Pointsbonsai todayNoch keine Bewertungen

- Ejemplo Cronograma Del Proyecto Según Pud RupDokument2 SeitenEjemplo Cronograma Del Proyecto Según Pud RupNair Estefani Hancco CruzNoch keine Bewertungen

- Language ModellingDokument3 SeitenLanguage ModellingPrakash SawantNoch keine Bewertungen

- Technical Manual of BR-15 Banknote Recycling ModuleDokument9 SeitenTechnical Manual of BR-15 Banknote Recycling ModuleJohn MarkNoch keine Bewertungen

- Green Computing Guide for Reducing Environmental ImpactDokument17 SeitenGreen Computing Guide for Reducing Environmental ImpactAkhyar AyubNoch keine Bewertungen

- UNDP Quantum User Guide For Suppliers October Edition PDFDokument111 SeitenUNDP Quantum User Guide For Suppliers October Edition PDFShahadath HossenNoch keine Bewertungen

- Guided By: Mr. Sitangshu Dey Submitted By: Kanchana Nath Himani Padalia (Mca I Sem)Dokument16 SeitenGuided By: Mr. Sitangshu Dey Submitted By: Kanchana Nath Himani Padalia (Mca I Sem)chandaka sai nikithaNoch keine Bewertungen

- Could Not Find Transformation Definition For: BU - DM BU - QUARTER - PLAN - F Failed To Import: M - LOAD - BU - QUARTER - PLAN - FDokument3 SeitenCould Not Find Transformation Definition For: BU - DM BU - QUARTER - PLAN - F Failed To Import: M - LOAD - BU - QUARTER - PLAN - FDeepak NarangNoch keine Bewertungen

- Erlangga Jti Uii SIM 2010 Basic Concept of MIS Part 05 Reg IPDokument28 SeitenErlangga Jti Uii SIM 2010 Basic Concept of MIS Part 05 Reg IPNoormalita IrvianaNoch keine Bewertungen

- Cyber Security III: Securing VPN and Emerging TechDokument37 SeitenCyber Security III: Securing VPN and Emerging TechSmita SaudagarNoch keine Bewertungen

- Ericsson BSC CommandsDokument9 SeitenEricsson BSC CommandsFlavio Farias De MedeirosNoch keine Bewertungen

- APE 3.5 Operation Manual enUS 28130426507Dokument30 SeitenAPE 3.5 Operation Manual enUS 28130426507068 RakeshNoch keine Bewertungen

- Dynamic Approver Groups Simplify AME Rules at Steel CompanyDokument20 SeitenDynamic Approver Groups Simplify AME Rules at Steel CompanyPoorna Chandra GaralapatiNoch keine Bewertungen

- PM Project Postmortem SurveyDokument8 SeitenPM Project Postmortem SurveyEduardo Duarte100% (1)