Beruflich Dokumente

Kultur Dokumente

Read-Only Memory (Usually Known by Its

Hochgeladen von

Anonymous 04kV8ba0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

19 Ansichten18 SeitenOriginaltitel

lecture9b.pdf

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

19 Ansichten18 SeitenRead-Only Memory (Usually Known by Its

Hochgeladen von

Anonymous 04kV8baCopyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 18

ROM (Read Only Memory)

• Read-only memory (usually known by its

acronym, ROM) is a class of storage media used

in computers and other electronic devices.

• Because data stored in ROM cannot be modified

(at least not very quickly or easily), it is mainly

used to distribute firmware

• Firmware is software that is very closely tied to

specific hardware, and unlikely to require

frequent updates.

• In its strictest sense, ROM refers only to mask ROM

(the oldest type of solid state ROM), which is fabricated

with the desired data permanently stored in it, and

thus can never be modified.

• However, more modern types such as EPROM and flash

EEPROM can be erased and re-programmed multiple

times; they are still described as "read-only memory"

because the reprogramming process is generally

infrequent, comparatively slow, and often does not

permit random access writes to individual memory

locations.

• Despite the simplicity of mask ROM, economies of

scale and field-programmability often make

reprogrammable technologies more flexible and

inexpensive, so that mask ROM is rarely used in new

products as of 2007.

• Classic mask-programmed ROM chips are

integrated circuits that physically encode the data

to be stored, and thus it is impossible to change

their contents after fabrication. Other types of

non-volatile solid-state memory permit some

degree of modification:

Types of ROM

Programmable read-only memory (PROM), or one-

time programmable ROM (OTP), can be written

to or programmed via a special device called a

PROM programmer. Typically, this device uses

high voltages to permanently destroy or create

internal links (fuses or antifuses) within the chip.

Consequently, a PROM can only be programmed

once.

• Erasable programmable read-only memory (EPROM) can be erased

by exposure to strong ultraviolet light (typically for 10 minutes or

longer), then rewritten with a process that again requires

application of higher than usual voltage. Repeated exposure to UV

light will eventually wear out an EPROM, but the endurance of

most EPROM chips exceeds 1000 cycles of erasing and

reprogramming. EPROM chip packages can often be identified by

the prominent quartz "window" which allows UV light to enter.

After programming, the window is typically covered with a label to

prevent accidental erasure.

• Electrically erasable programmable read-only memory (EEPROM)

is based on a similar semiconductor structure to EPROM, but allows

its entire contents (or selected banks) to be electrically erased, then

rewritten electrically, so that they need not be removed from the

computer (or camera, MP3 player, etc.). Writing or flashing an

EEPROM is much slower (milliseconds per bit) than reading from a

ROM or writing to a RAM (nanoseconds in both cases).

• Electrically alterable read-only memory (EAROM) is a type of

EEPROM that can be modified one bit at a time. Writing is a very

slow process and again requires higher voltage (usually around 12

V) than is used for read access. EAROMs are intended for

applications that require infrequent and only partial rewriting.

EAROM may be used as non-volatile storage for critical system

setup information; in many applications, EAROM has been

supplanted by CMOS RAM supplied by mains power and backed-up

with a lithium battery.

• Flash memory (or simply flash) is a modern type of EEPROM

invented in 1984. Flash memory can be erased and rewritten faster

than ordinary EEPROM, and newer designs feature very high

endurance (exceeding 1,000,000 cycles). Modern NAND flash makes

efficient use of silicon chip area, resulting in individual ICs with a

capacity as high as 16 GB as of 2007[update]; this feature, along with

its endurance and physical durability, has allowed NAND flash to

replace magnetic in some applications (such as USB flash drives).

Flash memory is sometimes called flash ROM or flash EEPROM

when used as a replacement for older ROM types, but not in

applications that take advantage of its ability to be modified quickly

and frequently.

DRAM

• Dynamic random access memory (DRAM) is a

type of random access memory that stores

each bit of data in a separate capacitor within

an integrated circuit. Since real capacitors leak

charge, the information eventually fades

unless the capacitor charge is refreshed

periodically. Because of this refresh

requirement, it is a dynamic memory as

opposed to SRAM and other static memory.

Types of DRAM

• Asynchronous DRAM

• Fast Page Mode (FPM) DRAM or FPRAM

• Extended Data Out (EDO) DRAM

• Burst EDO (BEDO) DRAM

• Synchronous Dynamic RAM (SDRAM)

• Direct Rambus DRAM (DRDRAM)

• Double Data Rate (DDR) SDRAM

Asynchronous DRAM

• This is the basic form, from which all others

are derived. An asynchronous DRAM chip has

power connections, some number of address

inputs (typically 12), and a few (typically 1 or

4) bidirectional data lines. There are four

active low control signals

Fast Page Mode (FPM) DRAM or

FPRAM

• Fast page mode DRAM is also called FPM DRAM,

Page mode DRAM, Fast page mode memory, or

Page mode memory.

• In page mode, a row of the DRAM can be kept

"open" by holding /RAS low while performing

multiple reads or writes with separate pulses of

/CAS. so that successive reads or writes within

the row do not suffer the delay of precharge and

accessing the row. This increases the

performance of the system when reading or

writing bursts of data.

Extended Data Out (EDO) DRAM

• EDO DRAM is similar to Fast Page Mode

DRAM with the additional feature that a new

access cycle can be started while keeping the

data output of the previous cycle active. This

allows a certain amount of overlap in

operation (pipelining), allowing somewhat

improved performance. It was 5% faster than

Fast Page Mode DRAM, which it began to

replace in 1993.

Burst EDO (BEDO) DRAM

• An evolution of the former, Burst EDO DRAM,

could process four memory addresses in one

burst, for a maximum of 5-1-1-1, saving an

additional three clocks over optimally

designed EDO memory. It was done by adding

an address counter on the chip to keep track

of the next address. BEDO also added a

pipelined stage allowing page-access cycle to

be divided into two components.

Synchronous Dynamic RAM (SDRAM)

• SDRAM refers to synchronous dynamic random access

memory, a term that is used to describe dynamic random

access memory that has a synchronous interface.

Traditionally, dynamic random access memory (DRAM) has

an asynchronous interface which means that it responds as

quickly as possible to changes in control inputs. SDRAM has

a synchronous interface, meaning that it waits for a clock

signal before responding to control inputs and is therefore

synchronized with the computer's system bus. The clock is

used to drive an internal finite state machine that pipelines

incoming instructions. This allows the chip to have a more

complex pattern of operation than asynchronous DRAM

which does not have a synchronized interface.

Direct Rambus DRAM (DRDRAM)

• The first PC motherboards with support for RDRAM

debuted in 1999. They supported PC-800 RDRAM,

which operated at 400 MHz and delivered 1600 MB/s

of bandwidth over a 16-bit bus using a 184-pin RIMM

form factor. Data is transferred on both the rising and

falling edges of the clock signal, a technique known as

double data rate. For marketing reasons the physical

clock rate was multiplied by two (because of the DDR

operation); therefore, the 400 MHz Rambus standard

was named PC-800. This was significantly faster than

the previous standard, PC-133 SDRAM, which operated

at 133 MHz and delivered 1066 MB/s of bandwidth

over a 64-bit bus using a 168-pin DIMM form factor.

Double Data Rate (DDR) SDRAM

• Double data rate (DDR) SDRAM was a later

development of SDRAM, used in PC memory beginning

in 2000. DDR2 SDRAM was originally seen as a minor

enhancement (based upon the industry standard

single-core CPU) on DDR SDRAM that mainly afforded

higher clock rates and somewhat deeper pipelining.

However, with the introduction and rapid acceptance

of the multi-core CPU in 2006, it is generally expected

in the industry that DDR2 will revolutionize the existing

physical DDR-SDRAM standard. Further, with the

development and introduction of DDR3 SDRAM in

2007, it is anticipated DDR3 will rapidly replace the

more limited DDR and newer DDR2.

• Like all SDRAM implementations, DDR2 stores

memory in memory cells that are activated with

the use of a clock signal to synchronize their

operation with an external data bus. Like DDR

before it, DDR2 cells transfer data both on the

rising and falling edge of the clock (a technique

called "double pumping"). The key difference

between DDR and DDR2 is that in DDR2 the bus is

clocked at twice the rate of the memory cells, so

four bits of data can be transferred per memory

cell cycle. Thus, without changing the memory

cells themselves, DDR2 can effectively operate at

twice the data rate of DDR

Data

Peak

Standard Memory I/O Bus transfers Module

Cycle time transfer

name clock clock per name

rate

second

400 3200 MB/

DDR2-400 100 MHz 10 ns 200 MHz PC2-3200

Million s

533 PC2-4200 4266 MB/

DDR2-533 133 MHz 7.5 ns 266 MHz

Million PC2-43001 s

667 PC2-5300 5333 MB/

DDR2-667 166 MHz 6 ns 333 MHz

Million PC2-54001 s

800 6400 MB/

DDR2-800 200 MHz 5 ns 400 MHz PC2-6400

Million s

DDR2- 1066 PC2-8500 8533 MB/

266 MHz 3.75 ns 533 MHz

1066 Million PC2-86001 s

• DDR3 memory provides a reduction in power consumption

of 30% compared to DDR2 modules due to DDR3's 1.5 V

supply voltage, compared to DDR2's 1.8 V or DDR's 2.5 V.

The 1.5 V supply voltage works well with the 90 nanometer

fabrication technology used in the original DDR3 chips.

Some manufacturers further propose using "dual-gate"

transistors to reduce leakage of current.

• DDR3 modules can transfer data at a rate of 800–1600 MHz

using both rising and falling edges of a 400–800 MHz I/O

clock. In comparison, DDR2's current range of data transfer

rates is 400–800 MHz using a 200–400 MHz I/O clock, and

DDR's range is 200–400 MHz based on a 100–200 MHz I/O

clock.

Data

Peak

Standard Memory I/O Bus transfers Module

Cycle time transfer

name clock clock per name

rate

second

800 6400 MB/

DDR3-800 100 MHz 10 ns 400 MHz PC3-6400

Million s

DDR3- 1066 8533 MB/

133 MHz 7.5 ns 533 MHz PC3-8500

1066 Million s

DDR3- 1333 PC3- 10667 MB

166 MHz 6 ns 667 MHz

1333 Million 10600 /s[1]

DDR3- 1600 PC3- 12800 MB

200 MHz 5 ns 800 MHz

1600 Million 12800 /

Das könnte Ihnen auch gefallen

- Placa Mae (p5vdc-Tvm) ManualDokument70 SeitenPlaca Mae (p5vdc-Tvm) ManualRoberto Azevedo da SilvaNoch keine Bewertungen

- Chapter 4 Memory ElementDokument87 SeitenChapter 4 Memory ElementWann FarieraNoch keine Bewertungen

- Computer Hardware Fundamentals NotesDokument9 SeitenComputer Hardware Fundamentals NotesfoggybluueNoch keine Bewertungen

- Nintendo 64 Architecture: Architecture of Consoles: A Practical Analysis, #8Von EverandNintendo 64 Architecture: Architecture of Consoles: A Practical Analysis, #8Noch keine Bewertungen

- Nintendo DS Architecture: Architecture of Consoles: A Practical Analysis, #14Von EverandNintendo DS Architecture: Architecture of Consoles: A Practical Analysis, #14Noch keine Bewertungen

- Design of Sram in VerilogDokument124 SeitenDesign of Sram in VerilogAbhi Mohan Reddy100% (3)

- Machine Cycle and Memory TypesDokument37 SeitenMachine Cycle and Memory TypesAravind YadavNoch keine Bewertungen

- Types of MemoryDokument14 SeitenTypes of MemorySriram RamakrishnanNoch keine Bewertungen

- Memory TypesDokument3 SeitenMemory Typesapi-3836139Noch keine Bewertungen

- Activity No. 2 Computer Architecture ICS 222 (LAB) : Submitted byDokument4 SeitenActivity No. 2 Computer Architecture ICS 222 (LAB) : Submitted byJasmine Mycarl MananganNoch keine Bewertungen

- THE Rom and Ram: Technical Vocational & Livelihood Computer Systems Servicing 12 First QuarterDokument4 SeitenTHE Rom and Ram: Technical Vocational & Livelihood Computer Systems Servicing 12 First QuarterbogusbaikawNoch keine Bewertungen

- Memory DevicesDokument19 SeitenMemory DevicesMst. Najnin SultanaNoch keine Bewertungen

- Memory Types and Their Uses: RAM, ROM, Cache and Virtual MemoryDokument21 SeitenMemory Types and Their Uses: RAM, ROM, Cache and Virtual MemoryManish JangidNoch keine Bewertungen

- Group Members: Karnail Katoch Vishal Mahant Archana Kahrinar Mohammad Pisavadi Kashyap BaradDokument55 SeitenGroup Members: Karnail Katoch Vishal Mahant Archana Kahrinar Mohammad Pisavadi Kashyap BaradpRiNcE DuDhAtRaNoch keine Bewertungen

- Memory System Design PDFDokument13 SeitenMemory System Design PDFNISHANT395Noch keine Bewertungen

- "Memory Interface" in (Microprocessor and Assembly Language)Dokument22 Seiten"Memory Interface" in (Microprocessor and Assembly Language)MUHAMMAD ABDULLAHNoch keine Bewertungen

- CDCA 2203 Ram & RomDokument11 SeitenCDCA 2203 Ram & RomMUHAMAD AMMAR SYAFIQ BIN MAD ZIN STUDENTNoch keine Bewertungen

- COA-Unit 4 Memory OraganizationDokument60 SeitenCOA-Unit 4 Memory Oraganizationtanuja rajputNoch keine Bewertungen

- Memory DevicesDokument60 SeitenMemory DevicesShahin ShuvoNoch keine Bewertungen

- MemoryDokument10 SeitenMemorynet_friend05Noch keine Bewertungen

- Unit 3 OF ESDDokument22 SeitenUnit 3 OF ESDTanveer ShariffNoch keine Bewertungen

- Types of RAM'sDokument20 SeitenTypes of RAM'sdisha_gopalaniNoch keine Bewertungen

- Memory and StorageDokument46 SeitenMemory and StoragekasthurimahaNoch keine Bewertungen

- Types of Computer MemoryDokument8 SeitenTypes of Computer MemoryPUBG OFFICIALNoch keine Bewertungen

- Defination of ROMDokument4 SeitenDefination of ROMshubham shakyaNoch keine Bewertungen

- Different Types of RAM FPM RamDokument2 SeitenDifferent Types of RAM FPM RamJayson RegayaNoch keine Bewertungen

- Memory Hierarchy and RAM/ROM ArchitectureDokument31 SeitenMemory Hierarchy and RAM/ROM ArchitectureAbdul Wahid NohriNoch keine Bewertungen

- Internal and External Devices of ComputerDokument53 SeitenInternal and External Devices of ComputerSayoojNoch keine Bewertungen

- Ram RomDokument42 SeitenRam Rommohit mishraNoch keine Bewertungen

- Read and write memory basicsDokument3 SeitenRead and write memory basicsmadesrrrrNoch keine Bewertungen

- Rom 1Dokument14 SeitenRom 1manoj kumar rout100% (2)

- Memories: Volatile and Non-VolatileDokument8 SeitenMemories: Volatile and Non-VolatilejancyphilipNoch keine Bewertungen

- Types of RAM - DRAM vs SRAMDokument6 SeitenTypes of RAM - DRAM vs SRAM93headbangerNoch keine Bewertungen

- The Notion of ReadDokument5 SeitenThe Notion of ReadDharan ChowdharyNoch keine Bewertungen

- DRAM Packaging Formats and TechnologiesDokument4 SeitenDRAM Packaging Formats and Technologiesrakista yec100% (1)

- Types of RAMDokument2 SeitenTypes of RAMCerina Avergonzado BuendiaNoch keine Bewertungen

- Memory Devices JayjeetDokument53 SeitenMemory Devices JayjeetmansurNoch keine Bewertungen

- Basic Microprocessor - Software Architecture: The MemoryDokument22 SeitenBasic Microprocessor - Software Architecture: The MemoryMim FauziNoch keine Bewertungen

- Primary MemoryDokument20 SeitenPrimary MemoryAayushmanNoch keine Bewertungen

- Types of RAM and ROMDokument6 SeitenTypes of RAM and ROMTinu Elza Vinu100% (1)

- Computer Memories ExplainedDokument6 SeitenComputer Memories ExplainedMuhammad UmairNoch keine Bewertungen

- Chapter 3.3Dokument4 SeitenChapter 3.3OzzyNoch keine Bewertungen

- CP and I Assing.Dokument12 SeitenCP and I Assing.Aditya YewleyNoch keine Bewertungen

- What is RAM? A guide to Random Access Memory types, features and moreDokument25 SeitenWhat is RAM? A guide to Random Access Memory types, features and moreSayyan Shaikh100% (1)

- DDR Memory Types and Specifications GuideDokument26 SeitenDDR Memory Types and Specifications GuideAlpynNoch keine Bewertungen

- Chap 4 Storage Devices - 9thDokument11 SeitenChap 4 Storage Devices - 9thZubair FaiziNoch keine Bewertungen

- Selection - Memory - DR Monika - 22.03.23Dokument8 SeitenSelection - Memory - DR Monika - 22.03.23Prof.Monika JainNoch keine Bewertungen

- Memory: Mohana S.H, Usmrfg College, Kuvempu UniversityDokument6 SeitenMemory: Mohana S.H, Usmrfg College, Kuvempu UniversityMohana KurubaNoch keine Bewertungen

- Plastic MemoryDokument14 SeitenPlastic Memorymanzar2004Noch keine Bewertungen

- Assignment: Embedded SystemsDokument6 SeitenAssignment: Embedded SystemsSudarshanNoch keine Bewertungen

- Dynamic Random Access MemoryDokument20 SeitenDynamic Random Access MemoryNahum QuirosNoch keine Bewertungen

- Embedded Flash Memory GuideDokument12 SeitenEmbedded Flash Memory GuidebharathiNoch keine Bewertungen

- FRAM - Semiconductor Memory TypesDokument5 SeitenFRAM - Semiconductor Memory TypesMehmet KırgözoğluNoch keine Bewertungen

- INTERNAL MEMORY Ram/romDokument10 SeitenINTERNAL MEMORY Ram/romRon NokwareNoch keine Bewertungen

- MemoryDokument7 SeitenMemoryHelner TaghapNoch keine Bewertungen

- T.Y. E.I. /2 / 1 Memories N.KapoorDokument5 SeitenT.Y. E.I. /2 / 1 Memories N.KapoorNeelam KapoorNoch keine Bewertungen

- Memory and I/O Interfacing Memory: AccessibilityDokument52 SeitenMemory and I/O Interfacing Memory: Accessibilitykarthick77Noch keine Bewertungen

- Here Is An Example of A Machine With 1GB of RAMDokument6 SeitenHere Is An Example of A Machine With 1GB of RAMaguslizarNoch keine Bewertungen

- Unit - III Concept of Memory PDFDokument13 SeitenUnit - III Concept of Memory PDFxsaaNoch keine Bewertungen

- Semiconductor MemoriesDokument63 SeitenSemiconductor MemoriesNayanjyot SinghNoch keine Bewertungen

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Von EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Noch keine Bewertungen

- Hardware and Networking Service Level - Ii Based On March 2022, Curriculum Version 1Dokument65 SeitenHardware and Networking Service Level - Ii Based On March 2022, Curriculum Version 1girmaw simachew100% (1)

- Importance of RAM in A ComputerDokument7 SeitenImportance of RAM in A Computerzansue abutamNoch keine Bewertungen

- P5kpl-Am - Memory QVLDokument7 SeitenP5kpl-Am - Memory QVLjohntotetwooNoch keine Bewertungen

- System Error GuideDokument10 SeitenSystem Error GuideJUAN CARLOS ZUÑIGA TIMANANoch keine Bewertungen

- Altium Designer Winter 09 Technical ReviewDokument49 SeitenAltium Designer Winter 09 Technical Reviewbeg49Noch keine Bewertungen

- CompTIA A+ incorrect answers on RAM typesDokument2 SeitenCompTIA A+ incorrect answers on RAM typesEd St JamesNoch keine Bewertungen

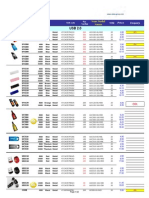

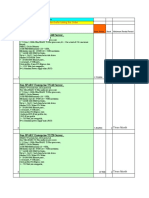

- V-GeN Flash Memory Price List Semarang ContactDokument7 SeitenV-GeN Flash Memory Price List Semarang ContactEko HaryantoNoch keine Bewertungen

- Cost To Cost: Mercury H55 + I-3 Cpu RS 6380 Dual Core 149/-Core To DUO 399Dokument7 SeitenCost To Cost: Mercury H55 + I-3 Cpu RS 6380 Dual Core 149/-Core To DUO 399RaghuNoch keine Bewertungen

- How To Use DDR2 RAM PDFDokument40 SeitenHow To Use DDR2 RAM PDFSharadNoch keine Bewertungen

- DDR SDRAM GuideDokument8 SeitenDDR SDRAM GuideToma95Noch keine Bewertungen

- Intel 955X Express Chipset: DatasheetDokument236 SeitenIntel 955X Express Chipset: DatasheetpotatoNoch keine Bewertungen

- ITP421 WEEK 3 - Random Access MemoryDokument27 SeitenITP421 WEEK 3 - Random Access MemoryJaira Mae DiazNoch keine Bewertungen

- Potomac 10SG MP BUILD 2008 0123Dokument64 SeitenPotomac 10SG MP BUILD 2008 0123Gleison GomesNoch keine Bewertungen

- Quarter 2 - Module 1: Performing Mensuration and CalculationDokument21 SeitenQuarter 2 - Module 1: Performing Mensuration and CalculationMinnie Roselle GoNoch keine Bewertungen

- ADATA Price ListDokument32 SeitenADATA Price ListPlano B SumhillNoch keine Bewertungen

- PCD Lab Manual VtuDokument92 SeitenPCD Lab Manual VtusankrajegowdaNoch keine Bewertungen

- Manual de La MotherBoard Porras Jose (G31TM-P21 - G31TM-P25 - G31TM-P31 - G31TM-P35) 100x150Dokument26 SeitenManual de La MotherBoard Porras Jose (G31TM-P21 - G31TM-P25 - G31TM-P31 - G31TM-P35) 100x150Camilo Andres100% (1)

- 3236Dokument40 Seiten3236Adela100% (2)

- VFTF09 An108Dokument53 SeitenVFTF09 An108Deepak KurupNoch keine Bewertungen

- End User ATeX 12.09.2006Dokument84 SeitenEnd User ATeX 12.09.2006Alexander BlackNoch keine Bewertungen

- DDR3 Derating Guide: Setup & Hold Timing DerivationDokument40 SeitenDDR3 Derating Guide: Setup & Hold Timing DerivationAkhila PurushothamanNoch keine Bewertungen

- s3c2450 Datasheet 200901Dokument2 Seitens3c2450 Datasheet 200901jerometim33Noch keine Bewertungen

- System X3200 M2 SpecificationsDokument24 SeitenSystem X3200 M2 SpecificationsJulio César Villa MoreiraNoch keine Bewertungen

- MB Manual Ga-ep45-Ud3p (Ud3r) (Ud3) 1.6 eDokument128 SeitenMB Manual Ga-ep45-Ud3p (Ud3r) (Ud3) 1.6 eHyder BasetNoch keine Bewertungen

- Navigator Rental Server Stock - April 2010Dokument30 SeitenNavigator Rental Server Stock - April 2010Satish KumarNoch keine Bewertungen

- AMD Opteron™Processor Product Data Sheet: 940-Pin Package Specific FeaturesDokument4 SeitenAMD Opteron™Processor Product Data Sheet: 940-Pin Package Specific FeaturesVenkat Kiran SribhashyamNoch keine Bewertungen

- Placa de Baza DG33FBDokument88 SeitenPlaca de Baza DG33FBPopStudio FotoNoch keine Bewertungen

- DDR3 VsDokument3 SeitenDDR3 VsMichael NavarroNoch keine Bewertungen