Beruflich Dokumente

Kultur Dokumente

Pipelining Vector Processing

Hochgeladen von

MRMAKBAROriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Pipelining Vector Processing

Hochgeladen von

MRMAKBARCopyright:

Verfügbare Formate

Pipelining and Vector Processing 1

PIPELINING AND VECTOR PROCESSING

• Parallel Processing

• Pipelining

• Arithmetic Pipeline

• Instruction Pipeline

• RISC Pipeline

• Vector Processing

• Array Processors

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 2 Parallel Processing

PARALLEL PROCESSING

Execution of Concurrent Events in the computing

process to achieve faster Computational Speed

Levels of Parallel Processing

- Job or Program level

- Task or Procedure level

- Inter-Instruction level

- Intra-Instruction level

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 3 Parallel Processing

PARALLEL COMPUTERS

Architectural Classification

– Flynn's classification

» Based on the multiplicity of Instruction Streams and

Data Streams

» Instruction Stream

• Sequence of Instructions read from memory

» Data Stream

• Operations performed on the data in the processor

Number of Data Streams

Single Multiple

Number of Single SISD SIMD

Instruction

Streams Multiple MISD MIMD

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 4 Parallel Processing

COMPUTER ARCHITECTURES FOR PARALLEL

PROCESSING

Von-Neuman SISD Superscalar processors

based

Superpipelined processors

VLIW

MISD Nonexistence

SIMD Array processors

Systolic arrays

Dataflow

Associative processors

MIMD Shared-memory multiprocessors

Reduction

Bus based

Crossbar switch based

Multistage IN based

Message-passing multicomputers

Hypercube

Mesh

Reconfigurable

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 5 Parallel Processing

SISD COMPUTER SYSTEMS

Control Processor Data stream Memory

Unit Unit

Instruction stream

Characteristics

- Standard von Neumann machine

- Instructions and data are stored in memory

- One operation at a time

Limitations

Von Neumann bottleneck

Maximum speed of the system is limited by the

Memory Bandwidth (bits/sec or bytes/sec)

- Limitation on Memory Bandwidth

- Memory is shared by CPU and I/O

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 6 Parallel Processing

SISD PERFORMANCE IMPROVEMENTS

• Multiprogramming

• Spooling

• Multifunction processor

• Pipelining

• Exploiting instruction-level parallelism

- Superscalar

- Superpipelining

- VLIW (Very Long Instruction Word)

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 7 Parallel Processing

MISD COMPUTER SYSTEMS

M CU P

M CU P Memory

• •

• •

• •

M CU P Data stream

Instruction stream

Characteristics

- There is no computer at present that can be

classified as MISD

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 8 Parallel Processing

SIMD COMPUTER SYSTEMS

Memory

Data bus

Control Unit

Instruction stream

P P ••• P Processor units

Data stream

Alignment network

M M ••• M Memory modules

Characteristics

- Only one copy of the program exists

- A single controller executes one instruction at a time

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 9 Parallel Processing

MIMD COMPUTER SYSTEMS

P M P M ••• P M

Interconnection Network

Shared Memory

Characteristics

- Multiple processing units

- Execution of multiple instructions on multiple data

Types of MIMD computer systems

- Shared memory multiprocessors

- Message-passing multicomputers

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 10 Pipelining

PIPELINING

A technique of decomposing a sequential process

into suboperations, with each subprocess being

executed in a partial dedicated segment that

operates concurrently with all other segments.

Ai * Bi + Ci for i = 1, 2, 3, ... , 7

Ai Bi Memory Ci

Segment 1

R1 R2

Multiplier

Segment 2

R3 R4

Adder

Segment 3

R5

R1 Ai, R2 Bi Load Ai and Bi

R3 R1 * R2, R4 Ci Multiply and load Ci

R5 R3 + R4 Add

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 11 Pipelining

OPERATIONS IN EACH PIPELINE STAGE

Clock Segment 1 Segment 2 Segment 3

Pulse

Number R1 R2 R3 R4 R5

1 A1 B1

2 A2 B2 A1 * B1 C1

3 A3 B3 A2 * B2 C2 A1 * B1 + C1

4 A4 B4 A3 * B3 C3 A2 * B2 + C2

5 A5 B5 A4 * B4 C4 A3 * B3 + C3

6 A6 B6 A5 * B5 C5 A4 * B4 + C4

7 A7 B7 A6 * B6 C6 A5 * B5 + C5

8 A7 * B7 C7 A6 * B6 + C6

9 A7 * B7 + C7

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 12 Pipelining

GENERAL PIPELINE

General Structure of a 4-Segment Pipeline

Clock

Input S1 R1 S2 R2 S3 R3 S4 R4

Space-Time Diagram

1 2 3 4 5 6 7 8 9 Clock cycles

Segment 1 T1 T2 T3 T4 T5 T6

2 T1 T2 T3 T4 T5 T6

3 T1 T2 T3 T4 T5 T6

4 T1 T2 T3 T4 T5 T6

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 13 Pipelining

PIPELINE SPEEDUP

n: Number of tasks to be performed

Conventional Machine (Non-Pipelined)

tn: Clock cycle

t1: Time required to complete the n tasks

t 1 = n * tn

Pipelined Machine (k stages)

tp: Clock cycle (time to complete each suboperation)

tk: Time required to complete the n tasks

tk = (k + n - 1) * tp

Speedup

Sk: Speedup

Sk = n*tn / (k + n - 1)*tp

tn

lim Sk =

n tp

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 14 Pipelining

PIPELINE AND MULTIPLE FUNCTION UNITS

Example

- 4-stage pipeline

- subopertion in each stage; tp = 20nS

- 100 tasks to be executed

- 1 task in non-pipelined system; 20*4 = 80nS

Pipelined System

(k + n - 1)*tp = (4 + 99) * 20 = 2060nS

Non-Pipelined System

n*k*tp = 100 * 80 = 8000nS

Speedup

Sk = 8000 / 2060 = 3.88

4-Stage Pipeline is basically identical to the system

with 4 identical function units Ii I i+1 I i+2 I i+3

Multiple Functional Units P1 P2 P3 P4

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 15 Arithmetic Pipeline

ARITHMETIC PIPELINE

Floating-point adder Exponents

a b

Mantissas

A B

X = A x 2a

Y = B x 2b R R

[1] Compare the exponents Compare Difference

Segment 1: exponents

[2] Align the mantissa by subtraction

[3] Add/sub the mantissa

[4] Normalize the result

R

Segment 2: Choose exponent Align mantissa

Segment 3: Add or subtract

mantissas

R R

Segment 4: Adjust Normalize

exponent result

R R

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 16 Instruction Pipeline

INSTRUCTION CYCLE

Six Phases* in an Instruction Cycle

[1] Fetch an instruction from memory

[2] Decode the instruction

[3] Calculate the effective address of the operand

[4] Fetch the operands from memory

[5] Execute the operation

[6] Store the result in the proper place

* Some instructions skip some phases

* Effective address calculation can be done in

the part of the decoding phase

* Storage of the operation result into a register

is done automatically in the execution phase

==> 4-Stage Pipeline

[1] FI: Fetch an instruction from memory

[2] DA: Decode the instruction and calculate

the effective address of the operand

[3] FO: Fetch the operand

[4] EX: Execute the operation

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 17 Instruction Pipeline

INSTRUCTION PIPELINE

Execution of Three Instructions in a 4-Stage Pipeline

Conventional

i FI DA FO EX

i+1 FI DA FO EX

i+2 FI DA FO EX

Pipelined

i FI DA FO EX

i+1 FI DA FO EX

i+2 FI DA FO EX

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 18 Instruction Pipeline

INSTRUCTION EXECUTION IN A 4-STAGE PIPELINE

Segment1: Fetch instruction

from memory

Decode instruction

Segment2: and calculate

effective address

Branch?

yes

no

Fetch operand

Segment3: from memory

Segment4: Execute instruction

Interrupt yes

Interrupt?

handling

no

Update PC

Empty pipe

Step: 1 2 3 4 5 6 7 8 9 10 11 12 13

Instruction 1 FI DA FO EX

2 FI DA FO EX

(Branch) 3 FI DA FO EX

4 FI FI DA FO EX

5 FI DA FO EX

6 FI DA FO EX

7 FI DA FO EX

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 19 Instruction Pipeline

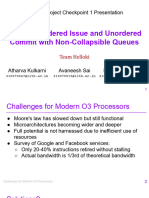

MAJOR HAZARDS IN PIPELINED EXECUTION

Structural hazards(Resource Conflicts)

Hardware Resources required by the instructions in

simultaneous overlapped execution cannot be met

Data hazards (Data Dependency Conflicts)

An instruction scheduled to be executed in the pipeline requires the

result of a previous instruction, which is not yet available

R1 <- B + C ADD DA B,C + Data dependency

R1 <- R1 + 1

INC DA bubble R1 +1

Control hazards

Branches and other instructions that change the PC

make the fetch of the next instruction to be delayed

JMP ID PC + PC Branch address dependency

bubble IF ID OF OE OS

Hazards in pipelines may make it Pipeline Interlock:

necessary to stall the pipeline Detect Hazards Stall until it is cleared

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 20 RISC Pipeline

RISC PIPELINE

RISC

- Machine with a very fast clock cycle that

executes at the rate of one instruction per cycle

<- Simple Instruction Set

Fixed Length Instruction Format

Register-to-Register Operations

Instruction Cycles of Three-Stage Instruction Pipeline

Data Manipulation Instructions

I: Instruction Fetch

A: Decode, Read Registers, ALU Operations

E: Write a Register

Load and Store Instructions

I: Instruction Fetch

A: Decode, Evaluate Effective Address

E: Register-to-Memory or Memory-to-Register

Program Control Instructions

I: Instruction Fetch

A: Decode, Evaluate Branch Address

E: Write Register(PC)

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 21 RISC Pipeline

DELAYED LOAD

LOAD: R1 M[address 1]

LOAD: R2 M[address 2]

ADD: R3 R1 + R2

STORE: M[address 3] R3

Three-segment pipeline timing

Pipeline timing with data conflict

clock cycle 1 2 3 4 5 6

Load R1 I A E

Load R2 I A E

Add R1+R2 I A E

Store R3 I A E

Pipeline timing with delayed load

clock cycle 1 2 3 4 5 6 7

Load R1 I A E

The data dependency is taken

Load R2 I A E care by the compiler rather

NOP I A E than the hardware

Add R1+R2 I A E

Store R3 I A E

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 22 RISC Pipeline

DELAYED BRANCH

Compiler analyzes the instructions before and after

the branch and rearranges the program sequence by

inserting useful instructions in the delay steps

Using no-operation instructions

Clock cycles: 1 2 3 4 5 6 7 8 9 10

1. Load I A E

2. Increment I A E

3. Add I A E

4. Subtract I A E

5. Branch to X I A E

6. NOP I A E

7. NOP I A E

8. Instr. in X I A E

Rearranging the instructions

Clock cycles: 1 2 3 4 5 6 7 8

1. Load I A E

2. Increment I A E

3. Branch to X I A E

4. Add I A E

5. Subtract I A E

6. Instr. in X I A E

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 23 Vector Processing

VECTOR PROCESSING

Vector Processing Applications

• Problems that can be efficiently formulated in terms of vectors

– Long-range weather forecasting

– Petroleum explorations

– Seismic data analysis

– Medical diagnosis

– Aerodynamics and space flight simulations

– Artificial intelligence and expert systems

– Mapping the human genome

– Image processing

Vector Processor (computer)

Ability to process vectors, and related data structures such as matrices

and multi-dimensional arrays, much faster than conventional computers

Vector Processors may also be pipelined

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 24 Vector Processing

VECTOR PROGRAMMING

DO 20 I = 1, 100

20 C(I) = B(I) + A(I)

Conventional computer

Initialize I = 0

20 Read A(I)

Read B(I)

Store C(I) = A(I) + B(I)

Increment I = i + 1

If I 100 goto 20

Vector computer

C(1:100) = A(1:100) + B(1:100)

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 25 Vector Processing

VECTOR INSTRUCTIONS

f1: V * V

f2: V * S V: Vector operand

f3: V x V * V S: Scalar operand

f4: V x S * V

Type Mnemonic Description (I = 1, ..., n)

f1 VSQR Vector square root B(I) * SQR(A(I))

VSIN Vector sine B(I) * sin(A(I))

VCOM Vector complement A(I) * A(I)

f2 VSUM Vector summation S * S A(I)

VMAX Vector maximum S * max{A(I)}

f3 VADD Vector add C(I) * A(I) + B(I)

VMPY Vector multiply C(I) * A(I) * B(I)

VAND Vector AND C(I) * A(I) . B(I)

VLAR Vector larger C(I) * max(A(I),B(I))

VTGE Vector test > C(I) * 0 if A(I) < B(I)

C(I) * 1 if A(I) > B(I)

f4 SADD Vector-scalar add B(I) * S + A(I)

SDIV Vector-scalar divide B(I) * A(I) / S

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 26 Vector Processing

VECTOR INSTRUCTION FORMAT

Vector Instruction Format

Operation Base address Base address Base address Vector

code source 1 source 2 destination length

Pipeline for Inner Product

Source

A

Source Multiplier Adder

B pipeline pipeline

Computer Organization Computer Architectures Lab

Pipelining and Vector Processing 27 Vector Processing

MULTIPLE MEMORY MODULE AND INTERLEAVING

Multiple Module Memory

Address bus

M0 M1 M2 M3

AR AR AR AR

Memory Memory Memory Memory

array array array array

DR DR DR DR

Data bus

Address Interleaving

Different sets of addresses are assigned to

different memory modules

Computer Organization Computer Architectures Lab

Das könnte Ihnen auch gefallen

- Pipelining and Vector Processing Chapter 9Dokument29 SeitenPipelining and Vector Processing Chapter 9mansi100% (6)

- Pipelining and Vector ProcessingDokument39 SeitenPipelining and Vector Processinghùng nguyễnNoch keine Bewertungen

- Pipeline and Vector ProcessingDokument37 SeitenPipeline and Vector ProcessingGiri Saranu83% (12)

- Pipelining and Vector ProcessingDokument37 SeitenPipelining and Vector ProcessingSautrik C. JoardarNoch keine Bewertungen

- Pipelining and Vector ProcessingDokument37 SeitenPipelining and Vector ProcessingGAURISH GARGNoch keine Bewertungen

- Pipelining and Vector Processing-1-30Dokument30 SeitenPipelining and Vector Processing-1-30Laxman VelloreNoch keine Bewertungen

- Chapter 3 - Pipelining-And-Vector-ProcessingDokument29 SeitenChapter 3 - Pipelining-And-Vector-ProcessingtkavithaNoch keine Bewertungen

- Co Unit3Dokument41 SeitenCo Unit3Nand kotNoch keine Bewertungen

- Parallal Architecture SDokument17 SeitenParallal Architecture Selsa annaNoch keine Bewertungen

- Lecture 8 Unit 4 Pipeline and Vector Processing 2019Dokument36 SeitenLecture 8 Unit 4 Pipeline and Vector Processing 2019Ashutosh DasNoch keine Bewertungen

- Pipeline and VectorDokument29 SeitenPipeline and VectorGâgäñ LøhîăNoch keine Bewertungen

- 04 HardwareDokument109 Seiten04 Hardwaresmitaasalunkhe1999Noch keine Bewertungen

- Parallel Computer Architecture ClassificationDokument23 SeitenParallel Computer Architecture ClassificationDenisNoch keine Bewertungen

- Computer ArchitectureDokument667 SeitenComputer Architecturevishalchaurasiya360001Noch keine Bewertungen

- CH03Dokument26 SeitenCH03mehreenNoch keine Bewertungen

- Modern Computer Architecture: Lecture1 Fundamentals of Quantitative Design and Analysis (I)Dokument41 SeitenModern Computer Architecture: Lecture1 Fundamentals of Quantitative Design and Analysis (I)mustafascrNoch keine Bewertungen

- Multi ThreadingDokument168 SeitenMulti ThreadingSandeep AlajangiNoch keine Bewertungen

- Multi ThreadingDokument168 SeitenMulti ThreadingSumanth GangappaNoch keine Bewertungen

- SHARE Pittsburgh IIB Internals of IBM Integration BusDokument79 SeitenSHARE Pittsburgh IIB Internals of IBM Integration BusjimenavNoch keine Bewertungen

- ComputerOrganization BasicDokument54 SeitenComputerOrganization BasickaneeshaNoch keine Bewertungen

- IIB - Internals of IBM Integration Bus PDFDokument34 SeitenIIB - Internals of IBM Integration Bus PDFPurushothamNoch keine Bewertungen

- CIS775: Computer Architecture: Chapter 1: Fundamentals of Computer DesignDokument43 SeitenCIS775: Computer Architecture: Chapter 1: Fundamentals of Computer DesignSwapnil Sunil ShendageNoch keine Bewertungen

- Introduction To Parallel Processing: Asim MunirDokument19 SeitenIntroduction To Parallel Processing: Asim Muniribrar7876Noch keine Bewertungen

- Computer System Architecture Morris ManoDokument261 SeitenComputer System Architecture Morris ManogirdharktrNoch keine Bewertungen

- Gpu Applications CatalogDokument72 SeitenGpu Applications CatalogNikola DjurovicNoch keine Bewertungen

- Cloud Computing Unit I Ch.2 2021Dokument21 SeitenCloud Computing Unit I Ch.2 2021Lipun SwainNoch keine Bewertungen

- Network SDN in Health Kahlert v0.4Dokument30 SeitenNetwork SDN in Health Kahlert v0.4anum asadNoch keine Bewertungen

- Computer ArchitectureDokument8 SeitenComputer ArchitecturePrafull ChikkamathNoch keine Bewertungen

- Computer Organization and ArchitechtureDokument321 SeitenComputer Organization and ArchitechtureSanjanaNoch keine Bewertungen

- Instruction Format PDFDokument5 SeitenInstruction Format PDFG.SAIDULUNoch keine Bewertungen

- Advanced Computer Architecture: Presented By, KrishnaDokument35 SeitenAdvanced Computer Architecture: Presented By, KrishnaLekshmiNoch keine Bewertungen

- cs668 Lec1 ParallelArchDokument18 Seitencs668 Lec1 ParallelArchIshAureaNoch keine Bewertungen

- Introduction Mod1Dokument120 SeitenIntroduction Mod1SHEENA YNoch keine Bewertungen

- Mano Computer System Architecture AllDokument261 SeitenMano Computer System Architecture Allsuperstar53878% (9)

- cs501 Archintro Pin2Dokument44 Seitencs501 Archintro Pin2Mohammadihsan NoorNoch keine Bewertungen

- Parralel PerformanceMeasurementDokument23 SeitenParralel PerformanceMeasurementDebashis DasNoch keine Bewertungen

- Chapter 8Dokument59 SeitenChapter 8K S Sanath KashyapNoch keine Bewertungen

- Microprogramming PDFDokument5 SeitenMicroprogramming PDFSunanda ThompsonNoch keine Bewertungen

- Computer System Architecture - Morris ManoDokument261 SeitenComputer System Architecture - Morris ManoHarshit RautNoch keine Bewertungen

- Pipelining and Vector ProcessingDokument37 SeitenPipelining and Vector ProcessingJohn DavidNoch keine Bewertungen

- 02 Cloud Computing - PrintDokument14 Seiten02 Cloud Computing - PrintNeeraj GargNoch keine Bewertungen

- Unit 4 MPMCDokument22 SeitenUnit 4 MPMCSekhar ReddyNoch keine Bewertungen

- Computer System Architecture - Morris Mano (1) - Pfu79k3tv14e238u9o4r794Dokument517 SeitenComputer System Architecture - Morris Mano (1) - Pfu79k3tv14e238u9o4r794Trending this yearNoch keine Bewertungen

- System and Network Administration Introduction & OverviewDokument40 SeitenSystem and Network Administration Introduction & OverviewArsalan JahaniNoch keine Bewertungen

- Advanced Computer Architecture: Sisir Kumar Jena Asst. Professor DIT UniversityDokument20 SeitenAdvanced Computer Architecture: Sisir Kumar Jena Asst. Professor DIT UniversitySisir Kumar JenaNoch keine Bewertungen

- 1 - Concurrent ProgrammingDokument28 Seiten1 - Concurrent ProgrammingBunny HoneyNoch keine Bewertungen

- 20201221-Complete Notes MCADokument96 Seiten20201221-Complete Notes MCADanish UllahNoch keine Bewertungen

- Short Course On Phase-Locked Loops and Their Applications Day 3, PM Lecture Behavioral Simulation ExercisesDokument16 SeitenShort Course On Phase-Locked Loops and Their Applications Day 3, PM Lecture Behavioral Simulation ExercisesAndrea FasatoNoch keine Bewertungen

- FlynnsDokument41 SeitenFlynnsAnonymous FPMwLUw8cNoch keine Bewertungen

- Processors and Programmable Logic: Khaled Grati Grati - Khaled@Supcom - TN 2020-2021Dokument18 SeitenProcessors and Programmable Logic: Khaled Grati Grati - Khaled@Supcom - TN 2020-2021ibrahimNoch keine Bewertungen

- Session Title: Bob Johnston / IPS Grid & HA SolutionsDokument31 SeitenSession Title: Bob Johnston / IPS Grid & HA Solutionsnirmal_itNoch keine Bewertungen

- Advanced Computer Architecture: Section 1 Parallel Computer ModelsDokument56 SeitenAdvanced Computer Architecture: Section 1 Parallel Computer ModelsSuhail AhmadNoch keine Bewertungen

- Chapter 1: Operating System FundamentalsDokument7 SeitenChapter 1: Operating System Fundamentalsnanad_hNoch keine Bewertungen

- William Stallings Computer Organization and Architecture 7 EditionDokument41 SeitenWilliam Stallings Computer Organization and Architecture 7 EditionINDIAN SQUATCHERNoch keine Bewertungen

- Lect2 ClassificationDokument23 SeitenLect2 ClassificationPetru TopalaNoch keine Bewertungen

- Mscs6060 Parallel and Distributed SystemsDokument50 SeitenMscs6060 Parallel and Distributed SystemsSadia MughalNoch keine Bewertungen

- CAD Systems in Mechanical and Production EngineeringVon EverandCAD Systems in Mechanical and Production EngineeringBewertung: 4.5 von 5 Sternen4.5/5 (3)

- B. A. Catlos, Muslims of Medieval Latin ChristendomDokument649 SeitenB. A. Catlos, Muslims of Medieval Latin ChristendomJose Daniel MontoyaNoch keine Bewertungen

- Pier ColumnDokument156 SeitenPier ColumnMRMAKBARNoch keine Bewertungen

- The Complete Sherlock Homes PDFDokument985 SeitenThe Complete Sherlock Homes PDFMRMAKBARNoch keine Bewertungen

- 'Temporary Structures' FormworkDokument11 Seiten'Temporary Structures' FormworkMRMAKBAR100% (1)

- Scaffolding CatalogueDokument10 SeitenScaffolding CatalogueMRMAKBARNoch keine Bewertungen

- COA Quetion Bank (Pyq) PDFDokument18 SeitenCOA Quetion Bank (Pyq) PDFp4006878Noch keine Bewertungen

- Multiple Choice Questions For Computer OperatorDokument5 SeitenMultiple Choice Questions For Computer OperatorRikesh DewanganNoch keine Bewertungen

- CP0675 03-May-2012 RM02Dokument35 SeitenCP0675 03-May-2012 RM02Sagar ThakrarNoch keine Bewertungen

- Isca TSPDokument14 SeitenIsca TSPupdatesmockbankNoch keine Bewertungen

- Unit4 COADokument71 SeitenUnit4 COAmayankrajput13626Noch keine Bewertungen

- Basic Computer Organization and DesignDokument35 SeitenBasic Computer Organization and Designabhisrit2008Noch keine Bewertungen

- Multivector&SIMD Computers Ch8Dokument12 SeitenMultivector&SIMD Computers Ch8Charu DhingraNoch keine Bewertungen

- Coa MCQ PDFDokument47 SeitenCoa MCQ PDFKeerthika100% (1)

- Introduction To Intel Architecture - The BasicsDokument25 SeitenIntroduction To Intel Architecture - The BasicsShiv Shakti BankaNoch keine Bewertungen

- CS683 Project Presentation (Helloki)Dokument33 SeitenCS683 Project Presentation (Helloki)Avaneesh S.SubramanyamNoch keine Bewertungen

- Chapter 2 Ed2Dokument47 SeitenChapter 2 Ed2Muhammad AqeefNoch keine Bewertungen

- Chapter One - Introduction To Assembly Programming NoteDokument33 SeitenChapter One - Introduction To Assembly Programming NoteMunir AliNoch keine Bewertungen

- COA - Chapter # 1Dokument21 SeitenCOA - Chapter # 1Set EmpNoch keine Bewertungen

- ECE 445 - Fall 2020 - Lecture 3 - MIPS ISA and Assembly LanguageDokument31 SeitenECE 445 - Fall 2020 - Lecture 3 - MIPS ISA and Assembly Language陳柏鈞Noch keine Bewertungen

- COSC 2406 Outline 2023FDokument4 SeitenCOSC 2406 Outline 2023Fcricket1223Noch keine Bewertungen

- Sem 3Dokument15 SeitenSem 3arpita sarkarNoch keine Bewertungen

- 01 IntroductionDokument36 Seiten01 IntroductionAlauddin KhanNoch keine Bewertungen

- EECS 373: Design of Microprocessor-Based SystemsDokument29 SeitenEECS 373: Design of Microprocessor-Based Systemsavinash_yuvarajNoch keine Bewertungen

- Basic Computer Organization and DesignDokument20 SeitenBasic Computer Organization and DesignMag Creation100% (1)

- Microprocessor Systems and Interfacing (EEE342)Dokument21 SeitenMicroprocessor Systems and Interfacing (EEE342)Sohaib ZaidiNoch keine Bewertungen

- BCA 6th SemDokument29 SeitenBCA 6th Sem9016msNoch keine Bewertungen

- 4th Sem Syllabus - GITAM UNIVERSITYDokument9 Seiten4th Sem Syllabus - GITAM UNIVERSITYVenkatesh RamojuNoch keine Bewertungen

- Computer Organization and Architecture TutorialDokument7 SeitenComputer Organization and Architecture Tutorialpritvekariya222Noch keine Bewertungen

- Performance Analysis of Dual Core, Core 2 Duo and Core I3 Intel ProcessorDokument7 SeitenPerformance Analysis of Dual Core, Core 2 Duo and Core I3 Intel ProcessorPRAFULKUMAR PARMARNoch keine Bewertungen

- RISC Processor DesignDokument33 SeitenRISC Processor Designkomal iqbalNoch keine Bewertungen

- Intel Processor Architecture-CoreDokument155 SeitenIntel Processor Architecture-Corejinish.K.GNoch keine Bewertungen

- Reserved: Basic Structure of Computers and Instruction SetDokument20 SeitenReserved: Basic Structure of Computers and Instruction SetJuanNoch keine Bewertungen

- MCA Syllabus - 1st Sem PDFDokument32 SeitenMCA Syllabus - 1st Sem PDFshatabdi mukherjeeNoch keine Bewertungen

- Important-University Questions Unit-WiseDokument7 SeitenImportant-University Questions Unit-Wisejitesh100% (1)

- 702-Umm-E-Rubab-Assignment-Mid Assignment-F1Dokument19 Seiten702-Umm-E-Rubab-Assignment-Mid Assignment-F1Akru JuttNoch keine Bewertungen