Beruflich Dokumente

Kultur Dokumente

A3916 Datasheet

Hochgeladen von

Asep HermansyahOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

A3916 Datasheet

Hochgeladen von

Asep HermansyahCopyright:

Verfügbare Formate

A3916

Dual DMOS Full-Bridge Motor Driver

FEATURES AND BENEFITS DESCRIPTION

• Wide, 2.7 to 15 V input voltage operating range Designed for pulse-width-modulated (PWM) control of low-

• Dual DMOS full-bridges: drive two DC motors or voltage stepper motors and single and dual DC motors, the

one stepper motor A3916 is capable of output currents up to 1 A per channel and

• Low RDS(ON) outputs operating voltages from 2.7 to 15 V.

• Synchronous rectification for reduced power dissipation

The A3916 has an internal fixed off-time PWM timer that sets

• Low-current sleep mode

a peak current based on the selection of a current sense resistor.

• Overcurrent protection

An output fault flag is provided that notifies the user of a TSD

• Internal UVLO and thermal shutdown circuitry

or overcurrent protection event.

• Integrated charge pump

• Pin-to-pin compatible with A3906 The A3916 is supplied in a low-profile 3 × 3 mm 16-terminal

QFN (suffix “ES”) and a low-profile 4 × 4 mm 20-terminal

QFN (suffixes “ES, -1”) both with exposed power tabs for

PACKAGEs:

enhanced thermal dissipation.

16-contact QFN

3 mm × 3 mm

(suffix ES)

20-contact QFN

4 mm × 4 mm

(suffix ES,-1)

Not to scale

VCP VCP

0.1 µF 0.1 µF

2.7 to 15 V 2.7 to 15 V

VBB VBB

SLEEPn SLEEPn

IN1

A3916 IN1 A3916

IN2 OUT1A IN2 OUT1A

CLK

IN3 CLK

IN3

IN4 OUT1B IN4 OUT1B

DC

Motor Step

SENSE1

Motor

FAULTn FAULTn

SENSE1

OUT2A

OUT2A

OUT2B

OUT2B

DC

Motor GND

SENSE2 SENSE2

GND

Figure 1: Typical Applications

A3916-DS, Rev. 3 January 19, 2018

MCO-0000139

A3916 Dual DMOS Full-Bridge Motor Driver

SPECIFICATIONS

Selection Guide

Part Number Packaging Packing

A3916GESTR-T 3 × 3 mm 16-contact QFN package 1500 pieces per 7-inch reel

A3916GESTR-T-1 4 × 4 mm 20-contact QFN package 1500 pieces per 7-inch reel

Absolute Maximum Ratings

Characteristic Symbol Notes Rating Unit

Supply Voltage VBB 15 V

Output Current IOUT Continuous 1.0 A

Output Current (parallel mode) IOUT(PAR) Continuous 1.8 A

Continuous 0.5 V

Sense Voltage VSENSEx

Pulsed, tw < 1 µs 2.5 V

Logic Input Voltage Range VIO –0.3 to 5.5 V

Junction Temperature TJ(MAX) 150 °C

Storage Temperature Range Tstg –55 to 150 °C

Operating Temperature Range TA Range G –40 to 105 °C

Thermal Characteristics: May require derating at maximum conditions; see application information

Characteristic Symbol Test Conditions* Value Unit

3 × 3 mm ES package 4-layer PCB based on JEDEC standard 47 °C/W

RθJA

4 × 4 mm ES-1 package 4-layer PCB based on JEDEC standard 37 °C/W

*Additional thermal information available on the Allegro website.

Allegro MicroSystems, LLC 2

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

A3916 Dual DMOS Full-Bridge Motor Driver

Pinout Diagrams and TErminal List Table

16 OUT1A

SENSE1

17 VCP

OUT1A

20 NC

19 NC

18 NC

VCP

NC

16

15

14

13

NC 1 15 SENSE1

GND 1 12 OUT1B

GND 2 14 OUT1B

SLEEPn 2 11 VBB

PAD SLEEPn 3 PAD 13 VBB

IN1 3 10 OUT2B

IN1 4 12 OUT2B

IN2 4 9 SENSE2

IN2 5 11 SENSE2

5

6

7

8

OUT2A 10

OUT2A

IN3

IN4

FAULTn

6

7

8

9

IN3

IN4

FAULTn

NC

16-Contact QFN (ES) Package 20-Contact QFN (ES, -1) Package

Terminal List Table

Number

Name Function

ES ES, -1

1 2 GND Ground

2 3 SLEEPn Active-Low Sleep Input

3 4 IN1 Control Input

4 5 IN2 Control Input

5 6 IN3 Control Input

6 7 IN4 Control Input

7 8 FAULTn Open-Drain Logic Output

8 10 OUT2A DMOS H-Bridge 2, Output A

9 11 SENSE2 Sense Resistor Terminal, Bridge 2

10 12 OUT2B DMOS H-Bridge 2, Output B

11 13 VBB Motor Supply Voltage

12 14 OUT1B DMOS H-Bridge 1, Output B

13 15 SENSE1 Sense Resistor Terminal, Bridge 1

14 16 OUT1A DMOS H-Bridge 1, Output A

15 17 VCP Charge Pump Capacitor

16 1,9,18,19,20 NC No Internal Connection

– – PAD Exposed Pad for Enhanced Thermal Performance

Allegro MicroSystems, LLC 3

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

A3916 Dual DMOS Full-Bridge Motor Driver

Functional Block Diagram

TSD

CHARGE PUMP VCP

VBB 0.1 µF

2.7 to 15 V

UVLO VREG

VBB

VBB

DMOS H BRIDGE

SLEEPn

IN1 Control

OUT1A

IN2 Logic

CLK

IN3 OUT1B

IN4

DC

Motor

SENSE1

+ -

VBB

FAULTn DMOS H BRIDGE

200 mV

OUT2A

OUT2B

DC

Motor

- +

GND SENSE2

Allegro MicroSystems, LLC 4

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

A3916 Dual DMOS Full-Bridge Motor Driver

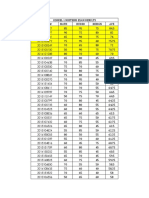

ELECTRICAL CHARACTERISTICS [1][2]: Valid at TJ = 25°C, VBB = 2.7 to 15 V, unless noted otherwise

Characteristics Symbol Test Conditions Min. Typ. Max. Unit

General

Load Supply Voltage Range VBB Operating 2.7 – 15 V

TJ = 25°C, 500 mA, VBB = 5 V – 335 450 mΩ

TJ = 25°C, 500 mA, VBB = 2.7 V – 335 450 mΩ

RDS(ON,HS)

TJ = 85°C, 500 mA, VBB = 5 V – 410 – mΩ

TJ = 85°C, 500 mA, VBB = 2.7 V – 410 – mΩ

Output On Resistance

TJ = 25°C, 500 mA, VBB = 5 V – 375 525 mΩ

TJ = 25°C, 500 mA, VBB = 2.7 V – 375 525 mΩ

RDS(ON,LS)

TJ = 85°C, 500 mA, VBB = 5 V – 455 – mΩ

TJ = 85°C, 500 mA, VBB = 2.7 V – 455 – mΩ

Diode Forward Voltage VF I = 500 mA – 0.85 1.0 V

IBB(2p7V) Outputs disabled, VBB = 2.7 V – 2.2 4.5 mA

VBB Supply Current IBB(15V) Outputs disabled, VBB = 15 V – 3.1 4.5 mA

IBB(SLEEP) Sleep Mode – – 0.5 µA

Control Logic

VIN(1) 2.0 – – V

Logic Input Voltage, INx

VIN(0) – – 0.8 V

VIN(1) 2.0 – – V

Logic Input Voltage, SLEEPn

VIN(0) – – 0.4 V

Logic Input Hysteresis VHYS 100 – 500 mV

Logic Input Current IIN VIN = 3.3 V, pulldown = 100 kΩ – 33 50 µA

Fault Output Voltage VFAULTn Flag asserted, IFAULTn = 1 mA – – 200 mV

Fault Output Leakage Current IFAULTn VFAULTn = 5 V – – 1.0 µA

VSENSE Blank time tBLANK 2.1 3.1 4.1 µs

VSENSE Trip Voltage VTRIP 170 205 240 mV

Fixed Off-Time tOFF 20 30 40 µs

Protection Circuits

Crossover Delay tOCD 200 550 1000 ns

VBB Undervoltage Lockout VBB(UVLO) VBB rising – 2.55 2.65 V

VBB Hysteresis VBB(UVLO,HYS) – 125 – mV

Thermal Shutdown Temperature TJ1 150 165 180 °C

Thermal Shutdown Hysteresis ΔTJ1 – 20 – °C

[1] Typical data is for design information only.

[2] Specified limits are tested at a single temperature and assured over operating temperature range by design and characterization.

Allegro MicroSystems, LLC 5

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

A3916 Dual DMOS Full-Bridge Motor Driver

Control Logic

Table 1: DC Motor Operation

IN1 IN2 OUT1A OUT1B Function

0 0 Off Off Disabled

1 0 High Low Forward

0 1 Low High Reverse

1 1 Low Low Brake

IN3 IN4 OUT2A OUT2B Function

0 0 Off Off Disabled

1 0 High Low Forward

0 1 Low High Reverse

1 1 Low Low Brake

Table 2: Stepper Motor Operation

IN1 IN2 IN3 IN4 OUT1A OUT1B OUT2A OUT2B Function

0 0 0 0 Off Off Off Off Disabled Disabled

1 0 1 0 High Low High Low Full Step 1 ½ Step 1

0 0 1 0 Off Off High Low – ½ Step 2

0 1 1 0 Low High High Low Full Step 2 ½ Step 3

0 1 0 0 Low High Off Off – ½ Step 4

0 1 0 1 Low High Low High Full Step 3 ½ Step 5

0 0 0 1 Off Off Low High – ½ Step 6

1 0 0 1 High Low Low High Full Step 4 ½ Step 7

1 0 0 0 High Low Off Off – ½ Step 8

Allegro MicroSystems, LLC 6

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

A3916 Dual DMOS Full-Bridge Motor Driver

FUNCTIONAL DESCRIPTION

Device Operation Enable

The A3916 is a dual full-bridge motor driver capable of operat- When all logic inputs are pulled to logic low, the outputs of the

ing one stepper motor, two DC motors, or one high-current DC bridges are disabled. The charge pump and internal circuitry

motor. MOSFET output stages substantially reduce the voltage continue to run when the outputs are disabled.

drop and the power dissipation of the A3916 outputs, compared

Thermal Shutdown

to typical drivers with bipolar transistors.

The A3916 will disable the outputs if the junction temperature

Output current can be regulated by pulse-width modulating

reaches 165°C. When the junction temperature drops 20°C, the

(PWM) the inputs. In addition to supporting external PWM of the outputs will be enabled.

driver, the A3916 limits the peak current by internally PWMing

the source driver when the current in the winding exceeds the Brake Mode

peak current, as determined by a sense resistor. If internal current

When driving DC motors, the A3916 goes into brake mode (turns

limiting is not needed, the sense pin should be shorted to ground.

on both sink drivers) when both of its inputs are high (IN1 and

Internal circuit protection includes thermal shutdown with hys- IN2, or IN3 and IN4). There is no current limiting during brak-

teresis, undervoltage lockout, internal clamp diodes, crossover ing, so care must be taken to ensure that the peak current during

current protection, and overcurrent protection. braking does not exceed the absolute maximum current.

External PWM Internal PWM Current Control

Output current regulation can be achieved by pulse-width modu- Each full-bridge is controlled by a fixed off-time PWM current

lating the inputs. Slow decay mode is selected by holding one control circuit that limits the load current to a desired value, ITRIP.

input high while PWMing the other input. Holding one input low Initially, a diagonal pair of source and sink DMOS outputs are

and PWMing the other input results in fast decay. enabled and current flows through the motor winding and the

current sense resistor, RSENSEx. When the voltage across RSENSEx

Blanking equals the internal reference voltage, the current sense compara-

tor resets the PWM latch, which turns off the source driver.

This function blanks the output of the current sense comparator

when the outputs are switched. The comparator output is blanked The maximum value of current limiting, ITRIP(max), is set by the

to prevent false current limit detections due to reverse recovery selection of the sense resistor, RSENSEx, and is approximated by a

currents of the clamp diodes or to switching transients related to transconductance function:

the capacitance of the load. The blank time, tBLANK, is approxi- ITRIP(max) = 0.2 ÷ RSENSEx

mately 3 μs. It is critical to ensure the maximum rating on SENSEx pins

(0.5 V) is not exceeded.

Sleep Mode

An active-low control input used to minimize power consump- Synchronous Rectification

tion when the A3916 is not in use. This disables much of the When a PWM off-cycle is triggered by an internal fixed off-time

internal circuitry including the output drivers, internal regulator, cycle, load current recirculates in slow decay SR mode. During

and charge pump. A logic high allows normal operation. When slow decay, current recirculates through the sink-side FET and

coming out of sleep mode, wait 1.5 ms before issuing a command the sink-side body diode. The SR feature enables the sink-side

to allow the internal regulator and charge pump to stabilize. FET, effectively shorting out the body diode. The sink driver is

Allegro MicroSystems, LLC 7

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

A3916 Dual DMOS Full-Bridge Motor Driver

not enabled until the source driver is turned off and the cross-

over delay has expired. This feature helps lower the voltage drop

during current recirculation, lowering power dissipation in the

bridge.

OCP

The voltage across enabled output drivers is monitored to protect

against short circuits. If an overcurrent protection event occurs,

both motor bridges are disabled until either SLEEPn is brought

low or the VBB supply is cycled.

FAULTn

This is an open-drain output that is pulled low during a TSD

or overcurrent protection event. For a TSD event, The output

is released when the die temperature falls below the TSD level

minus the hysteresis. For an over-current event, the output is held

low until either SLEEPn is brought low or the VBB supply is

cycled.

Parallel Operation

The A3916 can be paralleled for applications that require higher

output currents. In paralleled mode, the driver can source 1.8 A

continuous. The A3916 has two completely independent bridges

with separate internal current limit latches. This allows the device

to supply two separate loads, and as a result, when paralleled, it is

imperative that the internal current control is disabled by shorting

the sense pins to ground.

Because the internal current limit trip threshold is internally fixed

at 0.2 V, the trace resistance must be kept small so the internal

current latch is not triggered prematurely. With acceptable mar-

gin, the voltage drop across the trace resistance should be under

0.1 V. At a peak current of 2.5 A, the trace resistance should be

kept below 40 mΩ to prevent false tripping of the overcurrent

latch.

Each bridge has some variation in propagation delay. During this

time, it is possible that one bridge will have to support the full

load current for a very short period of time. Propagation delays

are characterized and guard banded to protect the driver from

damage during these events.

Allegro MicroSystems, LLC 8

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

A3916 Dual DMOS Full-Bridge Motor Driver

Package Outline Drawings

For Reference Only – Not for Tooling Use

(Reference JEDEC MO-220WEED-4)

Dimensions in millimeters – NOT TO SCALE

Exact case and lead configuration at supplier discretion within limits shown

0.30

0.50

3

16

16

0.90

1

A 1

2

3 1.70 3.10

1.70

0.75

3.10

0.25 C PCB Layout Reference View

0.50

1.70

0.40

1.70 A Terminal #1 mark area

2

B Exposed thermal pad (reference only, terminal #1 identifier appearance at supplier discretion)

1 C Reference land pattern layout (reference IPC7351 QFN50P300X300X80-17W2M); all pads a minimum

of 0.20 mm from all adjacent pads; adjust as necessary to meet application process requirements and

PCB layout tolerances; when mounting on a multilayer PCB, thermal vias at the exposed thermal pad

land can improve thermal dissipation (reference EIA/JEDEC Standard JESD51-5)

16

Figure 2: 16-contact 3 mm × 3 mm QFN package (Suffix ES)

Allegro MicroSystems, LLC 9

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

A3916 Dual DMOS Full-Bridge Motor Driver

For Reference Only – Not for Tooling Use

(Reference JEDEC MO-220WGGD)

Dimensions in millimeters – NOT TO SCALE

Exact case and lead configuration at supplier discretion within limits shown

0.30

0.50

4.00

20

20

0.95

1

A

2 1

2

4.00 2.45 4.10

2.45

21X D C

4.10

0.08 C 0.75

SEATING

PLANE C PCB Layout Reference View

0.25

0.50

0.40

B

2.45 A Terminal #1 mark area

2 B Exposed thermal pad (reference only, terminal #1 identifier appearance at supplier discretion)

1

C Reference land pattern layout (reference IPC7351 QFN50P400X400X80-21BM); all pads a minimum of 0.20 mm

from all adjacent pads; adjust as necessary to meet application process requirements and PCB layout tolerances;

when mounting on a multilayer PCB, thermal vias at the exposed thermal pad land can improve thermal dissipation

(reference EIA/JEDEC Standard JESD51-5)

20

D Coplanarity includes exposed thermal pad and terminals

2.45

Figure 3: 20-contact 4 mm × 4 mm QFN package (Suffix ES, -1)

Allegro MicroSystems, LLC 10

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

A3916 Dual DMOS Full-Bridge Motor Driver

Revision History

Number Date Description

– September 21, 2016 Initial release

Updated Features and Benefits (page 1) and Output On Resistance (page 5); corrected Selection

1 October 7, 2016

Guide (page 2).

2 January 18, 2017 Corrected VBB Hysteresis units (page 5).

3 January 19, 2018 Updated Blanking (page 7), OCP, Faultn, and Parallel Operations sections (page 8).

Copyright ©2018, Allegro MicroSystems, LLC

Allegro MicroSystems, LLC reserves the right to make, from time to time, such departures from the detail specifications as may be required to

permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that

the information being relied upon is current.

Allegro’s products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of

Allegro’s product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its

use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com

Allegro MicroSystems, LLC 11

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

Das könnte Ihnen auch gefallen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- WR424GB00DDokument16 SeitenWR424GB00DIgor San Martín PeñalozaNoch keine Bewertungen

- Silo Cement CalculationDokument11 SeitenSilo Cement CalculationFikriaraz AfifNoch keine Bewertungen

- Data Structures and AlgorithmsDokument45 SeitenData Structures and AlgorithmsKeith Tanaka MagakaNoch keine Bewertungen

- AutoCAD Mechanical 2015 Overview Brochure - A4Dokument4 SeitenAutoCAD Mechanical 2015 Overview Brochure - A4Raul ReynosoNoch keine Bewertungen

- 04.protection of 33KV Feeder.Dokument16 Seiten04.protection of 33KV Feeder.gnpr_10106080Noch keine Bewertungen

- Rochor Station Pile Design CalculationsDokument15 SeitenRochor Station Pile Design CalculationsDifa LiuNoch keine Bewertungen

- Bellin, E. H. (1984) - The Psychoanalytic Narrative On The Transformational Axis Between Writing and SpeechDokument15 SeitenBellin, E. H. (1984) - The Psychoanalytic Narrative On The Transformational Axis Between Writing and SpeechofanimenochNoch keine Bewertungen

- PDS - GulfSea Hydraulic AW Series-1Dokument2 SeitenPDS - GulfSea Hydraulic AW Series-1Zaini YaakubNoch keine Bewertungen

- Power Cable Installation ManualDokument50 SeitenPower Cable Installation ManualAnn DodsonNoch keine Bewertungen

- MSYS-1 0 11-ChangesDokument3 SeitenMSYS-1 0 11-ChangesCyril BerthelotNoch keine Bewertungen

- Windows Mbox Viewer User Manual 1.0.3.4Dokument33 SeitenWindows Mbox Viewer User Manual 1.0.3.4Billy NoelNoch keine Bewertungen

- Introduction to Continuous Optimization for Machine LearningDokument10 SeitenIntroduction to Continuous Optimization for Machine LearningMarcos OliveiraNoch keine Bewertungen

- CI SetDokument18 SeitenCI Setতন্ময় ঢালি Tanmay DhaliNoch keine Bewertungen

- IMChap 014 SDokument14 SeitenIMChap 014 STroy WingerNoch keine Bewertungen

- OracleDokument23 SeitenOracleriza arifNoch keine Bewertungen

- ASP Flashcards - QuizletDokument36 SeitenASP Flashcards - QuizletRehman MuzaffarNoch keine Bewertungen

- Pumps - IntroductionDokument31 SeitenPumps - IntroductionSuresh Thangarajan100% (1)

- Ey-H3l Yh1576Dokument44 SeitenEy-H3l Yh1576jorgeNoch keine Bewertungen

- WebControls - TabStripDokument38 SeitenWebControls - TabStripProkopis PrNoch keine Bewertungen

- The Machining of Brake DiscsDokument8 SeitenThe Machining of Brake DiscsBusu Cyp100% (1)

- Leveling Limits For Stationary Reciprocating Compressors: Engineering ReferenceDokument2 SeitenLeveling Limits For Stationary Reciprocating Compressors: Engineering ReferencealtruismNoch keine Bewertungen

- Self Report QuestionnaireDokument6 SeitenSelf Report QuestionnaireMustafa AL ShlashNoch keine Bewertungen

- Public Key Cryptography: S. Erfani, ECE Dept., University of Windsor 0688-558-01 Network SecurityDokument7 SeitenPublic Key Cryptography: S. Erfani, ECE Dept., University of Windsor 0688-558-01 Network SecurityAbrasaxEimi370Noch keine Bewertungen

- Tech Note 14Dokument2 SeitenTech Note 14meteohrNoch keine Bewertungen

- Die Science - Developing Forming Dies - Part I - The FabricatorDokument6 SeitenDie Science - Developing Forming Dies - Part I - The FabricatorSIMONENoch keine Bewertungen

- 98 99 Anti Lock BrakesDokument101 Seiten98 99 Anti Lock BrakestrialnaqueraNoch keine Bewertungen

- Notifier Battery Calculations-ReadmeDokument11 SeitenNotifier Battery Calculations-ReadmeJeanCarlosRiveroNoch keine Bewertungen

- Instrument Resume OIL and GAS.Dokument3 SeitenInstrument Resume OIL and GAS.RTI PLACEMENT CELLNoch keine Bewertungen

- Midterm Exam Result Ce199-1l 2Q1920Dokument3 SeitenMidterm Exam Result Ce199-1l 2Q1920RA CarpioNoch keine Bewertungen