Beruflich Dokumente

Kultur Dokumente

Informe Final 7

Hochgeladen von

pieroCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Informe Final 7

Hochgeladen von

pieroCopyright:

Verfügbare Formate

FACULTAD DE INGIENERIA ELECTRICA Y

ELECTRONICA_______________________

UNIVERSIDAD NACIONAL DE INGENIERÍA

FACULTAD DE INGENIERÍA ELÉCTRICA Y ELECTRÓNICA

CICLO : 2017-2

MATERIA : LABORATORIO DE CIRCUITOS

ANALOGICOS

TEMA : AMPLIFICADOR DE POTENCIA DE SIMETRIA

COMPLEMENTARIA

INFORME FINAL 7

NOMBRE Y APELLIDOS :

SOLIER GALVEZ PIERO

SARANGO VELIZ ANDY

CHIROQUE SANCHEZ JOSE

CABELLO LAZARO YESENIA

DOCENTE: : ANGEL ALBUQUERQUE

GUERRERO

SECCIÓN: : M

LABORATORIO DE CIRCUITOS ANALOGICOS IT144M 1

FACULTAD DE INGIENERIA ELECTRICA Y

ELECTRONICA_______________________

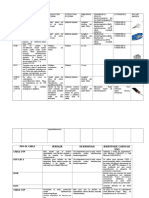

1.- En función de sus datos experimentales determine:

IC Q7, VCE Q7, VCB Q1, VB Q7:

TOMANDO EL CIRCUITO EN DC TENEMOS:

EXPERIMENTALMENTE SE OBTUVO:

En DC:

IC Q7 VCE Q7 VCB Q1 VB Q7

LABORATORIO DE CIRCUITOS ANALOGICOS IT144M 2

FACULTAD DE INGIENERIA ELECTRICA Y

ELECTRONICA_______________________

9.07 mA 8.84V 11.9V -10.5V

En AC:

LABORATORIO DE CIRCUITOS ANALOGICOS IT144M 3

FACULTAD DE INGIENERIA ELECTRICA Y

ELECTRONICA_______________________

VBE Q7 VE Q7 VB Q1 VB Q7 Vi

0.61V -10.3V -6.94V -9.64V 1 Vp

Para la salida obtuvimos los siguientes datos con respecto a la frecuencia:

f(Hz) 5 20 80 200 400 800 1k 2k 4k 10k 20k 30k 40k

Vout 24 172 400 492 512 518 520 512 504 488 460 432 404

(mV)

Nota: Dados los valores de los condensadores, cuando se trabajó en AC, estos

empezaron a comportarse como un corto circuito y así obtuvimos los valores en la

tabla anterior mostrada.

2.- Conclusiones y Observaciones correspondientes:

Los circuitos retroalimentados, es un circuito controlador de la ganancia hace que

la ganancia dependa de estos elementos lineales que conforman los circuitos

retroalimentado, y nos evita tener una gran ganancia de tensión y de corriente que

a veces son incontrolables.

LABORATORIO DE CIRCUITOS ANALOGICOS IT144M 4

FACULTAD DE INGIENERIA ELECTRICA Y

ELECTRONICA_______________________

Estos circuitos de multietapa nos sirve para obtener una mayor ganancia que los

circuitos amplificadores comunes con un solo transistor o con un solo Jfet.

Concluimos que las impedancias de entrada tienen que ser grande para una mejor

respuesta en la ganancia del transistor.

Se tuvo que tener cuidado con la resistencia en la salida del circuito ya que esta se

recalentaba constantemente por la cantidad de potencia que disipaba, lo más

recomendable era apagar las fuentes del circuito cada vez que se regularizaba la

frecuencia y después hacer las medidas correspondientes encendiendo las fuentes y

así sucesivamente hasta obtener todos los datos del laboratorio.

LABORATORIO DE CIRCUITOS ANALOGICOS IT144M 5

Das könnte Ihnen auch gefallen

- Armónicas en Sistemas Eléctricos IndustrialesVon EverandArmónicas en Sistemas Eléctricos IndustrialesBewertung: 4.5 von 5 Sternen4.5/5 (12)

- 2° Informe de Laboratorio de Potencia I-2Dokument15 Seiten2° Informe de Laboratorio de Potencia I-2Francis Horna RivasNoch keine Bewertungen

- LAB 6 - Regulador Zener y BJTDokument10 SeitenLAB 6 - Regulador Zener y BJTian barrigaNoch keine Bewertungen

- Practica No 2 Lab. EloDokument2 SeitenPractica No 2 Lab. EloEmerson Casi MarroNoch keine Bewertungen

- PRACTICAS ING EyE Sep 2020Dokument101 SeitenPRACTICAS ING EyE Sep 2020maco guzmanNoch keine Bewertungen

- Practicas Lab. Ing Eye Ago 2019Dokument110 SeitenPracticas Lab. Ing Eye Ago 2019bettyariana0% (1)

- Epi Laboratorio Citro B Condori Yancapallo Leonardo Walter 9Dokument9 SeitenEpi Laboratorio Citro B Condori Yancapallo Leonardo Walter 9Steep HacheNoch keine Bewertungen

- Fase 6Dokument10 SeitenFase 6jairo100% (1)

- Manual Practicas Lab. Ing Eye Ago 2022Dokument112 SeitenManual Practicas Lab. Ing Eye Ago 2022López Piñón IsaacNoch keine Bewertungen

- Laboratorio de ElectrotecniaDokument8 SeitenLaboratorio de ElectrotecniaWalterAlfaroFloresNoch keine Bewertungen

- Rectificador de OndaDokument20 SeitenRectificador de OndaAnonymous hHSPMvsGdNoch keine Bewertungen

- Proyecto Final de ElectronicaDokument12 SeitenProyecto Final de ElectronicaMarthin Sontura EscNoch keine Bewertungen

- Practicas Del Laboratorio de Ingeniería Eléctrica y Electrónica PDFDokument100 SeitenPracticas Del Laboratorio de Ingeniería Eléctrica y Electrónica PDFricardo100% (1)

- Reguladores de Voltaje Discretos e IntegradosDokument6 SeitenReguladores de Voltaje Discretos e IntegradosAngel RojasNoch keine Bewertungen

- Práctica 6Dokument3 SeitenPráctica 6Freddy SantanderNoch keine Bewertungen

- Amplificador Operacional Como InversorDokument9 SeitenAmplificador Operacional Como InversorMaycool CarriónNoch keine Bewertungen

- PRACTICAS LAB. ING EyE AGO 2020 PDFDokument112 SeitenPRACTICAS LAB. ING EyE AGO 2020 PDFErixel JijonNoch keine Bewertungen

- Potencia MonofasicaDokument13 SeitenPotencia MonofasicaThony Andia FuentesNoch keine Bewertungen

- LAB 05 CITRO1 Rectificador de Onda CompletaDokument4 SeitenLAB 05 CITRO1 Rectificador de Onda CompletaELIO CALIXTO APAZA MOLINANoch keine Bewertungen

- Preinforme 2Dokument11 SeitenPreinforme 2alconegro07Noch keine Bewertungen

- Practica 2Dokument19 SeitenPractica 2Angell Glez SalgadoNoch keine Bewertungen

- Informe1 - LabEP (USO DE SOFTWARE DE SIMULACIÓN PARA CIRCUITOS DE ELECTRÓNICA DE POTENCIA)Dokument10 SeitenInforme1 - LabEP (USO DE SOFTWARE DE SIMULACIÓN PARA CIRCUITOS DE ELECTRÓNICA DE POTENCIA)Mauricio LlanoNoch keine Bewertungen

- Grupo4 - CE3A-Lab 4Dokument9 SeitenGrupo4 - CE3A-Lab 4LUIS ALBERTO CUPA HANCCONoch keine Bewertungen

- Instituto Politécnico NacionalDokument17 SeitenInstituto Politécnico NacionalPau AGNoch keine Bewertungen

- Informe Practica 2 Rect TrifDokument5 SeitenInforme Practica 2 Rect TrifAndres Rengifo MejiaNoch keine Bewertungen

- Práctica 4 Lab Electricidad EsiqieDokument20 SeitenPráctica 4 Lab Electricidad EsiqieselinetNoch keine Bewertungen

- Informe Rectificador de OndaDokument6 SeitenInforme Rectificador de OndaJohann Mercado LeonNoch keine Bewertungen

- Laboratorio 3Dokument13 SeitenLaboratorio 3TANIA BEATRIZ LEON ARIASNoch keine Bewertungen

- Lab 3. Rectificación-Rizado RenovaboDokument8 SeitenLab 3. Rectificación-Rizado RenovaboKaterine Quimbayo AgredaNoch keine Bewertungen

- Prácticas Circuitos Ii PDFDokument16 SeitenPrácticas Circuitos Ii PDFHugo SuarezNoch keine Bewertungen

- Lab2 - Amplificador Fuente ComúnDokument8 SeitenLab2 - Amplificador Fuente Comúnedgar_tenorio_18100% (1)

- Informe 2 l2Dokument9 SeitenInforme 2 l2sergiocuellar7Noch keine Bewertungen

- Práctica5 Puente WienDokument8 SeitenPráctica5 Puente WienSarai Mendez MeloNoch keine Bewertungen

- Epi Laboratorio Citro B Quispe Condori Wilfredo 4Dokument9 SeitenEpi Laboratorio Citro B Quispe Condori Wilfredo 4Steep HacheNoch keine Bewertungen

- Practica 1 MultimetroDokument14 SeitenPractica 1 MultimetroDavis RjNoch keine Bewertungen

- Instituto Politécnico NacionalDokument93 SeitenInstituto Politécnico NacionalErick VelascoNoch keine Bewertungen

- Práctica 2Dokument23 SeitenPráctica 2Tania MaquedaNoch keine Bewertungen

- Respuesta en Frecuencia Del Amplificador Multietapa en CascadaDokument18 SeitenRespuesta en Frecuencia Del Amplificador Multietapa en CascadaManuel Alexis Santillana GarabitoNoch keine Bewertungen

- Práctica 2Dokument92 SeitenPráctica 2Mari SalasNoch keine Bewertungen

- Práctica #2 de Electrónica.Dokument14 SeitenPráctica #2 de Electrónica.Michael TuarezNoch keine Bewertungen

- Lab3 - Amplificador Drenaje Común y Compuerta Común Con MosfDokument11 SeitenLab3 - Amplificador Drenaje Común y Compuerta Común Con Mosfedgar_tenorio_18100% (1)

- Práctica 2. Ing. Electrica y ElectronicaDokument23 SeitenPráctica 2. Ing. Electrica y ElectronicaTania MaquedaNoch keine Bewertungen

- ProyFinal AngelMendoza - RubenGonzalezDokument20 SeitenProyFinal AngelMendoza - RubenGonzalezAngel MendozaNoch keine Bewertungen

- LabCirC - Pract4 - Parámetros de AC - Docx (1) - 1Dokument5 SeitenLabCirC - Pract4 - Parámetros de AC - Docx (1) - 1Jhonny Vargas100% (1)

- LabCirC - Pract4 - Parámetros de AC - DocxDokument6 SeitenLabCirC - Pract4 - Parámetros de AC - DocxStalin AguaizaNoch keine Bewertungen

- Práctica 4 - Amplificador OperacionalDokument11 SeitenPráctica 4 - Amplificador OperacionalLuis Humberto Reyes MuñozNoch keine Bewertungen

- Lab 01 Circuitos Electronicos 2Dokument4 SeitenLab 01 Circuitos Electronicos 2Lu RangelNoch keine Bewertungen

- Epi Laboratorio Citro B Castro Gutierrez Miguel Angel 4Dokument8 SeitenEpi Laboratorio Citro B Castro Gutierrez Miguel Angel 4Steep HacheNoch keine Bewertungen

- GUIA EloIDokument24 SeitenGUIA EloIArn_M_LNoch keine Bewertungen

- Lab 01 - ML125Dokument20 SeitenLab 01 - ML125william13cvNoch keine Bewertungen

- Práctica 2Dokument19 SeitenPráctica 2Alfredo TlapaleNoch keine Bewertungen

- Laboratorio de CircuitosDokument5 SeitenLaboratorio de CircuitosJavier EsquivelNoch keine Bewertungen

- Informe 4Dokument7 SeitenInforme 4juanNoch keine Bewertungen

- Laboratorio 2Dokument6 SeitenLaboratorio 2Bethza CalamaniNoch keine Bewertungen

- Lab 3 Makinas Electricas IDokument6 SeitenLab 3 Makinas Electricas IAlexander Valera ChupillonNoch keine Bewertungen

- Epi Laboratorio Citro B Mamani Orcco Piero Renato 9Dokument9 SeitenEpi Laboratorio Citro B Mamani Orcco Piero Renato 9Steep HacheNoch keine Bewertungen

- Lab 08 Citro1 PDFDokument3 SeitenLab 08 Citro1 PDFKaren CayoNoch keine Bewertungen

- 3 - Laboratorio de Circuitos ElectricosDokument9 Seiten3 - Laboratorio de Circuitos ElectricoscarlosNoch keine Bewertungen

- Cuestionario de ComputaciónDokument4 SeitenCuestionario de ComputaciónJuan Carlos McÖf̲̲̅̅ı̲̲̅̅c̲̲̅̅ı̲̲̅̅a̲̲̅̅l̲̲̅̅Noch keine Bewertungen

- Calculo AutotransformadorDokument4 SeitenCalculo Autotransformadordari245120Noch keine Bewertungen

- Tarea2 203038 10 Diana TocarrunchoDokument7 SeitenTarea2 203038 10 Diana Tocarrunchojaime dangondNoch keine Bewertungen

- Guía para El Desarrollo Del Componente Práctico Virtual - 243006Dokument15 SeitenGuía para El Desarrollo Del Componente Práctico Virtual - 243006Jairo HurtatisNoch keine Bewertungen

- Instituto Gubernamental Mixto HibuerasDokument15 SeitenInstituto Gubernamental Mixto HibuerasDarwinJosephCastilloNoch keine Bewertungen

- Manual de Prácticas para Microcontrolador ATmega8Dokument33 SeitenManual de Prácticas para Microcontrolador ATmega8PANCHIShdz100% (2)

- LTE - Balance Enlace DL LTEDokument13 SeitenLTE - Balance Enlace DL LTECarlos Gonzales100% (1)

- Práctica - 06 - El Transistor BJT PNP - Polarización y APLICACIONES NPNDokument13 SeitenPráctica - 06 - El Transistor BJT PNP - Polarización y APLICACIONES NPNYOFRE BRAYAN POMA CHUQUILLANQUINoch keine Bewertungen

- Dpi y LpiDokument12 SeitenDpi y LpiJorge LuqueNoch keine Bewertungen

- Formularios ComtelDokument6 SeitenFormularios ComtelJoseLuisAmpueroNoch keine Bewertungen

- Silabo de Sistemas Digitales 2013 - IIDokument11 SeitenSilabo de Sistemas Digitales 2013 - IIEdwin ChoquegonzaNoch keine Bewertungen

- Clase 01 - El TiristorDokument21 SeitenClase 01 - El Tiristorjohn haileNoch keine Bewertungen

- Examen Circuitos I Segundo Vila Rodriguez Bastidas PDFDokument4 SeitenExamen Circuitos I Segundo Vila Rodriguez Bastidas PDFjulio sanchezNoch keine Bewertungen

- Amplificador OperacionalDokument8 SeitenAmplificador OperacionalEdson GutierrezNoch keine Bewertungen

- 456622-An-01-Es-siemens Logo Kp300 Basic StarterkitDokument538 Seiten456622-An-01-Es-siemens Logo Kp300 Basic StarterkitluisNoch keine Bewertungen

- Conector Secundario Tipo FaaDokument2 SeitenConector Secundario Tipo FaamarckalhiNoch keine Bewertungen

- Todo Prog. Ing de Comuni InalambricasDokument7 SeitenTodo Prog. Ing de Comuni InalambricasOscar Marcelo Atachagua NaverosNoch keine Bewertungen

- Codificador y DecodificadorDokument2 SeitenCodificador y DecodificadorMiguel VHNoch keine Bewertungen

- Training Course Special PDFDokument78 SeitenTraining Course Special PDFfirenet colombia100% (1)

- Línea de Tiempo de Las ComputadorasDokument10 SeitenLínea de Tiempo de Las ComputadorasRuben Eduardo Sanchez LopezNoch keine Bewertungen

- Convertidores de Potencia de CCDokument5 SeitenConvertidores de Potencia de CCChristianNoch keine Bewertungen

- Grupo A - Proyecto Temporizador 555Dokument4 SeitenGrupo A - Proyecto Temporizador 555Edgar BaqueNoch keine Bewertungen

- Técnicas de Análisis de CircuitosDokument9 SeitenTécnicas de Análisis de CircuitosWilly SalcedoNoch keine Bewertungen

- Manual Cargador de Baterias CaseroDokument14 SeitenManual Cargador de Baterias CaseroLucero LopezNoch keine Bewertungen

- PIC - Programación Puertos de E&S PIC18F4550Dokument22 SeitenPIC - Programación Puertos de E&S PIC18F4550Kevin HansNoch keine Bewertungen

- Redes HFC Sena Tipos de AmplificadoresDokument4 SeitenRedes HFC Sena Tipos de AmplificadoresDescarga Detodo0% (1)

- O3b PPT Itesm 27feb15Dokument26 SeitenO3b PPT Itesm 27feb15Miguel Larumbe BoladoNoch keine Bewertungen

- p222 10154 Lista de Precios TECNOSERVICEDokument124 Seitenp222 10154 Lista de Precios TECNOSERVICEjose peresNoch keine Bewertungen

- Actividad 3 - Redes y Medios de TransmisionDokument2 SeitenActividad 3 - Redes y Medios de TransmisionLuis Fernando Torres RodriguezNoch keine Bewertungen

- 03a Polarizacion BJT EA1Dokument7 Seiten03a Polarizacion BJT EA1Gisela CaputoNoch keine Bewertungen