Beruflich Dokumente

Kultur Dokumente

Control LED Drive Circuit: Features

Hochgeladen von

JacksonVelozOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Control LED Drive Circuit: Features

Hochgeladen von

JacksonVelozCopyright:

Verfügbare Formate

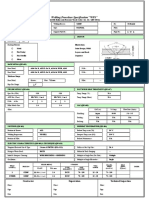

Etek

Microelectronics ET6202

Control LED drive circuit

Overview

ET6202 is 1 / 7 to 1 / 8 duty cycle control of the LED display driver circuit. By paragraph

11 output, the output gate 6, paragraph 1 / output gate, A display memory, control circuit, key

scan circuit composed of a single-chip high-reliability of the external LED driver circuit. Serial

data 4-wire serial interface into the ET6202, the use of SOP28 package.

Features

z CMOS technology

z Low-power

z A variety of display modes: choice of settings, and the number of spaces (4 to 7, 10 to 13)

z Scan button: 10 × 2 matrix

z 8 levels of brightness adjustment circuit

z 4-wire serial interface

z Package for SOP28

Pin assignment

OSC 1 28 GND

DI/O 2 27 GR1

CLK 3 26 GR2

STB 4 25 GND

K1 5 24 GR3

K2 6 23 GR4

VDD 7 22 GND

SG1/KS1 8 ET6202 21 VDD

SG2/KS2 9 20 SG14/GR5

SG3/KS3 10 19 SG13/GR6

SG4/KS4 11 18 SG12/GR7

SG5/KS5 12 17 SG10/KS10

SG6/KS6 13 16 SG9/KS9

SG7/KS7 14 15 SG8/KS8

Rev 1.1 2004-6-4

1/14

ET6202

Pin Description

Number

Pin Name I/O Description of the function

ET6202

1 OSC I Oscillation input port to connect a resistor to determine the oscillation frequency

Data input and output ports (N-channel open drain), the clock in the serial data

2 DI/O I/O output falling, In the clock rising edge of the serial data input.

Clock input port, when read in the rising edge of the serial data, and in falling

3 CLK I

output when the number According to

Serial interface filtering, falling in the STB input data as an order. (External

4 STB I

pull-down power Resistance)

I Key input data port, the port on the importation of these data show that

5,6 K1~K2 there is locked at the end of the cycle End

22,25, Grounding pin

GND ─

28

SG1/KS1~ Paragraph output port (P-channel open drain), can also be used as keys

8~17 O

SG10/KS10 input scanning

18 SG12/GR7 O Paragraph / output port gate

7,21 VDD ─ Power Supply

19,20, Gate output port

23

GR6~GR1 O

24,26,

27

I / O configuration

The logical part of the I / O diagram

below.

1. Input port: CLK, STB & DIN

VDD

GND

Rev 1.1 2004-6-4

2/14

ET6202

2. Input: K1 ~ K2

VDD

GND

3. Output ports: DOUT, GR1 ~ GR4

VDD

GND

4. Outputs: SG1 ~ SG10

VDD

GND

Rev 1.1 2004-6-4

3/14

ET6202

5. GR5,GR6 and SG12/GR7

VDD

GND

Functional block diagram

SG1/KS1

SG2/KS2

Control

SG3/KS3

DI/O Serial SG4/KS4

CLK Data SG5/KS5

STB Interface Show memory SG6/KS6

SG7/KS7

Paragraph SG8/KS8

driver / SG9/KS9

OSC Timing Scan key SG10/KS10

Crystal generator

driver / SG12/GR7

R SG13/GR6

Gate driver

SG14/GR5

Key scan matrix GR4

GND

Memory

GR3

GR2

GR1

Brightness

adjustment circuit

K1 K2 VDD GND

Rev 1.1 2004-6-4

4/14

ET6202

Functions

Order

STB ports in the state by the high-low, the importation of an order by the DIN port of the first byte (b0 ~ b7). If

the data or the order in the transmission For some reason, STB is set to port, serial communications are to be

initialized, the data is input / command be considered invalid.

Order 1: display mode command set

ET6202 provides as follows two display modes: a command in the port of the STB by the state after the high-low

by the DIN port to lose ET6202 into the first byte (b0 ~ b7). For these orders, the No. 3 to No. 6 (b2 ~ b5) are ig-

nored, 7 and 8 (b6 ~ b7) 0. Display mode command set used by the decision, gate number (4 to 7, 10 to 13). Must

show that an order to continue to make the show. If you choose the same mode settings, not to implement the

order, so there will be no show. When the electric power, the choice of 10 × 7-bit mode.

MSB LSB

0 0 ─ ─ ─ ─ b1 b0

b2 ~ b5 no assignment

Display mode:

b1 for 0, b0 to 0:13 paragraph × 4 bits

b1 for 0, b0 to 1:12 paragraph bit × 5

b1 for 1, b0 to 0:11 paragraph bit × 6

b1 for 1, b0 1:10 paragraph bit × 7

Order 2: Set the order data

Data set is the order of implementation of the ET6202 read and write data. The first order of 5 and 6 (b4, b5) are

ignored, 8-bit (b7) 0, No. 7 (b6) is set to 1. When the electric power supply when the first 4 to a (b3 ~ b0) should

be set to 0

MSB LSB

0 1 ─ ─ b3 b2 b1 b0

b4, b5 non-assignment

Mode:

b3 0: normal mode of operation

b3 1: Test mode

Incremental mode address settings (mode):

b2 0: After the data into the Incremental address

b2 1: Address the same

Read and write data mode:

b1 for 0, b0 0: write data to the display mode

b1 for 1, b0 0: Reading key scan data

Rev 1.1 2004-6-4

5/14

ET6202

ET6202's key scan matrix scan button and enter the data storage RAM

The ET6202 is a key scan matrix, as follows from the 10 × 2 array composed of:

K1

K2

SG1/ SG2/ SG3/ SG4/ SG5/ SG6/ SG7/ SG8/ SG9/ SG10/

KS1 KS2 KS3 KS4 KS5 KS6 KS7 KS8 KS9 KS10

Each scan key input data storage as follows, by an order from the highest-READ was read out. When the high

data (b0) was read out, The next lowest data (b7) was read out.

K1………………K2 K1………………K2

Read

SG1/KS1 SG2/KS2 x order

SG3/KS3 SG4/KS4 x

SG5/KS5 SG6/KS6 x

SG7/KS7 SG8/KS8 x

SG9/KS9 SG10/KS10 x

b0…………….b1 b3………………b4 b5………………b7

Notes: b5 ~ b7 no definition.

Order 3: Address set up a command

Address set up a command is set up for display memory address. If the address is 00H ~ 0DH, then the effective

address. If the address is 0EH Address or higher, the data is invalid unless once again set the correct address.

When the electric power, to address 00H.

Please refer to the chart below.

MSB LSB

1 1 ─ ─ b3 b2 b1 b0

b4, b5 non-assignment

b0 to b3 address 00H ~ 0DH

Rev 1.1 2004-6-4

6/14

ET6202

Display mode and the address of the RAM

Display RAM memory through the serial interface from the external device to input data ET6202.

ET6202 of RAM address is as follows (8 units).

SG1………………SG4 SG5………………SG8 SG9………………SG12

00HL 00HU 01HL DIG1

02HL 02HU 03HL DIG2

04HL 04HU 05HL DIG3

06HL 06HU 07HL DIG4

08HL 08HU 09HL DIG5

0AHL 0AHU 0BHL DIG6

0CHL 0CHU 0DHL DIG7

b0…………….b3 b4………………b7

xxHL xxHU

Low 4 High 4

Order 4: Display Control Order

Display Control command to control the display switches can also be used to set pulse width. Please refer to the

table below. When the electric power, setting 1 / 16 the width letter and the show closed (key stop scanning).

MSB LSB

1 0 ─ ─ b3 b2 b1 b0

b4, b5 non-assignment

Show:

b3 0: The show closed (to scan button)

b3 1: Open show

Dimming level:

000: width = 1 / 16

001: width = 2 / 16

010: width = 4 / 16

011: width = 10/16

100: width = 11/16

101: width = 12/16

110: width = 13/16

111: width = 14/16

Rev 1.1 2004-6-4

7/14

ET6202

Scan timing and show

Bond plans to scan and display timing is as follows. A key scan cycle includes 2. 10 × 2 matrix of data stored in RAM.

Tdisplay=500us Key scan data

SG Output DIG1 DIG2 DIG3 DIGn DIG1

G1

G2

G3

Gn

1 A =Tdisplay ×(n+1)

Rev 1.1 2004-6-4

8/14

ET6202

Serial communication format

The chart shown in the ET6202 is a serial communication format. DOUT port is an N-channel open drain output

port, so be sure to add a guarantee Pull-up resistor (1K ~ 10K) to DOUT port.

Receiver (data / write operations command)

If the data continue

STB

DIN

b0 b1 b2 b6 b7

CLK

1 2 3 7 8

Transmission (read data)

STB

DIN

b0 b1 b2 b3 b4 b5 b6 b7

CLK

1 2 3 4 5 6 7 8 1 2 3 4 5 6

twait

b0 b1 b2 b3 b4 b5

Reading set up a command data Start reading data

twait(Latency) 1 s )≥1µs It is worth noting that when reading data, the instructions of the eighth of the clock

rising edge to read the data then the first falling edge of the clock must be greater than or

1 s mean waiting time twait

Rev 1.1 2004-6-4

9/14

ET6202

Conversion characteristic waveform

ET6202 conversion wave characteristics are as follows.

fosc

OSC 50%

PWSTB

STB

PWCLK PWCLK

t CLK-STB

CLK

t setup thold

DIN

t PZL t PLZ

DOUT

t TZL t TLZ

Gn

90%

10%

10%

90%

Sn

t TZH t THZ

PWCLK (Clock pulse) 400ns PWSTB(Filter width) 1 s

tsetup(Data setup time) 100ns thold(Data hold time) 100ns

tCLK-STB(Filter clock time) 1 s tTHZ(Fall time) 10 s

tTZH(Rise time) 1 s tPZL(Transmission delay) 100ns

fosc = oscillation frequency tPLZ(Transmission delay) 300ns

tTZL<1µs tTLZ<10µs

Rev 1.1 2004-6-4

10/14

ET6202

Notes: The test conditions are as follows.

tTHZ(Pull-down resistance = 10k , load capacitance = 300pf)

tTLZ(Pull-up resistor = 10k , load capacitance = 300pf)

Apply

1. Input data show

STB

CLK

DIN Order 2 Order 3 Data 1 Data n Order 1 Order 4

Order 1: display mode command set

Order 2: Set the order data

Order 3: Address set up a command

Data 1 ~ n: mobile data show that (the largest of 14 bytes)

Order 4: Display Control Order

2. Enter a specific address

STB

CLK

DIN Order 2 Order 3 Data Order 1 Order 4

Order 2: Set data

Order 3: Address Setting

Data: The data show

Rev 1.1 2004-6-4

11/14

ET6202

Software flow chart

Start

Delay 200 ms

Set

Order 2

(Write data)

Set 3 order

Qing display

RAM

(See Note) Initialization

Set

Set

Order 1

Set

Order 4

(88H-8FH: open the show)

Main program

Set Order 2

(Including the key time to

scan the data and write data)

Set Main cycle

3 order

Set

Order 1

Set

Order 4

End

Rev 1.1 2004-6-4

12/14

ET6202

Notes:

1. Order 1: display mode

2. Order 2: Set data

3. Order 3: Address Setting

4. Order 4: Display Control

When the power supply IC of the first power-on, the display RAM in the content has not been defined, so be sure

to empty the initialization settings in the display RAM.

Limit parameter

1. Maximum Ratings(Ta = 25Co,GND=0V

Parameters Symbol Range Unit

To provide voltage VDD -0.5~+7 V

Logic input voltage VI -0.5~VDD+0.5 V

IOLGR +250 mA

Drive output current

IOHSG -50 mA

Maximum output current ITOTAL 400 mA

2. Recommended by the working conditions(Ta = -20~+70℃,GND = 0V)

Parameters Symbol Minimum Typical Max Unit

Logic supply voltage VDD 4.5 5 5.5 V

Dynamic current (see Note) IDDdyn — — 5 mA

高电平输入电压 VIH 0.8VDD — VDD V

低电平输入电压 VIL 0 — 0.3VDD V

注释:测试条件:设置显示控制命令=80H(显示关闭状态&无载入情况)

电参数(VDD = 5V,GND = 0V,Ta = 25℃)

参数 符号 测试条件 最小值 典型值 最大值 单位

V0=VDD-2V

IOHSG1 SG1~SG11, -20 -25 -40 mA

SG12/GR7

高电平输出电流

V0=VDD-3V

IOHSG2 SG1~SG11, -25 -30 -50 mA

SG12/GR7

V0=0.3V

低电平输出电流 IOLGR GR1~GR6, 100 140 — mA

SG12/GR7

IOLDOU

低电平输出电流 Vo=0.4V 4 — — mA

T

V0=VDD-3V

段输出端高电平输出

ITOLSG SG1~SG11, — — +5 %

电流百分比

SG12/GR7

高电平输入电压 VIH — 0.8VDD — 5 V

低电平输入电压 VIL — 0 — 0.3VDD V

振荡频率 fosc R=51k 350 500 650 kHz

K1~K2

K1~K2 的下拉电阻 RKN 40 — 100 kΩ

VDD=5V

Rev 1.1 2004-6-4

13/14

ET6202

Reference to the road map Applications

G1

DIGIT1

G2

DIGIT2

G3

DIGIT3

G4

51k DIGIT4

G5

OSC GND DIGIT5

G1 G6

DI/O GR1 DIGIT6

G2

CLK GR2

MCU

11段×6位LED

STB GND

(共阴极)

G3 S12

K1 GR3 SEG12

G4 S10

+5 K2 GR4 SEG10

S9

+5 VDD GND +5 SEG9

10k

10k

10k

S8

SG1/KS1 VDD 0.1uf SEG8

S1 G5 S7

SG2/KS2 SG14/GR5 SEG7

S2 G6 S6

SG3/KS3 SG13/GR6 SEG6

S3 S5

SG4/KS4 SG12/GR7 SEG5

S4 S12 S4

SG5/KS5 SG10/KS10 SEG4

S5 S10 S3

SG6/KS6 SG9/KS9 SEG3

S6 S9 S2

SG7/KS7 SG8/KS8 SEG2

S7 S8 S1

SEG1

KS10

KS9

KS8

KS7

KS6

KS5

KS4

KS3

KS2

KS1

SW28

SW25

SW22

SW19

SW16

SW13

SW10

SW7

SW4

SW1

SW29

SW26

SW23

SW20

SW17

SW14

SW11

SW8

SW5

SW2

LED cathode connection

共阴极的LED连接

a COM/DIGITAL(GRID) a

SEG1

SEG2 b f b

g

SEG3 c

d e c

SEG4

e h

SEG5 d

SEG6 f

SEG7 g

SEG8 h

1. 连接在 GND 和 VDD 端口之间的电容(0.1µF)必须放置在离 ET6202 尽可能近的地方。

2. 建议 NC 端口(管脚 10)连接到地。

*:此电路仅供参考。

Rev 1.1 2004-6-4

14/14

Das könnte Ihnen auch gefallen

- TM1628Dokument14 SeitenTM1628István FeketeNoch keine Bewertungen

- MC2101 TM1628 PDFDokument22 SeitenMC2101 TM1628 PDFPol ErnNoch keine Bewertungen

- Description: Technical DataDokument17 SeitenDescription: Technical DataDhivya NNoch keine Bewertungen

- LED Driver IC: DescriptionDokument12 SeitenLED Driver IC: Descriptionanand shekhawatNoch keine Bewertungen

- TM1638 enDokument18 SeitenTM1638 enfotakis michaelNoch keine Bewertungen

- L EDD Ri Ve R Co NT Ro LL Er T M163 8: 1, DescriptionDokument18 SeitenL EDD Ri Ve R Co NT Ro LL Er T M163 8: 1, DescriptionJorge Luis Vega CaballeroNoch keine Bewertungen

- Description Features: PT6967 LED Driver ICDokument22 SeitenDescription Features: PT6967 LED Driver ICDhivya NNoch keine Bewertungen

- VFD Driver/Controller IC: PT6315 v2.0 Sep. 2002Dokument26 SeitenVFD Driver/Controller IC: PT6315 v2.0 Sep. 2002movvNoch keine Bewertungen

- Datasheet TM1637Dokument12 SeitenDatasheet TM1637DiegoNoch keine Bewertungen

- Coolaudio V3208 DatasheetsDokument5 SeitenCoolaudio V3208 DatasheetsVictorNoch keine Bewertungen

- Vma425 SchemeDokument1 SeiteVma425 Schemejakalae5263Noch keine Bewertungen

- 7 A H-Bridge For DC-Motor Applications 30348: Preliminary DatasheetDokument4 Seiten7 A H-Bridge For DC-Motor Applications 30348: Preliminary DatasheetallisonNoch keine Bewertungen

- TM1628Dokument14 SeitenTM1628chandra sekhar BeheraNoch keine Bewertungen

- 7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetDokument32 Seiten7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetMecaSoftwareNoch keine Bewertungen

- ET6218R EtekMicroelectronicsDokument15 SeitenET6218R EtekMicroelectronicsHasnah HusnaNoch keine Bewertungen

- TLE7209 R InfineonDokument16 SeitenTLE7209 R Infineonmobil benerNoch keine Bewertungen

- TA84007PQ, TA84007SG, TA84007FG: PreliminaryDokument16 SeitenTA84007PQ, TA84007SG, TA84007FG: PreliminarywijakesumaNoch keine Bewertungen

- Levitation LightDokument1 SeiteLevitation LightHamza_AK100% (1)

- GD75232Dokument18 SeitenGD75232ijf_a3780Noch keine Bewertungen

- Datasheet SN3218Dokument12 SeitenDatasheet SN3218Daniel SilvaNoch keine Bewertungen

- Acrosser Technology AR B1673 DatasheetDokument5 SeitenAcrosser Technology AR B1673 DatasheetWaleed MareeNoch keine Bewertungen

- About The Device/PLC Connection ManualsDokument7 SeitenAbout The Device/PLC Connection ManualsDenisNoch keine Bewertungen

- Smart Octal Low-Side Switch: LogicDokument17 SeitenSmart Octal Low-Side Switch: Logicjuan echeverryNoch keine Bewertungen

- Rak3172-Sip Wisduo Lpwan Sip Datasheet: DescriptionDokument9 SeitenRak3172-Sip Wisduo Lpwan Sip Datasheet: DescriptionoliviercorianNoch keine Bewertungen

- AR-B5500 MANUAL: Setting Up The SystemDokument5 SeitenAR-B5500 MANUAL: Setting Up The SystemTrentungcaysoBombodealopNoch keine Bewertungen

- PD16732A, 16732B: Mos Integrated CircuitDokument24 SeitenPD16732A, 16732B: Mos Integrated CircuitAnika HernandezNoch keine Bewertungen

- TB62747AFG ToshibaDokument20 SeitenTB62747AFG ToshibavinNoch keine Bewertungen

- Vcore MosfetDokument8 SeitenVcore MosfetErick MirandaNoch keine Bewertungen

- Description Features: PT6964 LED Driver ICDokument15 SeitenDescription Features: PT6964 LED Driver ICDhivya NNoch keine Bewertungen

- Smart Octal Low-Side Switch: Features Product SummaryDokument16 SeitenSmart Octal Low-Side Switch: Features Product SummaryAriel MercochaNoch keine Bewertungen

- Schematic - PIC-Broggio Certo2 - 2023-10-26Dokument1 SeiteSchematic - PIC-Broggio Certo2 - 2023-10-26ENERGOSNoch keine Bewertungen

- TM1651 V1.1 enDokument12 SeitenTM1651 V1.1 enPriyanka ShanmugamNoch keine Bewertungen

- Datasheet PDFDokument12 SeitenDatasheet PDFomen0attaqiNoch keine Bewertungen

- DDR Termination Regulator: Features General DescriptionDokument1 SeiteDDR Termination Regulator: Features General DescriptionLina LinuNoch keine Bewertungen

- Trilithic Data Sheet Bts 781 GP: 1 1.1 FeaturesDokument17 SeitenTrilithic Data Sheet Bts 781 GP: 1 1.1 FeaturesВиктор СабовNoch keine Bewertungen

- Tle 62326 Low Side SwitchDokument19 SeitenTle 62326 Low Side SwitchDiego CaceresNoch keine Bewertungen

- S5851a eDokument28 SeitenS5851a ekunalkundanam1046Noch keine Bewertungen

- General-Purpose Relay G2Rs: Ordering InformationDokument12 SeitenGeneral-Purpose Relay G2Rs: Ordering InformationJulius Aldana BeltranNoch keine Bewertungen

- Main Features: - Set-Top-Boxes - White Goods - Home Appliances - DVD Players and VcrsDokument25 SeitenMain Features: - Set-Top-Boxes - White Goods - Home Appliances - DVD Players and VcrsDhivya NNoch keine Bewertungen

- DatasheetDokument16 SeitenDatasheetAndres GuerreroNoch keine Bewertungen

- Specification Nta92cDokument6 SeitenSpecification Nta92cRajeshNoch keine Bewertungen

- CA-104 E 05 ElectronicsDokument16 SeitenCA-104 E 05 ElectronicsMohammad RizkiNoch keine Bewertungen

- Update Reader 08.02.2024Dokument10 SeitenUpdate Reader 08.02.2024mikeNoch keine Bewertungen

- PTC Princeton Tech PT6312BLQ - C110225Dokument21 SeitenPTC Princeton Tech PT6312BLQ - C110225tulio enrique leon ayalaNoch keine Bewertungen

- Data Sheet HM 9270Dokument10 SeitenData Sheet HM 9270Ivan RomeroNoch keine Bewertungen

- 7N60 7N65 Data SheetDokument7 Seiten7N60 7N65 Data Sheetsunder punjabiNoch keine Bewertungen

- TLE4279 SiemensSemiconductorGroupDokument19 SeitenTLE4279 SiemensSemiconductorGroupLuis MezaNoch keine Bewertungen

- Dokumen - Tips - 11 Siemens s5s7 Series M2icokr Siemen11 Siemens s5s7 Series s5 95uDokument20 SeitenDokumen - Tips - 11 Siemens s5s7 Series M2icokr Siemen11 Siemens s5s7 Series s5 95uzahra ghaziNoch keine Bewertungen

- SG3524NDokument20 SeitenSG3524NAhmed ShagidullinNoch keine Bewertungen

- SG3524 PDFDokument24 SeitenSG3524 PDFErasmo Franco SNoch keine Bewertungen

- Sg3524 Texas Instrument WayDokument24 SeitenSg3524 Texas Instrument WayDaniel NwodoNoch keine Bewertungen

- AR-701B-X Fit 35mm DIN Rail or Mount Directly: CN1 CN2 CN3Dokument6 SeitenAR-701B-X Fit 35mm DIN Rail or Mount Directly: CN1 CN2 CN3trisatriabNoch keine Bewertungen

- MCP23009Dokument52 SeitenMCP23009João Oliveira BentesNoch keine Bewertungen

- GS8208 LED Datasheet PDFDokument12 SeitenGS8208 LED Datasheet PDFDaisyNoch keine Bewertungen

- TB62747AFG, TB62747AFNG: 16-Output Constant Current LED DriverDokument20 SeitenTB62747AFG, TB62747AFNG: 16-Output Constant Current LED DriverSaša DinčićNoch keine Bewertungen

- Cj1w-Cif11 DSDokument6 SeitenCj1w-Cif11 DSPérsio Costanti de AraújoNoch keine Bewertungen

- Schematic - How To Make MT8870 DTMF Phone Audio Decoder - 2022-08-08Dokument1 SeiteSchematic - How To Make MT8870 DTMF Phone Audio Decoder - 2022-08-08Florencio cancheNoch keine Bewertungen

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsVon EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsBewertung: 1 von 5 Sternen1/5 (1)

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIVon EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSINoch keine Bewertungen

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsVon EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNoch keine Bewertungen

- Sharp CD-sw200Dokument124 SeitenSharp CD-sw200tecnologo456Noch keine Bewertungen

- BufferDokument1 SeiteBufferAlainbravopaezNoch keine Bewertungen

- 2SB507Dokument4 Seiten2SB507JacksonVelozNoch keine Bewertungen

- Advanced Power Electronics Corp.: AP70T03GH/JDokument4 SeitenAdvanced Power Electronics Corp.: AP70T03GH/JJacksonVelozNoch keine Bewertungen

- Math ExamDokument21 SeitenMath ExamedgemarkNoch keine Bewertungen

- PixiiDokument3 SeitenPixiiFoxNoch keine Bewertungen

- M.Sc. Steel Structures LEC. #7 Plastic Analysis and Design: Dr. Qasim Shaukat KhanDokument43 SeitenM.Sc. Steel Structures LEC. #7 Plastic Analysis and Design: Dr. Qasim Shaukat KhanSSNoch keine Bewertungen

- Carbonate Platform MateriDokument8 SeitenCarbonate Platform MateriNisaNoch keine Bewertungen

- 5000-5020 en PDFDokument10 Seiten5000-5020 en PDFRodrigo SandovalNoch keine Bewertungen

- Iroquois Clothes and WampumDokument3 SeitenIroquois Clothes and Wampumapi-254323856Noch keine Bewertungen

- Wps For Carbon Steel THK 7.11 GtawDokument1 SeiteWps For Carbon Steel THK 7.11 GtawAli MoosaviNoch keine Bewertungen

- You're reading a free preview. Pages 4 to 68 are not shown in this preview. Leer la versión completa You're Reading a Free Preview Page 4 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 5 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 6 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 7 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 8 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 9 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 10 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 11 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 12 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 13 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 14 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 15 is notDokument9 SeitenYou're reading a free preview. Pages 4 to 68 are not shown in this preview. Leer la versión completa You're Reading a Free Preview Page 4 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 5 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 6 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 7 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 8 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 9 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 10 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 11 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 12 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 13 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 14 is not shown in this preview. DESCARGA You're Reading a Free Preview Page 15 is notFernando ToretoNoch keine Bewertungen

- Southern California International Gateway Final Environmental Impact ReportDokument40 SeitenSouthern California International Gateway Final Environmental Impact ReportLong Beach PostNoch keine Bewertungen

- April 8/91: All GroupsDokument33 SeitenApril 8/91: All Groupsreza mirzakhaniNoch keine Bewertungen

- 5G NR Essentials Guide From IntelefyDokument15 Seiten5G NR Essentials Guide From IntelefyUzair KhanNoch keine Bewertungen

- Xii Mathematics CH 01 Question BankDokument10 SeitenXii Mathematics CH 01 Question BankBUNNY GOUDNoch keine Bewertungen

- A Tall Order - Cooling Dubai's Burj Khalifa: FeatureDokument2 SeitenA Tall Order - Cooling Dubai's Burj Khalifa: FeatureMohsin KhanNoch keine Bewertungen

- Hatayoga 1Dokument11 SeitenHatayoga 1SACHIDANANDA SNoch keine Bewertungen

- 2021-01-01 - Project (Construction) - One TemplateDokument1.699 Seiten2021-01-01 - Project (Construction) - One TemplatemayalogamNoch keine Bewertungen

- Technology ForecastingDokument38 SeitenTechnology ForecastingSourabh TandonNoch keine Bewertungen

- MikoritkDokument6 SeitenMikoritkChris Jonathan Showip RouteNoch keine Bewertungen

- Measuring and Modeling Vertical Crosshead Vibration in Api-618 Reciprocating CompressorsDokument18 SeitenMeasuring and Modeling Vertical Crosshead Vibration in Api-618 Reciprocating CompressorshmshawkiNoch keine Bewertungen

- Ibragimova Lesson 4Dokument3 SeitenIbragimova Lesson 4Dilnaz IbragimovaNoch keine Bewertungen

- State Farm Claims: PO Box 52250 Phoenix AZ 85072-2250Dokument2 SeitenState Farm Claims: PO Box 52250 Phoenix AZ 85072-2250georgia ann polley-yatesNoch keine Bewertungen

- HYDRAULIC WINCH-MS1059 - Operation & Maintenance Manual Rev ADokument33 SeitenHYDRAULIC WINCH-MS1059 - Operation & Maintenance Manual Rev Azulu80Noch keine Bewertungen

- Carte EnglezaDokument112 SeitenCarte EnglezageorgianapopaNoch keine Bewertungen

- YhhjjDokument52 SeitenYhhjjSam CunananNoch keine Bewertungen

- Steve Jobs TalkDokument3 SeitenSteve Jobs TalkDave CNoch keine Bewertungen

- Molde Soldadura TADokument1 SeiteMolde Soldadura TAMarcos Ivan Ramirez AvenaNoch keine Bewertungen

- Team 6 - Journal Article - FinalDokument8 SeitenTeam 6 - Journal Article - FinalAngela Christine DensingNoch keine Bewertungen

- NATO Obsolescence Management PDFDokument5 SeitenNATO Obsolescence Management PDFluisNoch keine Bewertungen

- 50 Law-Firms Details by Vaibhav SharmaDokument17 Seiten50 Law-Firms Details by Vaibhav SharmaApoorva NandiniNoch keine Bewertungen

- Nuttall Gear CatalogDokument275 SeitenNuttall Gear Catalogjose huertasNoch keine Bewertungen

- Ict's - 2022 - Mentorship - Summarized - Thread - by - Trader - Theory - Sep 22, 22 - From - RattibhaDokument11 SeitenIct's - 2022 - Mentorship - Summarized - Thread - by - Trader - Theory - Sep 22, 22 - From - RattibhaChristiana OnyinyeNoch keine Bewertungen