Beruflich Dokumente

Kultur Dokumente

WWW - Manaresults.Co - In: Set No. 1

Hochgeladen von

Rajesh PylaOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

WWW - Manaresults.Co - In: Set No. 1

Hochgeladen von

Rajesh PylaCopyright:

Verfügbare Formate

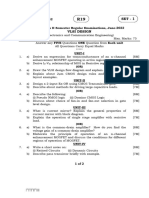

Code No: RT41028 R13 Set No.

1

IV B.Tech I Semester Regular/Supplementary Examinations, Oct/Nov - 2018

VLSI DESIGN

(Electrical and Electronics Engineering)

Time: 3 hours Max. Marks: 70

Question paper consists of Part-A and Part-B

Answer ALL sub questions from Part-A

Answer any THREE questions from Part-B

*****

PART–A (22 Marks)

1. a) What is the size of silicon wafer used for manufacturing state-of-the art VLSI

IC`s? Explain why? [4]

b) Define Figure of Merit with the necessary expression. [3]

c) Design a layout diagram for two input nMOS NAND gate. [4]

d) List and explain the three sources of wiring capacitances. [3]

e) What are the effects of scaling on Vt ? [4]

f) Define library. Give the syntax of signal assignment statement. [4]

PART–B (3x16 = 48 Marks)

2. a) Explain the MOS transistor operation with the help of neat sketches in the

Depletion mode. [8]

b) Discuss the steps involved in BiCMOS technology. [8]

3. a) Clearly explain body effect of MOSFET. [8]

b) Design and draw the circuit diagram of an nMOS inverter and explain its

operation with the help of transfer characteristics. [8]

4. a) Design a stick diagram for two input nMOS NOR Gate. [8]

b) Discuss the transistor related design rule (orbit 2µm CMOS). [8]

5. a) Explain in detail about formal estimation of CMOS inverter delay. [8]

b) Discuss nMOS transistor as a switch. [8]

6. a) Explain the limits of miniaturization on scaling. [8]

b) In gate logic, compare the geometric aspects between two-input nMOS NAND

and CMOS NAND gates. [8]

7. a) List the various abstraction levels in VHDL. Explain any one of them. [8]

b) Write in brief about logic synthesis process. [8]

1 of 1

WWW.MANARESULTS.CO.IN

|''|'''||''||'''||||

Das könnte Ihnen auch gefallen

- WWW - Manaresults.Co - In: Set No. 1Dokument4 SeitenWWW - Manaresults.Co - In: Set No. 1DivyaNoch keine Bewertungen

- SubsystemsDokument1 SeiteSubsystemsMaheshwar ReddyNoch keine Bewertungen

- 523 BA19 Ad 01Dokument5 Seiten523 BA19 Ad 01ramesh1926Noch keine Bewertungen

- WWW - Manaresults.co - In: Set No. 1Dokument1 SeiteWWW - Manaresults.co - In: Set No. 1HaripriyaNoch keine Bewertungen

- Code No: R05320402Dokument4 SeitenCode No: R05320402chvsrsettiNoch keine Bewertungen

- Vlsi Design: III B. Tech II Semester Regular Examinations, April/May - 2019Dokument4 SeitenVlsi Design: III B. Tech II Semester Regular Examinations, April/May - 2019pawan100% (1)

- Set No. 1: WWW - Manaresults.Co - inDokument1 SeiteSet No. 1: WWW - Manaresults.Co - inkishore kumarNoch keine Bewertungen

- Vlsi Design April 2019Dokument4 SeitenVlsi Design April 2019RakeshNoch keine Bewertungen

- WWW - Manaresults.Co - In: (Electronics and Communication Engineering)Dokument8 SeitenWWW - Manaresults.Co - In: (Electronics and Communication Engineering)Adhvay KrishnaNoch keine Bewertungen

- VLSIDesignDokument5 SeitenVLSIDesignVenkatesh KolatiNoch keine Bewertungen

- r7411001 Vlsi DesignDokument4 Seitenr7411001 Vlsi DesignsivabharathamurthyNoch keine Bewertungen

- Set No. 1: M Ds GS TN 2 DSDokument6 SeitenSet No. 1: M Ds GS TN 2 DSSRINIVASA RAO GANTANoch keine Bewertungen

- r05320402 Vlsi DesignDokument4 Seitenr05320402 Vlsi DesignSRINIVASA RAO GANTANoch keine Bewertungen

- VLSI DESIGN Question Bank: Unit 1Dokument12 SeitenVLSI DESIGN Question Bank: Unit 1Babu GundlapallyNoch keine Bewertungen

- WWW - Manaresults.Co - In: Set No. 1Dokument4 SeitenWWW - Manaresults.Co - In: Set No. 1Muneer DasariNoch keine Bewertungen

- r05410207 Vlsi DesignDokument7 Seitenr05410207 Vlsi Design9010469071Noch keine Bewertungen

- Jntu Vlsi Systems DesignDokument5 SeitenJntu Vlsi Systems Design9010469071Noch keine Bewertungen

- WWW - Manaresults.co - In: Vlsi DesignDokument2 SeitenWWW - Manaresults.co - In: Vlsi DesignjagadeeshNoch keine Bewertungen

- Rr320405 Vlsi DesignDokument6 SeitenRr320405 Vlsi DesignSrinivasa Rao GNoch keine Bewertungen

- Rr410505 Vlsi Systems DesignDokument4 SeitenRr410505 Vlsi Systems DesignSrinivasa Rao GNoch keine Bewertungen

- Vlsi QP 1Dokument6 SeitenVlsi QP 1Sailesh PosaniNoch keine Bewertungen

- WWW - Manaresults.Co - In: Set No. 1Dokument4 SeitenWWW - Manaresults.Co - In: Set No. 1jani28cseNoch keine Bewertungen

- R07 Set No. 2Dokument4 SeitenR07 Set No. 2Naga LakshmiNoch keine Bewertungen

- WWW - Manaresults.co - In: Computer NetworksDokument1 SeiteWWW - Manaresults.co - In: Computer NetworksMurali Krishna ChanapathiNoch keine Bewertungen

- Set No: 1: Code No: V3219/R07Dokument4 SeitenSet No: 1: Code No: V3219/R07Gopi Pavan JonnadulaNoch keine Bewertungen

- rr321202 Vlsi Systems DesignDokument4 Seitenrr321202 Vlsi Systems DesignSRINIVASA RAO GANTANoch keine Bewertungen

- VI Sem Jun-July 2005Dokument10 SeitenVI Sem Jun-July 2005Suraj KumarNoch keine Bewertungen

- B .Tech IV Year I Semester (R07) Supplementary Examinations June 2015Dokument1 SeiteB .Tech IV Year I Semester (R07) Supplementary Examinations June 2015subbuNoch keine Bewertungen

- WWW - Manaresults.Co - In: (Electronics and Communication Engineering)Dokument2 SeitenWWW - Manaresults.Co - In: (Electronics and Communication Engineering)venkiscribd444Noch keine Bewertungen

- NR-221103 - Digital Circuits Design and ApplictionDokument5 SeitenNR-221103 - Digital Circuits Design and ApplictionSrinivasa Rao G100% (1)

- Jntua University Previous Question Papers: Dept., of E.C.E, RCEWDokument4 SeitenJntua University Previous Question Papers: Dept., of E.C.E, RCEWHarshini ANoch keine Bewertungen

- Digital Nov 07Dokument6 SeitenDigital Nov 07skssushNoch keine Bewertungen

- WWW - Manaresults.co - In: Digital System Design & Digital Ic ApplicationsDokument1 SeiteWWW - Manaresults.co - In: Digital System Design & Digital Ic Applicationssailaja kumariNoch keine Bewertungen

- M.E. (VLSI & Embedded System) : Asic Design and Modelling (2008 Course)Dokument9 SeitenM.E. (VLSI & Embedded System) : Asic Design and Modelling (2008 Course)Manu SeaNoch keine Bewertungen

- University Question Papers - VLSIDokument26 SeitenUniversity Question Papers - VLSIVijayNoch keine Bewertungen

- Previous PapersDokument12 SeitenPrevious PapersKaran SanaNoch keine Bewertungen

- Previous Question PapersDokument4 SeitenPrevious Question Papersshaker423Noch keine Bewertungen

- CS 801D PDFDokument4 SeitenCS 801D PDFarnab paulNoch keine Bewertungen

- Eprvd-102 Eprds-102a - 01.12 PDFDokument2 SeitenEprvd-102 Eprds-102a - 01.12 PDFNaresh KumarNoch keine Bewertungen

- R7310201-Computer System OrganizationDokument4 SeitenR7310201-Computer System OrganizationsivabharathamurthyNoch keine Bewertungen

- Electronic Switching Systems R16 Oct 2019Dokument4 SeitenElectronic Switching Systems R16 Oct 2019yaswanth saiNoch keine Bewertungen

- Ec 1354Dokument5 SeitenEc 1354kvnelavarasiNoch keine Bewertungen

- 1 Semester Model Question PapersDokument17 Seiten1 Semester Model Question PapersBalaji MohantyNoch keine Bewertungen

- WWW - Manaresults.Co - in WWW - Manaresults.Co - In: Set No. 1Dokument4 SeitenWWW - Manaresults.Co - in WWW - Manaresults.Co - In: Set No. 1Sree pujitha DoppalapudiNoch keine Bewertungen

- WWW - Manaresults.Co - in WWW - Manaresults.Co - In: Set No. 1Dokument4 SeitenWWW - Manaresults.Co - in WWW - Manaresults.Co - In: Set No. 1Sree pujitha DoppalapudiNoch keine Bewertungen

- Intelligent Manufacturing SystemsDokument5 SeitenIntelligent Manufacturing SystemsVenkata RamuduNoch keine Bewertungen

- IV-i Question Bank (r15)Dokument82 SeitenIV-i Question Bank (r15)kd17209Noch keine Bewertungen

- M.Tech I Semester Supplementary Examinations February/March 2018Dokument1 SeiteM.Tech I Semester Supplementary Examinations February/March 2018baburao_kodavatiNoch keine Bewertungen

- (3965) - 636 M.E. (E & TC) : (VLSI & Embedded Systems)Dokument14 Seiten(3965) - 636 M.E. (E & TC) : (VLSI & Embedded Systems)Manu SeaNoch keine Bewertungen

- Campusexpress - Co.in: Set No. 1Dokument8 SeitenCampusexpress - Co.in: Set No. 1skssushNoch keine Bewertungen

- Iare Co Ece QP 1Dokument2 SeitenIare Co Ece QP 1harshit playboyNoch keine Bewertungen

- SEPTEMBERDokument3 SeitenSEPTEMBERRocky BobeeNoch keine Bewertungen

- Unconventional Machining Processes November 2016Dokument4 SeitenUnconventional Machining Processes November 2016SATISHNoch keine Bewertungen

- Vlsi Design June 2022Dokument8 SeitenVlsi Design June 2022SivaGaneshGollaNoch keine Bewertungen

- WWW - Manaresults.Co - In: Set No. 1Dokument1 SeiteWWW - Manaresults.Co - In: Set No. 1surendraloya99Noch keine Bewertungen

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionVon EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionNoch keine Bewertungen

- Complete PCB Design Using OrCAD Capture and PCB EditorVon EverandComplete PCB Design Using OrCAD Capture and PCB EditorBewertung: 5 von 5 Sternen5/5 (1)

- From Microstructure Investigations to Multiscale Modeling: Bridging the GapVon EverandFrom Microstructure Investigations to Multiscale Modeling: Bridging the GapDelphine BrancherieNoch keine Bewertungen

- 8 Bi-CMOSDokument9 Seiten8 Bi-CMOSRajesh PylaNoch keine Bewertungen

- Common Emitter AmplifierDokument3 SeitenCommon Emitter AmplifierRajesh PylaNoch keine Bewertungen

- 6 CMOS Twin Tub ProcessDokument17 Seiten6 CMOS Twin Tub ProcessRajesh PylaNoch keine Bewertungen

- Low PowerDokument67 SeitenLow PowerRajesh PylaNoch keine Bewertungen

- 7 Alternative Forms of Pull-UpDokument15 Seiten7 Alternative Forms of Pull-UpRajesh Pyla100% (1)

- Common Emitter ConfigurationDokument4 SeitenCommon Emitter ConfigurationRajesh PylaNoch keine Bewertungen

- 5 CMOS P-Well & N-Well ProcessDokument15 Seiten5 CMOS P-Well & N-Well ProcessRajesh PylaNoch keine Bewertungen

- Unit 6 - BEEEDokument61 SeitenUnit 6 - BEEERajesh PylaNoch keine Bewertungen

- 5 CMOS P-Well & N-Well ProcessDokument15 Seiten5 CMOS P-Well & N-Well ProcessRajesh PylaNoch keine Bewertungen

- Unit 5 - BEEE 2Dokument17 SeitenUnit 5 - BEEE 2Rajesh PylaNoch keine Bewertungen

- Unit 4 - BEEEDokument41 SeitenUnit 4 - BEEERajesh PylaNoch keine Bewertungen

- JNTUK R16 Syllabus For ECEDokument154 SeitenJNTUK R16 Syllabus For ECEVenugopal Konapala100% (1)

- 10 Latch UpDokument6 Seiten10 Latch UpRajesh PylaNoch keine Bewertungen

- 6 CMOS Twin Tub ProcessDokument17 Seiten6 CMOS Twin Tub ProcessRajesh PylaNoch keine Bewertungen

- The Design and Simulation of An InverterDokument27 SeitenThe Design and Simulation of An InverterArunNoch keine Bewertungen

- 7 3Dokument1 Seite7 3Rajesh PylaNoch keine Bewertungen

- Digital Communications by J.s.chitodeDokument188 SeitenDigital Communications by J.s.chitodeKrishna Prakash Nanduri100% (1)

- Vlsi QB 2019Dokument5 SeitenVlsi QB 2019Rajesh PylaNoch keine Bewertungen

- Mentor Tut1Dokument30 SeitenMentor Tut1Dhruva PradhanNoch keine Bewertungen

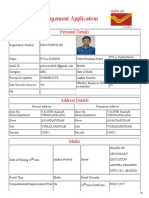

- Postal JobDokument3 SeitenPostal JobRajesh PylaNoch keine Bewertungen

- Unit-5 Part ADokument7 SeitenUnit-5 Part ARajesh PylaNoch keine Bewertungen

- H 6809102015Dokument1 SeiteH 6809102015Rajesh PylaNoch keine Bewertungen

- The Design and Simulation of An InverterDokument27 SeitenThe Design and Simulation of An InverterArunNoch keine Bewertungen

- 7 3Dokument1 Seite7 3Rajesh PylaNoch keine Bewertungen

- Designing Implementing Real Time Signal Processing SystemsDokument44 SeitenDesigning Implementing Real Time Signal Processing SystemsRajesh PylaNoch keine Bewertungen

- Basics of Quantum MechanicsDokument43 SeitenBasics of Quantum MechanicsIvan MishelNoch keine Bewertungen

- AdderDokument20 SeitenAdderRajesh PylaNoch keine Bewertungen

- Ugc Admin Journal ReportDokument1 SeiteUgc Admin Journal ReportRajesh PylaNoch keine Bewertungen

- Design Rules 1Dokument20 SeitenDesign Rules 1Rajesh PylaNoch keine Bewertungen

- ECEN720: High-Speed Links Circuits and Systems Spring 2021: Lecture 5: Termination, TX Driver, & Multiplexer CircuitsDokument66 SeitenECEN720: High-Speed Links Circuits and Systems Spring 2021: Lecture 5: Termination, TX Driver, & Multiplexer Circuits陈晨Noch keine Bewertungen

- V850ES/KF1, V850ES/KG1, V850ES/KJ1: User's ManualDokument757 SeitenV850ES/KF1, V850ES/KG1, V850ES/KJ1: User's ManualArif RahmanNoch keine Bewertungen

- ELEN2021: Microprocessors: Digital Logic and DesignDokument25 SeitenELEN2021: Microprocessors: Digital Logic and DesignKuzivashe KudzeremaNoch keine Bewertungen

- A Universal Programming Cable For RadiosDokument39 SeitenA Universal Programming Cable For RadiosANSELMO LIMANoch keine Bewertungen

- GM300 SMDokument46 SeitenGM300 SMChristianNoch keine Bewertungen

- M74HC595B1Dokument13 SeitenM74HC595B1GeorgeNoch keine Bewertungen

- HT750 ServiceManualDokument96 SeitenHT750 ServiceManualkeroxc100% (1)

- TMUX13xx 5-V, Bidirectional 8:1, 1-Channel and 4:1, 2-Channel Multiplexers With Injection Current ControlDokument46 SeitenTMUX13xx 5-V, Bidirectional 8:1, 1-Channel and 4:1, 2-Channel Multiplexers With Injection Current ControlsibicsrNoch keine Bewertungen

- Single-Inductor Multiple-Output Switching Converters With Time-Multiplexing Control in Discontinuous Conduction ModeDokument12 SeitenSingle-Inductor Multiple-Output Switching Converters With Time-Multiplexing Control in Discontinuous Conduction ModeZhongpeng LiangNoch keine Bewertungen

- BTS 410 E2 Fonte CDMDokument16 SeitenBTS 410 E2 Fonte CDMPaulo SilvaNoch keine Bewertungen

- A Simple Circuit Approach To Reduce Delay Variations in Domino Logic GatesDokument9 SeitenA Simple Circuit Approach To Reduce Delay Variations in Domino Logic GatesKarthick NpNoch keine Bewertungen

- Ee141 Hw4 SolDokument16 SeitenEe141 Hw4 SolVidhya Ds100% (1)

- Circuits at The Nanoscale - Communications, Imaging, and SensingDokument635 SeitenCircuits at The Nanoscale - Communications, Imaging, and SensingAnkurNoch keine Bewertungen

- 74HC151Dokument11 Seiten74HC151jnax101Noch keine Bewertungen

- BiCMOS Advantages PDFDokument2 SeitenBiCMOS Advantages PDFPratibha SinghNoch keine Bewertungen

- Embedded Systems Design: A Unified Hardware/Software IntroductionDokument30 SeitenEmbedded Systems Design: A Unified Hardware/Software IntroductionNaresh Ks100% (1)

- DLCDokument16 SeitenDLCPrakashPrakashNoch keine Bewertungen

- Lecture 4 - The CMOS InverterDokument7 SeitenLecture 4 - The CMOS InverterVimala PriyaNoch keine Bewertungen

- Design of A Low Power 10T SRAM Cell: Nternational Ournal of Nnovative Esearch in Cience, Ngineering and EchnologyDokument3 SeitenDesign of A Low Power 10T SRAM Cell: Nternational Ournal of Nnovative Esearch in Cience, Ngineering and EchnologySuyash KumarNoch keine Bewertungen

- Introduction To L-EditDokument22 SeitenIntroduction To L-EditsairaghubabuNoch keine Bewertungen

- MOSIS Scalable CMOS (SCMOS) Design Rules (Revision 7.2) The MOSIS Service Usc/Isi 4676 Admiralty Way Marina Del Rey, CA 90292-6695Dokument30 SeitenMOSIS Scalable CMOS (SCMOS) Design Rules (Revision 7.2) The MOSIS Service Usc/Isi 4676 Admiralty Way Marina Del Rey, CA 90292-6695Anonymous 8umLvvHuNoch keine Bewertungen

- 3V CMOS Rail To Rail Op-AmpDokument5 Seiten3V CMOS Rail To Rail Op-AmpDadan DadicNoch keine Bewertungen

- VLSI BasicsDokument3 SeitenVLSI BasicsAlok YadavNoch keine Bewertungen

- Defect-Oriented Testing For Nano-Metric Cmos Vlsi Circuits 2nd EditionDokument342 SeitenDefect-Oriented Testing For Nano-Metric Cmos Vlsi Circuits 2nd EditionRotoplastic de Cuauhtémoc S.A. de C.V.Noch keine Bewertungen

- Notes On Digital Camera 1Dokument5 SeitenNotes On Digital Camera 1Ashoka VanjareNoch keine Bewertungen

- Novel Decoupling Capacitor Designs For Sub-90nm CMOS TechnologyDokument6 SeitenNovel Decoupling Capacitor Designs For Sub-90nm CMOS TechnologyNitin SonuNoch keine Bewertungen

- Low-Complexity Low-Latency Architecture For Identical of Data Encoded With Hard Systematic Error-Correcting CodesDokument104 SeitenLow-Complexity Low-Latency Architecture For Identical of Data Encoded With Hard Systematic Error-Correcting CodesJaya SwaroopNoch keine Bewertungen

- Unit-2 Mos and Bicmos Circuit Design ProcessesDokument29 SeitenUnit-2 Mos and Bicmos Circuit Design ProcessesSai KallemNoch keine Bewertungen

- Thesis Class E Power AMplifiers For Wireless CommunicationsDokument124 SeitenThesis Class E Power AMplifiers For Wireless CommunicationsYasmani Armas FuentesNoch keine Bewertungen

- Nc7Sz04 Tinylogic Uhs Inverter: Features DescriptionDokument10 SeitenNc7Sz04 Tinylogic Uhs Inverter: Features DescriptionyajujotosNoch keine Bewertungen