Beruflich Dokumente

Kultur Dokumente

Design of A Buck Converter PDF

Hochgeladen von

Daniel PancheOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Design of A Buck Converter PDF

Hochgeladen von

Daniel PancheCopyright:

Verfügbare Formate

International Journal of Engineering Research ISSN: 2319-6890)(online),2347-5013(print)

Volume No.5 Issue: Special 5, pp: 992-1128 20 May 2016

DESIGN OF A BUCK CONVERTER

B.VENKATESH NETHRAVATHI.S

Assistant Professor, Member IEEE, Assistant Professor, Member IEEE,

Electrical and Electronics Department, Electrical and Electronics Department,

B M S College of Engineering, B M S College of Engineering,

Bengaluru-19 Bengaluru-19

venkatesh.bodapati@gmail.com nethravathis.eee@bmsce.ac.in

Abstract— DC to DC converters are important in portable Buck boost converter - The buck-boost can be used for either

electronic devices. Such electronic devices often contain several step down or step up.

sub-circuits, each with its own voltage level requirement than

that supplied by the battery or an external supply (sometimes ISOLATING CONVERTERS:

higher or lower than the supply voltage, and possibly even Fly back converter - it operates like the buck-

negative voltage). Switched DC – DC converters offer a method boost converter.

to convert one level of voltage to other, thereby saving space Forward converter – Similar to fly back

instead of using multiple batteries to accomplish the same thing.

This work aims at designing a DC-DC Buck converter with input converter, but in contrast, there are two distinct

28V and regulated 5V DC as output. phases for energy storage and delivery to the

output, and the forward converter uses the

Keywords: DC-DC converter, Buck converter. transformer in a more traditional manner.

II. BUCK CONVERTER

I. INTRODUCTION

The buck converter is used for voltage step down /reduction.

A. DC to DC converters are important in portable electronic

devices such as cellular phones and laptop computers, A. Basic Circuit

telecommunication equipments, as well as DC motor

drives which are supplied with power from batteries

primarily.

The input to DC –DC converter is an unregulated DC

voltage. The converter produces a regulated output voltage,

having a magnitude (and possibly polarity) that differs

from the input voltage. High efficiency is invariably

required, since cooling of inefficient power convertersis

difficult and expensive. The ideal DC –DC converter Fig1: Basic Circuit

exhibits 100% efficiency; in practice, efficiencies of 70%-

95% are typically obtained. This is achieved using The switch position is varied periodically, such that vs( t) is

switched mode, or chopper circuits whose elements a rectangular waveform having period Ts and duty cycle . In

dissipate negligible power. Pulse width modulation ) practice, the SPDT switch is realized using semicondu ctor

(PWM allows control and regulation of the total outpute. devices such as diodes, power MOSFETs, IGBTs, BJTs , or

voltag This approach is also employed in applications g thyristors. The switch network changes the dc componen t of

involvin alternating current, including high efficiencyC the voltage. By Fourier analysis, the dc component of a

DC–A power converters (inverters and power - waveform is given by its average value. The average value of

amplifiers), AC AC power converters, and some AC-DC s vs(t) is given by

power converter (low harmonic rectifiers). t on

1

Vs = vs (t)dt

T s 0

B. CLASSIFICATION:

t on

= Vg = DVg

NON-ISOLATING CONVERTERS: Ts

Buck converter- steps down the voltage. Since 0<D<1, the dc component of Vs is less than or equal

Boost converter –steps up the voltage. to Vg.

ICCIT16 @ CiTech, Bengaluru doi : 10.17950/ijer/v5i5/025 Page 1105

International Journal of Engineering Research ISSN: 2319-6890)(online),2347-5013(print)

Volume No.5 Issue: Special 5, pp: 992-1128 20 May 2016

B. Realization of a Buck converter using MOSFET.

A. Principle of operation

Fig.2 illustrates one way to realize the switch

network in the buck converter, using a power MOSFET

and diode. A gate drive circuit switches the MOSFET

between the conducting (on) and blocking (off) states, as

commanded by a logic signal δ(t). When δ(t) is high (for

0<t<DTs), MOSFET Q1 conducts with negligible drain-

to-source voltage. Hence, vs(t) is approximately equal to

Vg, and the diode is reverse biased. The positive inductor

current i L(t) flows through the MOSFET. At time t=DTs,

δ(t) becomes low, commanding MOSFET Q1 to turn off.

The inductor current must continue to flow; hence, i L(t)

forward biases diode D1, and vs(t) is now approximately

equal to zero. Provided that the inductor current i L(t)

remains positive, diode D1 conducts for the remainder of

the switching period. Diodes that operate in this manner

are called freewheeling diodes. Since the converter output

voltage v(t) is a function of the switch duty cycle D, a

control system can be constructed that varies the duty Fig.2: control circuit for buck converter

cycle to cause the output voltage to follow a given

reference vr. Figure illustrates the block diagram of a

simple converter feedback system. The output voltage is

sensed using a voltage divider, and is compared with an

accurate dc reference voltage vr. The resulting error signal

is passed through an op-amp compensation network. The

analog voltage vc(t) is next fed into a pulse-width-

modulator. The modulator produces a switched voltage

waveform that is proportional to the control voltage vc(t).

If this control system is well designed, then the duty cycle

is automatically adjusted such that the converter output

voltage v follows the reference voltage vr, and is Fig.3: Pin diagram of SG3524

essentially independent of variations in vg or load current.

The SG3524 is a fixed-frequency pulse-width-

modulation (PWM) voltage-regulator control circuit. The

regulator operates at a fixed frequency that is programmed

III. DESIGN

by one timing resistor, RT, and one timing capacitor, CT.

We have, RT establishes a constant charging current for CT. While

∆I=Va (Vs-Va) / fLVs this uses more current than a series connected RC, it

∆Vc = Va(Vs-Va) / 8LCf² Vs provides a linear ramp voltage at CT which is used as a

Initial conditions: time dependent reference for the PWM comparator. The

Vs=28V charging current is equal to 3.6V/RT, and should be

Va=5V restricted to between 30mA and 2mA. The equivalent

Ripple voltage=50mV range for RT is 1.8k to 100k. The range of values for CT

Ripple current=10% of output current also has limits, as the discharge time of CT determines the

Output current=1A pulse width of the oscillator output pulse. The pulse is

Switching frequency=100 kHz used (among other things) as a blanking pulse to both

By substituting these values in the equations, we determine outputs to insure that there is no possibility of having both

the values of L and C. We get, L=410µH and C=2.5µF. outputs on simultaneously during transitions. A pulse

Control circuit for buck converter is as shown in Fig.2 width below 0.35us may cause failure of the internal flip

flop to toggle. This restricts the minimum value of CT to

1000pF. (Note: Although the oscillator output is a

convenient oscilloscope synchronous input, the probe

capacitance will increase the pulse width and decrease the

oscillator frequency slightly). Obviously, the upper limit to

the pulse width is determined by the modulation range

required in the power supply at the chosen switching

frequency. Practical values of CT fall between 1000pF and

0.1pF, although successful 120 Hz oscillators have been

implemented with values up to 5pF and a series surge limit

resistor of 100 ohms. The oscillator frequency is

ICCIT16 @ CiTech, Bengaluru doi : 10.17950/ijer/v5i5/025 Page 1106

International Journal of Engineering Research ISSN: 2319-6890)(online),2347-5013(print)

Volume No.5 Issue: Special 5, pp: 992-1128 20 May 2016

approximately 1/RT*CT; where R in ohms, C in µF and

frequency is in MHz. Note that for buck regulator IV.OBSERVATIONS

topologies, the two outputs can be wired for an effective Output voltage Vo is observed for different values of

0- 90% duty cycle range. With this connection, the output input voltage Vi and load resistance RL and the values

frequency is the same as the oscillator frequency. For are tabulated.

push-pull applications, the outputs are used separately; the

flip- flop limits the duty cycle range at each output to 0- RL=3.9kΩ Vi=28V

45%, and the effective switching frequency at the Vi (V) Vo (V)

transformer is ½ the oscillator frequency. If it is desired to

synchronize the SG3524 to an external clock, a positive 20 4.94

pulse may be applied to the clock pin. The oscillator 23.5 4.94

should be programmed with RT and CT values that cause 26.5 4.95

it to free run at 90% of the external sync frequency. A

sync pulse with a maximum logic zero of +0.3V and a 28 4.95

minimum logic 1 of +2.4V applied to pin 3 will lock the 30 4.95

oscillator to the external source. The minimum

synchronous pulse width should be 200ns, and the

maximum is determined by the required dead time. The RL (kΩ) Vo (V)

clock pin should never be driven more negative than -0.3V, 1 4.94

nor more positive than +5V. The nominal resistance to 2.2 4.95

ground is 3.2k at the clock pin, ± 25% over temperature. If

2.7 4.95

two or more SG3524 must be synchronized together,

program one master unit with RT and CT for the desired 3.9 4.95

frequency. Leave the RT pins on the slaves open, connect

the CT pins to the CT of the master, and connect the clock WAVEFORMS

pins to the clock pin of the master. Since CT is a high-

impedance node, this synchronous technique works best 1. Ramp waveform of CT at pin 7 of SG3524 with an

when all devices are close together. oscillating frequency of 200 kHz.

B. Estimation of RT and CT for the oscillating frequency of

200 kHz

Fig.4. Waveform across output capacitor

ICCIT16 @ CiTech, Bengaluru doi : 10.17950/ijer/v5i5/025 Page 1107

International Journal of Engineering Research ISSN: 2319-6890)(online),2347-5013(print)

Volume No.5 Issue: Special 5, pp: 992-1128 20 May 2016

Fig.5. Regulated DC

output

V. CONCLUSION

After obtaining experimental results, we see that

DC output voltage of 5V stepped down from 28V, is

obtained and the output is seen to be a regulated DC.

VI. ACKNOWLEDGEMENT

The authors would like to thank TEQIP II, MHRD

and BMS College of Engineering for the financial

support in the context of presented work.

VII. REFERENCES

[1] Ned Mohan, Tore M. Undeland, William P. Robbins, Power

Electronics: Converters, Applications and design, Student edition,

New York, John Wiley and sons.

[2] Muhammad H. Rashid, Power electronics: Circuits, Devices, and

Applications, Third edition, Pearson Education.

[3] S Salivahanan, V S KanchanaBhaaskaran, Linear Integrated

Circuits, Tata McGraw Hill Publications.

[4] Switched mode power supplies, NPTEL Course, Version 2 EE IIT,

Kharagpur.

[5] P. Chhawchharia; D. K. W. Cheng; Y. S. Lee, ―On the performance

improvement for design optimization of buck convertors‖, Power

Electronics and Drive Systems, 1997. Proceedings., 1997

International Conference

[6] www.wikepedia.com

[7] www.texasinstruments.com

[8] www.linearic.in

[9] www.in.mouser.com

ICCIT16 @ CiTech, Bengaluru doi : 10.17950/ijer/v5i4/060 Page 1108

Das könnte Ihnen auch gefallen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- 1997 UBC Vol 2Dokument501 Seiten1997 UBC Vol 2Ali KaroutNoch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Bewertung: 2.5 von 5 Sternen2.5/5 (3)

- STEM: Science, Technology, Engineering and Maths Principles Teachers Pack V10Von EverandSTEM: Science, Technology, Engineering and Maths Principles Teachers Pack V10Noch keine Bewertungen

- Introduction of CENTUM VP R6 RS R4 FullDokument98 SeitenIntroduction of CENTUM VP R6 RS R4 FullmohamedfaizykaNoch keine Bewertungen

- Buck ConverterDokument52 SeitenBuck Convertermayankrkl50% (2)

- 9 Basic DC To DC Converter CircuitsDokument40 Seiten9 Basic DC To DC Converter Circuitsuser123phc100% (1)

- Analog Circuit Design Volume Three: Design Note CollectionVon EverandAnalog Circuit Design Volume Three: Design Note CollectionBewertung: 3 von 5 Sternen3/5 (2)

- Buck ReportDokument9 SeitenBuck ReportNaeem GulNoch keine Bewertungen

- Voltage Stress in Power SystemsDokument29 SeitenVoltage Stress in Power Systemssorry2qazNoch keine Bewertungen

- Connecting To The Internet With Pico WDokument30 SeitenConnecting To The Internet With Pico WKnut BoergeNoch keine Bewertungen

- Ethics and RoboticsDokument13 SeitenEthics and Roboticspobeda8Noch keine Bewertungen

- Ansible For Real-Life Automation - Gineesh MadapparambathDokument893 SeitenAnsible For Real-Life Automation - Gineesh Madapparambathvijayendra0% (1)

- 1.1 Introduction To Buck ConverterDokument44 Seiten1.1 Introduction To Buck Converterapi-19810277Noch keine Bewertungen

- Power Electronics Applied to Industrial Systems and Transports, Volume 2: Power Converters and their ControlVon EverandPower Electronics Applied to Industrial Systems and Transports, Volume 2: Power Converters and their ControlBewertung: 5 von 5 Sternen5/5 (1)

- Two-Stage H-Bridge Transformer Coupled DC-DC Converter With Zero Voltage SwitchingDokument8 SeitenTwo-Stage H-Bridge Transformer Coupled DC-DC Converter With Zero Voltage SwitchingRakeshconclaveNoch keine Bewertungen

- Library - Management - Project Report by Vaishali & Sukhwinder Kaur BCA (3rd Yr.)Dokument64 SeitenLibrary - Management - Project Report by Vaishali & Sukhwinder Kaur BCA (3rd Yr.)Naveen SharmaNoch keine Bewertungen

- Design and Implementation of ZCS BUCK CONVERTERDokument51 SeitenDesign and Implementation of ZCS BUCK CONVERTERAriful Haque100% (1)

- 320D2L - Serie - Esg - Plano HidraulicoDokument10 Seiten320D2L - Serie - Esg - Plano HidraulicoJorge Calderon RojasNoch keine Bewertungen

- DC-DC Converters Lab ManualDokument32 SeitenDC-DC Converters Lab ManualShah SahadNoch keine Bewertungen

- Safety-enhanced-high-step-up-DC-DC-converter-for-ac-photovoltaic-module-applications Chapter 2 DC-DC Converters 12 PageDokument16 SeitenSafety-enhanced-high-step-up-DC-DC-converter-for-ac-photovoltaic-module-applications Chapter 2 DC-DC Converters 12 PageVenkatesh ChintalaNoch keine Bewertungen

- A Implementation of Single-Switch Nonisolated Transformerless Buck-Boost DC-DC ConverterDokument6 SeitenA Implementation of Single-Switch Nonisolated Transformerless Buck-Boost DC-DC ConverterKPCYP COHODNoch keine Bewertungen

- Lab Innovation Project DC DCDokument15 SeitenLab Innovation Project DC DCAyush MittalNoch keine Bewertungen

- Microcontroller Based DC-DC Cascode Buck-Boost Converter: Sanjeet Kumar Dr. Parsuram ThakuraDokument6 SeitenMicrocontroller Based DC-DC Cascode Buck-Boost Converter: Sanjeet Kumar Dr. Parsuram ThakuraNurhayatiNoch keine Bewertungen

- Ec1355 Esd EceDokument31 SeitenEc1355 Esd EceSenthil KumarNoch keine Bewertungen

- DC To DC Buck and Boost ConverterDokument5 SeitenDC To DC Buck and Boost ConverterR ABHISHEKNoch keine Bewertungen

- DC-DC Converters PDFDokument7 SeitenDC-DC Converters PDFRidaNoch keine Bewertungen

- Analysis and Construction of Push Pull Converter - Noor Rulmuna Bt. Mohd Sarmin - TK7872.C8.N66 2006Dokument27 SeitenAnalysis and Construction of Push Pull Converter - Noor Rulmuna Bt. Mohd Sarmin - TK7872.C8.N66 2006Rizwan FaizNoch keine Bewertungen

- Zeta Converter PidDokument7 SeitenZeta Converter Pidvenkateswarlu chamalaNoch keine Bewertungen

- Comparative Analysis of MPPT Based Solar Charge ControllerDokument7 SeitenComparative Analysis of MPPT Based Solar Charge ControllerMechanical Robot Designers V CreationsNoch keine Bewertungen

- Lab Experiment - Introduction To Switch Mode Power SupplyDokument9 SeitenLab Experiment - Introduction To Switch Mode Power SupplyChris ManahanNoch keine Bewertungen

- Buck RegulatorDokument6 SeitenBuck RegulatorBhukya Reethvik RathodNoch keine Bewertungen

- Boost ConvertersDokument4 SeitenBoost ConvertersSyed Mohammad FarooqueNoch keine Bewertungen

- Current Mirror 1Dokument5 SeitenCurrent Mirror 1Shaheer DurraniNoch keine Bewertungen

- Design of Transformer-Less DC To AC Converter Using PWM TechniqueDokument6 SeitenDesign of Transformer-Less DC To AC Converter Using PWM TechniqueHariesh WaranNoch keine Bewertungen

- Final ReviewDokument19 SeitenFinal ReviewSanyam JainNoch keine Bewertungen

- Analysis of Buck Converter and Simulating It For Different Switching Frequencies and Different Power DevicesDokument6 SeitenAnalysis of Buck Converter and Simulating It For Different Switching Frequencies and Different Power DevicesPrema Vinod PatilNoch keine Bewertungen

- Switching Regulator Fundamentals: Application ReportDokument28 SeitenSwitching Regulator Fundamentals: Application Reportbookreader1968Noch keine Bewertungen

- Traiki2018 FormulaDokument6 SeitenTraiki2018 FormulaTamilselvanNoch keine Bewertungen

- Bee4223:Power Electronics and Drive SystemsDokument7 SeitenBee4223:Power Electronics and Drive SystemsChiam Tat MingNoch keine Bewertungen

- Transformer Based Resonant DC Inverter For Brushless DC Motor Drive SystemDokument7 SeitenTransformer Based Resonant DC Inverter For Brushless DC Motor Drive SystemStudents Xerox ChidambaramNoch keine Bewertungen

- Renewable Energy Based On Current Fed Switched Inverter For Smart Grid ApplicationDokument3 SeitenRenewable Energy Based On Current Fed Switched Inverter For Smart Grid ApplicationiirNoch keine Bewertungen

- Z Source ConverterDokument12 SeitenZ Source Converterravirnjn88Noch keine Bewertungen

- 135264ijsetr6989 1453Dokument8 Seiten135264ijsetr6989 1453wasabikikkomanNoch keine Bewertungen

- Design and Construction of A Low DC Voltage Power Supply UnitDokument28 SeitenDesign and Construction of A Low DC Voltage Power Supply UnitRasaq Eneji Jimoh100% (1)

- A Single-Phase Isolated Z-Source Inverter: Swetadri Ghosh, Koustuv Sarkar, Dipten Maiti, Sujit K. BiswasDokument4 SeitenA Single-Phase Isolated Z-Source Inverter: Swetadri Ghosh, Koustuv Sarkar, Dipten Maiti, Sujit K. BiswassaiNoch keine Bewertungen

- Comparative Performance Analysis of Boost Converter and Luo Converter For Controllinng of DC Motor SpeedDokument8 SeitenComparative Performance Analysis of Boost Converter and Luo Converter For Controllinng of DC Motor SpeedguruvigneshnzNoch keine Bewertungen

- Shyam Course ProjectDokument6 SeitenShyam Course ProjectBhukya Reethvik RathodNoch keine Bewertungen

- Design and Simulation of DC-DC Converter Used in Solar Charge ControllersDokument4 SeitenDesign and Simulation of DC-DC Converter Used in Solar Charge ControllersInternational Journal of Engineering Inventions (IJEI)Noch keine Bewertungen

- 20977-Article Text-63774-1-10-20180626Dokument8 Seiten20977-Article Text-63774-1-10-20180626gürcan EserNoch keine Bewertungen

- Switched Inductor Based Quadratic ConverterDokument6 SeitenSwitched Inductor Based Quadratic ConverterInternational Journal of Innovative Science and Research TechnologyNoch keine Bewertungen

- 고전압비와 낮은 전압 스트레스를 가진 단일 스위치와 전압 체배 회로를 이용한 새로운 비절연형 DC-DC 컨버터Dokument5 Seiten고전압비와 낮은 전압 스트레스를 가진 단일 스위치와 전압 체배 회로를 이용한 새로운 비절연형 DC-DC 컨버터Armandinho CaveroNoch keine Bewertungen

- Simulation and Prototype Implementation of Phase Shift Full Bridge DC DC ConverterDokument4 SeitenSimulation and Prototype Implementation of Phase Shift Full Bridge DC DC ConverterjimmyNoch keine Bewertungen

- Buck BoostDokument11 SeitenBuck Boostkima lachgarNoch keine Bewertungen

- IAETSD-JARAS High Gain Ratio Hybrid Transformer Based On DC-DC Converter For PV Grid ApplicationsDokument6 SeitenIAETSD-JARAS High Gain Ratio Hybrid Transformer Based On DC-DC Converter For PV Grid ApplicationsiaetsdiaetsdNoch keine Bewertungen

- A DC-DC Converter With High Voltage Gain and Two Input Boost StagesDokument10 SeitenA DC-DC Converter With High Voltage Gain and Two Input Boost Stagesnadeemq_0786Noch keine Bewertungen

- Single Phase Single Stage Bidirectional Isolated Zvs Acdc With PFCDokument8 SeitenSingle Phase Single Stage Bidirectional Isolated Zvs Acdc With PFCSamyak ParakhNoch keine Bewertungen

- Implementation of Single Stage Three Level Power Factor Correction AC-DC Converter With Phase Shift ModulationDokument6 SeitenImplementation of Single Stage Three Level Power Factor Correction AC-DC Converter With Phase Shift ModulationseventhsensegroupNoch keine Bewertungen

- Intersil Basics Dec2011Dokument3 SeitenIntersil Basics Dec2011Marius BarNoch keine Bewertungen

- Improved Step Down Conversion in Interleaved Buck Converter and Low Switching LossesDokument10 SeitenImproved Step Down Conversion in Interleaved Buck Converter and Low Switching LossesinventyNoch keine Bewertungen

- DC-DC Konverter Basic DesignDokument16 SeitenDC-DC Konverter Basic DesignTaufik InsaniNoch keine Bewertungen

- Power Electronics NotesDokument2 SeitenPower Electronics Notesprasad357Noch keine Bewertungen

- Application of Soft-Switching in Domestic Solar Power SystemDokument4 SeitenApplication of Soft-Switching in Domestic Solar Power SystemTrần HuyNoch keine Bewertungen

- Series-Connected DC-DC Power Converters For Low-Voltage DC Source in Distributed GenerationDokument6 SeitenSeries-Connected DC-DC Power Converters For Low-Voltage DC Source in Distributed GenerationnaumanaliNoch keine Bewertungen

- A Step Down Transformerless Single Switch Integerated Buck and Buck-Boost ConverterDokument7 SeitenA Step Down Transformerless Single Switch Integerated Buck and Buck-Boost ConverterMogal RajeshNoch keine Bewertungen

- 2002apr08 Icd Amd Pow TacDokument9 Seiten2002apr08 Icd Amd Pow TacMihaela CaciumarciucNoch keine Bewertungen

- CATALOG 2017 (Branch-Wise)Dokument33 SeitenCATALOG 2017 (Branch-Wise)RajeevSangamNoch keine Bewertungen

- Airbus Peter Sander The Future of Alm 3d Printing Airbus Innovation Days 2016Dokument10 SeitenAirbus Peter Sander The Future of Alm 3d Printing Airbus Innovation Days 2016Хардип ЗинтаNoch keine Bewertungen

- Hospital Equipment and Its Management System A MinDokument4 SeitenHospital Equipment and Its Management System A MinPaola LorenzattoNoch keine Bewertungen

- Comsol PricelistDokument4 SeitenComsol PricelistKalipada SenNoch keine Bewertungen

- Pioneer PLX 500kDokument15 SeitenPioneer PLX 500kFabiNoch keine Bewertungen

- 1 Question Bank For Unit 1Dokument11 Seiten1 Question Bank For Unit 1Ajay KareNoch keine Bewertungen

- Group 2 SpecificationsDokument13 SeitenGroup 2 SpecificationsАлексейNoch keine Bewertungen

- MANDATORYDokument7 SeitenMANDATORYkamlesh yadavNoch keine Bewertungen

- CareerCentre Resume and Cover Letter Toolkit - UofTDokument32 SeitenCareerCentre Resume and Cover Letter Toolkit - UofTMallikaShakyaNoch keine Bewertungen

- VMware GPM 02 PDFDokument42 SeitenVMware GPM 02 PDFHai HoangNoch keine Bewertungen

- Computer Science Project On Snake and Ladder GameDokument17 SeitenComputer Science Project On Snake and Ladder GameAdarsh GodiyalNoch keine Bewertungen

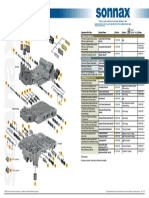

- Aisin AW TF-81SC: Click On Part Numbers For Product Details or VisitDokument1 SeiteAisin AW TF-81SC: Click On Part Numbers For Product Details or Visittejonmx100% (1)

- Case Study NasariaDokument20 SeitenCase Study NasariaHarsh SinhaNoch keine Bewertungen

- Digital Circuit Design TrendsDokument5 SeitenDigital Circuit Design TrendsnagarajuNoch keine Bewertungen

- Generator Protection - 7UM85 - Technical DataDokument42 SeitenGenerator Protection - 7UM85 - Technical DataDoan Anh TuanNoch keine Bewertungen

- Colortrac S4e Service Manual-2Dokument66 SeitenColortrac S4e Service Manual-2hany_elbanna2000100% (1)

- Safety Manual (B-80687EN 10)Dokument35 SeitenSafety Manual (B-80687EN 10)Jander Luiz TomaziNoch keine Bewertungen

- Application Whitelisting: Approaches and ChallengesDokument6 SeitenApplication Whitelisting: Approaches and ChallengesijcseitjournalNoch keine Bewertungen

- Week3 Modulation BasicsDokument30 SeitenWeek3 Modulation BasicsAbdulrahman AlsomaliNoch keine Bewertungen

- Mathsoft Group 1 BBMDokument7 SeitenMathsoft Group 1 BBMBrandon DeanNoch keine Bewertungen

- Using Avaya Health Check ToolDokument24 SeitenUsing Avaya Health Check ToolkokostNoch keine Bewertungen

- Sap Erp Financials Configuration and Design 2nd Ed 59c5c66e1723dd42ad224565Dokument1 SeiteSap Erp Financials Configuration and Design 2nd Ed 59c5c66e1723dd42ad224565VManiKishoreNoch keine Bewertungen