Beruflich Dokumente

Kultur Dokumente

Wa0004 PDF

Hochgeladen von

Jochum0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

27 Ansichten2 SeitenOriginaltitel

DOC-20190418-WA0004.pdf

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

27 Ansichten2 SeitenWa0004 PDF

Hochgeladen von

JochumCopyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 2

MODULE 3

SIGNED AND UNSIGNED INSTRUCTIONS

A binary number may be signed or unsigned. The MIPS architecture uses two’s

complement representation of signed numbers. MIPS has certain instructions that

come in signed and unsigned flavors, including addition and subtraction,

multiplication and division, set less than, and partial word loads.

1. Addition and Subtraction

Addition and subtraction are performed identically whether the number is signed

or unsigned. However, the interpretation of the results is different.

If two large signed numbers are added together, the result may incorrectly

produce the opposite sign. This is called arithmetic overflow. The MIPS processor

takes an exception on arithmetic overflow. The program can decide what to do

about the overflow, then return to where it left off.

MIPS provides signed and unsigned versions of addition and subtraction. The

signed versions are add, addi, and sub. The unsigned versions are addu, addiu,

and subu. The two versions are identical except that signed versions trigger an

exception on overflow, whereas unsigned versions do not.

2. Multiplication and Division

Multiplication and division behave differently for signed and unsigned numbers.

For example, as an unsigned number, 0xFFFFFFFF represents a large number,

but as a signed number, it represents -1. Therefore, multiplication and division

come in both signed and unsigned flavors. mult and div treat the operands as

signed numbers. multu and divu treat the operands as unsigned numbers.

3. Set Less Than

Set less than instructions can compare either two registers (slt) or a register and

an immediate (slti). Set less than also comes in signed (slt and slti) and unsigned

(sltu and sltiu) versions. In a signed comparison, 0x80000000 is less than any

other number, because it is the most negative two’s complement number. In an

unsigned comparison, 0x80000000 is greater than 0x7FFFFFFF but less than

0x80000001, because all numbers are positive.

4. Loads

Byte load instructions come in signed (lb) and unsigned (lbu) versions. lb sign-

extends and lbu zero-extends the byte to fill the entire 32-bit register. Similarly,

MIPS provides signed and unsigned half-word loads (lh and lhu), which load two

bytes into the lower half and sign or zero-extend the upper half of the word.

FLOATING POINT INSTRUCTIONS

The MIPS architecture defines an optional floating-point coprocessor, known as

coprocessor 1. In early MIPS implementations, the coprocessor was a separate

chip that users could purchase if they needed fast floating-point math. In most

recent MIPS implementations, the floating-point coprocessor is built in alongside

the main processor.

MIPS defines 32 floating-point registers of 32 bit size, $f0–$f31. These are

separate from the ordinary registers used so far. MIPS supports both single and

double-precision IEEE floating point arithmetic. Double precision (64-bit)

numbers are stored in pairs of 32-bit registers. By convention, certain registers

are reserved for certain purposes, as given in table below.

Floating-point instructions all have an opcode of 17 (100012). They require both

a funct field and a cop (coprocessor) field to indicate the type of instruction.

Hence, MIPS defines the F-type instruction format for floating-point instructions,

shown in Figure below.

Floating-point instructions come in both single and double-precision flavors. The

section cop = 16 (100002) for single-precision instructions or 17 (100012) for

double precision instructions. F-type instructions have two source operands, fs

and ft, and one destination, fd.

Floating-point arithmetic instructions include addition (add.s, add.d), subtraction

(sub.s, sub.d), multiplication (mul.s, mul.d), and division (div.s, div.d) as well as

negation (neg.s, neg.d) and absolute value (abs.s, abs.d).

Note: Including .s or .d in the mnemonic is to indicate instruction precision. i.e.

add.s is a single precision instruction while add.d is a double precision instruction.

Floating-point branches have two parts. First, a compare instruction is used to

set or clear the floating-point condition flag (fpcond). Then, a conditional branch

checks the value of the flag. The compare instructions include equality, less than,

and less than/equal to. The conditional branch instructions are bc1f and bc1t that

branch if fpcond is FALSE or TRUE, respectively.

Floating-point registers are loaded and stored from memory using lwc1 and swc1.

These instructions move 32 bits, so two are necessary to handle a double-

precision number.

Das könnte Ihnen auch gefallen

- MicroStrategy Quick Start Guide (Fernando Carlos Rivero Esqueda)Dokument319 SeitenMicroStrategy Quick Start Guide (Fernando Carlos Rivero Esqueda)nosic60451Noch keine Bewertungen

- The Complete Guide To Using Arrays in Excel VBADokument26 SeitenThe Complete Guide To Using Arrays in Excel VBAHemalatha S KumarNoch keine Bewertungen

- Block DiagramDokument1 SeiteBlock DiagramDimaz Hanggoro0% (2)

- 6.7.1 Description of LTE972: Flexi Baseband Module FBBADokument6 Seiten6.7.1 Description of LTE972: Flexi Baseband Module FBBAАндрей МоисеевNoch keine Bewertungen

- PLI Basic Training Using VSAM, IMS and DB2Von EverandPLI Basic Training Using VSAM, IMS and DB2Bewertung: 1 von 5 Sternen1/5 (1)

- Emerging Trends in Electronics MCQ PDF: Question BankDokument42 SeitenEmerging Trends in Electronics MCQ PDF: Question BankHarshad Bhong43% (7)

- VMware Microsegmentation Solution OverviewDokument2 SeitenVMware Microsegmentation Solution Overviewa bNoch keine Bewertungen

- IEC 61131 Standard Assignment #1Dokument54 SeitenIEC 61131 Standard Assignment #1naranbaatar_bNoch keine Bewertungen

- SCSP SNIA Certified Storage Professional TBRDokument582 SeitenSCSP SNIA Certified Storage Professional TBRkunal100% (1)

- Modern Introduction to Object Oriented Programming for Prospective DevelopersVon EverandModern Introduction to Object Oriented Programming for Prospective DevelopersNoch keine Bewertungen

- Question and KeyDokument12 SeitenQuestion and KeykevingladsonNoch keine Bewertungen

- Microprocessors Lecture 4 - NewDokument5 SeitenMicroprocessors Lecture 4 - NewAriane Faye SalongaNoch keine Bewertungen

- Mplabx Data TypeDokument16 SeitenMplabx Data TypeindustrialmechatechNoch keine Bewertungen

- SIC MACHINE ARCHITECTURE SUGANYA KEERTHANADokument47 SeitenSIC MACHINE ARCHITECTURE SUGANYA KEERTHANAsivayagNoch keine Bewertungen

- Lec06 1Dokument19 SeitenLec06 1tanyapahwaNoch keine Bewertungen

- Computer Architecture Lab 06Dokument8 SeitenComputer Architecture Lab 06Itz Sami UddinNoch keine Bewertungen

- MIPS AssemblyInstruction FormatsDokument5 SeitenMIPS AssemblyInstruction Formatsfeezy1100% (1)

- Syssoft 1Dokument19 SeitenSyssoft 1api-3826913Noch keine Bewertungen

- Explain FLYNN Classification With Suitable ExamplesDokument7 SeitenExplain FLYNN Classification With Suitable Examplesjishupanja33Noch keine Bewertungen

- Csci 260 Study Guide-5Dokument10 SeitenCsci 260 Study Guide-5zubayerthewizardNoch keine Bewertungen

- PIC Simulator IDE GuideDokument4 SeitenPIC Simulator IDE GuideManzo SicatNoch keine Bewertungen

- General Instruction FormatDokument6 SeitenGeneral Instruction Formatapi-19967001Noch keine Bewertungen

- ALU and Logic InstructionsDokument47 SeitenALU and Logic InstructionsDawit TesfayeNoch keine Bewertungen

- Assembly - Registers Assembly - RegistersDokument5 SeitenAssembly - Registers Assembly - RegistersHenry ChipindaNoch keine Bewertungen

- 07 68000 Instruction SetDokument13 Seiten07 68000 Instruction SetYassine BouaichiNoch keine Bewertungen

- Coa Rest NotesDokument24 SeitenCoa Rest NotesAyush NayakNoch keine Bewertungen

- MM Module2 Cse NotesDokument54 SeitenMM Module2 Cse NotesNaveen NNoch keine Bewertungen

- Multiplication and Division OverviewDokument38 SeitenMultiplication and Division OverviewShanjida JimNoch keine Bewertungen

- 8086 Register Organization (IMPDokument6 Seiten8086 Register Organization (IMPSukanti PalNoch keine Bewertungen

- MIPS Instruction Coding With HexDokument4 SeitenMIPS Instruction Coding With HexMichael van der WerveNoch keine Bewertungen

- Standard Basic Language ElementsDokument19 SeitenStandard Basic Language ElementsGerzain Cruz Lila100% (1)

- MIPS Instruction SetDokument7 SeitenMIPS Instruction Setsreenidhi sarmaNoch keine Bewertungen

- Addressing ModesDokument6 SeitenAddressing ModesabinayamalathyNoch keine Bewertungen

- Registri TriDokument4 SeitenRegistri TriNenad FemicNoch keine Bewertungen

- Instructions: Assembly Language: 2.1 Instructions and Instruction SetDokument5 SeitenInstructions: Assembly Language: 2.1 Instructions and Instruction SetRoberto Jr VelascoNoch keine Bewertungen

- The Processor Unit (Cpu) : By: Solomon SDokument50 SeitenThe Processor Unit (Cpu) : By: Solomon SAmanuelNoch keine Bewertungen

- Computer Architecture Instruction Set GuideDokument65 SeitenComputer Architecture Instruction Set GuideHexy ManucianNoch keine Bewertungen

- Chap - 4 MPDokument59 SeitenChap - 4 MPAraarsoo JaallataaNoch keine Bewertungen

- CPU Organization – Hardware design Vs. MicroprogrammingDokument105 SeitenCPU Organization – Hardware design Vs. Microprogrammingridersonthestorm1Noch keine Bewertungen

- Processor RegistersDokument6 SeitenProcessor Registersirinaasdf12Noch keine Bewertungen

- Microproccessor NOTESDokument55 SeitenMicroproccessor NOTESharshitharaghuramNoch keine Bewertungen

- 2a. CS602 Microprocessor and Microcontroller - SoftwareDokument44 Seiten2a. CS602 Microprocessor and Microcontroller - SoftwareRehan NightNoch keine Bewertungen

- System Software Unit 1Dokument14 SeitenSystem Software Unit 1TAJCHISHTINoch keine Bewertungen

- STUDY OF 8086/8088: Assembler Is An Intermediate Program, Which Converts AssemblyDokument15 SeitenSTUDY OF 8086/8088: Assembler Is An Intermediate Program, Which Converts AssemblyShashank SoodNoch keine Bewertungen

- ALU and MAC NotesDokument36 SeitenALU and MAC NotesMajerry Pierre-AntoineNoch keine Bewertungen

- Department of Information and Communication Technology Course: ICT-3205: Computer Architecture and MicroprocessorDokument12 SeitenDepartment of Information and Communication Technology Course: ICT-3205: Computer Architecture and MicroprocessorBashar AhmedNoch keine Bewertungen

- Chapter 5 Description of Function InstructionsDokument14 SeitenChapter 5 Description of Function Instructionsm_abubakarqureshiNoch keine Bewertungen

- COE301 Lab 2 Introduction MIPS AssemblyDokument7 SeitenCOE301 Lab 2 Introduction MIPS AssemblyItz Sami UddinNoch keine Bewertungen

- Addressing Mode General Meaning: RegisterDokument27 SeitenAddressing Mode General Meaning: RegisterkNoch keine Bewertungen

- CMPS290 Class Notes (Chap02) - Understanding Computer Instructions and Data RepresentationDokument45 SeitenCMPS290 Class Notes (Chap02) - Understanding Computer Instructions and Data RepresentationzeeshanNoch keine Bewertungen

- ECE 485 Computer Organization and Design: D I Mips CPU M DDokument32 SeitenECE 485 Computer Organization and Design: D I Mips CPU M DAkhila kommireddyNoch keine Bewertungen

- Computer Organization & Assembly Language: Lab Manual 5Dokument8 SeitenComputer Organization & Assembly Language: Lab Manual 5Psyco PathNoch keine Bewertungen

- Memory Addressing and Instruction FormatsDokument9 SeitenMemory Addressing and Instruction Formatsrobern ndoloNoch keine Bewertungen

- Comparing Registers: MIPS vs. ARM AssemblyDokument12 SeitenComparing Registers: MIPS vs. ARM Assemblyshruti chouhanNoch keine Bewertungen

- System Software NotesDokument104 SeitenSystem Software NotesVishal PatelNoch keine Bewertungen

- Assignment-1: Software TechnologyDokument4 SeitenAssignment-1: Software TechnologySwarnim ShuklaNoch keine Bewertungen

- Instruction Formats ExplainedDokument5 SeitenInstruction Formats ExplainedPragya SinghNoch keine Bewertungen

- Chapter 2 PDFDokument18 SeitenChapter 2 PDFKrishna ChaitanyaNoch keine Bewertungen

- Sheet MicorDokument42 SeitenSheet MicorFiras TaherNoch keine Bewertungen

- 1 MIPSfeaturesDokument5 Seiten1 MIPSfeaturesArvind Krishnaa JNoch keine Bewertungen

- Overview of Assembly LanguageDokument4 SeitenOverview of Assembly LanguageFaisalMajeedNoch keine Bewertungen

- Computer Architecture: Register Transfer & Micro-OperationsDokument24 SeitenComputer Architecture: Register Transfer & Micro-OperationsDipak SharmaNoch keine Bewertungen

- Computer Architecture: Register Transfer & Micro-OperationsDokument24 SeitenComputer Architecture: Register Transfer & Micro-OperationsDipak SharmaNoch keine Bewertungen

- MIPS Assembly Code for Loops and DecisionsDokument10 SeitenMIPS Assembly Code for Loops and DecisionszubayerthewizardNoch keine Bewertungen

- Lec 3 PDFDokument11 SeitenLec 3 PDFAbdullah AliNoch keine Bewertungen

- Fixed Versus Floating PointDokument5 SeitenFixed Versus Floating PointAnil AgarwalNoch keine Bewertungen

- MP Instruction SetDokument15 SeitenMP Instruction SetKannan MuthusamyNoch keine Bewertungen

- Life SkillsDokument2 SeitenLife SkillsJochumNoch keine Bewertungen

- Mechanical Engineering PDFDokument2 SeitenMechanical Engineering PDFMohammed Asif NNoch keine Bewertungen

- Wa0001Dokument1 SeiteWa0001JochumNoch keine Bewertungen

- I/O System Standards: Serial, Parallel, PCI, SCSI, USBDokument10 SeitenI/O System Standards: Serial, Parallel, PCI, SCSI, USBJochumNoch keine Bewertungen

- MIPS Signed and Unsigned InstructionsDokument2 SeitenMIPS Signed and Unsigned InstructionsJochumNoch keine Bewertungen

- A Simple PDFDokument2 SeitenA Simple PDFJaheer MakalNoch keine Bewertungen

- Electrical EngineeringDokument22 SeitenElectrical EngineeringJochumNoch keine Bewertungen

- Wa0003Dokument5 SeitenWa0003JochumNoch keine Bewertungen

- Wa0003Dokument5 SeitenWa0003JochumNoch keine Bewertungen

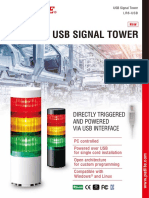

- Lr6 Usb Signal Tower: Directly Triggered and Powered Via Usb InterfaceDokument2 SeitenLr6 Usb Signal Tower: Directly Triggered and Powered Via Usb InterfaceHajnal GorgenyiNoch keine Bewertungen

- Jessore Felicity BigData Data Center Solution - V1.0Dokument19 SeitenJessore Felicity BigData Data Center Solution - V1.0Muhtadin IqbalNoch keine Bewertungen

- Controls For Information SecurityDokument14 SeitenControls For Information Securitymuhammad f laitupaNoch keine Bewertungen

- Screenshot 2023-12-06 at 8.31.50 PMDokument30 SeitenScreenshot 2023-12-06 at 8.31.50 PMgj7cpz4fzyNoch keine Bewertungen

- Protect any cellular device and organization from mobile network threatsDokument2 SeitenProtect any cellular device and organization from mobile network threatswaiphyo 49Noch keine Bewertungen

- VMC 8609adpDokument49 SeitenVMC 8609adpSanjeev KumarNoch keine Bewertungen

- Classes of Computers: Analog Computer Digital Computer Hybrid ComputerDokument23 SeitenClasses of Computers: Analog Computer Digital Computer Hybrid ComputerEuscelle Grace LimenNoch keine Bewertungen

- Fiber To The DeskDokument7 SeitenFiber To The DesknabillyusofNoch keine Bewertungen

- Openbts SWDokument37 SeitenOpenbts SWrampravesh kumarNoch keine Bewertungen

- BSC (Hons) Web TechnologiesDokument17 SeitenBSC (Hons) Web TechnologiesRoubin DhallapahNoch keine Bewertungen

- VPLEX 4.0 Installation and Setup GuideDokument114 SeitenVPLEX 4.0 Installation and Setup GuideSujit FrancisNoch keine Bewertungen

- Professional Cloud Network EngineerDokument5 SeitenProfessional Cloud Network EngineerMillionn GizawNoch keine Bewertungen

- Hard Disk Block Size Advantages and DisadvantagesDokument3 SeitenHard Disk Block Size Advantages and DisadvantagessrikanthNoch keine Bewertungen

- CPP Vs JavaDokument5 SeitenCPP Vs Javadasoundofreason1065Noch keine Bewertungen

- 1ADokument7 Seiten1APedro RodriguezNoch keine Bewertungen

- Unit4 AssignmentDokument4 SeitenUnit4 AssignmentChris TrimbleNoch keine Bewertungen

- Document Title: Specification of Diagnostics Event ManagerDokument176 SeitenDocument Title: Specification of Diagnostics Event ManageryuvarajnarayanasamyNoch keine Bewertungen

- Bta06 600CDokument7 SeitenBta06 600Cdozer_kamilNoch keine Bewertungen

- Amazon Aws ListDokument40 SeitenAmazon Aws ListHarshal GunjalNoch keine Bewertungen

- 03 Assembler (UPDATED)Dokument12 Seiten03 Assembler (UPDATED)Saurabh100% (1)

- DSE808 Data Sheet PDFDokument2 SeitenDSE808 Data Sheet PDFYuri Da Gama SantosNoch keine Bewertungen

- Unit 8 Structure and UnionDokument15 SeitenUnit 8 Structure and UnionWicked SaZzNoch keine Bewertungen