Beruflich Dokumente

Kultur Dokumente

Module 4 Ktunotes - in Min

Hochgeladen von

JamieOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Module 4 Ktunotes - in Min

Hochgeladen von

JamieCopyright:

Verfügbare Formate

EC206 Computer Organizations Module 4

MICROARCHITECTURES

Architecture:- Specifies the programmer’s view of the processor in terms of registers,

instructions and memory.

Example- MIPS architecture, IA 32 architecture

Microarchitecture:- Connection between logic and architecture.

It is the specific arrangement of registers, ALUs, Finite state machine (FSM),

memories and other logic building blocks needed to implement architecture.

• Any architecture can have different microarchitectures each with different

performance, cost and complexity.

Different microarchitectures of MIPS architecture

1. √ Single cycle microarchitecture

- All operations (fetch, decode, execute, write back) are performed in a single

clock cycle

- The instruction which need longest time decide the clock frequency

2. √ Multi cycle microarchitecture

- All operations(fetch, decode, execute, write back) are performed in a multiple

clock cycle

- Each instruction takes different number of clocks.

3. Pipelined microarchitecture

ES . I N

- Fetching of next instruction while decoding current instruction and executing

previous instruction.

N O T

KTU

Prepared by Susan Varghese, Asst. Prof, Dept of ECE Page 1

To get more study materails visit www.ktunotes.in

EC206 Computer Organizations Module 4

State elements of MIPS processor - A computer is just a big fancy state machine.

Registers and memory form the states and the processor keeps reading and

updating the state, according to the instructions in some program.

CONTROL Collection of state elements and their interconnection in a

processor is called Datapath (or EU or DPU)

Current Next

The control unit interprets the instruction and produces

state state

the control signals in proper sequence to carry out the

STATE operation.

1. Architectural state – consists of Program Counter (PC) and the 32 register set

2. Instruction memory

3. Data memory

4. Non architectural states –additional set of registers and circuits to either simplify

the logic or improve the performance

eg:- additional registers in multi cycle microarchitecture

ES . I N

N O T

KTU

- We can read from two registers at same time called 2 port memory

- RegWrite should be 1 for a register write operation.

Topics in 4th module - Performance analysis and Design process of single cycle and multi

cycle microarchitecture

Prepared by Susan Varghese, Asst. Prof, Dept of ECE Page 2

To get more study materails visit www.ktunotes.in

EC206 Computer Organizations Module 4

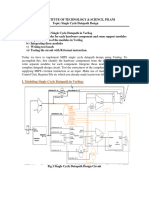

Design of single cycle microarchitecture Datapath for

1. Datapath for Instruction fetching

- The CPU is always in an infinite loop, fetching instructions from memory and

executing them.

- The program counter or PC register holds the address of the current instruction.

- MIPS instructions are each four bytes long, so the PC should be incremented by

four to read the next instruction in sequence.

2. Datapath for R type instruction

- Register-to-register arithmetic instructions use the R-type format.

-

. I N

R-type instructions must access registers and an ALU.

ES

-

long.

N O T

Ther is thirty two 32-bits registers and each register specifier (address) is 5 bits

-

- KTU

We can read from two registers at time called 2 port memoy

RegWrite should be 1 for a register write operation.

Datapath for R type Instruction

3. Datapath for I type instruction (lw, sw - Base addressing mode)

Prepared by Susan Varghese, Asst. Prof, Dept of ECE Page 3

To get more study materails visit www.ktunotes.in

EC206 Computer Organizations Module 4

The lw, sw and beq instructions all use the I-type encoding.

- rt is the destination for lw, but a source for beq and sw.

- Address is a 16-bit signed constant.

- For an instruction like lw $t0, –4($sp), the base register $sp is added to the sign-

extended constant to get a data memory address.

- This means the ALU must accept either a register operand for arithmetic

instructions or a sign-extended immediate operand for lw and sw.

- We’ll add a multiplexer, controlled by ALUSrc (ALU source), to select either a

register operand (0) or a constant operand (1).

ES . I N

N O T

KTU

4. Datapath for I type instruction (beq – PC relative addressing mode)

Prepared by Susan Varghese, Asst. Prof, Dept of ECE Page 4

To get more study materails visit www.ktunotes.in

EC206 Computer Organizations Module 4

- For branch instructions, the constant is not an address but an instruction offset (or

word offset) from the next program counter to the desired address.

- The target address L is three instructions past the first add, so the encoding of the

branch instruction has 0000 0000 0000 0011 for the address field.

- Instructions are four bytes long, so the actual memory offset is 12 bytes.

The steps in executing a beq

1. Fetch the instruction, like beq $at, $0, offset, from memory.

2. Read the source registers, $at and $0, from the register file.

3. Compare the values by subtracting them in the ALU.

4. If the subtraction result is 0, the source operands were equal and the PC should be

loaded with the target address, PC + 4 + (offset x 4). Zero flag will set to 1 if the

result is zero. Zero flag is going as input to the control unit to take the decision.

S . N

5. Otherwise the branch should not be taken, and the PC should just be incremented to

I

PC + 4 to fetch the next instruction sequentially.

E

N O T

KTU

Design of single cycle microarchitecture Control unit

Prepared by Susan Varghese, Asst. Prof, Dept of ECE Page 5

To get more study materails visit www.ktunotes.in

EC206 Computer Organizations Module 4

The control unit is responsible for setting all the control signals so that each

instruction is executed properly.

Generating control signals

• The entire 32 instruction bits are not needed for the control unit to generate control

signals.

• Most of the signals can be generated from the instruction opcode alone.

• The control unit needs 13 bits of inputs.

Six bits make up the instruction’s opcode.

Six bits come from the instruction’s func field.

It also needs the Zero flag of the ALU.

The figure below shows the final Datapath of single cycle microarchitecture. There are

about 8 control signals, RegDst, RegWrite, ALUSrc, ALUControl, MemWrite, MemRead,

PCSrc, MemToReg.

ES . I N

N O T

KTU

The control unit producing the control signals for this datapath can be built by

combinational and sequential circuit design.

Design of Control unit for R Type Instructions (single cycle)

Prepared by Susan Varghese, Asst. Prof, Dept of ECE Page 6

To get more study materails visit www.ktunotes.in

EC206 Computer Organizations Module 4

Instructi

Control Signals

on RegDst ALUSrc MemtoReg RegWrite MemRead MemWrite Branch ALUOp

C8 C7 C6 C5 C4 C3 C2 C 1C 0

R-Type 1 0 0 1 x x 0 10

Inputs (Opcode field in the instruction) Outputs (control signals)

Inst31 Inst30 Inst29 Inst28 Inst27 Inst26 C8 C7 C6 C5 C4 C3 C2 C1 C0

0 0 0 0 0 0 1 0 0 1 x x 0 1 0

ES . I N

N O T

KTU

Design of multi cycle microarchitecture Datapath and Control unit

Prepared by Susan Varghese, Asst. Prof, Dept of ECE Page 7

To get more study materails visit www.ktunotes.in

EC206 Computer Organizations Module 4

The single-cycle processor has three primary weaknesses.

1. It requires a clock cycle long enough to support the slowest instruction (lw), even

though most instructions are faster.

2. It requires three adders (one in the ALU and two for the PC logic); adders are

relatively expensive circuits, especially if they must be fast.

3. It has separate instruction and data memories, because both instruction and data

accesses needed within same clock cycle. Most computers have a single large

memory that holds both instructions and data and that can be read and written.

The multicycle processor addresses these weaknesses by

• Breaking an instruction into multiple shorter steps. In each short step, the

processor can read or write the memory or register file or use the ALU. Different

instructions use different numbers of steps, so simpler instructions can complete

faster than more complex ones.

• The processor needs only one adder; this adder is reused for different purposes on

various steps.

• The processor uses a combined memory for instructions and data. The instruction is

fetched from memory on the first step, and data may be read or written on later

steps.

In multi cycle implementation introduce additional Registers in every stages of the

datapath to buffer each step. These “non-architectural register” are not accessible to

programmer. In multi-cycle, same ALU used twice, in distinct cycles!

ES . I N

N O T

KTU

Above figure showing the control signals and Datapath (multicycle) for the

• Instructions lw, sw, R-type and beq

• Calculating instruction addresses

i) (PC+4) - for normal ii) (PC+4+Imm15:0*4) – for beq instruction

Prepared by Susan Varghese, Asst. Prof, Dept of ECE Page 8

To get more study materails visit www.ktunotes.in

EC206 Computer Organizations Module 4

State R-Type lw Sw beq PC Address*

Input

element instruction instruction instruction instruction calculation

Instruction

Address in* - Data address Data address

address

Instr/data

From 2nd

memory

Data in (WD) - - source register -

(Register file)

Source 1reg I25:21 I25:21 I25:21 I25:21

Source 2 reg I20:16 - - I20:16

Register

file

Destn reg* I15:11 I20:16 I20:16 (source) -

From Data

RegData in* From ALUout - -

memory

Data out1 of Data out1 of Data out1 of Data out1 of

Input1,SrcA* PC+4

register file register file register file register file

Data out2 of I15:0 I15:0 Data out2 of 4 (normal) or

Input2,SrcB**

ALU register file (sign extnd) (sign extnd) register file Imm15:0*4 (beq)

Instruction

Result of the Data memory Data memory

ALUresult memory

operation address address

address

Note:- * need 2:1 mux – (address in, Dest reg, RegData in, ALUSrcA, PC address in)

** need 4:1 mux – (ALUSrcB)

ES . I N

N O T

KTU

Prepared by Susan Varghese, Asst. Prof, Dept of ECE Page 9

To get more study materails visit www.ktunotes.in

EC206 Computer Organizations Module 4

MemtoReg =1, data is moving from

memory to Reg (lw)

=0, data is moving from

ALUresult to reg (R type)

RegDst =1, destination register is

selected by the bits I15:11

=0, by bits I20:16

IorD =0, Instruction address

=1, Data address

PCSrc =0, PC+4 (normal)

=1, PC+4+Imm15:0

ALUSrcA =0, PC+4

= 1, register dataOut1

ALUSrcB =00, register dataOut2

=01, 4

=10, signextImm15:0

=11, signextImm15:0*4

ES . I N

N O T

KTU

Prepared by Susan Varghese, Asst. Prof, Dept of ECE Page 10

To get more study materails visit www.ktunotes.in

EC206 Computer Organizations Module 4

PERFORMANCE ANALYSIS

• The cost depends on the amount of hardware required and the implementation

technology.

• There are many ways to measure the performance of a computer; the only gimmick-

free way to measure performance is by measuring the execution time of a program

of interest to you. The computer that executes your program fastest has the highest

performance. The next best choice is to measure the total execution time of a

collection of programs that are similar to those you plan to run. Such collections of

programs are called benchmarks, and the execution times of these programs are

commonly published to give some indication of how a processor performs.

• The execution time of a program, measured in seconds, is given by

𝐶𝐶𝐶𝐶𝐶𝐶𝐶𝐶𝐶𝐶𝐶𝐶 𝑠𝑠𝑠𝑠𝑠𝑠𝑠𝑠𝑠𝑠𝑠𝑠𝑠𝑠

𝐸𝐸𝐸𝐸𝐸𝐸𝐸𝐸𝐸𝐸𝐸𝐸𝐸𝐸𝐸𝐸𝐸𝐸 𝑡𝑡𝑡𝑡𝑡𝑡𝑡𝑡 = (#𝑖𝑖𝑖𝑖𝑖𝑖𝑖𝑖𝑖𝑖𝑖𝑖𝑖𝑖𝑖𝑖𝑖𝑖𝑖𝑖𝑖𝑖𝑖𝑖)( )( )

𝐼𝐼𝐼𝐼𝐼𝐼𝐼𝐼𝐼𝐼𝐼𝐼𝐼𝐼𝐼𝐼𝐼𝐼𝐼𝐼𝐼𝐼𝐼𝐼 𝑐𝑐𝑐𝑐𝑐𝑐𝑐𝑐𝑐𝑐

The number of instructions in a program depends on the processor architecture.

Some architecture has complicated instructions that do more work per instruction, thus

reducing the number of instructions in a program. However, these complicated

instructions are often slower to execute in hardware.

The number of instructions also depends enormously on the cleverness of the

programmer.

. I N

The number of cycles per instruction, often called CPI, is the number of clock cycles

ES

required to execute an average instruction.

N O T

KTU

The number of seconds per cycle is the clock period, Tc. The clock period is determined by

the critical path through the logic on the processor.

Performance analysis of single cycle microarchitecture

Each instruction in the single-cycle processor takes one clock cycle, so the CPI is 1. The

critical path for the lw instruction.

Performance analysis of multi cycle microarchitecture

The execution time of an instruction depends on both the number of cycles it uses and the

cycle time. Whereas the single-cycle processor performed all instructions in one cycle, the

multicycle processor uses varying numbers of cycles for the various instructions. However,

the multicycle processor does less work in a single cycle and, thus, has a shorter cycle time.

The multicycle processor requires three cycles for beq and j instructions, four cycles for

sw, addi, and R-type instructions, and five cycles for lw instructions. The CPI depends on

the relative likelihood that each instruction is used.

Prepared by Susan Varghese, Asst. Prof, Dept of ECE Page 11

To get more study materails visit www.ktunotes.in

Das könnte Ihnen auch gefallen

- 2 16 1350130228 7. Flexible Wireless DataDokument6 Seiten2 16 1350130228 7. Flexible Wireless DataSumeet SauravNoch keine Bewertungen

- MIPS Report FileDokument17 SeitenMIPS Report FileAayushiNoch keine Bewertungen

- Unit 2 - Embedded SystemDokument75 SeitenUnit 2 - Embedded Systemsujith100% (4)

- Sparc Processor: by - Sagar B Patel Charotar Inst. of Techno. ChangaDokument24 SeitenSparc Processor: by - Sagar B Patel Charotar Inst. of Techno. ChangaRavishah007Noch keine Bewertungen

- Conference Template A4Dokument4 SeitenConference Template A4ATHIRA V RNoch keine Bewertungen

- Continuation 4TH Unit DpacoDokument18 SeitenContinuation 4TH Unit DpacoSANJAY KASI VISVANATHANNoch keine Bewertungen

- EC8552 Computer Architecture and Organization 2 MDokument23 SeitenEC8552 Computer Architecture and Organization 2 MKeshvan DhanapalNoch keine Bewertungen

- Ijaret: ©iaemeDokument9 SeitenIjaret: ©iaemeIAEME PublicationNoch keine Bewertungen

- Task Switching:: JMP Call JMP Call Iret JMP Call IretDokument19 SeitenTask Switching:: JMP Call JMP Call Iret JMP Call IretAshish PatilNoch keine Bewertungen

- QB106611Dokument6 SeitenQB106611Kingsley SNoch keine Bewertungen

- Computer Architecture 16 MarksDokument28 SeitenComputer Architecture 16 MarksBalachandar2000100% (1)

- Risc Processor Using VHDLDokument5 SeitenRisc Processor Using VHDLAruna RajanNoch keine Bewertungen

- AC CourseWork MihaiTrofimDokument31 SeitenAC CourseWork MihaiTrofimDima VlasNoch keine Bewertungen

- Exp 2Dokument10 SeitenExp 2NAFISA ISLAM 1808006Noch keine Bewertungen

- 10th Lecture: Multiple-Issue Processors: Please Recall: Branch PredictionDokument28 Seiten10th Lecture: Multiple-Issue Processors: Please Recall: Branch PredictionSohei LaNoch keine Bewertungen

- Microprocessor Module-5 Question AnswersDokument8 SeitenMicroprocessor Module-5 Question AnswersShubham BargeNoch keine Bewertungen

- W5 - L1 - MacInst and OperDokument36 SeitenW5 - L1 - MacInst and OperNeel RavalNoch keine Bewertungen

- 32 Bit Risc ProcessorDokument60 Seiten32 Bit Risc ProcessorMuruganantham MuthusamyNoch keine Bewertungen

- Design and Performance Analysis of 8-Bit RISC Processor Using Xilinx ToolDokument7 SeitenDesign and Performance Analysis of 8-Bit RISC Processor Using Xilinx Toolkirat palNoch keine Bewertungen

- Design of 32-Bit Risc Cpu Based On Mips: Journal of Global Research in Computer ScienceDokument5 SeitenDesign of 32-Bit Risc Cpu Based On Mips: Journal of Global Research in Computer ScienceAkanksha Dixit ManodhyaNoch keine Bewertungen

- Ee/Ce 6370 Spring 2015: Design Assignment: Utd Pipelined MicroprocessorDokument7 SeitenEe/Ce 6370 Spring 2015: Design Assignment: Utd Pipelined MicroprocessorRohit YedidaNoch keine Bewertungen

- Instruction Pipeline Design, Arithmetic Pipeline Deign - Super Scalar Pipeline DesignDokument34 SeitenInstruction Pipeline Design, Arithmetic Pipeline Deign - Super Scalar Pipeline DesignMarlon TugweteNoch keine Bewertungen

- Objectives:: CS311 Lecture: CPU Control: Hardwired Control and Microprogrammed ControlDokument13 SeitenObjectives:: CS311 Lecture: CPU Control: Hardwired Control and Microprogrammed ControlVaibhav SharmaNoch keine Bewertungen

- Computer Architecture IIDokument27 SeitenComputer Architecture IIOlouge Eya EkolleNoch keine Bewertungen

- Computer ArchitectureDokument4 SeitenComputer ArchitectureAgrippa MungaziNoch keine Bewertungen

- Lecture 2 Basic CPU ArchitecturesDokument7 SeitenLecture 2 Basic CPU ArchitecturesMohan Krishna Reddy KarriNoch keine Bewertungen

- 2-Introduction To Pentium ProcessorDokument15 Seiten2-Introduction To Pentium Processorafzal_a92% (13)

- ArchitectureDokument14 SeitenArchitectureGopal PawarNoch keine Bewertungen

- Module 3 CoaDokument17 SeitenModule 3 CoaGourab DashNoch keine Bewertungen

- RISC Instruction Set:: I) Data Manipulation InstructionsDokument8 SeitenRISC Instruction Set:: I) Data Manipulation InstructionsSwarup BharNoch keine Bewertungen

- Superscalar Processor Pentium ProDokument11 SeitenSuperscalar Processor Pentium ProdiwakerNoch keine Bewertungen

- Aca 2 Marks With AnswersDokument22 SeitenAca 2 Marks With AnswersmenakadevieceNoch keine Bewertungen

- Course Material (Question Bank)Dokument6 SeitenCourse Material (Question Bank)Práviñ KumarNoch keine Bewertungen

- Chapter Four 4. The Control UnitDokument9 SeitenChapter Four 4. The Control UnitTamene TekileNoch keine Bewertungen

- A) Von Neumann ArchitectureDokument3 SeitenA) Von Neumann Architecturedriftwood 069Noch keine Bewertungen

- IRJET Design of Low Power 32 Bit RISC PRDokument8 SeitenIRJET Design of Low Power 32 Bit RISC PRpawan vermaNoch keine Bewertungen

- Input Unit: Five Basic Components of Computer SystemDokument9 SeitenInput Unit: Five Basic Components of Computer SystemJefin PaulNoch keine Bewertungen

- Cse IV Computer Organization (10cs46) SolutionDokument62 SeitenCse IV Computer Organization (10cs46) Solutionnbpr0% (1)

- 8 Bit Microprocessor Using VHDL: Pallavi Deshmane, Maithili Lad & Pooja Mhetre Sharan KumarDokument6 Seiten8 Bit Microprocessor Using VHDL: Pallavi Deshmane, Maithili Lad & Pooja Mhetre Sharan KumarshubhamNoch keine Bewertungen

- Machines, Machine Languages, and Digital Logic: Accumulator Machines Have A Sharply Limited Number of DataDokument6 SeitenMachines, Machine Languages, and Digital Logic: Accumulator Machines Have A Sharply Limited Number of DataZanz ProjectzNoch keine Bewertungen

- BFM3333 Course: Microcontroller SystemDokument33 SeitenBFM3333 Course: Microcontroller SystemMostafa AbdulmalekNoch keine Bewertungen

- Lab Sheet 6 Single Cycle Datapath FinalDokument3 SeitenLab Sheet 6 Single Cycle Datapath FinalSANJEEV MALLICKNoch keine Bewertungen

- CoDokument80 SeitenCogdayanand4uNoch keine Bewertungen

- AssembyDokument57 SeitenAssembyOmar KamilNoch keine Bewertungen

- 17 Bit Implementation For Dual Core Risc ArchitectureDokument6 Seiten17 Bit Implementation For Dual Core Risc ArchitecturelambanaveenNoch keine Bewertungen

- Cep 1Dokument8 SeitenCep 1ShivamNoch keine Bewertungen

- Computer Arch NotesDokument9 SeitenComputer Arch NoteszomukozaNoch keine Bewertungen

- HenzonzzzzDokument5 SeitenHenzonzzzzapi-548516280Noch keine Bewertungen

- COA Mod 1 UpdatedDokument22 SeitenCOA Mod 1 UpdatedMirror LeechNoch keine Bewertungen

- Coa Unit - 5 NotesDokument6 SeitenCoa Unit - 5 Notes1NT19IS077-MADHURI.CNoch keine Bewertungen

- Chapter 4 - Central Processing Units Is BzudhesvsDokument7 SeitenChapter 4 - Central Processing Units Is Bzudhesvsrosdi jkmNoch keine Bewertungen

- Computer System Organizations: Ms - Chit Su MonDokument74 SeitenComputer System Organizations: Ms - Chit Su MonAjharuddin AnsariNoch keine Bewertungen

- kjwkc3 - Cs 2700 Mid TermDokument2 Seitenkjwkc3 - Cs 2700 Mid Termjinrongliu2382Noch keine Bewertungen

- CMPS293&290 Class Notes Chap 02Dokument24 SeitenCMPS293&290 Class Notes Chap 02hassanNoch keine Bewertungen

- Computer System Architecture MCA - 301Dokument10 SeitenComputer System Architecture MCA - 301Mangesh MalvankarNoch keine Bewertungen

- 5EC3-01: Computer Architecture: UNIT-3Dokument11 Seiten5EC3-01: Computer Architecture: UNIT-3Himanshi SainiNoch keine Bewertungen

- The Sparc ArchitectureDokument16 SeitenThe Sparc ArchitectureAshwini PatilNoch keine Bewertungen

- Computer Organization and Assembly Language: Lecture 2 - x86 Processor ArchitectureDokument23 SeitenComputer Organization and Assembly Language: Lecture 2 - x86 Processor ArchitectureNosreffejDelRosarioNoch keine Bewertungen

- SciLab Tugas 1Dokument24 SeitenSciLab Tugas 1Det StrixNoch keine Bewertungen

- Ineo 367 BrochureDokument8 SeitenIneo 367 BrochureandiNoch keine Bewertungen

- Java Programming: Program 2: Write A Program in Java For Widening and Narrowing ConversionDokument4 SeitenJava Programming: Program 2: Write A Program in Java For Widening and Narrowing Conversionumair riazNoch keine Bewertungen

- Serv LetsDokument15 SeitenServ LetsannaNoch keine Bewertungen

- MAN Cats t200 User MunualDokument9 SeitenMAN Cats t200 User MunualСаиф АббасNoch keine Bewertungen

- 20ESIT202 - Python ProgrammingDokument12 Seiten20ESIT202 - Python ProgrammingRashim RBNoch keine Bewertungen

- Fulmo GT: ECA1092 SeriesDokument2 SeitenFulmo GT: ECA1092 SeriesFlorescu FlorinNoch keine Bewertungen

- PLC Controlled Motion Release NotesDokument5 SeitenPLC Controlled Motion Release NotesEduardo Antonio MateusNoch keine Bewertungen

- MF-230 FAQ Harvey Norman v1.0Dokument2 SeitenMF-230 FAQ Harvey Norman v1.0Nur Liyana Binti YaakobNoch keine Bewertungen

- Keylo Operating Manual: HanoverDokument19 SeitenKeylo Operating Manual: HanoverDario Gabriel Coz RojasNoch keine Bewertungen

- ACS880 IGBT Supply Control Program: Firmware ManualDokument254 SeitenACS880 IGBT Supply Control Program: Firmware ManualGopinath PadhiNoch keine Bewertungen

- IOT-Assignment 2 PDFDokument5 SeitenIOT-Assignment 2 PDFQusai KHNoch keine Bewertungen

- OOT TutorialDokument3 SeitenOOT TutorialChaeriah WaelNoch keine Bewertungen

- Transport Layer ServicesDokument71 SeitenTransport Layer ServicesSomnath SinhaNoch keine Bewertungen

- Exam 1 SolDokument8 SeitenExam 1 SolChuang JamesNoch keine Bewertungen

- Apache KafkaDokument37 SeitenApache KafkaPhani Karthik MaradaniNoch keine Bewertungen

- Tomcat Cluster SetupDokument3 SeitenTomcat Cluster SetupsmjainNoch keine Bewertungen

- Lgr25, Lgr250, & Lgr1000: High-Speed Bacnet Routing & IntegrationDokument2 SeitenLgr25, Lgr250, & Lgr1000: High-Speed Bacnet Routing & IntegrationEssam MohamedNoch keine Bewertungen

- Sick NoderedDokument8 SeitenSick NoderedMateo PožgajNoch keine Bewertungen

- ADDADokument50 SeitenADDAAnupam KumarNoch keine Bewertungen

- Computer Basic KnowledgeDokument143 SeitenComputer Basic KnowledgeRam Prasad0% (1)

- Aud. in Cis Env. Final Exam 2nd Sem Ay2017-18 (Sam)Dokument9 SeitenAud. in Cis Env. Final Exam 2nd Sem Ay2017-18 (Sam)Uy SamuelNoch keine Bewertungen

- JCL Faqs: JCL Questions Amit Sethi Page 1 of 51Dokument51 SeitenJCL Faqs: JCL Questions Amit Sethi Page 1 of 51Ravikumar VankadaraNoch keine Bewertungen

- Installation and Architecture - 2019v2Dokument32 SeitenInstallation and Architecture - 2019v2abdiel AlveoNoch keine Bewertungen

- D45 System: 322011 Digital Colour Entrance Panel With Addresses ListDokument10 SeitenD45 System: 322011 Digital Colour Entrance Panel With Addresses ListBrunaNoch keine Bewertungen

- DfgfgsadfgsfDokument52 SeitenDfgfgsadfgsfdjzaffiroNoch keine Bewertungen

- Naslite Plus ManualDokument11 SeitenNaslite Plus Manualgregory_hamilton_9Noch keine Bewertungen

- Software Requirements Specification NetbeansDokument16 SeitenSoftware Requirements Specification NetbeansRaj PandeyNoch keine Bewertungen

- Pwn2Own 2014 AFD - Sys Privilege EscalationDokument16 SeitenPwn2Own 2014 AFD - Sys Privilege Escalationc583162Noch keine Bewertungen

- Python Basics-2Dokument94 SeitenPython Basics-2mahendra naikNoch keine Bewertungen