Beruflich Dokumente

Kultur Dokumente

Lecture-45 CPU Initiated Conditional Data Transfer: Port 1 Tristate Buffer 8-It Latch

Hochgeladen von

WilliamOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Lecture-45 CPU Initiated Conditional Data Transfer: Port 1 Tristate Buffer 8-It Latch

Hochgeladen von

WilliamCopyright:

Verfügbare Formate

Lecture-45

CPU Initiated Conditional Data Transfer

In CPU initiated conditional data transfer, the processor initiates

the data transfer process but the execution of I/O instruction for data

transfer is conditioned on the I/O device being ready for the data

transfer. Readiness is determined by an unconditional transfer of

status information from the I/O device to the processor that contains

the state of the I/O device hardware. Often 1 or 2 bits indicate the

status of an I/O device.

A single bit of status information indicates when a single input

port has information available for input or when a single output port is

ready to receive information. The software that tests the status flag

increases the time associated with the I/O operation; the additional

time is the I/O overhead.

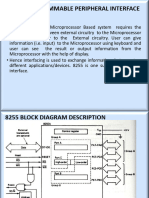

D7

D6 8

PORT 1 Data from

8-it Latch input device

Tristate

Buffer

D0

+5V

IDSP 01 H

D

Tri-state Buffer

Q

High indicating

data available

IDSP 00H

IDSP 01 H

Fig.7.21 Checking of Status of Input Device in Conditional Polled I/O

Consider, for example an input device that has data available at

input port „1‟ (let‟s call it DATA) for transmission to microprocessor.

To indicate the availability of data, the input device sets a flag bit 7 of

input port „0‟(let‟s call it STATUS). The use of flags in controlling

conditional transfer is referred to as handshaking with programmed

I/O. It is the only way of knowing when new data is available for input

to the microprocessor.

PIN: IN STATUS ; Input status byte

ORA A ; Set flags.

JP PIN ; Check data available status bit (bit7)

; if data is not available, wait

IN DATA ; Data is available, input data and

; clear data available flag.

MOV M,A ; Transfer data to memory

INX H ; Increment memory pointer

DCR B ; Decrement counter

JNZ PIN ; Back to pin if more data is to be input

RET

Fig.7.22 ALP to Input Data from an I/O Device in Polled I/O

To determine availability of data for inputs, the microprocessor

periodically input the status word at input port „0‟ and tests bit 7. If bit

7 is 1, data is available & an instruction inputs it from port „1‟. The

input device select strobe that enables the data from port „1‟ also

resets the data available flag.

The frequency with which the status flag is checked determines

the minimum length of time it takes to transfer the data. An input

subroutine executes a tight loop to check the status flag. The

subroutine given above assumes that the number of bytes of data to

be transferred is in B and that (H,L) points to the starting address of

the data buffer in memory when the subroutine is called.

This problem is best illustrated by taking an example. The

example to be considered is a direct interfacing of a tri-state ADC

based on Successive Approximation method. The block diagram is

shown in fig.7.23.

EOC D7-D0

8

CE

TRI STATE ADC

SOC

H H

L

VA(t)

Fig.6.23 Schematic Diagram of Tri-state 8-bit ADC

In fig.7.23 VA(t) is the analog input signal whose digital equivalent is

required. The 8-bit digital equivalent is obtained internally as and

when necessary by successive approximation principle which is very

fast. The data is made available at the output terminals D7 –D0 when

the chip enable signal CE is made ACTIVE LOW. When CE is HIGH,

the D7–D0 terminals are tri-stated. This ADC does not produce the

digital equivalent as and when the analog input changes but it needs

a start pulse designated as START OF CONVECSION (SOC) pulse.

In the ADC shown in figure, the SOC pulse is normally HIGH, goes

LOW and again HIGH. This LOW to HIGH transition of SOC signal

starts the conversion process. Once the process starts the digital

equivalent is not available instantaneously. It takes time, and the time

taken to get the digital equivalent, once the conversion starts is

known as the conversion time. Normally for a successive

approximation ACD chip the conversion time TC is around 100μsec. It

is assumed that the analog input is not changing during this

conversion time. This is true in the case of slow changing analog

signals. In the case of fast changing, analog input signal vA(t) of fig-2

shall be the output of a sample and hold circuit. Sample and hold

circuit is also available in the form of an IC chip.

Once the conversion begins, the external world must be told

that the ADC is busy in conversion. ADC issues a control signal

output known as “END OF CONVERSION (EOC)” signal for this

purpose. EOC is normally LOW and goes HIGH when conversion

starts. It remains HIGH as long as the conversion is not over and

goes LOW again when the conversion is complete. The complete

timing signal are shown in fig.7.24.

H H

SOC L

Internal

D7-D0 Don't care data Valid Data

EOC

Tc

CE

External Tri-state

Valid Data

D7-D0

Fig.7.24 Timing Diagram during Analog to Digital Conversion

We shall use the timing signals shown in fig.7.24, to interface the

ADC of fig.7.23 directly to microprocessor.

Let us interface the given ADC as memory mapped I/O

through the CPU initiated polled I/O transfer. Let the memory spaced

allocated to this device page C0H. It means that the complete

memory space address C000H to CFFH is allocated to this device.

Studying fig.7.23 and fig.7.24 we see that three different control

signals are to be generated or checked at appropriate time to read

one byte of data from the given ADC. Let us allocate the following

locations, all falling with in page C0H to generate these signals.

1) SOC : C0 X2 H

2) EOC : C0 X1 H

3) CE : C0 X0 H

Having allocated the addresses we can, draw the internal circuitry, of

given ADC of fig.7.23 for polled I/O transfer. Necessary interfacing

diagram is shown in fig.7.25.

To generate or checked control signals, the address lines A1

and A0 are to be decoded provided the higher order address is C0H.

A3 A2 A1 A0

X X 1 0 ------- SOC

X X 0 1 ------- EOC

X X 0 0 ------ CE

The desired address is put on address bus using MOV M,A

instruction. Content of accumulator is put on data bus during the

execution of MOV M, A. It is a fictitious write operation since it is used

to generate only a control pulse for ADC operation. No other device is

selected.

AB

BDB

D0 8 D7-D0 BCB

15 14 13 12 11 10 9 A8 EOC RD

RD WR

IO/M

A1 A0

74138

A0 0

A1 1

2

A2

3 EOC D7-D0

E1 4

E2 5

E3 6 TRI- STATE

7 SOC ADC

VA(t)

Fig.7.25 Interfacing of ADC with System Bus in Memory Mapped I/O

The producer to be followed to get one byte of data from the ADC is

as follows:

1) Initiate the conversion process by generating an SOC pulse. This

is done by a write operation on to the address C002H. This is a

fictitious write operation as the content of BDB is not written

anywhere but this operation is used only to generate SOC pulse.

However, fictitious write operations are always performed to

generate search pulses. Fictitious read operation is not

performed to generate a pulse because internal registers are not

to be disturbed.

2) Having applied SOC pulse, microprocessor should monitor the

EOC signal continuously to find whether the conversion is

complete. This is done by the processor by reading from the

memory location C001H and clerking whether D0 bit is zero.

3) It waits in step (2) continually monitoring the EOC signal as long

as EOC is HIGH.

4) When EOC is found LOW – a READ operation is performed from

the memory address C000H to take in 8-bits of digital equivalent

of analog signal at that time. The above process has to be

repeated for reading more than one sample of analog signal.

The detailed flow chart for reading one byte of data from fig.7.25

through polled I/O transfer is given in fig.7.26.

(H,L) C002

M(H,L) (A)

(L) (L) - 1

(A) M(H,L)

RRC

IS No

CY =0 ?

Yes

(L) (L) - 1

(A) M(H,L)

Fig.7.26 Flowchart for ADC Interfaced in Memory Mapped I/O

The ALP corresponding to fig.7.26 is shown in fig.7.27.

:

SOC EQU C0002H

LXI H, SOC ; (H,L) pints to SOC

MOV M,A ; Generate SOC pulse

DCR L

NEXT: MOV A,M ; Read EOC signal

RRC

JC NEXT ; If conversion is not over

; go back to check it again

DCR L ; If conversion is over

MOV A,M ; read data from ADC

:

Fig.7.27 ALPfor ADC Interfaced in Memory Mapped I/O

In the above discussions, we have interfaced the ADC directly with

the processor bus. It is possible, however, to interface the ADC with

the bus through programmable peripheral interface support chip. It

will be discussed later on.

Das könnte Ihnen auch gefallen

- Programming The DRAGON12-PLUS-USB in C and Assembly Language Using CodeWarriorDokument217 SeitenProgramming The DRAGON12-PLUS-USB in C and Assembly Language Using CodeWarriorJordan BienkoNoch keine Bewertungen

- Lwmirror2 3.0-H-004 (A0) Mirror2 3.0Dokument56 SeitenLwmirror2 3.0-H-004 (A0) Mirror2 3.0Pavel75% (4)

- Schaum Outline of Computer NetworkingDokument3 SeitenSchaum Outline of Computer NetworkingWilliamNoch keine Bewertungen

- 8255Dokument34 Seiten8255Manjula Bn100% (1)

- Parallel and Serial AdcDokument45 SeitenParallel and Serial AdcAman Deep100% (1)

- 8085 MicroprocessorDokument23 Seiten8085 Microprocessorauromaaroot196% (55)

- 8085 MicroprocessorDokument23 Seiten8085 Microprocessorauromaaroot196% (55)

- Sermons of St. Anthony of PaduaDokument1.210 SeitenSermons of St. Anthony of PaduaCath90100% (5)

- Mpmcnotesunit IIIDokument34 SeitenMpmcnotesunit IIIAmy OliverNoch keine Bewertungen

- NEC 022 External Paper SolutionDokument13 SeitenNEC 022 External Paper SolutionSachin PalNoch keine Bewertungen

- Block Diagram of 8255 WITH ExplanationDokument8 SeitenBlock Diagram of 8255 WITH Explanationsenthilkumar100% (2)

- 7-Segment Display & ADC Controls With 8051: LABORATORY - Experiment 5Dokument12 Seiten7-Segment Display & ADC Controls With 8051: LABORATORY - Experiment 5Vikas Ravi TPNoch keine Bewertungen

- #Tutorialspoint Programmable Peripheral Interface 8255: Block DiagramDokument26 Seiten#Tutorialspoint Programmable Peripheral Interface 8255: Block DiagramHasib PeyalNoch keine Bewertungen

- 8255 Mode 1,2 TD PDFDokument26 Seiten8255 Mode 1,2 TD PDFNaveen Kishore GattimNoch keine Bewertungen

- Data Bus BufferDokument16 SeitenData Bus BufferAbdul Samad KhanNoch keine Bewertungen

- Design With Microprocessors: Lecture 13: I/O InterfacesDokument28 SeitenDesign With Microprocessors: Lecture 13: I/O InterfacesthotalnNoch keine Bewertungen

- 8255 PpiDokument14 Seiten8255 PpiHarisankar R N R 21BRS1524Noch keine Bewertungen

- #Tutorialspoint Programmable Peripheral Interface 8255: Block DiagramDokument13 Seiten#Tutorialspoint Programmable Peripheral Interface 8255: Block DiagramHasib PeyalNoch keine Bewertungen

- Unit 6 2Dokument25 SeitenUnit 6 2Venkatesh RachaNoch keine Bewertungen

- Lecture-11 (8255 PPI)Dokument8 SeitenLecture-11 (8255 PPI)MAA COMPUTERNoch keine Bewertungen

- Finnal Diploma ME 111 Control ProjectDokument18 SeitenFinnal Diploma ME 111 Control ProjectSharif AwadNoch keine Bewertungen

- Adc & DacDokument10 SeitenAdc & DacMohamed Irshad AboubackerNoch keine Bewertungen

- Unit IIIDokument42 SeitenUnit IIISoundarrajan RajanNoch keine Bewertungen

- Embedded System Design - DisplaysDokument32 SeitenEmbedded System Design - DisplaysAnanthNoch keine Bewertungen

- Datasheet 82C55Dokument26 SeitenDatasheet 82C55Paulo VictorNoch keine Bewertungen

- Lecture 23Dokument8 SeitenLecture 23VINAYNoch keine Bewertungen

- Assignment Title: Programmable Peripheral Interface 8255: American International University-Bangladesh Summer 2019-2020Dokument7 SeitenAssignment Title: Programmable Peripheral Interface 8255: American International University-Bangladesh Summer 2019-2020MahiNoch keine Bewertungen

- Temp Indicator Use AT89C51Dokument11 SeitenTemp Indicator Use AT89C51sumit_saNoch keine Bewertungen

- Interfacing With PeriferalsDokument21 SeitenInterfacing With PeriferalsSunil AcharyaNoch keine Bewertungen

- Assignment Title: Programmable Peripheral Interface 8255: American International University-Bangladesh Summer 2019-2020Dokument7 SeitenAssignment Title: Programmable Peripheral Interface 8255: American International University-Bangladesh Summer 2019-2020MahiNoch keine Bewertungen

- Basic I/O Interface: A Course in Microprocessor Electrical Engineering Dept. University of IndonesiaDokument17 SeitenBasic I/O Interface: A Course in Microprocessor Electrical Engineering Dept. University of IndonesiaenricosaroinsongNoch keine Bewertungen

- Micro Final TRMPPRDokument13 SeitenMicro Final TRMPPRDeependra DabasNoch keine Bewertungen

- CH 3 PpiDokument12 SeitenCH 3 PpiAnisSamyNoch keine Bewertungen

- Adc 0808Dokument10 SeitenAdc 0808nakranimahender50% (2)

- Memory Interface Circuits 80x86 Processors: Ref: Online Course On EE-390, KFUPMDokument15 SeitenMemory Interface Circuits 80x86 Processors: Ref: Online Course On EE-390, KFUPMMarcus QeqqrqrrqNoch keine Bewertungen

- 8255Dokument28 Seiten8255satyanarayana12Noch keine Bewertungen

- Expt No 8 - 2023Dokument4 SeitenExpt No 8 - 2023Yachika YadavNoch keine Bewertungen

- Unit 4 - Computer Organization and Architecture - WWW - Rgpvnotes.inDokument15 SeitenUnit 4 - Computer Organization and Architecture - WWW - Rgpvnotes.inrk.chakrawartiNoch keine Bewertungen

- LCD and Keyboard Interfacing: Unit VDokument21 SeitenLCD and Keyboard Interfacing: Unit VrushitaaNoch keine Bewertungen

- Programmable Peripheral Interface (8255A)Dokument27 SeitenProgrammable Peripheral Interface (8255A)Jobair Al NahianNoch keine Bewertungen

- Input Output Port and InterfacingDokument44 SeitenInput Output Port and Interfacingsk087510100% (1)

- Peripheral Interfacing + Coding: Lets Learn How To Do It in 8051 !!Dokument44 SeitenPeripheral Interfacing + Coding: Lets Learn How To Do It in 8051 !!malhiavtarsinghNoch keine Bewertungen

- Assgmt 2Dokument57 SeitenAssgmt 2ayulza89Noch keine Bewertungen

- Features Description: CMOS Programmable Peripheral InterfaceDokument26 SeitenFeatures Description: CMOS Programmable Peripheral Interfaceanh_em5503Noch keine Bewertungen

- Iotuni 22Dokument24 SeitenIotuni 22Ashwin BenkeNoch keine Bewertungen

- 3 - General Purpose Programmable Peripheral DevicesDokument11 Seiten3 - General Purpose Programmable Peripheral DevicesHamza Abu Ajamia100% (2)

- 8255A Programmable: Peripheral Interface (PPI)Dokument26 Seiten8255A Programmable: Peripheral Interface (PPI)ShazidNoch keine Bewertungen

- Unit3 MicroprocessorDokument27 SeitenUnit3 MicroprocessorAshishNoch keine Bewertungen

- Chapter 2: 8255 Programmable Peripheral Interface: Department of MechatronicsDokument29 SeitenChapter 2: 8255 Programmable Peripheral Interface: Department of MechatronicsTho Ho DucNoch keine Bewertungen

- Unit 8 Digital Interfacing: Q.1.Describe Briefly The Methods of Data TransferDokument10 SeitenUnit 8 Digital Interfacing: Q.1.Describe Briefly The Methods of Data TransferpranoyiboyNoch keine Bewertungen

- Design of Handshake Mode With 8255 Using 8086Dokument10 SeitenDesign of Handshake Mode With 8255 Using 8086Rishab Mehta100% (1)

- Input/Output Interface Circuits And Lsi Peripheral Device: 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 10-2Dokument27 SeitenInput/Output Interface Circuits And Lsi Peripheral Device: 國立台灣大學 生物機電系 林達德 611 37100 微處理機原理與應用 Lecture 10-2sai420Noch keine Bewertungen

- Unit - 3 8255: (Programmable Peripheral Interface)Dokument7 SeitenUnit - 3 8255: (Programmable Peripheral Interface)Praveen SinghNoch keine Bewertungen

- 8255 Peripheral InterfaceDokument11 Seiten8255 Peripheral InterfaceSumanth ReddysrNoch keine Bewertungen

- Parallel Data TransfersDokument5 SeitenParallel Data TransfersWanjira KigokoNoch keine Bewertungen

- Last 3 EXPERIMENTs of TrainerDokument20 SeitenLast 3 EXPERIMENTs of TrainerAmanNoch keine Bewertungen

- Mecha Unit IIIDokument70 SeitenMecha Unit IIICAD With RaoNoch keine Bewertungen

- Nagindas Khandwala College of Commerce, Arts & Management Studies & Shantaben Nagindas Khandwala College of Science Malad (W), Mumbai - 64Dokument35 SeitenNagindas Khandwala College of Commerce, Arts & Management Studies & Shantaben Nagindas Khandwala College of Science Malad (W), Mumbai - 64127fyitvanshnagdaNoch keine Bewertungen

- ADC Measurement DetailDokument9 SeitenADC Measurement DetailMuhammad SiddiqueNoch keine Bewertungen

- Iotuni 21Dokument5 SeitenIotuni 21Ashwin BenkeNoch keine Bewertungen

- Unit - 5 8 Hours Interfacing Programming in C - 2: Pin DescriptionDokument25 SeitenUnit - 5 8 Hours Interfacing Programming in C - 2: Pin DescriptionHarshith Gowda RNoch keine Bewertungen

- MP PrintDokument64 SeitenMP PrintpoonamNoch keine Bewertungen

- 8255Dokument28 Seiten8255Gulam Rabbani Mohammed OsmanNoch keine Bewertungen

- Parallel Port ConfigurationDokument20 SeitenParallel Port ConfigurationvipoooNoch keine Bewertungen

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxVon EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxBewertung: 4 von 5 Sternen4/5 (2)

- Experiment: 1 Euclidean and Extended Euclidean AlgorithmDokument23 SeitenExperiment: 1 Euclidean and Extended Euclidean AlgorithmWilliamNoch keine Bewertungen

- Laplace TableDokument2 SeitenLaplace Tablecabeza2750% (2)

- Kristin Ackerson, Virginia Tech EE Spring 2002Dokument27 SeitenKristin Ackerson, Virginia Tech EE Spring 2002Kartik PatelNoch keine Bewertungen

- Short NotesDokument27 SeitenShort NotesWilliamNoch keine Bewertungen

- ExIndexes SolnDokument3 SeitenExIndexes SolnWilliamNoch keine Bewertungen

- New Heights: For Hard Disk DrivesDokument10 SeitenNew Heights: For Hard Disk DrivesWilliamNoch keine Bewertungen

- Ma/Csse 473 Day 28: Optimal BstsDokument29 SeitenMa/Csse 473 Day 28: Optimal BstsWilliamNoch keine Bewertungen

- 8085 Interrupts - GDLCDokument36 Seiten8085 Interrupts - GDLCWilliamNoch keine Bewertungen

- Wires11 PDFDokument10 SeitenWires11 PDFMuthuKumaranNoch keine Bewertungen

- 2010 Vol14 Iss 3 Intel Technology JournalDokument164 Seiten2010 Vol14 Iss 3 Intel Technology JournalWilliamNoch keine Bewertungen

- Wires11 PDFDokument10 SeitenWires11 PDFMuthuKumaranNoch keine Bewertungen

- Counter Design Using Sram PDFDokument5 SeitenCounter Design Using Sram PDFWilliamNoch keine Bewertungen

- Language On Schools - English Irregular Verbs List-1 PDFDokument5 SeitenLanguage On Schools - English Irregular Verbs List-1 PDFWilliamNoch keine Bewertungen

- HardwiredControlUnit PDFDokument12 SeitenHardwiredControlUnit PDFWilliamNoch keine Bewertungen

- CompArchCh05L14MicroprogrammedControl PDFDokument16 SeitenCompArchCh05L14MicroprogrammedControl PDFWilliamNoch keine Bewertungen

- CompArchCh05L14MicroprogrammedControl PDFDokument16 SeitenCompArchCh05L14MicroprogrammedControl PDFWilliamNoch keine Bewertungen

- Lecture32 PDFDokument10 SeitenLecture32 PDFWilliamNoch keine Bewertungen

- Lecture17 PDFDokument8 SeitenLecture17 PDFWilliamNoch keine Bewertungen

- Lecture-66 Asynchronous Serial Data CommunicationDokument6 SeitenLecture-66 Asynchronous Serial Data CommunicationVasthav KalluriNoch keine Bewertungen

- Lecture14 PDFDokument11 SeitenLecture14 PDFWilliamNoch keine Bewertungen

- AnalDokument142 SeitenAnalSomya PrasadNoch keine Bewertungen

- AnalDokument142 SeitenAnalSomya PrasadNoch keine Bewertungen

- AnalDokument142 SeitenAnalSomya PrasadNoch keine Bewertungen

- AnalDokument142 SeitenAnalSomya PrasadNoch keine Bewertungen

- Digital Electronics by Godse PDFDokument5 SeitenDigital Electronics by Godse PDFWilliamNoch keine Bewertungen

- CMS Hardware enDokument224 SeitenCMS Hardware enMas Kuncrit100% (2)

- AutoCAD Electrical JIC Admin Course Syllabus SampleDokument3 SeitenAutoCAD Electrical JIC Admin Course Syllabus Samplefadapow4uNoch keine Bewertungen

- Group7 Kiss JanusDokument33 SeitenGroup7 Kiss JanusCathrine Joy Roderos0% (1)

- W417 E1 01+CS1W CIF31+User Manual OmronDokument41 SeitenW417 E1 01+CS1W CIF31+User Manual OmronAby Alexander Jacobo MedalNoch keine Bewertungen

- Abacus Plus Hematology Analyzer - Service ManualDokument97 SeitenAbacus Plus Hematology Analyzer - Service ManualMed KerroumNoch keine Bewertungen

- Cp1intro To CDokument57 SeitenCp1intro To CV keerthikaNoch keine Bewertungen

- s7 300 314 IfmDokument93 Seitens7 300 314 IfmBlack WinNoch keine Bewertungen

- 3B6 ASA CB Can Bus Angle SensorDokument2 Seiten3B6 ASA CB Can Bus Angle SensorZian Henn100% (1)

- PSS 3047-3 Operating Manual 21062-En-12Dokument101 SeitenPSS 3047-3 Operating Manual 21062-En-12Anonymous m1cSnEavoNoch keine Bewertungen

- Most Important Computer QuestionsDokument63 SeitenMost Important Computer QuestionsShubham SharmaNoch keine Bewertungen

- USB in A NutShellDokument35 SeitenUSB in A NutShellSandro Jairzinho Carrascal Ayora100% (1)

- Sibas Computer (Traction Control Unit (Tcu) ) : ApplicationDokument59 SeitenSibas Computer (Traction Control Unit (Tcu) ) : ApplicationTiagohowpy RamosNoch keine Bewertungen

- Floating Point DSPs by BhaskarDokument44 SeitenFloating Point DSPs by BhaskarSai Anirudh SanagaramNoch keine Bewertungen

- GFK2892 GCG001 User Manual PDFDokument77 SeitenGFK2892 GCG001 User Manual PDFFabricio SouzaNoch keine Bewertungen

- What Is MicroprocessorDokument12 SeitenWhat Is MicroprocessorEdna Dimaano LalusinNoch keine Bewertungen

- COURSE FILE FINAL - ModifiedDokument23 SeitenCOURSE FILE FINAL - ModifiedLovely SinghNoch keine Bewertungen

- FX5 - User's Manual (Ethernet Communication) JY997D56201-G (10.17)Dokument176 SeitenFX5 - User's Manual (Ethernet Communication) JY997D56201-G (10.17)Dat NguyenNoch keine Bewertungen

- ETKP4.0 Emulator Probe For MPC561/562 and MPC563/564: Data SheetDokument34 SeitenETKP4.0 Emulator Probe For MPC561/562 and MPC563/564: Data SheetABDUL QADIRNoch keine Bewertungen

- Software Defined Test Fundamentals Guide PreviewDokument12 SeitenSoftware Defined Test Fundamentals Guide Previewpvengat86Noch keine Bewertungen

- Vvpa3cg en M b004Dokument24 SeitenVvpa3cg en M b004SaasiNoch keine Bewertungen

- MCU Architecture & Programming: An IntroductionDokument26 SeitenMCU Architecture & Programming: An IntroductionMarc Neil ApasNoch keine Bewertungen

- BT Digital SolutionsDokument68 SeitenBT Digital SolutionsHoàng TềNoch keine Bewertungen

- NOTESn MICROPROCESSORDokument27 SeitenNOTESn MICROPROCESSORtheamazingspidermich1234Noch keine Bewertungen

- Pba - Pro Stanag HR Sep2008Dokument2 SeitenPba - Pro Stanag HR Sep2008jcfermosellNoch keine Bewertungen

- Computer Science Notes: Computer Architecture & Fetch-Execute CycleDokument15 SeitenComputer Science Notes: Computer Architecture & Fetch-Execute CycleShreyan GuptaNoch keine Bewertungen

- Assignment No1 Task .No 1Dokument24 SeitenAssignment No1 Task .No 1Faria AmirNoch keine Bewertungen

- Munication With Profibus SystemsDokument283 SeitenMunication With Profibus SystemsAhmed KhairiNoch keine Bewertungen

- Asus U36JC-NYC2 ManualDokument0 SeitenAsus U36JC-NYC2 ManualRazmanNoch keine Bewertungen