Beruflich Dokumente

Kultur Dokumente

StudentGradeHistory 17MVD0018 PDF

Hochgeladen von

JIGAR JAYESHKUMAR PANKHANIA 17MVD0018Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

StudentGradeHistory 17MVD0018 PDF

Hochgeladen von

JIGAR JAYESHKUMAR PANKHANIA 17MVD0018Copyright:

Verfügbare Formate

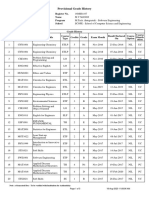

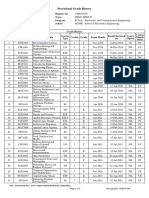

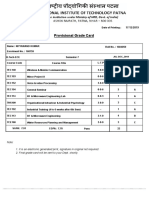

Provisional Grade History

Register No. 17MVD0018

Name PANKHANIA JIGAR JAYESHKUMAR

Program M.Tech. - VLSI Design

School SENSE - School of Electronics Engineering

Grade History

Course Credits Grade Result Declared Course Course

Sl.No Course Code Course Title Exam Month

Type On Option Distrib

ution

1 ECE5015 Digital IC Design ETP 4 B Nov-2017 11-Dec-2017 NIL PC

2 ECE5016 Analog IC Design ETL 4 B Nov-2017 11-Dec-2017 NIL PC

3 ECE5017 Digital Design with FPGA ETLP 4 A Nov-2017 11-Dec-2017 NIL PC

4 ECE5018 Physics of VLSI Devices TH 3 B Nov-2017 11-Dec-2017 NIL PC

Computer Aided Design

5 ECE5019 TH 3 A Nov-2017 11-Dec-2017 NIL PE

for VLSI

Advanced Computer

6 MAT5009 TH 3 A Nov-2017 11-Dec-2017 NIL UC

Arithmetic

Science, Engineering and

7 SET5001 PJT 2 A Nov-2017 19-Jan-2018 NIL UC

Technology Project - I

Essentials of Business

8 STS5001 SS 1 B Nov-2017 19-Dec-2017 NIL UC

Etiquettes

9 ECE5014 ASIC Design ETL 4 A Apr-2018 14-May-2018 NIL PC

Scripting Languages and

10 ECE5021 ETL 4 B Apr-2018 14-May-2018 NIL PE

Verification

Memory Design and

11 ECE5023 TH 3 B Apr-2018 09-May-2018 NIL PE

Testing

VLSI Testing and

12 ECE5029 TH 3 A Apr-2018 16-May-2018 NIL PE

Testability

13 ECE6025 Low Power IC Design ETP 3 A Apr-2018 14-May-2018 NIL PE

14 ECE6026 Mixed Signal IC Design ETP 3 A Apr-2018 14-May-2018 NIL PE

15 GER5001 Deutsch fuer Anfaenger TH 2 B Apr-2018 09-May-2018 NIL UC

Science, Engineering and

16 SET5002 PJT 2 A Apr-2018 19-May-2018 NIL UC

Technology Project - II

17 STS5002 Preparing for Industry SS 1 B Apr-2018 18-May-2018 NIL UC

18 ECE5024 IC Technology TH 3 C Jul-2018 12-Jul-2018 NIL PE

19 ECE5025 System-on-Chip Design TH 3 B Jul-2018 16-Jul-2018 NIL PE

20 ECE6099 Masters Thesis PJT 16 A Apr-2019 24-May-2019 NIL UC

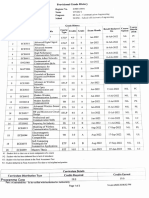

N1 : Student fails to clear one or more components of a course

Note : eGenerated Doc - To be verified with Institution for Authenticity

Page 1 of 2 30-May-2019 15:05:56 PM

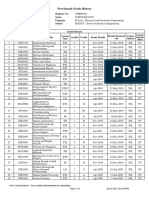

Provisional Grade History

Register No. 17MVD0018

Name PANKHANIA JIGAR JAYESHKUMAR

Program M.Tech. - VLSI Design

School SENSE - School of Electronics Engineering

N2 : Student who has been debarred due to lack of attendance

N3 : Student who has been absent in the Final Assessment Test

N4 : Student debarred in Final Assessment Test due to indiscipline/malpractice

Curriculum Details

Curriculum Distribution Type Credits Required Credits Earned

Programme Core 19 19

University Core 27 27

Programme Elective 18 25

University Elective 6 0

Basket Course - 0

Total Credits 70 71

Basket Details

Basket Title Distribution Type Credits Required Credits Earned

Soft Skills M.Tech. UC 2 2

English and Foreign Language UC 2 2

CGPA Details

Credits Credits CGPA S Grades A Grades B Grades C Grades D Grades E Grades F Grades N Grades

Registered Earned

71 71 8.56 0 10 9 1 0 0 0 0

Note : eGenerated Doc - To be verified with Institution for Authenticity

Page 2 of 2 30-May-2019 15:05:56 PM

Das könnte Ihnen auch gefallen

- COT 2nd Quarter Grade 8Dokument3 SeitenCOT 2nd Quarter Grade 8John Frits Gerard Mombay67% (3)

- LS 2. LAS. Percentage Problems (Commission)Dokument8 SeitenLS 2. LAS. Percentage Problems (Commission)Brandon Culbengan100% (1)

- Ecfvg FaqDokument11 SeitenEcfvg FaqAhmed FekryNoch keine Bewertungen

- H.E Fbs Grade 9-Budget-Of-workDokument4 SeitenH.E Fbs Grade 9-Budget-Of-workRodGaetosMasucolNoch keine Bewertungen

- Provisional Grade History: Register No. Name Program SchoolDokument3 SeitenProvisional Grade History: Register No. Name Program SchoolGoutham ReddyNoch keine Bewertungen

- Student GradeDokument6 SeitenStudent Gradetanuj guptaNoch keine Bewertungen

- Provisional Grade History ReportDokument5 SeitenProvisional Grade History ReportMike RomeoNoch keine Bewertungen

- Provisional Grade History: Register No. Name Program SchoolDokument4 SeitenProvisional Grade History: Register No. Name Program SchoolABHISHEK SAWANTNoch keine Bewertungen

- Provisional Grade History: Register No. Name Program SchoolDokument3 SeitenProvisional Grade History: Register No. Name Program SchoolJamunaraniNoch keine Bewertungen

- StudentGradeHistory 19BCY10038Dokument4 SeitenStudentGradeHistory 19BCY10038Help UsNoch keine Bewertungen

- Provisional Grade History: Register No. Name Program SchoolDokument2 SeitenProvisional Grade History: Register No. Name Program SchoolKarthik ReddyNoch keine Bewertungen

- Aktu One View by Aktu SDC - pdf2006480100028Dokument8 SeitenAktu One View by Aktu SDC - pdf2006480100028rakesh15mathNoch keine Bewertungen

- Aktu One View by Aktu SDC - pdf2006480100012Dokument3 SeitenAktu One View by Aktu SDC - pdf2006480100012rakesh15mathNoch keine Bewertungen

- Aktu One View by Aktu SDC - pdf2006480100007Dokument8 SeitenAktu One View by Aktu SDC - pdf2006480100007rakesh15mathNoch keine Bewertungen

- Biju Patnaik University of Technology, OdishaDokument3 SeitenBiju Patnaik University of Technology, Odisharohitsf22 olypmNoch keine Bewertungen

- Deliverable List for Alindo Hydrogen Transfer Line ProjectDokument4 SeitenDeliverable List for Alindo Hydrogen Transfer Line ProjectEdo FaiZal CandraWinataNoch keine Bewertungen

- Student Result: Session: 2015-16 (REGULAR) Semesters: 1,2 Result: PCP PTNS Marks: 1113/2000 COPDokument8 SeitenStudent Result: Session: 2015-16 (REGULAR) Semesters: 1,2 Result: PCP PTNS Marks: 1113/2000 COPyamini joshiNoch keine Bewertungen

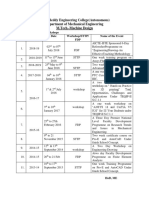

- Malla Reddy Engineering College (Autonomous) Department of Mechanical Engineering M.Tech.-Machine DesignDokument1 SeiteMalla Reddy Engineering College (Autonomous) Department of Mechanical Engineering M.Tech.-Machine DesignVenkata Reddy EmaniNoch keine Bewertungen

- RESULTDokument13 SeitenRESULTKartikey TyagiNoch keine Bewertungen

- Semester Grade Point Average (SGPA-VIII) : 7.07: University of Calicut Examination ResultsDokument1 SeiteSemester Grade Point Average (SGPA-VIII) : 7.07: University of Calicut Examination ResultsmunawarpmNoch keine Bewertungen

- CV Kevin Ikhwan Muhammad Pt. Hasakona BinaciptaDokument6 SeitenCV Kevin Ikhwan Muhammad Pt. Hasakona BinaciptaKevin MuhammadNoch keine Bewertungen

- SridarDokument2 SeitenSridarpranava sathyachidanandaNoch keine Bewertungen

- Bce1603365386047 1 PDFDokument860 SeitenBce1603365386047 1 PDFvamsi karnaNoch keine Bewertungen

- Aktu One View by Aktu SDC - pdf2006480100002Dokument5 SeitenAktu One View by Aktu SDC - pdf2006480100002rakesh15mathNoch keine Bewertungen

- Biju Patnaik University of Technology, OdishaDokument4 SeitenBiju Patnaik University of Technology, OdishaAndha KanoonNoch keine Bewertungen

- Dept. Course Details - Faculty WiseDokument12 SeitenDept. Course Details - Faculty Wisesarathkumar sebastinNoch keine Bewertungen

- 13BME0557 - History - 12 07 2016 - 15 18 15Dokument3 Seiten13BME0557 - History - 12 07 2016 - 15 18 15ASIMNoch keine Bewertungen

- Aktu One View by Aktu SDC - pdf2006480100029Dokument7 SeitenAktu One View by Aktu SDC - pdf2006480100029rakesh15mathNoch keine Bewertungen

- Aktu One View by Aktu SDC - pdf2006480100038Dokument7 SeitenAktu One View by Aktu SDC - pdf2006480100038rakesh15mathNoch keine Bewertungen

- 2nd Cse 1 Marks Report PDFDokument91 Seiten2nd Cse 1 Marks Report PDFgupta_ssrkm2747Noch keine Bewertungen

- Official Transcript of RecordsDokument2 SeitenOfficial Transcript of RecordsSantiago AmayaNoch keine Bewertungen

- Student Result: Aktu-One-View (Oneview - Aspx)Dokument2 SeitenStudent Result: Aktu-One-View (Oneview - Aspx)Ankit DwivediNoch keine Bewertungen

- Aktu One View by Aktu SDC - pdf2006480100037Dokument5 SeitenAktu One View by Aktu SDC - pdf2006480100037rakesh15mathNoch keine Bewertungen

- M.tech VLSI and ES Course Strucure 2020-21 - R 12 Dec 2020Dokument63 SeitenM.tech VLSI and ES Course Strucure 2020-21 - R 12 Dec 2020cutesandNoch keine Bewertungen

- Mahatma Gandhi University Kottayam: Result SheetDokument1 SeiteMahatma Gandhi University Kottayam: Result SheetGokul K NairNoch keine Bewertungen

- Grade Card: Visvesvaraya National Institute of Technology NagpurDokument363 SeitenGrade Card: Visvesvaraya National Institute of Technology NagpurNIKHIL KASATNoch keine Bewertungen

- Aktu One View by Aktu SDC - pdf2006480100001Dokument7 SeitenAktu One View by Aktu SDC - pdf2006480100001rakesh15mathNoch keine Bewertungen

- Aktu One View by Aktu SDC - pdf2006480100016Dokument7 SeitenAktu One View by Aktu SDC - pdf2006480100016rakesh15mathNoch keine Bewertungen

- VIT Final Year Production Engineering Syllabus A14 RevisedDokument42 SeitenVIT Final Year Production Engineering Syllabus A14 RevisedAnkush RatnaparkheNoch keine Bewertungen

- Aktu One View by Aktu SDC - pdf2006480100034Dokument7 SeitenAktu One View by Aktu SDC - pdf2006480100034rakesh15mathNoch keine Bewertungen

- Biju Patnaik University of Technology, Odisha: Even (2017 18) 1601202805Dokument1 SeiteBiju Patnaik University of Technology, Odisha: Even (2017 18) 1601202805Mahendra K BhagatNoch keine Bewertungen

- GradeCardBtecprint PDFDokument1 SeiteGradeCardBtecprint PDFNityanand KumarNoch keine Bewertungen

- StudentGradeHistory 21MAE0053Dokument2 SeitenStudentGradeHistory 21MAE0053Piyush BidwaiNoch keine Bewertungen

- ಕ ಫ ಾಂಶ ಜು ೖ/ಆಗ -೨೦೨೧. Vtu Provisional Results Of Ug / Pg July/August-2021 ExaminationDokument2 Seitenಕ ಫ ಾಂಶ ಜು ೖ/ಆಗ -೨೦೨೧. Vtu Provisional Results Of Ug / Pg July/August-2021 ExaminationVachana HiremathNoch keine Bewertungen

- C-051-VP-040-CLTW-SCH-0006 REV-1 Code-A With Minor CommentsDokument5 SeitenC-051-VP-040-CLTW-SCH-0006 REV-1 Code-A With Minor CommentsMidha NeerNoch keine Bewertungen

- M&a DSP VTU Result 2023Dokument2 SeitenM&a DSP VTU Result 2023محمد فہیمNoch keine Bewertungen

- Aktu One View by Aktu SDC - pdf2006480100030Dokument5 SeitenAktu One View by Aktu SDC - pdf2006480100030rakesh15mathNoch keine Bewertungen

- JPG Publication DetailsDokument18 SeitenJPG Publication DetailsdigbijoyNoch keine Bewertungen

- Computer Science and EngineeringDokument2 SeitenComputer Science and EngineeringRejin PaulNoch keine Bewertungen

- Aktu One View by Aktu SDC - pdf2006480100023Dokument7 SeitenAktu One View by Aktu SDC - pdf2006480100023rakesh15mathNoch keine Bewertungen

- Faculty Profile May 2016Dokument5 SeitenFaculty Profile May 2016Sakthidasan SankaranNoch keine Bewertungen

- IES PrepDokument2 SeitenIES PrepOoi Wei ShengNoch keine Bewertungen

- AKTU-One-View Student ResultDokument4 SeitenAKTU-One-View Student ResultBharti SinghNoch keine Bewertungen

- Aktu One View by Aktu SDC - pdf2006480100005Dokument4 SeitenAktu One View by Aktu SDC - pdf2006480100005rakesh15mathNoch keine Bewertungen

- Semester Grade CardDokument1 SeiteSemester Grade Cardsx developerNoch keine Bewertungen

- VVATSCS012Dokument2 SeitenVVATSCS012shanNoch keine Bewertungen

- MtechDokument2 SeitenMtechVivek S 21MCE0016Noch keine Bewertungen

- PG Syllabus 2018-20Dokument72 SeitenPG Syllabus 2018-20Om KoliNoch keine Bewertungen

- CAS Findings EvidenceRCADokument14 SeitenCAS Findings EvidenceRCAFrank RojasNoch keine Bewertungen

- Aktu One View by Aktu SDC - pdf2006480100026Dokument7 SeitenAktu One View by Aktu SDC - pdf2006480100026rakesh15mathNoch keine Bewertungen

- CSE Course and Subject TimetableDokument21 SeitenCSE Course and Subject TimetableKALIMUTHU KNoch keine Bewertungen

- Reappear Result of B.Tech. 3rd Sem. PIE 26082021Dokument4 SeitenReappear Result of B.Tech. 3rd Sem. PIE 26082021Prince G.Noch keine Bewertungen

- Engineering DrawingDokument7 SeitenEngineering DrawingMARIAMOO1Noch keine Bewertungen

- From Traders to Innovators: Science and Technology in Singapore since 1965Von EverandFrom Traders to Innovators: Science and Technology in Singapore since 1965Noch keine Bewertungen

- ASSIGNMENT II - Verification Using System VerilogDokument2 SeitenASSIGNMENT II - Verification Using System VerilogJIGAR JAYESHKUMAR PANKHANIA 17MVD0018Noch keine Bewertungen

- Parents Meeting CircularDokument1 SeiteParents Meeting CircularJIGAR JAYESHKUMAR PANKHANIA 17MVD0018Noch keine Bewertungen

- Capstone Project Report Format PDFDokument13 SeitenCapstone Project Report Format PDFJIGAR JAYESHKUMAR PANKHANIA 17MVD0018Noch keine Bewertungen

- Provisional Grade History: Register No. Name Program SchoolDokument2 SeitenProvisional Grade History: Register No. Name Program SchoolJIGAR JAYESHKUMAR PANKHANIA 17MVD0018Noch keine Bewertungen

- DSOA Theatre Handbook 2015-16Dokument54 SeitenDSOA Theatre Handbook 2015-16np18358Noch keine Bewertungen

- Mbao 108Dokument2 SeitenMbao 108rameshNoch keine Bewertungen

- Pres. Sergio Osmeña High School Manila Senior High School DepartmentDokument11 SeitenPres. Sergio Osmeña High School Manila Senior High School DepartmentRodlet PalmaNoch keine Bewertungen

- Executive Summary-3Dokument12 SeitenExecutive Summary-3Arjun Das100% (1)

- Research Activity2Dokument4 SeitenResearch Activity2Miguel Maribao Aquino Jr.Noch keine Bewertungen

- Hunter Terrell Cma Individualized Career Plan r2023 1Dokument15 SeitenHunter Terrell Cma Individualized Career Plan r2023 1api-708273919Noch keine Bewertungen

- Teacher Information FormDokument5 SeitenTeacher Information FormdasdmNoch keine Bewertungen

- Role of School Leadership in Developing Outstanding StudentsDokument7 SeitenRole of School Leadership in Developing Outstanding StudentsJulian JulioNoch keine Bewertungen

- China Report 2019, DecDokument8 SeitenChina Report 2019, DecBadri PaudelNoch keine Bewertungen

- Telephone DirectoryDokument56 SeitenTelephone Directorymann chalaNoch keine Bewertungen

- Chemistry Lesson PlanDokument3 SeitenChemistry Lesson Planapi-316656033Noch keine Bewertungen

- Ndep 2019-2020Dokument2 SeitenNdep 2019-2020Ma Ro Tan100% (1)

- Classroom and Safety Management Plans ECS - 567 Week 8Dokument9 SeitenClassroom and Safety Management Plans ECS - 567 Week 8Jacqueline MedinaNoch keine Bewertungen

- Arduini CVDokument3 SeitenArduini CVtinaarduiniNoch keine Bewertungen

- Bushra Shoukat: Professional GoalsDokument1 SeiteBushra Shoukat: Professional Goalsbisma amirNoch keine Bewertungen

- Reflective Essay On The Philosophy of Misamis UniversityDokument1 SeiteReflective Essay On The Philosophy of Misamis UniversityBonife Leo LubayNoch keine Bewertungen

- USCGA Class of 2025 International Cadet Program NominationDokument14 SeitenUSCGA Class of 2025 International Cadet Program NominationRüel DellovaNoch keine Bewertungen

- Degree Fpi Ism Pend - Awal - .Kanak2 BiDokument5 SeitenDegree Fpi Ism Pend - Awal - .Kanak2 BianasirrrNoch keine Bewertungen

- Detailed Lesson Plan in Pe 5Dokument14 SeitenDetailed Lesson Plan in Pe 5Trisha Olila CasimeroNoch keine Bewertungen

- Module 4 Teaching & Assessing WritingDokument13 SeitenModule 4 Teaching & Assessing WritingKath ButronNoch keine Bewertungen

- Chapter IDokument53 SeitenChapter IMerly RamosNoch keine Bewertungen

- First Grade Read Aloud Lesson PlanDokument6 SeitenFirst Grade Read Aloud Lesson Planapi-610735778Noch keine Bewertungen

- Arts7 q1 w1 Arts and Crafts of Ilocos Region and Cordillera Administrative RegionDokument2 SeitenArts7 q1 w1 Arts and Crafts of Ilocos Region and Cordillera Administrative RegionApolinario MatiasNoch keine Bewertungen

- CV Tax Accounting Grad Seeks JobDokument2 SeitenCV Tax Accounting Grad Seeks JobgresyestepinaNoch keine Bewertungen

- Lesson 1Dokument27 SeitenLesson 1MarkAnthonyLopezNoch keine Bewertungen

- Bloom's TaxonomyDokument9 SeitenBloom's TaxonomySC Zoe100% (2)