Beruflich Dokumente

Kultur Dokumente

Ao4813 PDF

Hochgeladen von

Anonymous t9tLb3WgOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Ao4813 PDF

Hochgeladen von

Anonymous t9tLb3WgCopyright:

Verfügbare Formate

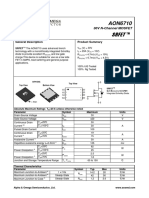

AO4813

30V Dual P-Channel MOSFET

General Description Product Summary

The AO4813 combines advanced trench MOSFET VDS -30V

technology with a low resistance package to provide ID (at VGS=-10V) -7.1A

extremely low RDS(ON). This device is ideal for load switch RDS(ON) (at VGS=-10V) < 25mΩ

and battery protection applications.

RDS(ON) (at VGS = -4.5V) < 40mΩ

100% UIS Tested

100% Rg Tested

SOIC-8

Top View Bottom View D D

Top View

S2 1 8 D2

G2 2 7 D2

S1 3 6 D1

G1 4 5 D1 G G

S S

Pin1

Absolute Maximum Ratings TA=25°C unless otherwise noted

Parameter Symbol Maximum Units

Drain-Source Voltage VDS -30 V

Gate-Source Voltage VGS ±20 V

Continuous Drain TA=25°C -7.1

ID

Current TA=70°C -5.6 A

C

Pulsed Drain Current IDM -40

Avalanche Current C IAS, IAR -27 A

Avalanche energy L=0.1mH C EAS, EAR 36 mJ

TA=25°C 2

PD W

Power Dissipation B TA=70°C 1.3

Junction and Storage Temperature Range TJ, TSTG -55 to 150 °C

Thermal Characteristics

Parameter Symbol Typ Max Units

Maximum Junction-to-Ambient A t ≤ 10s 48 62.5 °C/W

RθJA

Maximum Junction-to-Ambient A D Steady-State 74 90 °C/W

Maximum Junction-to-Lead Steady-State RθJL 32 40 °C/W

Rev 9: April 2011 www.aosmd.com Page 1 of 6

AO4813

Electrical Characteristics (TJ=25°C unless otherwise noted)

Symbol Parameter Conditions Min Typ Max Units

STATIC PARAMETERS

BVDSS Drain-Source Breakdown Voltage ID=-250µA, VGS=0V -30 V

VDS=-30V, VGS=0V -1

IDSS Zero Gate Voltage Drain Current µA

TJ=55°C -5

IGSS Gate-Body leakage current VDS=0V, VGS= ±20V ±100 nA

VGS(th) Gate Threshold Voltage VDS=VGS ID=-250µA -1.5 -2.0 -2.5 V

ID(ON) On state drain current VGS=-10V, VDS=-5V -40 A

VGS=-10V, ID=-7.1A 17 25

mΩ

RDS(ON) Static Drain-Source On-Resistance TJ=125°C 24 33

VGS=-4.5V, ID=-5.6A 27 40 mΩ

gFS Forward Transconductance VDS=-5V, ID=-7.1A 24 S

VSD Diode Forward Voltage IS=-1A,VGS=0V -0.75 -1 V

IS Maximum Body-Diode Continuous Current -2.5 A

DYNAMIC PARAMETERS

Ciss Input Capacitance 1040 1250 pF

Coss Output Capacitance VGS=0V, VDS=-15V, f=1MHz 180 pF

Crss Reverse Transfer Capacitance 125 175 pF

Rg Gate resistance VGS=0V, VDS=0V, f=1MHz 2 4 6 Ω

SWITCHING PARAMETERS

Qg(10V) Total Gate Charge 19 nC

Qg(4.5V) Total Gate Charge 9.6 nC

VGS=-10V, VDS=-15V, ID=-7.1A

Qgs Gate Source Charge 3.6 nC

Qgd Gate Drain Charge 4.6 nC

tD(on) Turn-On DelayTime 10 ns

tr Turn-On Rise Time VGS=-10V, VDS=-15V, RL=2.2Ω, 5.5 ns

tD(off) Turn-Off DelayTime RGEN=3Ω 26 ns

tf Turn-Off Fall Time 9 ns

trr Body Diode Reverse Recovery Time IF=-7.1A, dI/dt=500A/µs 11.5 ns

Qrr Body Diode Reverse Recovery Charge IF=-7.1A, dI/dt=500A/µs 25 nC

A. The value of RθJA is measured with the device mounted on 1in2 FR-4 board with 2oz. Copper, in a still air environment with TA =25°C. The

value in any given application depends on the user's specific board design.

B. The power dissipation PD is based on TJ(MAX)=150°C, using ≤ 10s junction-to-ambient thermal resistance.

C. Repetitive rating, pulse width limited by junction temperature TJ(MAX)=150°C. Ratings are based on low frequency and duty cycles to keep

initialTJ=25°C.

D. The RθJA is the sum of the thermal impedence from junction to lead RθJL and lead to ambient.

E. The static characteristics in Figures 1 to 6 are obtained using <300µs pulses, duty cycle 0.5% max.

F. These curves are based on the junction-to-ambient thermal impedence which is measured with the device mounted on 1in2 FR-4 board with

2oz. Copper, assuming a maximum junction temperature of TJ(MAX)=150°C. The SOA curve provides a single pulse ratin g.

THIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL

COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING

OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,

FUNCTIONS AND RELIABILITY WITHOUT NOTICE.

Rev 9: April 2011 www.aosmd.com Page 2 of 6

AO4813

TYPICAL ELECTRICAL AND THERMAL CHARACTERISTICS

60 40

-10V -7V VDS=-5V

50 -5V

30

40

-4.5V

-ID (A)

-ID(A)

30 20

20 -3.5V

10 125°C 25°C

10

VGS=-3.0V

0 0

0 1 2 3 4 5 0 1 2 3 4 5

-VDS (Volts) -VGS(Volts)

Fig 1: On-Region Characteristics (Note E) Figure 2: Transfer Characteristics (Note E)

35 1.8

Normalized On-Resistance

30 1.6 VGS=-10V

ID=-7.1A

RDS(ON) (mΩ )

25 VGS=-4.5V 1.4

17

5

20 1.2 2

10

VGS=-4.5V

15 1

VGS=-10V ID=-5.6A

10 0.8

0 5 10 15 20 0 25 50 75 100 125 150 175

-ID (A)

Temperature (°C) 0

Figure 3: On-Resistance vs. Drain Current and Figure 4: On-Resistance vs. Junction Temperature

Gate Voltage (Note E)

18

(Note E)

60 1.0E+02

ID=-7.1A

1.0E+01

50

40

1.0E+00

RDS(ON) (mΩ )

40 1.0E-01 125°C

-IS (A)

125°C

1.0E-02

30

1.0E-03 25°C

20 25°C 1.0E-04

10 1.0E-05

2 4 6 8 10 0.0 0.2 0.4 0.6 0.8 1.0 1.2

-VGS (Volts) -VSD (Volts)

Figure 5: On-Resistance vs. Gate-Source Voltage Figure 6: Body-Diode Characteristics (Note E)

(Note E)

Rev 9: April 2011 www.aosmd.com Page 3 of 6

AO4813

TYPICAL ELECTRICAL AND THERMAL CHARACTERISTICS

10 1600

VDS=-15V

ID=-7.1A 1400

8

1200 Ciss

Capacitance (pF)

1000

-VGS (Volts)

6

800

4 600

Coss

400

2

200

Crss

0 0

0 5 10 15 20 0 5 10 15 20 25 30

Qg (nC) -VDS (Volts)

Figure 7: Gate-Charge Characteristics Figure 8: Capacitance Characteristics

100 TA=25°C

100.0

-IAR (A) Peak Avalanche Current

TA=100°C

TA=150°C

10.0 RDS(ON) 10µs

limited 100µs

-ID (Amps)

10 TA=125°C

1.0

1ms

10ms

0.1 TJ(Max)=150°C

10s

TA=25°C

DC

1 0.0

1 10 100 1000 0.01 0.1 1 10 100

µs)

Time in avalanche, tA (µ -VDS (Volts)

Figure 9: Single Pulse Avalanche capability (Note Figure 10: Maximum Forward Biased Safe

C)

Operating Area (Note F)

10000

TA=25°C

1000

Power (W)

100

10

1

0.00001 0.001 0.1 10 1000

Pulse Width (s)

Figure 11: Single Pulse Power Rating Junction-to-Ambient (Note F)

Rev 9: April 2011 www.aosmd.com Page 4 of 6

AO4813

TYPICAL ELECTRICAL AND THERMAL CHARACTERISTICS

10

D=Ton/T In descending order

Zθ JA Normalized Transient

TJ,PK=TA+PDM.ZθJA.RθJA D=0.5, 0.3, 0.1, 0.05, 0.02, 0.01, single pulse

Thermal Resistance

1 RθJA=90°C/W

0.1

PD

0.01

Single Pulse

Ton

T

0.001

0.00001 0.0001 0.001 0.01 0.1 1 10 100 1000

Pulse Width (s)

Figure 12: Normalized Maximum Transient Thermal Impedance (Note F)

Rev 9: April 2011 www.aosmd.com Page 5 of 6

AO4813

Gate Charge Test Circuit & Waveform

Vgs

Qg

- -10V

VDC

-

+ Vds Qgs Qgd

VDC

+

DUT

Vgs

Ig

Charge

Resistive Switching Test Circuit & Waveforms

RL

Vds ton toff

td(on) tr t d(off) tf

Vgs

-

Vgs DUT VDC

Vdd 90%

Rg

+

Vgs 10%

Vds

Unclamped Inductive Switching (UIS) Test Circuit & Waveforms

2

L E AR= 1/2 LIAR

Vds

Id Vds

- BVDSS

Vgs

Vgs VDC

Vdd

Rg

+ Id

I AR

DUT

Vgs Vgs

Diode Recovery Test Circuit & Waveforms

Vds + Q rr = - Idt

DUT

Vgs

t rr

Vds - L -Isd -I F

Isd dI/dt

+ Vdd -I RM

Vgs VDC

Vdd

Ig

- -Vds

Rev 9: April 2011 www.aosmd.com Page 6 of 6

Das könnte Ihnen auch gefallen

- General Description Product Summary: 30V Dual P-Channel MOSFETDokument6 SeitenGeneral Description Product Summary: 30V Dual P-Channel MOSFETbiomed2083Noch keine Bewertungen

- Mosfet Doble Superficial Canal N 30V 8amp AO4854Dokument6 SeitenMosfet Doble Superficial Canal N 30V 8amp AO4854Antonio ChavezNoch keine Bewertungen

- AO4800Dokument6 SeitenAO4800Muhammad Ramdhan MusiamNoch keine Bewertungen

- General Description Product Summary: 30V Dual P-Channel MOSFETDokument5 SeitenGeneral Description Product Summary: 30V Dual P-Channel MOSFETAENoch keine Bewertungen

- General Description Product Summary: 30V P-Channel MOSFETDokument5 SeitenGeneral Description Product Summary: 30V P-Channel MOSFETGioVoTamNoch keine Bewertungen

- General Description Product Summary: 40V Dual N-Channel MOSFETDokument5 SeitenGeneral Description Product Summary: 40V Dual N-Channel MOSFETYimmy BarrosoNoch keine Bewertungen

- General Description Product Summary: 40V Dual N-Channel MOSFETDokument5 SeitenGeneral Description Product Summary: 40V Dual N-Channel MOSFETOscar MedinaNoch keine Bewertungen

- Ao4801 PDFDokument5 SeitenAo4801 PDFlujorebNoch keine Bewertungen

- General Description Product Summary: 30V Dual P-Channel MOSFETDokument5 SeitenGeneral Description Product Summary: 30V Dual P-Channel MOSFETAmjad ZaidNoch keine Bewertungen

- AO4822ADokument5 SeitenAO4822AAdolfo SanchezNoch keine Bewertungen

- General Description Product Summary: 30V N-Channel MOSFETDokument6 SeitenGeneral Description Product Summary: 30V N-Channel MOSFETAntonioPeriniNoch keine Bewertungen

- General Description Product Summary: 30V P-Channel MOSFETDokument5 SeitenGeneral Description Product Summary: 30V P-Channel MOSFETStoica VictorNoch keine Bewertungen

- General Description Product Summary: 20V Dual N-Channel MOSFETDokument5 SeitenGeneral Description Product Summary: 20V Dual N-Channel MOSFETmiguel angel jaramilloNoch keine Bewertungen

- General Description Product Summary: 30V Complementary MOSFETDokument9 SeitenGeneral Description Product Summary: 30V Complementary MOSFETSebastian CorreaNoch keine Bewertungen

- AOSP21357Dokument5 SeitenAOSP21357Carlos Roman MonkadaNoch keine Bewertungen

- AO4620 Complementary Enhancement Mode Field Effect TransistorDokument7 SeitenAO4620 Complementary Enhancement Mode Field Effect TransistorRenato-Paty CavachiniNoch keine Bewertungen

- AO4620 Complementary Enhancement Mode Field Effect TransistorDokument13 SeitenAO4620 Complementary Enhancement Mode Field Effect TransistorbobNoch keine Bewertungen

- General Description Product Summary: 100V Dual N-Channel MOSFETDokument6 SeitenGeneral Description Product Summary: 100V Dual N-Channel MOSFETJumhurul HanafiiNoch keine Bewertungen

- AO3415A AlphaOmegaSemiconductorsDokument5 SeitenAO3415A AlphaOmegaSemiconductorsinfosolutionNoch keine Bewertungen

- Ao 4407Dokument5 SeitenAo 4407Bsm GwapuNoch keine Bewertungen

- General Description Product Summary: 30V P-Channel MOSFETDokument6 SeitenGeneral Description Product Summary: 30V P-Channel MOSFETIkram BalochNoch keine Bewertungen

- General Description Product Summary: 30V P-Channel MOSFETDokument6 SeitenGeneral Description Product Summary: 30V P-Channel MOSFETCarlos Luis ColmenaresNoch keine Bewertungen

- AO4409 Mosfet para Ampli Bluetooth ChinoDokument5 SeitenAO4409 Mosfet para Ampli Bluetooth ChinoAnival FabregasNoch keine Bewertungen

- General Description Product Summary: 30V N-Channel MOSFETDokument5 SeitenGeneral Description Product Summary: 30V N-Channel MOSFETPedro OrtegaNoch keine Bewertungen

- Aop605 PDFDokument9 SeitenAop605 PDFopenscribdformeNoch keine Bewertungen

- General Description Product Summary: 30V P-Channel MOSFETDokument5 SeitenGeneral Description Product Summary: 30V P-Channel MOSFETKarlita GaspitoNoch keine Bewertungen

- AO4610 Complementary Enhancement Mode Field Effect TransistorDokument9 SeitenAO4610 Complementary Enhancement Mode Field Effect TransistorSergio Daniel CaminoNoch keine Bewertungen

- General Description Product Summary: 30V N-Channel MOSFETDokument5 SeitenGeneral Description Product Summary: 30V N-Channel MOSFETTaufik MantofaniNoch keine Bewertungen

- DatasheetDokument5 SeitenDatasheetcody 2Noch keine Bewertungen

- Srfet: 30V N-Channel MOSFETDokument5 SeitenSrfet: 30V N-Channel MOSFETGaspar GarciaNoch keine Bewertungen

- General Description Product Summary: 30V N-Channel MOSFETDokument5 SeitenGeneral Description Product Summary: 30V N-Channel MOSFETaffes electroniqueNoch keine Bewertungen

- Ao4604 PDFDokument9 SeitenAo4604 PDFRicardo SoaresNoch keine Bewertungen

- SMD Type Mosfet: Dual P-Channel MOSFET AO4813Dokument5 SeitenSMD Type Mosfet: Dual P-Channel MOSFET AO4813Will AlcântaraNoch keine Bewertungen

- General Description Product Summary: 30V N-Channel MOSFETDokument6 SeitenGeneral Description Product Summary: 30V N-Channel MOSFETShamim DhaliNoch keine Bewertungen

- Ao4468 PDFDokument5 SeitenAo4468 PDFaffes electroniqueNoch keine Bewertungen

- AO4710 AlphaOmegaSemiconductorsDokument6 SeitenAO4710 AlphaOmegaSemiconductorsanggie machoNoch keine Bewertungen

- AO4620 Complementary Enhancement Mode Field Effect TransistorDokument7 SeitenAO4620 Complementary Enhancement Mode Field Effect TransistorElLopeNoch keine Bewertungen

- General Description Product Summary: 20V P-Channel MOSFETDokument7 SeitenGeneral Description Product Summary: 20V P-Channel MOSFETAspire2222Noch keine Bewertungen

- AO4620 Complementary Enhancement Mode Field Effect TransistorDokument7 SeitenAO4620 Complementary Enhancement Mode Field Effect TransistorElLopeNoch keine Bewertungen

- Df6a D52V Ao6415Dokument5 SeitenDf6a D52V Ao6415dulah kemprohNoch keine Bewertungen

- Srfet: Product Summary General DescriptionDokument5 SeitenSrfet: Product Summary General DescriptionShamim DhaliNoch keine Bewertungen

- Product Summary General Description: 40V N-Channel MOSFETDokument4 SeitenProduct Summary General Description: 40V N-Channel MOSFETsagarNoch keine Bewertungen

- AON6504Dokument6 SeitenAON6504Mar GaoNoch keine Bewertungen

- General Description Product Summary: 30V Dual P-Channel MOSFETDokument7 SeitenGeneral Description Product Summary: 30V Dual P-Channel MOSFETDaniel CarreraNoch keine Bewertungen

- General Description Product Summary: 30V P-Channel MOSFETDokument5 SeitenGeneral Description Product Summary: 30V P-Channel MOSFEThosahe765Noch keine Bewertungen

- Acer Aspire 4740 4745 5740 5745 - COMPAL LA-5681P - REV 1.0Dokument5 SeitenAcer Aspire 4740 4745 5740 5745 - COMPAL LA-5681P - REV 1.0Ali AkbarNoch keine Bewertungen

- Product Summary General Description: 30V P-Channel MOSFETDokument5 SeitenProduct Summary General Description: 30V P-Channel MOSFETabdou kaderNoch keine Bewertungen

- Ao4435 Power Mosfet - ImportantDokument5 SeitenAo4435 Power Mosfet - ImportantSURESH CHANDRA ROUTNoch keine Bewertungen

- 71r-A14hmo-9h10 A14hm0-Ab10Dokument5 Seiten71r-A14hmo-9h10 A14hm0-Ab10Renato MacbarrosNoch keine Bewertungen

- General Description Product Summary: 60V P-Channel MOSFETDokument5 SeitenGeneral Description Product Summary: 60V P-Channel MOSFETdario defazyNoch keine Bewertungen

- AO4800B, AO4800BL Dual N-Channel Enhancement Mode Field Effect TransistorDokument4 SeitenAO4800B, AO4800BL Dual N-Channel Enhancement Mode Field Effect TransistorSmail BachirNoch keine Bewertungen

- General Description Product Summary: 30V P-Channel MOSFETDokument5 SeitenGeneral Description Product Summary: 30V P-Channel MOSFETAgusWinotoNoch keine Bewertungen

- AO4486Dokument6 SeitenAO4486senjinatorNoch keine Bewertungen

- AO4912 Asymmetric Dual N-Channel Enhancement Mode Field Effect TransistorDokument8 SeitenAO4912 Asymmetric Dual N-Channel Enhancement Mode Field Effect TransistorAntonioPeriniNoch keine Bewertungen

- AO4484Dokument4 SeitenAO4484waluyo128Noch keine Bewertungen

- General Description Product Summary: 30V P-Channel MOSFETDokument5 SeitenGeneral Description Product Summary: 30V P-Channel MOSFETM Romadi SiregarNoch keine Bewertungen

- General Description Product Summary: 30V N-Channel AlphamosDokument6 SeitenGeneral Description Product Summary: 30V N-Channel AlphamosDavid SimonNoch keine Bewertungen

- Datasheet 3Dokument6 SeitenDatasheet 3alan segundo garcia chotaNoch keine Bewertungen

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsVon EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNoch keine Bewertungen

- TBS1000B Series Oscilloscope Datasheet 3GW30004Dokument12 SeitenTBS1000B Series Oscilloscope Datasheet 3GW30004SURESH CHANDRA ROUTNoch keine Bewertungen

- Ao4435 Power Mosfet - ImportantDokument5 SeitenAo4435 Power Mosfet - ImportantSURESH CHANDRA ROUTNoch keine Bewertungen

- Zenith Z-150 PC Service ManualDokument380 SeitenZenith Z-150 PC Service ManualSURESH CHANDRA ROUT100% (1)

- 1 N 5391Dokument4 Seiten1 N 5391JavierGomezNoch keine Bewertungen

- LT1038Dokument9 SeitenLT1038SURESH CHANDRA ROUTNoch keine Bewertungen

- Galileo SchematicDokument27 SeitenGalileo SchematicluisNoch keine Bewertungen

- Fparts Alienware Bios UpdateDokument3 SeitenFparts Alienware Bios UpdatelockedioNoch keine Bewertungen

- IPMSB H61 DNS - ReadmeDokument1 SeiteIPMSB H61 DNS - ReadmeSURESH CHANDRA ROUTNoch keine Bewertungen

- ST8550DDokument5 SeitenST8550DSURESH CHANDRA ROUTNoch keine Bewertungen

- DM0565RDokument20 SeitenDM0565RSURESH CHANDRA ROUTNoch keine Bewertungen

- L4970ADokument21 SeitenL4970ASURESH CHANDRA ROUTNoch keine Bewertungen

- Panel BVCH t240xw01 v1 3 (DS)Dokument27 SeitenPanel BVCH t240xw01 v1 3 (DS)SURESH CHANDRA ROUT100% (1)

- Fds 4435Dokument5 SeitenFds 4435Rommel LoayzaNoch keine Bewertungen

- Samsung 740n ETDokument3 SeitenSamsung 740n ETSURESH CHANDRA ROUTNoch keine Bewertungen

- + 1.2v To + 25v Adjustable RegulatorDokument12 Seiten+ 1.2v To + 25v Adjustable RegulatorSURESH CHANDRA ROUTNoch keine Bewertungen

- lcd-mst6m48v2.0c 244 PDFDokument12 Seitenlcd-mst6m48v2.0c 244 PDFSURESH CHANDRA ROUTNoch keine Bewertungen

- This Is 1Dokument2 SeitenThis Is 1SURESH CHANDRA ROUTNoch keine Bewertungen

- Rendezvous - 2005-2007 PDFDokument8.854 SeitenRendezvous - 2005-2007 PDFKirk1978Noch keine Bewertungen

- Transformer and Motor Control ELEN 30022Dokument85 SeitenTransformer and Motor Control ELEN 30022Richmond Bautista VillasisNoch keine Bewertungen

- Robotic Landmine Detector Final ReportDokument18 SeitenRobotic Landmine Detector Final ReportS Bharadwaj Reddy100% (1)

- TWH Led ClassicDokument3 SeitenTWH Led Classicvictor farfanNoch keine Bewertungen

- Motional EMFDokument21 SeitenMotional EMFAparna DuggiralaNoch keine Bewertungen

- UNIT 1: Principles of Power ElectronicsDokument15 SeitenUNIT 1: Principles of Power ElectronicsIntekhab AlamNoch keine Bewertungen

- Development of Transcutaneous Electrical Nerve Stimulator (TENS) Chair With Microcontroller Based ApplicationDokument9 SeitenDevelopment of Transcutaneous Electrical Nerve Stimulator (TENS) Chair With Microcontroller Based Applicationsumathy ysNoch keine Bewertungen

- Solar Charge Controller: With Integrated LED DriverDokument4 SeitenSolar Charge Controller: With Integrated LED DriverSyaifNoch keine Bewertungen

- Experiment 1 Preliminary Report: ELEC3307 Electronics LaboratoryDokument5 SeitenExperiment 1 Preliminary Report: ELEC3307 Electronics LaboratoryArda Deniz EryiğitNoch keine Bewertungen

- Smartpack Monitoring and Control Unit PDFDokument20 SeitenSmartpack Monitoring and Control Unit PDFSohaib Omer SalihNoch keine Bewertungen

- MegaBrute Leafcutter Mods 03 PDFDokument6 SeitenMegaBrute Leafcutter Mods 03 PDFPierre-FrançoisLacenaireNoch keine Bewertungen

- KL 300Dokument4 SeitenKL 300Zaheer AbbasNoch keine Bewertungen

- MIT Haystack Lunch Talk 2-3-10Dokument19 SeitenMIT Haystack Lunch Talk 2-3-10Stu SutherlandNoch keine Bewertungen

- Solectria Xgi™ 1000: Modbus Manual Models: XGI 1000-50/60 XGI 1000-60/65 XGI 1000-60/60 XGI 1000-65/65Dokument31 SeitenSolectria Xgi™ 1000: Modbus Manual Models: XGI 1000-50/60 XGI 1000-60/65 XGI 1000-60/60 XGI 1000-65/65Baggi NNoch keine Bewertungen

- Catalog Thornton IngDokument161 SeitenCatalog Thornton IngAllyfranhy Nunes AlvesNoch keine Bewertungen

- Power Electronic DimmerDokument75 SeitenPower Electronic DimmerCelalettin YüceNoch keine Bewertungen

- IR Sensor Theory of OperationDokument4 SeitenIR Sensor Theory of OperationSebastin Ashok100% (1)

- Manejo Service ToolDokument35 SeitenManejo Service ToolClementeNoch keine Bewertungen

- Motor Selection GuideDokument55 SeitenMotor Selection GuideElafanNoch keine Bewertungen

- Standard For Hand-Over Test of Electric Equipment Electric Equipment Installation EngineeringDokument82 SeitenStandard For Hand-Over Test of Electric Equipment Electric Equipment Installation EngineeringHuang Han100% (2)

- Experiment - 12: Power Angle Curve of Syncronous MachineDokument3 SeitenExperiment - 12: Power Angle Curve of Syncronous MachinesanjuNoch keine Bewertungen

- 5075 DatasheetDokument3 Seiten5075 Datasheetjon1224Noch keine Bewertungen

- EPX-series Manual Ver 0.9 PDFDokument136 SeitenEPX-series Manual Ver 0.9 PDFNguyen TriNoch keine Bewertungen

- RA-5700 Tri-Band Distributed Antenna System: User ManualDokument66 SeitenRA-5700 Tri-Band Distributed Antenna System: User ManualforwirelessNoch keine Bewertungen

- Sony ss-ccx4b ss-ccx4w Ver.1.1 SMDokument2 SeitenSony ss-ccx4b ss-ccx4w Ver.1.1 SMrobsonrivarolaNoch keine Bewertungen

- Opt Encoder 62CDokument2 SeitenOpt Encoder 62CPeter BirdNoch keine Bewertungen

- Caterpillar - 3412 - 750kVADokument2 SeitenCaterpillar - 3412 - 750kVAPrashant NaikNoch keine Bewertungen

- Magnetic Balance Test On Transformers PDFDokument3 SeitenMagnetic Balance Test On Transformers PDFDhinesh KumarNoch keine Bewertungen

- Power TechnicsDokument14 SeitenPower Technicserkamlakar2234Noch keine Bewertungen