Beruflich Dokumente

Kultur Dokumente

Lecture 8

Hochgeladen von

Bernard Mkumbwa Jr.0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

18 Ansichten40 Seitenvlsi

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenvlsi

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

18 Ansichten40 SeitenLecture 8

Hochgeladen von

Bernard Mkumbwa Jr.vlsi

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 40

TN 423: VLSI CIRCUITS

Lecture 6

ASSEMBLY AND PACKAGING

TECHNIQUES

Ngeze, LV VLSI Circuits 1

Outline

1. Introduction

2. Wafer Assembly Techniques

3. Packaging of VLSI

4. Package Design Considerations (Parameters)

5. Package Types

Ngeze, LV VLSI Circuits 2

Introduction

Ω Packaging of VLSI ranges from preassembly

wafer preparation to fabrication technologies for

the packages

Ω It affects the cost, performance and reliability of

the packaged die

Ω Packaging techniques have to be upgraded

accordingly because of the increase in chip

complexity and chip size

Ω Number of I/O terminals required for logic and

microprocessor devices has continued to

increase in proportion to the number of gates on

the chip Ngeze, LV VLSI Circuits 3

Introduction

Rent’s Rule

Ω In the 1960s, E. F. Rent, an IBM employee,

found a remarkable trend between the number

of I/O pins (terminals, T) at the boundaries of IC

designs and the number of internal components

(g), such as logic gates or standard cells.

Ω Rent’s rule states that the following relationship

exists between several chip parameters.

T = AKP

Ngeze, LV VLSI Circuits 4

Introduction

T is the number of I/O terminals,

A the average number of terminals for one block and

K the number of blocks within the chip,

p the Rent’s exponent (p < 1.0, generally 0.5 < p < 0.8)

Ω Rent's rule has been widely used to

estimate the number of interconnects.

estimate power dissipation in interconnects.

Ngeze, LV VLSI Circuits 5

Introduction

Questions:

1. The average number of connections for one

block is 72 pins. The chip has six block. Find the

number of external connections if p=0.6

2. A 360 legged chip has K blocks with 10

terminals each. If p = 0.7, find the K.

Ngeze, LV VLSI Circuits 6

Introduction

Ω The decrease in feature size results in chips

with higher I/O count and more interconnections

to the silicon

Ω The chip is to be made as small as possible and

placed into high density packages requiring

smaller lead spacing

Ω The package design is also required to provide

good heat dissipation

Good electrical performance and

high reliability

Ngeze, LV VLSI Circuits 7

Wafer Assembly Techniques

Ω The assembly sequence for plastic and ceramic

packages include:

1. Wafer preparations

Wafer backgrinding, wafer slicing, and wafer

handling are of utmost importance

Thicker wafers place more demand on the

separation process and on VLSI package design

and assembly process

Diamond wheel dicing method is used nowdays to

have better quality cuts that allowthe narrowing of

streets and improved capability for cutting through

dissimilar materials

Ngeze, LV VLSI Circuits 8

Wafer Assembly Techniques

2. Die interconnection

The back of the die is mechanically attached to an

appropriate mount medium

Bond pads on the circuit side of the die are

electrically connected to the package

3. Die bonding

Requires thermal and stress management for large

dies

Eutectic die bonding

Epoxy die bonding

Ngeze, LV VLSI Circuits 9

Wafer Assembly Techniques

4. Wire bonding

This step follows after die bonding

Gold wire is ball-wedge bonded

Symmetrical geometry of the capillary tip is used

Ngeze, LV VLSI Circuits 10

Packaging of VLSI

What is Packaging of VLSI?

Ω It is the science and the art of establishing

interconnections and a suitable operating environment

for predominantly electrical circuits.

Ngeze, LV VLSI Circuits 11

Packaging of VLSI

Need for Packaging?

ΩIt supplies the chips with wires to

1. distribute signals and power,

2. remove the heat generated by the circuits, and

3. provide them with physical support and

environmental protection.

ΩIt plays an important role in determining the

performance, cost, and reliability of the system.

Ngeze, LV VLSI Circuits 12

Electronic Packaging Requirements

Ω Speed

Large bandwidth

Short inter-chip propagation delay

Ω Size

Compact size

Ω Thermal & Mechanical Properties

High heat removal rate

A good match between the thermal coefficients of the dice and

the chip carrier

Ω Test & Reliability

Easy to test

Easy to modify

Highly reliable

Low cost Ngeze, LV VLSI Circuits 13

Electronic Packaging Requirements

Ω Pin Count

Large I/O count per chip

Large I/O between the first and second level

package

Ω Noise

Low noise coupling among wires

Good-quality transmission line

Good power distribution

Ngeze, LV VLSI Circuits 14

Packaging Hierarchy

Ω The semiconductor chip is encapsulated into a

package, which constitutes the first level of

packaging.

Ω A printed circuit board is usually employed

because the total circuit and bit count required

might exceed that available on a single first-

level package.

Ω Further, there may be components that cannot

be readily integrated on first-level package,

such as capacitors, high power resistors,

inductors, etc

Ngeze, LV VLSI Circuits 15

Packaging Hierarchy

Ω Several levels of packaging will be present.

Ω They are often referred to as a packaging

hierarchy.

Ω The number of levels within a hierarchy may

vary, depending on the degree of integration

and the totality of packaging needs

Ngeze, LV VLSI Circuits 16

Packaging Hierarchy

Ω Package Hierarchy

Ngeze, LV VLSI Circuits 17

Package Design Considerations

(Parameters)

Number of Terminals

Ω The total number of terminals at packaging

interfaces is a major cost factor.

Ω Signal interconnections and terminals constitute

the majority of conducting elements.

Ω Other conductors supply power and provide

ground or other reference voltages.

Ngeze, LV VLSI Circuits 18

Package Design Considerations

(Parameters)

Electrical Design Considerations

Ω Electrical performance at the IC package level is of

great importance for microwave designs

Ω As a signal propagates through the package, it is

degraded due to reflections and line resistance.

Ω Control of the resistance and the inductance associated

with the power and ground distribution paths to combat

ground bounce and the simultaneous switching noise is

needed

Ngeze, LV VLSI Circuits 19

Package Design Considerations

(Parameters)

Thermal Design Considerations

Ω Needed to keep the operating junction

temperature of a silicon chip low

Ω The package should provide a good medium for

heat transfer from junction to the ambient/heat

sink.

Ω The junction temperature should be kept below

150°C to ensure proper electrical performance

and to contain the propensity to fail

Ngeze, LV VLSI Circuits 20

Package Design Considerations

(Parameters)

Reliability

Ω The package should have good

thermomechanical performance for better

reliability.

Testability

Ω Several tests are employed to assess the

reliability of the packages

Ngeze, LV VLSI Circuits 21

IC Packages

Ω An IC package falls into two basic categories.

1. Single-layer technology

the package is constructed around the IC chip on a

lead frame.

the IC chip is first mechanically bonded to a lead

frame,

It is then electrically interconnected with fine wires

from the chip bond pads to the corresponding lead-

frame fingers.

The final package is then constructed around the

lead-frame subassembly

Ngeze, LV VLSI Circuits 22

IC Packages

2. Multi-layer technology

The IC chip is assembled into a prefabricated

package

Ω Two single-layer technologies are used in the

industry:

1. molded plastic and

2. glass-sealed pressed ceramic.

Ngeze, LV VLSI Circuits 23

IC Packages

Plastic Packaging

Ω Plastic is a generic term for a host of man-made organic

polymers.

Ω Polymer materials are relatively porous structures,

which may allow absorption or transport of water

molecules and ions

Ceramic Packaging

Ω Pressed ceramic technology packages are used mainly

for economically encapsulating ICs and semiconductor

devices

Ω Silicon carbide (SiC), aluminum nitride, beryllia (BeO),

and alumina (Al2O3) are some of the ceramics used in

electronic packaging

Ngeze, LV VLSI Circuits 24

Package Types

Ω IC packages have been developed over time to

meet the requirements of high speed and

density.

Ω These are classified as follows:

Ngeze, LV VLSI Circuits 25

Package Types

1. Through Hole Packages

Ω Through-the-board hole mounting technology uses

precision holes drilled through the board and plated

with copper.

Ω This copper plating forms the connections between

separate layers.

Ω These layers consist of thin copper sheets stacked

together and insulated by epoxy fiberglass.

Ω There are no dedicated via structures to make

connections between wiring levels; through holes

serve that purpose.

Ngeze, LV VLSI Circuits 26

Package Types

Ω Different types of through hole packages can be

further classified as:

(a) Dual-in-Line Packages (DIPs)

(b) Quad Flat Packages (QFPs)

(c) Pin Grid Arrays (PGA)

Ngeze, LV VLSI Circuits 27

Package Types

(a) Dual-in-Line Packages (DIPs)

Ω A dual-in-line package is a rectangular package

with two rows of pins in its two sides.

Ω DIPs are the workhorse of the high-volume and

general-purpose logic products.

Ngeze, LV VLSI Circuits 28

Package Types

(b) Quad Flat Packages (QFPs)

Ω DIP package has become up to 50 times larger than the

bare die size itself, thus defeating the objective of

shrinking the size of the integrated circuits.

Ω It provides pins all around.

Ω In QFPs, pins are provided on all four sides.

Ω Thin QFPs are developed to reduce the weight of the

package.

Ngeze, LV VLSI Circuits 29

Package Types

(c) Pin Grid Arrays (PGA)

Ω A pin grid array has leads on its entire bottom surface

rather than only at its periphery.

Ω It offers a much larger pin count.

Ω It has cavity-up and cavity-down versions.

Ω High pin count and larger power dissipation capability of

PGAs make them attractive for different types of

packaging.

Ngeze, LV VLSI Circuits 30

Package Types

2. Surface-Mounted Packages

ΩSurface mounting solves many of the shortcomings of

through-the-board mounting.

ΩA chip carrier is soldered to the pads on the surface of a

board without requiring any through holes.

ΩThe smaller component sizes, lack of through holes, and

the possibility of mounting chips on both sides of the PC

board improve the board density.

ΩTypes of surface-mount packages are available

a) Small-Outline Packages (SOPs)

b) Plastic-leaded Chip Carriers (PLCCs)

c) Leadless Ceramic Chip Carriers (LCCCs)

Ngeze, LV VLSI Circuits 31

Package Types

(a) Small-Outline Packages (SOPs)

Ω The small-outline package has gull-wing shaped leads.

Ω It requires less pin spacing than through hole mounted

DIPs and PGAs.

Ω SOP packages usually have small lead counts and are

used for discrete, analog, and SSI/MSI logic parts.

Ngeze, LV VLSI Circuits 32

Package Types

(b) Plastic-leaded Chip Carriers (PLCCs)

Ω PLCCs such as gull-wing and J-leaded chip carriers,

offer higher pin counts than SOP.

Ω J-leaded chip carriers pack denser and are more

suitable for automation than gull-wing leaded carriers

because their leads do not extend beyond the package.

Ngeze, LV VLSI Circuits 33

Package Types

(c) Leadless Ceramic Chip Carriers (LCCCs)

Ω LCCCs take advantage of multilayer ceramic technology.

Ω The conductors are left exposed around the package

periphery to provide contacts for surface mounting.

Ω The ceramic substrate also has a high thermal

conductivity.

Ngeze, LV VLSI Circuits 34

Package Types

3. Flip-Chip Packages

Ω The length of the electrical connections between the

chip and the substrate can be minimized by placing

solder bumps on the dice, flipping the chips over,

aligning them with the contacts pads on the substrate,

and reflowing the solder balls in a furnace to establish

the bonding between the chips and the package.

Ω This method provides electrical connections with minute

parasitic inductance and capacitance.

Ω Contact pads are distributed over the entire chip

surface.

Ngeze, LV VLSI Circuits 35

Package Types

Ω This flipping

saves silicon area,

increases the maximum I/O and power/ground

terminals available with a given die size, and

provides more efficiently routed signal and

power/ground interconnections on the chips.

Ngeze, LV VLSI Circuits 36

Package Types

4. Chip Size Packages (CSPs)

ΩTo combine the advantages of both packaged

chip and bare chip in one solution, a variety of

CSPs have been developed.

ΩCSPs can be divided into two categories: the

fan-in type and the fan-out type.

1. Fan-in type CSPs are suitable for memory

applications that have relatively low pin counts.

2. The fan-out CSPs are used mainly for logic

applications: because of the die size to pin count

ratio, the solder bumps cannot be designed within

the chip area.

Ngeze, LV VLSI Circuits 37

Package Types

Ω CSP Package

Ngeze, LV VLSI Circuits 38

Package Types

5. Multi-Chip Modules (MCMs)

Ω Several chips are supported on a single

package.

Ω Most multi-chip packages are made of ceramic.

Ω By eliminating one level of packaging, the

inductance and capacitance of the electrical

connections among the dice are reduced.

Ω Usually, the dice are mounted on a multilayer

ceramic substrate via solder bumps, and the

ceramic substrate offers a dense

interconnection network

Ngeze, LV VLSI Circuits 39

Package Types

Ngeze, LV VLSI Circuits 40

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Definitions of Each of The 20 Tools of Process ControlDokument2 SeitenDefinitions of Each of The 20 Tools of Process Control88No1FanNoch keine Bewertungen

- Wifi Smart Net Camera V380Dokument3 SeitenWifi Smart Net Camera V380Bernard Mkumbwa Jr.Noch keine Bewertungen

- TN 423: Vlsi Circuits: Lecture 6dDokument21 SeitenTN 423: Vlsi Circuits: Lecture 6dBernard Mkumbwa Jr.Noch keine Bewertungen

- TN 423: Vlsi Circuits: Lecture 9aDokument41 SeitenTN 423: Vlsi Circuits: Lecture 9aBernard Mkumbwa Jr.Noch keine Bewertungen

- TN 423: Vlsi Circuits: Lecture 7bDokument49 SeitenTN 423: Vlsi Circuits: Lecture 7bBernard Mkumbwa Jr.Noch keine Bewertungen

- TN 423: Vlsi Circuits: Lecture 7aDokument24 SeitenTN 423: Vlsi Circuits: Lecture 7aBernard Mkumbwa Jr.Noch keine Bewertungen

- Lecture 6aDokument24 SeitenLecture 6aBernard Mkumbwa Jr.Noch keine Bewertungen

- TN 423: Vlsi Circuits: Lecture 6cDokument35 SeitenTN 423: Vlsi Circuits: Lecture 6cBernard Mkumbwa Jr.Noch keine Bewertungen

- TN 423: Vlsi Circuits: Introduction To SiliconDokument16 SeitenTN 423: Vlsi Circuits: Introduction To SiliconBernard Mkumbwa Jr.Noch keine Bewertungen

- TN 423: Vlsi CircuitsDokument45 SeitenTN 423: Vlsi CircuitsBernard Mkumbwa Jr.Noch keine Bewertungen

- TN 423: Vlsi Circuits: Lecture 4bDokument43 SeitenTN 423: Vlsi Circuits: Lecture 4bBernard Mkumbwa Jr.Noch keine Bewertungen

- TN 423: Vlsi Circuits: Lecture 4aDokument36 SeitenTN 423: Vlsi Circuits: Lecture 4aBernard Mkumbwa Jr.Noch keine Bewertungen

- TN 423: Vlsi Circuits: Silicon WafersDokument23 SeitenTN 423: Vlsi Circuits: Silicon WafersBernard Mkumbwa Jr.Noch keine Bewertungen

- Vlsi Circuits: 10 CreditsDokument69 SeitenVlsi Circuits: 10 CreditsBernard Mkumbwa Jr.Noch keine Bewertungen

- Application Note: Docsis 3.1Dokument24 SeitenApplication Note: Docsis 3.1Bernard Mkumbwa Jr.Noch keine Bewertungen

- Intership SeminarDokument18 SeitenIntership SeminarChandan K HNoch keine Bewertungen

- CHD Candidate Guidebook PDFDokument20 SeitenCHD Candidate Guidebook PDFsyammc0% (1)

- 5S Implementation Copy 1 AutoRecoveredDokument8 Seiten5S Implementation Copy 1 AutoRecoveredChristian BarrientosNoch keine Bewertungen

- M. of St. Lighting Poles Installation & Related LCPDokument18 SeitenM. of St. Lighting Poles Installation & Related LCPWaleed Salih100% (1)

- Plantronics Voyager Pro Plus ManualDokument10 SeitenPlantronics Voyager Pro Plus Manualbsd_storesNoch keine Bewertungen

- Huawei ActixOne 20110530 Use Case V3 PDFDokument66 SeitenHuawei ActixOne 20110530 Use Case V3 PDFsolarisan6Noch keine Bewertungen

- QR Code Reader and ScannerDokument6 SeitenQR Code Reader and ScannerNgwang Leonard Tenzi100% (1)

- EE610: CMOS Analog EE610: CMOS Analog Circuits: L3: MOS Models-3Dokument47 SeitenEE610: CMOS Analog EE610: CMOS Analog Circuits: L3: MOS Models-3Epili Rajkiran SarabaNoch keine Bewertungen

- Exsite Ip Pant Tilt System Spec SheetDokument8 SeitenExsite Ip Pant Tilt System Spec SheetAnuj PalNoch keine Bewertungen

- Module 5Dokument80 SeitenModule 5Big Brown BeastNoch keine Bewertungen

- Bajaj Auto LTD Pulsar 180 Ug 4 Es Bsiii Usg Automobiles Pvt. LTDDokument1 SeiteBajaj Auto LTD Pulsar 180 Ug 4 Es Bsiii Usg Automobiles Pvt. LTDzaid AhmedNoch keine Bewertungen

- Joaquín Vélez: 1 HOTEL CENTRAL PARK - NYC - Construction EngineerDokument2 SeitenJoaquín Vélez: 1 HOTEL CENTRAL PARK - NYC - Construction EngineerVaé RiberaNoch keine Bewertungen

- Configuring SNMP On ProteusDokument12 SeitenConfiguring SNMP On ProteusAijaz MirzaNoch keine Bewertungen

- InfoSys Interview Questions For APIDokument3 SeitenInfoSys Interview Questions For APIVijjuNoch keine Bewertungen

- ClickFunnels Vs WebsiteDokument2 SeitenClickFunnels Vs WebsiteJOEYNoch keine Bewertungen

- Potopna Crpka PEDROLLO VXC Vortex BrosuraDokument4 SeitenPotopna Crpka PEDROLLO VXC Vortex Brosurajose03Noch keine Bewertungen

- QL 320 TDokument109 SeitenQL 320 TSteven SalweyNoch keine Bewertungen

- ConveyersDokument10 SeitenConveyersSai Srinivas BodapatiNoch keine Bewertungen

- Smart Fire Alarm System Using ArduinoDokument2 SeitenSmart Fire Alarm System Using Arduinokritwik barua100% (1)

- Piping Specification For WSA Plants (ASME)Dokument33 SeitenPiping Specification For WSA Plants (ASME)Widian RienandaNoch keine Bewertungen

- Certificado Apc Iso 14001-2004 PDFDokument4 SeitenCertificado Apc Iso 14001-2004 PDFMao MartinNoch keine Bewertungen

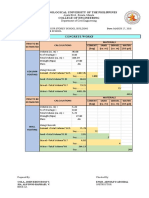

- 2 Concrete Works CompuDokument14 Seiten2 Concrete Works CompuALFONSO RAPHAEL SIANoch keine Bewertungen

- 3161 Governor: For Control of Engines and Steam TurbinesDokument4 Seiten3161 Governor: For Control of Engines and Steam TurbinesWilliam's SalgadoNoch keine Bewertungen

- Nha Balut Tondo Manila - Less 1tDokument20 SeitenNha Balut Tondo Manila - Less 1tTechnical Unit SjmdoNoch keine Bewertungen

- History of ComputerDokument4 SeitenHistory of ComputerJaren QueganNoch keine Bewertungen

- Farman Ullah: PersonalDokument3 SeitenFarman Ullah: PersonalArslan ShafiNoch keine Bewertungen

- Bhel Summer Training (Industrial Training) ReportDokument35 SeitenBhel Summer Training (Industrial Training) ReportAmelia WarnerNoch keine Bewertungen

- Contoh P&IDDokument1 SeiteContoh P&IDLudy Oji PrastamaNoch keine Bewertungen

- Airport Qualification and Familiarization ChartsDokument3 SeitenAirport Qualification and Familiarization Chartsjackygdp645Noch keine Bewertungen