Beruflich Dokumente

Kultur Dokumente

Prasun Ghosal: Computer Organization and Architecture

Hochgeladen von

AnindyaKundu0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

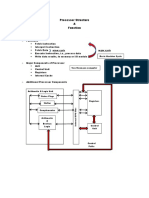

24 Ansichten3 SeitenThe document discusses key concepts in computer organization and architecture. It defines common components of a computer system like the CPU, memory, registers, buses, and I/O devices. It also explains the fetch-decode-execute cycle of instruction processing, different types of interrupts, and concurrency models like single-CPU time-sharing and multi-CPU parallel processing. Common operations like data transfer between CPU and memory are also outlined.

Originalbeschreibung:

CPU Interrupt and I/O

Originaltitel

Cpu Interrupt

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenThe document discusses key concepts in computer organization and architecture. It defines common components of a computer system like the CPU, memory, registers, buses, and I/O devices. It also explains the fetch-decode-execute cycle of instruction processing, different types of interrupts, and concurrency models like single-CPU time-sharing and multi-CPU parallel processing. Common operations like data transfer between CPU and memory are also outlined.

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

24 Ansichten3 SeitenPrasun Ghosal: Computer Organization and Architecture

Hochgeladen von

AnindyaKunduThe document discusses key concepts in computer organization and architecture. It defines common components of a computer system like the CPU, memory, registers, buses, and I/O devices. It also explains the fetch-decode-execute cycle of instruction processing, different types of interrupts, and concurrency models like single-CPU time-sharing and multi-CPU parallel processing. Common operations like data transfer between CPU and memory are also outlined.

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 3

Computer Organization and Architecture

Prasun Ghosal

Operational code / opcode Instruction fetch Running state

Instruction decode Halt state

Opcode + operand / address Operand fetch Software halt

Execute Halt input

Auto shutdown

Opcode + I operand / address +II operand / Store the result

address

Accumulator (AC) Frequency Every instruction specifies a macro operation

Program Counter (PC) Time period to be performed by the CPU

Memory address register (MAR) Duty cycle Opcode

Memory buffer register (MBR) Instruction set

Instruction register (IR) A clock signal has a frequency of 5 GHz with

General purpose register (GPR) a duty cycle of 40%. Calculate its period and Toexecute an instruction CPU has to perform

I/O data register (IODR)

pulse width. several micro operations.

Clearing a register, incrementing a counter etc.

I/O address register (IOAR)

Anevent inside a computer system requiring External Nested interrupts

some urgent action by the CPU External hardware error Interrupt priority

CPU suspends the current program execution IO interrupt Interrupt masking

Branches to an ISR NMI

Non-maskable interrupt

Common types | Data transfer

Power fail

| End of I/O

I/O completion Memory parity error

Data transfer Internal

Bus cycle malfunction

Overflow Hardware

| Error in CPU hardware

| Program exceptions (overflow, illegal opcode etc.)

Software (INT instruction)

Data transfer Instructionfrom memory to CPU A single CPU multiplexes among multiple

Through CPU (SW) Data from memory to CPU programs executing them concurrently; all

| Programmed mode

Data from CPU to memory

programs stay in a common memory

| Interrupt mode

Memory address from CPU to memory

Bypassing CPU (HW)

| DMA mode Port address from CPU to I/O controllers

Command from CPU to I/O controllers

Status from I/O controllers to CPU

Morethan one CPU in a single system with

each CPU executing a different program;

each CPU may have a separate memory or all

CPUs may share a common memory

Das könnte Ihnen auch gefallen

- Diab Computer 3Dokument41 SeitenDiab Computer 3RadNoch keine Bewertungen

- InputOutput Interfacing - Lec 4Dokument22 SeitenInputOutput Interfacing - Lec 4Danu NimNoch keine Bewertungen

- CTMT Chap 07.processor Structure and FunctionDokument38 SeitenCTMT Chap 07.processor Structure and FunctionTrần Đình Minh KhoaNoch keine Bewertungen

- Processor Structure and FunctionDokument55 SeitenProcessor Structure and Functionmutia sabrina100% (1)

- William Stallings Computer Organization and Architecture 9 EditionDokument55 SeitenWilliam Stallings Computer Organization and Architecture 9 EditionshahbaadshahNoch keine Bewertungen

- (Advanced) Computer Architechture Prof. Dr. Hasan Hüseyin BALIK (3 Week)Dokument47 Seiten(Advanced) Computer Architechture Prof. Dr. Hasan Hüseyin BALIK (3 Week)فقد الاحبه غربةNoch keine Bewertungen

- Chapter 3 Third Week 2021Dokument45 SeitenChapter 3 Third Week 2021sumeraNoch keine Bewertungen

- Lecture 1 Computer OrgDokument26 SeitenLecture 1 Computer OrgmalNoch keine Bewertungen

- CH14 COA9e Processor Structure and FunctionDokument40 SeitenCH14 COA9e Processor Structure and FunctionTuấnNoch keine Bewertungen

- Slot04 05 CH03 TopLevelView 38 SlidesDokument38 SeitenSlot04 05 CH03 TopLevelView 38 SlidesĐạt TrầnNoch keine Bewertungen

- Device Communication: I/O Module FunctionDokument3 SeitenDevice Communication: I/O Module FunctionJackey ChuaNoch keine Bewertungen

- COA Lecture 23 Interupt Driven Io PDFDokument15 SeitenCOA Lecture 23 Interupt Driven Io PDFA3 AashuNoch keine Bewertungen

- Architecture IIDokument158 SeitenArchitecture IIGafeer FableNoch keine Bewertungen

- William Stallings Computer Organization and Architecture 9 EditionDokument23 SeitenWilliam Stallings Computer Organization and Architecture 9 Editionyusha habibNoch keine Bewertungen

- Vision de Alto Nivel Del Computador V5 PDFDokument52 SeitenVision de Alto Nivel Del Computador V5 PDFGARY DAVID TRUJILLO MOTATO100% (1)

- ZCC Group - Embedded Mbedded System Research & Development Evelopment LabDokument1 SeiteZCC Group - Embedded Mbedded System Research & Development Evelopment LabA2IT Pvt. Ltd.Noch keine Bewertungen

- WINSEM2023-24 BCSE205L TH VL2023240500897 2024-03-18 Reference-Material-IDokument40 SeitenWINSEM2023-24 BCSE205L TH VL2023240500897 2024-03-18 Reference-Material-Iprathampalgandhi10Noch keine Bewertungen

- Slot04 05 CH03 TopLevelView 38 SlidesDokument38 SeitenSlot04 05 CH03 TopLevelView 38 Slidestuan luuNoch keine Bewertungen

- Slide #5Dokument32 SeitenSlide #5lewjw-wm22Noch keine Bewertungen

- Computer-System StructuresDokument37 SeitenComputer-System StructuresHamoodi AlmayahiNoch keine Bewertungen

- Microprocessor Based Systems: Lecture No 03 Introduction To Von Neumann ArchitectureDokument32 SeitenMicroprocessor Based Systems: Lecture No 03 Introduction To Von Neumann ArchitectureMuhammad ZubairNoch keine Bewertungen

- Oprating Syste Chap 3Dokument25 SeitenOprating Syste Chap 3zerihun nanaNoch keine Bewertungen

- WilliamStallings Chp3 PDFDokument60 SeitenWilliamStallings Chp3 PDFAlfonsus devinNoch keine Bewertungen

- Slot04 05 CH03 TopLevelView 38 SlidesDokument38 SeitenSlot04 05 CH03 TopLevelView 38 SlidesTruong Huu Nhat (K17 HL)Noch keine Bewertungen

- Direct Memory Access DMA PDFDokument15 SeitenDirect Memory Access DMA PDFdevendra prasadNoch keine Bewertungen

- ٣محاضرات أساسيات نضام الحاسوبDokument10 Seiten٣محاضرات أساسيات نضام الحاسوبmuazalamri2006Noch keine Bewertungen

- Lec - 6 InterruptsDokument76 SeitenLec - 6 Interruptsjarvis 1011Noch keine Bewertungen

- ELEC3300 06 InterruptDokument38 SeitenELEC3300 06 InterruptKeith wongNoch keine Bewertungen

- 01 - Mod 2 - Livro AutorresponsabilidadeDokument9 Seiten01 - Mod 2 - Livro AutorresponsabilidadeNillyNoch keine Bewertungen

- William Stallings Computer Organization and Architecture 9 EditionDokument60 SeitenWilliam Stallings Computer Organization and Architecture 9 EditionFahmida RahmanNoch keine Bewertungen

- Presentatio N ON Fundamenta LS OF ComputersDokument26 SeitenPresentatio N ON Fundamenta LS OF ComputersrajamrajuvNoch keine Bewertungen

- Computer Arch. & Organization - I: The Basic Organization of ComputersDokument33 SeitenComputer Arch. & Organization - I: The Basic Organization of Computerssaksham0506Noch keine Bewertungen

- Input Output9 6 2021Dokument53 SeitenInput Output9 6 2021zkd9n8f6kfNoch keine Bewertungen

- Lesson 1 - Basic Computer OrganizationDokument17 SeitenLesson 1 - Basic Computer OrganizationSteph Kier PonterasNoch keine Bewertungen

- I/O: Connecting To Outside World: So Far, We've Learned How ToDokument8 SeitenI/O: Connecting To Outside World: So Far, We've Learned How ToTrần LouisNoch keine Bewertungen

- Module 10 - IO SystemsDokument46 SeitenModule 10 - IO Systemshexeko8100Noch keine Bewertungen

- Chapter 3 - A Top Level View of Computer Function and InterconnectionDokument38 SeitenChapter 3 - A Top Level View of Computer Function and InterconnectionKhang NguyenNoch keine Bewertungen

- CH03 A Top Level View of ComputerDokument37 SeitenCH03 A Top Level View of ComputerDương DũngNoch keine Bewertungen

- CH03 COA9e A Top Level View of ComputerDokument37 SeitenCH03 COA9e A Top Level View of ComputerHuy ChuNoch keine Bewertungen

- 2019 2020 CSE206 Week04 Ch3 Computer SystemsDokument46 Seiten2019 2020 CSE206 Week04 Ch3 Computer Systemstemhem racuNoch keine Bewertungen

- 3.hardware and Software InterruptsDokument23 Seiten3.hardware and Software Interruptsyogeshwari bahiramNoch keine Bewertungen

- COA Lecture 6Dokument27 SeitenCOA Lecture 6Saifi SulehriNoch keine Bewertungen

- Introduction Part 2 - Lec 1Dokument58 SeitenIntroduction Part 2 - Lec 1Danu NimNoch keine Bewertungen

- A394982016 16523 11 2019 Chapter8.00Dokument39 SeitenA394982016 16523 11 2019 Chapter8.00yogesh kumarNoch keine Bewertungen

- Introduction To Microcontrollers: ECE473/573 Microprocessor System Design, Dr. Shiue 1Dokument14 SeitenIntroduction To Microcontrollers: ECE473/573 Microprocessor System Design, Dr. Shiue 1zaheer_ahamed2000Noch keine Bewertungen

- William Stallings Computer Organization and Architecture 9 EditionDokument60 SeitenWilliam Stallings Computer Organization and Architecture 9 EditionmisbahNoch keine Bewertungen

- MES (Mod-1)Dokument59 SeitenMES (Mod-1)Sathwik Rao KNoch keine Bewertungen

- Data Structures Through C LanguageDokument75 SeitenData Structures Through C LanguageMuhammadNoch keine Bewertungen

- Computer Organization and Architecture: William StallingsDokument78 SeitenComputer Organization and Architecture: William StallingsNITHIYA PAUL 1847244Noch keine Bewertungen

- 02 Computer StructureDokument81 Seiten02 Computer StructureA.Selçuk TunçerNoch keine Bewertungen

- Chapter 2 (Part II) - Instruction Sets (Characteristics and Functions)Dokument49 SeitenChapter 2 (Part II) - Instruction Sets (Characteristics and Functions)Kirubel EsayasNoch keine Bewertungen

- Input Output TechniquesDokument65 SeitenInput Output Techniquesvivek srivastavNoch keine Bewertungen

- Processes: Process ManagementDokument17 SeitenProcesses: Process ManagementCrystal ClearNoch keine Bewertungen

- Unit 4Dokument48 SeitenUnit 4Anmol D. PradhanNoch keine Bewertungen

- Slot04 05 CH03 TopLevelView 38 SlidesDokument39 SeitenSlot04 05 CH03 TopLevelView 38 Slideshuynq.ce190715Noch keine Bewertungen

- 02 Computer StructureDokument56 Seiten02 Computer StructureFurkan TopaloğluNoch keine Bewertungen

- UNIT 6 Input-Output-OrganizationDokument25 SeitenUNIT 6 Input-Output-OrganizationSaranya Priyanka100% (1)

- Slides 1Dokument20 SeitenSlides 1Muhammad yousufNoch keine Bewertungen

- Estimation of ParametersDokument47 SeitenEstimation of ParametersAnindyaKunduNoch keine Bewertungen

- 3 Semester: Information TechnologyDokument6 Seiten3 Semester: Information TechnologyAnindyaKunduNoch keine Bewertungen

- Random VariablesDokument53 SeitenRandom VariablesAnindyaKunduNoch keine Bewertungen

- Ac NotesDokument4 SeitenAc NotesAnindyaKunduNoch keine Bewertungen

- Bit W Terrte-L: Po/l'v'nzatry'Dokument6 SeitenBit W Terrte-L: Po/l'v'nzatry'AnindyaKunduNoch keine Bewertungen

- IIEST Brochure 17-18Dokument19 SeitenIIEST Brochure 17-18AnindyaKunduNoch keine Bewertungen

- Find The Value of (A) (B) 0.2 Log 125 2 Log 1024 (C) (D) 6 Log 36 5 2 Log 4.log 5Dokument2 SeitenFind The Value of (A) (B) 0.2 Log 125 2 Log 1024 (C) (D) 6 Log 36 5 2 Log 4.log 5AnindyaKunduNoch keine Bewertungen

- LogarithmsDokument2 SeitenLogarithmsAnindyaKunduNoch keine Bewertungen

- Manual para Tarjeta Reguladora de Voltaje AVR MX321Dokument6 SeitenManual para Tarjeta Reguladora de Voltaje AVR MX321Rodrigo ObregonNoch keine Bewertungen

- A Tracer Study On Btte GraduatesDokument15 SeitenA Tracer Study On Btte GraduatesOzalleAngryBertNoch keine Bewertungen

- Technical Manual Operator'S and Unit Maintenance Manual FOR Firing Device, Demolition. M122 (NSN 1375-01-021-0606) (EIC: 2NA)Dokument7 SeitenTechnical Manual Operator'S and Unit Maintenance Manual FOR Firing Device, Demolition. M122 (NSN 1375-01-021-0606) (EIC: 2NA)Михаил НаумовNoch keine Bewertungen

- Filtration 2Dokument5 SeitenFiltration 2Ramon Dela CruzNoch keine Bewertungen

- Bearer Independent Call Control Protocol (Cs2) and Signalling System No.7 - Isdn User Part General Functions of Messages and ParametersDokument31 SeitenBearer Independent Call Control Protocol (Cs2) and Signalling System No.7 - Isdn User Part General Functions of Messages and Parameterssahil_chandna25Noch keine Bewertungen

- Proposal Tripurainfo Job PortalDokument10 SeitenProposal Tripurainfo Job PortalEkta DevNoch keine Bewertungen

- Manual de TallerDokument252 SeitenManual de TallerEdison RodriguezNoch keine Bewertungen

- Computer Science - Paper 1 - Mock 1Dokument10 SeitenComputer Science - Paper 1 - Mock 1uththaramala calderaNoch keine Bewertungen

- Kumar Saurabh Resume (SAP IBP)Dokument6 SeitenKumar Saurabh Resume (SAP IBP)SaurabhSinhaNoch keine Bewertungen

- MT Company PresentationDokument30 SeitenMT Company Presentationjose manuelNoch keine Bewertungen

- The Manuals Com Cost Accounting by Matz and Usry 9th Edition Manual Ht4Dokument2 SeitenThe Manuals Com Cost Accounting by Matz and Usry 9th Edition Manual Ht4ammarhashmi198633% (12)

- Open XPS Support in Windows 8: WhitePaperDokument24 SeitenOpen XPS Support in Windows 8: WhitePaperDeepak Gupta (DG)Noch keine Bewertungen

- Samtec ASP 134488 01 DatasheetDokument4 SeitenSamtec ASP 134488 01 DatasheetamiteshtripathiNoch keine Bewertungen

- Presentation DIP5000 enDokument31 SeitenPresentation DIP5000 enNeelakandan MasilamaniNoch keine Bewertungen

- Module 3 Lesson 1 Edited For CBL Lesson ContentDokument3 SeitenModule 3 Lesson 1 Edited For CBL Lesson ContentMariecris BatasNoch keine Bewertungen

- Multiquadrant Dynamics in The Speed-Torque PlaneDokument41 SeitenMultiquadrant Dynamics in The Speed-Torque PlanethanvandhNoch keine Bewertungen

- Cap 1Dokument10 SeitenCap 1Oscar Bello LemusNoch keine Bewertungen

- صيانة المولدات و المحولات الكهربائيهDokument15 Seitenصيانة المولدات و المحولات الكهربائيهMostafa AllamNoch keine Bewertungen

- Europa Universalis IV CheatsDokument7 SeitenEuropa Universalis IV CheatsZamri Bin RadzaliNoch keine Bewertungen

- ACC Flow Chart (Whole Plan) - Rev00Dokument20 SeitenACC Flow Chart (Whole Plan) - Rev00amandeep12345Noch keine Bewertungen

- Literature Study Nift ChennaiDokument5 SeitenLiterature Study Nift ChennaiAnkur SrivastavaNoch keine Bewertungen

- CM Line Catalog ENUDokument68 SeitenCM Line Catalog ENUdmugalloyNoch keine Bewertungen

- MSDS EmaxDokument10 SeitenMSDS EmaxAnonymous mfKWzk1UNoch keine Bewertungen

- Advanced Microscopy Simplifi Ed: Bx53M/BxfmDokument28 SeitenAdvanced Microscopy Simplifi Ed: Bx53M/BxfmRepresentaciones y Distribuciones FALNoch keine Bewertungen

- BDM DriverDokument16 SeitenBDM DrivervolvodiagNoch keine Bewertungen

- ElinkDokument36 SeitenElinkjosemanuelarangoNoch keine Bewertungen

- A White Paper On IExpense Features in R12Dokument17 SeitenA White Paper On IExpense Features in R12Balaji ShindeNoch keine Bewertungen

- Scan 0001Dokument1 SeiteScan 0001ochiroowitsNoch keine Bewertungen

- From To: Airtel Logo Change: Does It Make Marketing SenseDokument3 SeitenFrom To: Airtel Logo Change: Does It Make Marketing SenseAvinash HaryanNoch keine Bewertungen