Beruflich Dokumente

Kultur Dokumente

CH-4 Register Transfer and Microoperation Assignment PDF

Hochgeladen von

Bhaumik MuliyaOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

CH-4 Register Transfer and Microoperation Assignment PDF

Hochgeladen von

Bhaumik MuliyaCopyright:

Verfügbare Formate

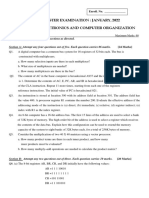

MARWADI UNIVERSITY

Faculty of Technology

Department of Information and Communication Technology

Computer Organization and Architecture (01CT0301)

Assignment

CH-4 Register Transfer and Microoperation

1. A digital computer has a common bus system for 16 registers of 32 bits each. The bus

is constructed with multiplexers.

a. How many selection inputs are there in each multiplexer?

b. What size of multiplexers are needed?

c. How many multiplexers are there in the bus?

2. The 4-bit adder-subtractor circuit with controlling input M has the following values

for data inputs A and B. In each case, determine the values of the outputs: S3, S2, S1,

S0 and C4.

3. Design a 4-bit combinational decrementer circuit using four full-adder circuits. This

circuit decrement input 4-bit data by one.

4. The 8-bit registers AR, BR, CR, and DR initially have the following values:

AR=11110010

BR=11111111

CR=10111001

DR=11101010

Determine the 8-bit values in each register after the execution of the following

sequence of microoperations.

a. AR AR + BR

b. CR CR /\ DR , BR BR + 1

c. AR AR – CR

5. If register A holds AF data. Mention content of register A after in Hexadecimal

number system

a. SHL A

b. SHR A

c. CIL A

d. CIR A

e. ASHL A

f. ASHR A

Das könnte Ihnen auch gefallen

- Multiplexer and DemultiplexerDokument5 SeitenMultiplexer and DemultiplexerAdebayo AdebariNoch keine Bewertungen

- Cardiovascular System Heart ReviewerDokument8 SeitenCardiovascular System Heart ReviewerImmanuel Cris PalasigueNoch keine Bewertungen

- 1.Gdpr - Preparation Planning GanttDokument6 Seiten1.Gdpr - Preparation Planning GanttbeskiNoch keine Bewertungen

- Anais Nin - Under A Glass Bell-Pages-29-32 WordDokument6 SeitenAnais Nin - Under A Glass Bell-Pages-29-32 WordArmina MNoch keine Bewertungen

- COA Assignment: This Assignment Consists of 10 Questions. Each Question Is of 5 MarksDokument3 SeitenCOA Assignment: This Assignment Consists of 10 Questions. Each Question Is of 5 Marksprakhar agrawalNoch keine Bewertungen

- Solution To Assignments For BScCSIT 3rd Semester (2069)Dokument8 SeitenSolution To Assignments For BScCSIT 3rd Semester (2069)Bijay MishraNoch keine Bewertungen

- QbankDokument3 SeitenQbankAnanthi RajkumarNoch keine Bewertungen

- Do Practice CODokument2 SeitenDo Practice COSudeep SharmaNoch keine Bewertungen

- Fifth WeekDokument1 SeiteFifth WeekRohit SaxenaNoch keine Bewertungen

- COA Assignment - 3Dokument2 SeitenCOA Assignment - 3KomalNoch keine Bewertungen

- 2629acomputer ArchitectureDokument15 Seiten2629acomputer ArchitectureSiddhant Jain SethNoch keine Bewertungen

- End Semester Examination: January, 2022 Digital Electronics and Computer OrganizationDokument3 SeitenEnd Semester Examination: January, 2022 Digital Electronics and Computer OrganizationFFFNoch keine Bewertungen

- Computer Organization and Architecture (01CE0402) Lab ManualDokument4 SeitenComputer Organization and Architecture (01CE0402) Lab ManualrockyNoch keine Bewertungen

- COA QuestionBank - 1Dokument3 SeitenCOA QuestionBank - 1itzzsandeshNoch keine Bewertungen

- CA Assignment IIDokument9 SeitenCA Assignment IISomesh ThakurNoch keine Bewertungen

- Mid 2 DLDDokument2 SeitenMid 2 DLDnskprasad89Noch keine Bewertungen

- COA WorksheetDokument1 SeiteCOA WorksheetAngesom DestaNoch keine Bewertungen

- E6995ca TutDokument14 SeitenE6995ca Tutrabinoss0% (1)

- Computer Applications and ManagementDokument11 SeitenComputer Applications and ManagementParag PaliwalNoch keine Bewertungen

- COA GTU Tutorial Solution Part 1Dokument4 SeitenCOA GTU Tutorial Solution Part 1HarmanjotSinghBhatia50% (2)

- Practice Sheet CDA-1Dokument6 SeitenPractice Sheet CDA-1brijesh.gec21Noch keine Bewertungen

- CN Assignment 1Dokument1 SeiteCN Assignment 1HacraloNoch keine Bewertungen

- UMA VLSI DesignDokument158 SeitenUMA VLSI DesignsallyNoch keine Bewertungen

- Shivalik College of Engineering Question Bank Computer Organization B.Tech II Year (IV Semester)Dokument5 SeitenShivalik College of Engineering Question Bank Computer Organization B.Tech II Year (IV Semester)Paras TilaraNoch keine Bewertungen

- CA-Assignment 2 - FinalDokument2 SeitenCA-Assignment 2 - Finaljixxy jaxNoch keine Bewertungen

- DSP Unit 1 To 5 QBDokument12 SeitenDSP Unit 1 To 5 QBSamuel WhiteNoch keine Bewertungen

- Microprocessor Microcontroller EXAM 2021 MGDokument11 SeitenMicroprocessor Microcontroller EXAM 2021 MGRene EBUNLE AKUPANNoch keine Bewertungen

- Question Bank Unit - V: Registers & Counters Part - A (Each Question Carries 1 Mark)Dokument9 SeitenQuestion Bank Unit - V: Registers & Counters Part - A (Each Question Carries 1 Mark)Nithya SNoch keine Bewertungen

- Microprocessor (ECE-3153)Dokument2 SeitenMicroprocessor (ECE-3153)RAHUL RTRNoch keine Bewertungen

- HT TP: //qpa Pe R.W But .Ac .In: 2011 Computer NetworksDokument7 SeitenHT TP: //qpa Pe R.W But .Ac .In: 2011 Computer NetworksNitin NileshNoch keine Bewertungen

- First Internal Question Bank SUB: DSPA (10TE74) DATE: 03/09/2014Dokument2 SeitenFirst Internal Question Bank SUB: DSPA (10TE74) DATE: 03/09/20149chand3Noch keine Bewertungen

- Es Unit 2 MCQDokument7 SeitenEs Unit 2 MCQPradnya NavaleNoch keine Bewertungen

- Workbook CS502 PDFDokument40 SeitenWorkbook CS502 PDFGaitonde GaneshNoch keine Bewertungen

- E-1 MCQ SYBCSDokument8 SeitenE-1 MCQ SYBCSOMNoch keine Bewertungen

- Te Oct 2014Dokument149 SeitenTe Oct 2014contrasterNoch keine Bewertungen

- Digital Logic QuestionsDokument6 SeitenDigital Logic Questionseidmoh1202Noch keine Bewertungen

- Network Basics CollectionDokument11 SeitenNetwork Basics Collectionrocks66aryanNoch keine Bewertungen

- BSC (H) CSHT II 204 Mid2012 Ddu Assignment IDokument2 SeitenBSC (H) CSHT II 204 Mid2012 Ddu Assignment IRavi RanjanNoch keine Bewertungen

- Coa Unit 1Dokument83 SeitenCoa Unit 1Shiv Patel 18-38Noch keine Bewertungen

- Maharana Pratap Group of Institutions Kanpur Microprocessor Unit-1 (Cs/Ee)Dokument3 SeitenMaharana Pratap Group of Institutions Kanpur Microprocessor Unit-1 (Cs/Ee)mmmnaNoch keine Bewertungen

- 8051 MCQDokument25 Seiten8051 MCQRohan Bachhav100% (1)

- In Computers, Subtraction Is Generally Carried Out byDokument2 SeitenIn Computers, Subtraction Is Generally Carried Out byatul211988Noch keine Bewertungen

- Assignment 1Dokument1 SeiteAssignment 1PULKIT KUMAR 21SCSE1420057Noch keine Bewertungen

- Axes - Placement Sample Question Papers: Micro ProcessorDokument7 SeitenAxes - Placement Sample Question Papers: Micro ProcessorNagaValliNoch keine Bewertungen

- Register Transfer and Micro-Operations UNIT-1Dokument53 SeitenRegister Transfer and Micro-Operations UNIT-1Anjan Kumar KantepalliNoch keine Bewertungen

- Unit 5 QBDokument11 SeitenUnit 5 QBAMAN SRIVASTAVA (RA2011030010057)Noch keine Bewertungen

- NetworkingDokument2 SeitenNetworkingNaveen MedisettyNoch keine Bewertungen

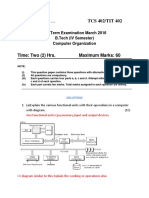

- Roll No TCS 402/TIT 402: Time: Two (2) Hrs. Maximum Marks: 60Dokument18 SeitenRoll No TCS 402/TIT 402: Time: Two (2) Hrs. Maximum Marks: 60Obsii ChalaNoch keine Bewertungen

- DSP Question BankDokument3 SeitenDSP Question BankNaveen HegdeNoch keine Bewertungen

- MCQ de 2022Dokument11 SeitenMCQ de 202201ABHIGYAN MAJINoch keine Bewertungen

- Digital ComminicationsDokument8 SeitenDigital ComminicationsAkbarSabNoch keine Bewertungen

- Com OrgDokument39 SeitenCom OrgDouaa M. AliNoch keine Bewertungen

- Question Bank of Unit-III COADokument4 SeitenQuestion Bank of Unit-III COAYamini BishtNoch keine Bewertungen

- ContdDokument2 SeitenContdchandra sekharNoch keine Bewertungen

- Tute 3Dokument4 SeitenTute 3mgayanan0% (1)

- Digi Comm Model QP P1Dokument3 SeitenDigi Comm Model QP P1bku14677Noch keine Bewertungen

- Question Bank For DecoDokument2 SeitenQuestion Bank For Decotheamg7272Noch keine Bewertungen

- DC aDCghskjskksks FjsDokument4 SeitenDC aDCghskjskksks FjsSaiteja GundapuNoch keine Bewertungen

- DC Assignment 2019 PDFDokument2 SeitenDC Assignment 2019 PDFRashmi VermaNoch keine Bewertungen

- Sheet 1 - Spring 2018Dokument1 SeiteSheet 1 - Spring 2018dfgsqkjNoch keine Bewertungen

- Digital Signal Processing: Instant AccessVon EverandDigital Signal Processing: Instant AccessBewertung: 3.5 von 5 Sternen3.5/5 (2)

- SS Notes PDFDokument43 SeitenSS Notes PDFBhaumik MuliyaNoch keine Bewertungen

- SS NotesDokument43 SeitenSS NotesBhaumik MuliyaNoch keine Bewertungen

- Logical PDFDokument8 SeitenLogical PDFBhaumik MuliyaNoch keine Bewertungen

- Data Structure Using C by ISRD GroupDokument458 SeitenData Structure Using C by ISRD Groupmalirehman8750% (2)

- PG 19 - 20 GROUP 5Dokument2 SeitenPG 19 - 20 GROUP 5Kevin Luis Pacheco ZarateNoch keine Bewertungen

- Essay On Earth QuakeDokument7 SeitenEssay On Earth Quakexlgnhkaeg100% (2)

- 11v.jigisha Chaptear2Dokument53 Seiten11v.jigisha Chaptear2Anirban PalNoch keine Bewertungen

- Handling Qualites of CanardDokument49 SeitenHandling Qualites of CanardUsman GhummanNoch keine Bewertungen

- Catalyst 3750 Series Switches TroubleshootDokument19 SeitenCatalyst 3750 Series Switches TroubleshootSugumar DuraisamyNoch keine Bewertungen

- Seerat Mujaddid Alf-e-Sani (Urdu)Dokument518 SeitenSeerat Mujaddid Alf-e-Sani (Urdu)Talib Ghaffari100% (12)

- Machine DesignDokument34 SeitenMachine DesignMohammed Yunus33% (3)

- Erika Peters - Complete Idiot's Guide To Walking For Health-Alpha (2001) PDFDokument313 SeitenErika Peters - Complete Idiot's Guide To Walking For Health-Alpha (2001) PDFSiva SubramaniNoch keine Bewertungen

- Kematian Di ICUDokument24 SeitenKematian Di ICURahmida RahmyNoch keine Bewertungen

- Resume - General Manager - Mohit - IIM BDokument3 SeitenResume - General Manager - Mohit - IIM BBrexa ManagementNoch keine Bewertungen

- MCDP4, LogisticsDokument127 SeitenMCDP4, Logisticsjayemcee2100% (2)

- Hussain Kapadawala 1Dokument56 SeitenHussain Kapadawala 1hussainkapda7276Noch keine Bewertungen

- Short Tutorial On Recurrence RelationsDokument13 SeitenShort Tutorial On Recurrence RelationsAbdulfattah HusseinNoch keine Bewertungen

- Shalini NaagarDokument2 SeitenShalini NaagarAazam AdtechiesNoch keine Bewertungen

- AQA Music A LevelDokument10 SeitenAQA Music A LevelHindy LaiNoch keine Bewertungen

- 280-Article Text-1201-1-10-20220426Dokument8 Seiten280-Article Text-1201-1-10-20220426Ayu Ratri PNoch keine Bewertungen

- Individual Workweek Accomplishment ReportDokument16 SeitenIndividual Workweek Accomplishment ReportRenalyn Zamora Andadi JimenezNoch keine Bewertungen

- Operations Research Letters: Meichun Lin, Woonghee Tim Huh, Guohua WanDokument8 SeitenOperations Research Letters: Meichun Lin, Woonghee Tim Huh, Guohua WanQuỳnh NguyễnNoch keine Bewertungen

- DBS AR 2019 Final Final PDFDokument371 SeitenDBS AR 2019 Final Final PDFDevi Nurusr100% (1)

- CabillanDokument12 SeitenCabillanvivivioletteNoch keine Bewertungen

- LESSON 6 Perfect TensesDokument4 SeitenLESSON 6 Perfect TensesAULINO JÚLIONoch keine Bewertungen

- Types of Non Verbal CommunicationDokument7 SeitenTypes of Non Verbal Communicationgaurav gharat100% (1)

- An Aging Game Simulation Activity For Al PDFDokument13 SeitenAn Aging Game Simulation Activity For Al PDFramzan aliNoch keine Bewertungen

- World War I Almanac Almanacs of American WarsDokument561 SeitenWorld War I Almanac Almanacs of American WarsMatheus Benedito100% (1)

- Lista Alumnos Julio 2019123Dokument74 SeitenLista Alumnos Julio 2019123Mateo RomeroNoch keine Bewertungen

- Accenture 172199U SAP S4HANA Conversion Brochure US Web PDFDokument8 SeitenAccenture 172199U SAP S4HANA Conversion Brochure US Web PDFrajesh2kakkasseryNoch keine Bewertungen

- Interpret Market Trends and Developments TASk 1Dokument7 SeitenInterpret Market Trends and Developments TASk 1Raí SilveiraNoch keine Bewertungen