Beruflich Dokumente

Kultur Dokumente

Vita Manual

Hochgeladen von

castillo_leoOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Vita Manual

Hochgeladen von

castillo_leoCopyright:

Verfügbare Formate

Approved ANSI Standard

ANSI/VITA 42.0-2008 (R2014)

XMC

Abstract

This document defines an open standard for supporting high-speed, switched

interconnect protocols on an existing, widely deployed mezzanine card form factor.

Approved: December 2008

Reaffirmed: August 2014

American National Standards Institute, Inc.

Secretariat: VITA

ANSI/VITA 42.0-2008 (R2014) VITA

Copyright © VITA 2014. All Rights Reserved. www.vita.com

info@vita.com

Notices

American National Standard

Approval of an American National Standard requires verification by ANSI that the requirements

for due process, consensus, and other criteria for approval have been met by the standards

developer.

Consensus is established when, in the judgment of the ANSI Board of Standards Review,

substantial agreement has been reached by directly and materially affected interests.

Substantial agreement means much more than a simple majority, but not necessarily unanimity.

Consensus requires that all views and objections be considered, and that a concerted effort be

made toward their resolution.

The use of American National Standards is completely voluntary; their existence does not in

any respect preclude anyone, whether he has approved the standards or not, from

manufacturing, marketing, purchasing, or using products, processes, or procedures not

conforming to the standards.

The American National Standards Institute does not develop standards and will in no

circumstances give an interpretation of any American National Standard. Moreover, no person

shall have the right or authority to issue an interpretation of an American National Standard in

the name of the American National Standard Institute. Requests for interpretations should be

addressed to the secretariat or sponsor whose name appears on the title page of this standard.

CAUTION NOTICE: This American National Standard may be revised or withdrawn at any

time. The procedures of the American National Standards Institute require that action be taken

periodically to reaffirm, revise, or withdraw this standard. Purchases of American National

Standards may receive current information on all standard by calling or writing the American

National Standards Institute.

NOTE: The user’s attention is called to the possibility that compliance with this standard may

require use of an invention covered by patent rights.

By publication of this standard, no position is taken with respect to the validity of this claim or of

any patent rights in connection therewith. The patent holder has, however, filed a statement of

willingness to grant a license under these rights on reasonable and nondiscriminatory terms and

conditions to applicants desiring to obtain such a license. Details may be obtained from the

standards developer.

COPYRIGHT NOTICE

Published by:

VITA

Copyright © 2014 by VITA

All rights reserved.

Except for employees of VITA member companies, no part of this publication may be

reproduced in any form, in an electronic retrieval system or otherwise, without prior written

permission of the publisher.

Printed in the United States of America - R1.2, ISBN 1-885731-80-9.

ANSI/VITA 42.0-2008 (R2014)

Copyright © VITA 2014. All Rights Reserved.

Table of Contents

1 Introduction ........................................................................................................................................... 1

1.1 Objectives ..................................................................................................................................... 1

1.2 Overview ....................................................................................................................................... 1

1.3 Terminology .................................................................................................................................. 1

1.3.1 Specification Key Words ......................................................................................................... 1

1.3.2 Definitions ................................................................................................................................ 2

1.4 Normative References .................................................................................................................. 3

1.5 Dimensions ................................................................................................................................... 4

2 Compliance ........................................................................................................................................... 5

3 Mezzanine Cards.................................................................................................................................. 6

3.1 Overview ....................................................................................................................................... 6

3.2 Single-Width Mezzanine Cards .................................................................................................... 7

3.3 Double-Width Mezzanine Cards ................................................................................................... 9

3.4 Populating Optional PMC Connector Areas ............................................................................... 11

3.5 Populating Optional XMC Connector Areas ............................................................................... 11

3.6 Conduction Cooling..................................................................................................................... 11

4 Carrier Board ...................................................................................................................................... 12

4.1 Overview ..................................................................................................................................... 12

4.2 Connector Configurations ........................................................................................................... 14

4.3 Populating Optional PMC Connector Areas ............................................................................... 14

4.4 Populating Optional XMC Connector Areas ............................................................................... 14

5 XMC Connector .................................................................................................................................. 17

5.1 Pin Definitions for Primary XMC Connectors .............................................................................. 17

5.2 Pin Definitions for Secondary XMC Connectors ......................................................................... 20

5.2.1 Fabric Mode Pin Usage for XMC Secondary Connectors ..................................................... 20

5.2.2 User I/O Mode Pin Usage for XMC Secondary Connectors ................................................. 20

5.3 JTAG Signals .............................................................................................................................. 21

5.4 IPMI Support ............................................................................................................................... 21

5.5 Connector Pads and Labeling .................................................................................................... 22

5.6 Connector Assembly ................................................................................................................... 22

5.7 Signal Routing and Electrical ...................................................................................................... 23

5.8 Power Consumption and Heat Dissipation ................................................................................. 24

5.8.1 Carrier Voltage ...................................................................................................................... 24

5.8.2 Power Sequencing ................................................................................................................ 24

6 Identification ....................................................................................................................................... 25

6.1 Labels ......................................................................................................................................... 25

6.2 Label Locations ........................................................................................................................... 25

6.3 Identification Block ...................................................................................................................... 25

7 Compatibility Issues............................................................................................................................ 27

7.1 Mechanical Interoperability ......................................................................................................... 27

7.2 Electrical Interoperability ............................................................................................................. 27

7.3 System Interoperability ............................................................................................................... 27

ANSI/VITA 42.0-2008 (R2014)

Copyright © VITA 2014. All Rights Reserved.

8 Appendix A: Recommendations for Protocol Layer Standards .......................................................... 28

9 Appendix B: Identification Block Identifiers and Parameters for PMC Connectors ............................ 29

10 Appendix C: Connector Pin Usage on P25 for Double-Width Cards ................................................. 30

11 Appendix D: IPMI Serial EEPROM FRU Information ......................................................................... 31

11.1 Addressing .................................................................................................................................. 31

11.2 Devices ....................................................................................................................................... 31

11.3 FRU Data .................................................................................................................................... 31

12 Appendix A: Acknowledgements ........................................................................................................ 33

12.1 Working Group Members ............................................................................................................ 33

12.2 ANSI Ballot Group....................................................................................................................... 34

12.3 Comments, Corrections, or Additions ......................................................................................... 35

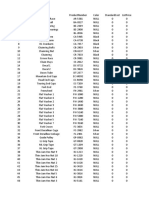

List of Tables

Table 1-1: Definitions .................................................................................................................................... 2

Table 5-1: Primary XMC Connector Pin Definition...................................................................................... 17

Table 5-2: I2C Address Decoding ............................................................................................................... 18

Table 5-3: Signal Summary......................................................................................................................... 19

Table 5-4: Secondary XMC Connector Pin Definition ................................................................................. 20

Table 5-5: PCIe to VITA Connector Comparison ........................................................................................ 23

Table 5-6: Voltage Level Tolerances .......................................................................................................... 24

Table 5-7: Voltage Level Tolerances for VPWR ......................................................................................... 24

Table 6-1: Identification Block – General Format ....................................................................................... 26

Table 9-1: Sample Compatibility Identification Block .................................................................................. 29

Table 11-1: Subtype 0: base definition (fixed length, mandatory) .............................................................. 31

Table 11-2: Subtype 1: I2C device definition (variable length, optional) .................................................... 32

Table 12-1: Working Group Members ......................................................................................................... 33

Table 12-2: ANSI Ballot Group ................................................................................................................... 34

List of Figures

Figure 3-1: Typical XMC Single-Width Mezzanine Card without PMC Connectors ..................................... 6

Figure 3-2: Typical XMC Double-Width Mezzanine Card without PMC Connectors .................................... 7

Figure 3-3: Single-Width Mezzanine Card Mechanical Layout with Optional PMC Connectors (Conduction

Cooled Holes Not Shown) ............................................................................................................................. 8

Figure 3-4: Optional Single-Width Mezzanine Card Mechanical Layout with Shortened Depth .................. 8

Figure 3-5: XMC Connector Placement Details on Single-Width Mezzanine Card ...................................... 9

Figure 3-6: Double-Width Mezzanine Card Connector Mechanical Layout with Optional PMC Connectors

(Conduction Cooled Holes Not Shown) ...................................................................................................... 10

Figure 3-7: Optional Double-Width Mezzanine Card Connector Mechanical Layout with Shortened Depth

.................................................................................................................................................................... 11

Figure 4-1: Typical 6U Carrier Card Supporting a Single XMC .................................................................. 13

ANSI/VITA 42.0-2008 (R2014)

Copyright © VITA 2014. All Rights Reserved.

Figure 4-2: Typical 6U Carrier Card Supporting Two Single-Width XMCs ................................................. 13

Figure 4-3: Carrier Cards – Typical Layout for Single-Width XMCs with Optional PMC Connectors ......... 15

Figure 4-4: Carrier Cards – Typical Layout for Double-Width XMCs with Optional PMC Connectors ....... 16

Figure 5-1: Geographical Addressing Mapping .......................................................................................... 18

Figure 5-2: Mezzanine Card Connector Grid Labeling (Component Side View) ........................................ 22

Figure 5-3: Carrier Card Connector Grid Labeling (Component Side View) .............................................. 22

ANSI/VITA 42.0-2008 (R2014)

Copyright © VITA 2014. All Rights Reserved.

1 Introduction

The inherent limits of bus architectures have sparked wide-spread interest in switched interconnect

technologies such as RapidIO and PCI Express, whose many high-speed point-to-point connections

deliver high aggregate bandwidths on a flattened architecture, utilizing fewer pins and operating over

greater transmission distances.

In light of these advantages, this document proposes to expand the potential features of Common

Mezzanine Cards (CMC) by defining a standard by which switched interconnect technologies can be

integrated into these cards.

1.1 Objectives

This specification defines an open standard for supporting high-speed, switched interconnect protocols on

an existing, widely deployed form factor. In light of this objective, specific goals include supporting:

A high-speed switched interconnect.

Open standardized technologies for switched fabrics.

Standard PMC form factors.

Compatibility with existing PMC specifications.

PMC, XMC, or dual-mode mezzanine cards.

PMC, XMC, or dual-mode carriers.

Standard VME, CompactPCI, Advanced TCA, and PCI Express carriers.

Standard PMC stacking heights.

Optional conduction cooling.

In support of these goals, this document specifies the mechanical and generic electrical requirements

necessary to serve as a basis for any number of protocol layer standards built on and complying with this

standard. Protocol layer standards should follow the recommendations in Appendix A.

1.2 Overview

The XMC Mezzanine Card base standard defines physical features that enable switched communications

between a standard mezzanine card and its carrier. These features include the addition of one or more

connectors carrying the additional electrical signals necessary for such communications.

In addition to providing signals to carry data to and from the carrier module, these high-speed connectors

provide adequate power, ground, and auxiliary signals so that the mezzanine card can function without

signals from any standard PMC connectors, thus making PMC connectors optional. This specification

requires no changes to existing PMC connectors, allowing them to continue supporting PCI-32 and PCI-

64 protocol layers.

1.3 Terminology

1.3.1 Specification Key Words

To avoid confusion and to make very clear what the requirements for compliance are, many of the

paragraphs in this standard are labeled with keywords that indicate the type of information they contain.

These keywords are listed below:

Rule

Recommendation

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 1

Suggestion

Permission

Observation

Any text not labeled with one of these keywords should be interpreted as descriptive in nature. These will

be written in either a descriptive or a narrative style.

The keywords are used as follows:

Rule <chapter>-<number>:

Rule 1-1: Rules form the basic framework of this standard. They are sometimes expressed in text form

and sometimes in the form of figures, tables or drawings. All rules shall be followed to ensure

compatibility between board and backplane designs. All rules use the “shall” or “shall not” words to

emphasize the importance of the rule. The “shall” or “shall not” words are reserved exclusively for stating

rules in this standard and are not used for any other purpose.

Recommendation <chapter>-<number>:

Recommendation 1-1: Wherever a recommendation appears, designers would be wise to take the advice

given. Doing otherwise might result in poor performance or awkward problems. Recommendations found

in this standard are based on experience and are provided to designers to speed their traversal of the

learning curve. All recommendations use the “should” or “should not” words to emphasize the importance

of the recommendation. The “should” or “should not” words are reserved exclusively for stating

recommendations in this standard and are not used for any other purpose.

Suggestion <chapter>-<number>:

Suggestion 1-1: A suggestion contains advice, which is helpful but not vital. The reader is encouraged to

consider the advice before discarding it. Some design decisions that need to be made are difficult until

experience has been gained. Suggestions are included to help a designer who has not yet gained this

experience.

Permission <chapter>-<number>:

Permission 1-1: In some cases a rule does not specifically prohibit a certain design approach, but the

reader might be left wondering whether that approach might violate the spirit of the rule or whether it

might lead to some subtle problem. Permissions reassure the reader that a certain approach is

acceptable and will cause no problems. All permissions use the “may” words to emphasize the

importance of the permission. The lower-case “may” words are reserved exclusively for stating

permissions in this standard and are not used for any other purpose.

Observation <chapter>-<number>:

Observation 1-1: Observations do not offer any specific advice. They usually follow naturally from what

has just been discussed. They spell out the implications of certain rules and bring attention to things that

might otherwise be overlooked. They also give the rationale behind certain rules so that the reader

understands why the rule must be followed.

1.3.2 Definitions

The following terms are used within the body of the specification. In this context, they have the following

meanings.

Table 1-1: Definitions

Term Definition

XMC An evolution of the PMC mezzanine card that includes a new connector

and the electrical signals necessary for switched communications

between the mezzanine card and its carrier.

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 2

Carrier Board A PCB that complies with the IEEE 1386 - Standard for a Common

Mezzanine Card Family and has an XMC-compliant primary connector.

Mezzanine Card A PCB that attaches to a Carrier Board and has an XMC-compliant

primary connector.

PMC Connectors Any connectors implemented on an XMC Carrier Board or Mezzanine

Card defined by IEEE 1386.1-2001 - Standard Physical and

Environmental Layers for PCI Mezzanine Cards. On mezzanine cards,

PMC connectors occupy locations Pn1 through Pn4.

XMC Connectors Connectors implemented on an XMC Carrier Board or Mezzanine Card

defined by this standard and subordinate protocol layer standards as

opposed to IEEE 1386.1-2001 - Standard Physical and Environmental

Layers for PCI Mezzanine Cards. On mezzanine cards, XMC connectors

occupy locations Pn5 and Pn6.

Primary Connector An XMC connector implemented on an XMC Carrier Board or Mezzanine

Card that carries auxiliary signals, voltage signals, and differential data

signals between the carrier and mezzanine card. On Mezzanine Cards,

the primary connector occupies connector location P15. General pin

assignments for the primary connector are provided in this specification,

while detailed signal assignments are documented in subsidiary protocol

specifications.

Secondary Connector Any XMC connector implemented on an XMC Carrier Board other than

the primary connector. Secondary connectors do not carry auxiliary

signals, but may carry differential data signals or user I/O signals. General

pin assignments for the secondary connector are provided in this

specification, while detailed signal assignments are documented in

subsidiary protocol specifications.

RFU (Reserved for Future Use by this Standard). Use of anything marked RFU

is prohibited in current designs and may impair compatibility with future

revisions of this standard.

RPS (Reserved for Use by Protocol Standards). Use of anything marked RPS

may impair compatibility with protocol layer standards built on or

complying with this standard. If a specific protocol layer standard does not

explicitly define the use of a pin marked RPS, that pin may be used as a

User Defined (UD) pin and still remain compliant with that protocol

standard.

UD (User Defined). Implementation of anything marked UD will never be

specified by this standard and any protocol layer standard built on or

complying with this standard.

1.4 Normative References

The following publications are used in conjunction with this standard. When any of the referenced

specifications are superseded by an approved revision, that revision shall apply.

IEEE 1386-2001 Standard for a Common Mezzanine Card http://www.standards.ieee.org

Family

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 3

IEEE 1386.1-2001 Standard Physical and Environmental http://standards.ieee.org

Layers for PCI Mezzanine Cards

IEEE 1149.1-2001 Standard Test Access Port and http://standards.ieee.org

Boundary-Scan Architecture

ANSI/VITA 20-2001 (R2011) Conduction Cooled PCI http://www.vita.com

Mezzanine Card (CCPMC)

ANSI/VITA 32-2003 Processor PMC Standard for http://www.vita.com

Processor PCI Mezzanine Cards

ANSI/VITA 39-2003 PCI-X Auxiliary Standard for PMCs http://www.vita.com

and Processor PMCs

VITA 42.10-200x XMC General Purpose I/O Standard http://www.vita.com

(XMC.10)

ANSI/TIA/EIA-644-A-2001 Electrical Characteristics of Low http://www.ansi.org

Voltage Differential Signaling (LVDS) Interface Circuits

PICMG 2.9 R1.0 CompactPCI System Management http://www.picmg.org

Platform Management Field Replaceable Unit (FRU) http://www.download.intel.com/design/se

Information Storage Definition (ISD) V1.0, Document Rev. rvers/ipmi/FRU1011.pdf

1.1, September 27, 1999 (Intel Corporation, Hewlett-

Packard Company, NEC Corporation, Dell Computer

Corporation,

I2C-Bus Specification 2.1 http://www.nxp.com

1.5 Dimensions

This standard follows the mechanical and dimensional specifications given in IEEE 1386 except where

noted. All dimensions are expressed in millimeters.

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 4

2 Compliance

To claim compliance to this standard a product shall comply with all appropriate requirements found in

IEEE 1386.1-2001 and this standard.

In the event of conflicts between this standard and other referenced standards, this standard shall take

precedence.

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 5

3 Mezzanine Cards

3.1 Overview

Mechanically, an XMC-compliant mezzanine card differs from a IEEE 1386-2001 compliant CMC in one

or more of the following ways:

The XMC has a primary XMC connector and possibly one or more secondary XMC connectors in

addition to any PMC connectors present on the card.

The XMC may have no PMC connectors.

Four compliant form factors are specified for XMC mezzanine cards, standard and short single-width

XMCs and standard and short double-width XMCs. Typical implementations are shown in Figure 3-1 and

Figure 3-2.

The XMC mezzanine card does not comply with the IEEE 1386-2001 component height limit in the

component area due to the height of the XMC connector. Short XMC cards do not comply with the IEEE

1386-2001 standard’s length, shortening this dimension by 10mm. Otherwise, XMC cards comply with

IEEE 1386-2001.

Figure 3-1: Typical XMC Single-Width Mezzanine Card without PMC Connectors

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 6

Figure 3-2: Typical XMC Double-Width Mezzanine Card without PMC Connectors

3.2 Single-Width Mezzanine Cards

Two form factors are specified for single-width XMC mezzanine cards, a standard IEEE 1386-2001 form

factor and an optional, shorter form factor that may be used for XMCs without PMC connectors (see

section 7.1). A single-width XMC shall have a primary XMC connector plug occupying connector location

P15 and may have a secondary XMC connector plug occupying connector location P16.

Mechanical specifications, connector locations, and connector labeling for single-width standard XMCs

shall conform to those shown in Figure 3-3.

Mechanical specifications for single-width short XMCs shall conform to those shown in Figure 3-4.

Implementers may optionally shorten the length of an XMC in order to reduce overhang of unsupported

printed circuit board material by locating the right edge in the figure anywhere in the hatched area. Note

that the 5V keypin location is not relevant to XMCs and therefore can be eliminated if the board edge is

located closer to the XMC connectors. However, for compatibility with combined PMC/XMC sites, when

the board edge is located such that material exists in this area, the keypin hole shall be present.

Details for placement of XMC connectors are shown in Figure 3-5.

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 7

Figure 3-3: Single-Width Mezzanine Card Mechanical Layout with Optional PMC Connectors

(Conduction Cooled Holes Not Shown)

Figure 3-4: Optional Single-Width Mezzanine Card Mechanical Layout with Shortened Depth

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 8

Figure 3-5: XMC Connector Placement Details on Single-Width Mezzanine Card

3.3 Double-Width Mezzanine Cards

Two form factors are specified for double-width XMC mezzanine cards, a standard IEEE 1386-2001 form

factor and an optional, shorter form factor that may be used for XMCs without PMC connectors (see

section 7.1). A double-width XMC shall have a primary XMC connector plug occupying connector location

P15 and may have up to three secondary XMC connector plugs occupying connector locations P16, P25,

and P26. If P25 is implemented, it shall conform to the connector pin usage described in Appendix C.

Mechanical specifications, connector locations, and connector labeling for double-width standard XMCs

shall conform to those shown in Figure 3-6.

Mechanical specifications for double-width short XMCs shall conform to those shown in Figure 3-7.

Implementers may optionally shorten the length of an XMC in order to reduce overhang of unsupported

printed circuit board material by locating the right edge in the figure anywhere in the hatched area. Note

that the 5V keypin location is not relevant to XMCs and therefore can be eliminated if the board edge is

located closer to the XMC connectors. However, for compatibility with combined PMC/XMC sites, when

the board edge is located such that material exists in this area, the keypin hole shall be present.

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 9

Figure 3-6: Double-Width Mezzanine Card Connector Mechanical Layout with Optional PMC

Connectors (Conduction Cooled Holes Not Shown)

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 10

Figure 3-7: Optional Double-Width Mezzanine Card Connector Mechanical Layout with Shortened

Depth

3.4 Populating Optional PMC Connector Areas

The implementation of PMC connectors is optional. Areas defined for optional PMC connectors that are

not present may be populated with components. Component heights in these areas shall not exceed

4.0 mm.

3.5 Populating Optional XMC Connector Areas

Areas defined for optional XMC connector plugs that are not present may be populated with components.

Component heights in these areas shall not exceed 6.5 mm.

3.6 Conduction Cooling

XMCs may implement conduction cooling. If implemented, the implementation shall comply with

ANSI/VITA 20-2001 (R2011). Note that mechanical dimensions and keep-outs for ANSI/VITA 20-2001

(R2011) compliant conduction cooled XMCs will differ from those specified in this document. Note also

that neither this standard nor ANSI/VITA 20-2001 (R2011) makes provisions for a shortened form factor

for conduction-cooled XMCs.

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 11

4 Carrier Board

4.1 Overview

Mechanically, a carrier board that supports XMC mezzanine cards differs from a standard PMC carrier in

one or more of the following ways:

The XMC carrier has a primary XMC connector and possibly one or more secondary XMC

connectors in addition to any PMC connectors present on the card.

The XMC carrier may have PMC connectors to support legacy PMC modules, or may have no

PMC connectors.

The standard stacking height of the XMC connectors is defined to be 10 mm as measured from the inner

surface of the carrier PCB to the inner surface of the mezzanine card PCB.

Stacking heights of 10 mm or greater in increments of 1 mm as defined in IEEE 1386 Section 5.1 (i.e.

“host” side) may be used. Alternate stacking heights as defined in IEEE 1386 Section 4.9 (i.e.

“mezzanine” side) are not permitted.

For stacking heights greater than 10 mm, each 1 mm increment in stacking height shall increment the

allowable component height in each region of the carrier board by 1 mm. Allowable component height on

the carrier board shall be identical with IEEE 1386 except as specified herein.

The allowable component height for an XMC module shall be as specified in Section 3 regardless of the

stacking height.

A stacking height of 10 mm will allow an XMC module to fit on a carrier board with a slot pitch of 0.8 inch

(e.g., VMEbus). A stacking height of 12 mm will allow an XMC module to fit on a carrier board with a slot

pitch of 1.0 inch (e.g., VITA 48).

Typical implementations are shown in Figure 4-1 and Figure 4-2.

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 12

Figure 4-1: Typical 6U Carrier Card Supporting a Single XMC

Figure 4-2: Typical 6U Carrier Card Supporting Two Single-Width XMCs

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 13

4.2 Connector Configurations

An XMC carrier supporting a single-width XMC shall have a primary XMC connector receptacle occupying

connector location J15 and may have a secondary XMC connector receptacle occupying connector

location J16.

A carrier supporting a double-width XMC card shall have a primary XMC connector receptacle occupying

connector location J15 and may have up to three secondary XMC connector receptacles occupying

connector locations J16, J25, and J26. Vendors should note the special connector pin usage for

connector P25 on double-wide XMC mezzanine cards described in Appendix C.

Typical layouts and connector locations for carriers supporting single-width and double-width XMC cards

with the full complement of PMC and XMC connectors are shown in Figure 4-3 and Figure 4-4.

Keep out areas should be free from traces, vias, and pads that could short with mezzanine components

under shock or vibration unless these areas are protected by appropriate insulating material.

4.3 Populating Optional PMC Connector Areas

Connector areas defined for optional PMC connectors that are not present may be populated with

components. Component heights in these areas shall comply with the component envelope specified in

IEEE 1386.

4.4 Populating Optional XMC Connector Areas

Areas defined for optional XMC connectors that are not present may not be populated with components

due to the height of the XMC connector that may be installed on the module.

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 14

Figure 4-3: Carrier Cards – Typical Layout for Single-Width XMCs with Optional PMC Connectors

.

PIN A1, TYP

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 15

Figure 4-4: Carrier Cards – Typical Layout for Double-Width XMCs with Optional PMC Connectors

.

PIN A1, TYP

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 16

5 XMC Connector

All XMC mezzanine card XMC connector plugs shall be part type SC-P-051. All XMC carrier XMC

connector receptacles shall be part type SC-R-052.

5.1 Pin Definitions for Primary XMC Connectors

The row and column labeling of contacts for the primary XMC connector shall comply with Table 5-1. The

tables indicate differential pairs with a “DP” prefix and a “+” or “-” suffix. The tables indicate active-low

signals with a “#” suffix. Voltage tolerances for power pins are documented in section 5.8.

Table 5-1: Primary XMC Connector Pin Definition

A B C D E F

01 DP00+ DP00- 3.3V DP01+ DP01- VPWR

02 GND GND TRST# GND GND MRSTI#

03 DP02+ DP02- 3.3V DP03+ DP03- VPWR

04 GND GND TCK GND GND MRSTO#

05 DP04+ DP04- 3.3V DP05+ DP05- VPWR

06 GND GND TMS GND GND +12V

07 DP06+ DP06- 3.3V DP07+ DP07- VPWR

08 GND GND TDI GND GND -12V

09 DP08+ DP08- RPS DP09+ DP09- VPWR

10 GND GND TDO GND GND GA0

11 DP10+ DP10- MBIST# DP11+ DP11- VPWR

12 GND GND GA1 GND GND MPRESENT#

13 DP12+ DP12- 3.3V AUX DP13+ DP13- VPWR

14 GND GND GA2 GND GND MSDA

15 DP14+ DP14- RPS DP15+ DP15- VPWR

16 GND GND MVMRO GND GND MSCL

17 DP16+ DP16- RFU DP17+ DP17- RFU

18 GND GND RPS GND GND RPS

19 DP18+ DP18- RPS DP19+ DP19- RPS

1

Samtec part number ASP-105885-01 or equivalent.

2

Samtec part number ASP-105884-01 or equivalent.

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 17

Pin usage is defined in the protocol layer standards except as follows.

DP[00..19]. Differential Pairs. These signals are used by the XMC to transmit or receive high-speed

protocol-specific data from the carrier. These signals are fully defined in the appropriate protocol layer

standard. These signals shall tolerate EIA-644 signal levels.

MSCL. IPMI I2C serial clock. This signal shall provide a clock reference to the XMC mezzanine card for a

two-wire serial management bus.

MSDA. IPMI I2C serial data. This signal shall provide a data line for a two-wire serial management bus.

GA[0..2]. I2C channel select. These signals allow a carrier to address a specific XMC slot on an IPMI I2C

bus shared by multiple XMCs. The XMC decodes these signals to determine its IPMI I2C address as

shown in Table 5-2. Addresses decoding for two types of target devices are shown, serial EEPROMs and

optional devices. I2C addresses are 7 bits and are by convention left justified in a byte. Table 5-2

assumes that the most significant bit is transmitted first. The carrier shall provide a unique code on these

signals for each XMC slot that shares an IPMI I2C. A value of 111b implies no connector is present.

Note that GA0 from the Primary XMC connector is the MSB and connects to Address bit 2 on

EEPROMs/Devices, while GA2 from the XMC connector is the LSB and connects to Address bit 0 on

EEPROMs/Devices. See Figure 5-1.

Table 5-2: I2C Address Decoding

GA0 GA1 GA2 GA[0..2] I2C Address I2C Addresses

Addr[2] Addr[1] Addr[0] for Serial for Optional Devices

EEPROM

0 0 0 000 0b101 0000 0bxxx x000

0 0 1 001 0b101 0001 0bxxx x001

0 1 0 010 0b101 0010 0bxxx x010

0 1 1 011 0b101 0011 0bxxx x011

1 0 0 100 0b101 0100 0bxxx x100

1 0 1 101 0b101 0101 0bxxx x101

1 1 0 110 0b101 0110 0bxxx x110

1 1 1 111 Not present Not present

EPROM

XMC

or

Primary

Optional

Connector

Device

GA0 Addr[2]

GA1 Addr[1]

GA2 Addr[0]

For additional information about I2C Address Decoding, refer to Appendix D.

Figure 5-1: Geographical Addressing Mapping

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 18

MBIST#. XMC Built In Self Test. This signal allows the carrier to determine whether an XMC has

completed its built-in self test. If this signal is used, it shall be asserted low at the de-assertion of MRSTI#

to indicate that the XMC is performing self-test and is not yet ready. This signal shall remain asserted for

at least 10 usec. If this signal is not used, it should be left unconnected by the XMC. If this signal is used

by the carrier, it should be pulled up by the carrier to support XMCs that do not implement this signal.

This signal is asynchronous with respect to XMC or PCI clocks.

MVMRO. XMC Write Prohibit. When this signal is asserted high, the XMC shall disable writes to non-

volatile memory on the XMC. The standard does not impose any requirements on the timing of this

signal. XMC modules should be designed to accept transitions on this signal at any time while valid power

is applied to the XMC.

MRSTI#. XMC Reset In. When this signal is asserted low by the carrier, the mezzanine card shall initialize

itself into a known state. The carrier shall drive this signal with a 10-millisecond or longer pulse, as

measured from the time that power is stabilized (see 4.5.2).

MRSTO#. XMC Reset Out. As input to the carrier, this optional signal provides an input to the carrier’s

reset logic in order to support a reset button or other reset source on the XMC. To avoid reset loops, the

XMC shall not drive this signal in response to an MRSTI# signal from the carrier. The XMC shall drive this

signal with a 10- millisecond or longer pulse.

MPRESENT#. Module present. This signal allows the carrier to determine whether an XMC is present.

The XMC shall connect this signal to ground.

TRST#. JTAG Reset. This signal shall provide for asynchronous initialization of the TAP controller on the

XMC.

TCK. JTAG Clock. This signal shall provide an independent clock reference for TAP controller operation.

TMS. JTAG Mode Select. This signal shall provide state control of the TAP controller on the XMC.

TDI. JTAG Data In. This signal shall provide for serial writes of test data and instructions into the XMC.

TDO. JTAG Data Out. This signal shall provide for serial writes of test data and instructions out of the

XMC.

VPWR. Power pins. These signals carry either 12V or 5V power from the carrier to the XMC. The XMC

shall accept either voltage level from the carrier. Acceptable voltage level tolerances are listed in

Table 5-6.

Table 5-3 provides a summary of the signals described previously.

Table 5-3: Signal Summary

Signal Description Direction Type Notes

DP[00..19] Differential Pairs (Note 1) (Note 2) 1,2

MSCL I2C Serial Clock Input LVTTL 3,4,8

MSDA I2C Serial Data I/O LVTTL 3,4,8

GA[0..2] I2C Channel Select. Input LVTTL 8

MVMRO XMC Write Prohibit Input LVTTL 8

MRSTI# XMC Reset In Input LVTTL 8

MRSTO# XMC Reset Out Output LVTTL 3,5,6,8

MBIST# XMC BIST Active Output LVTTL 5,6,8

MPRESENT# Module present. Output LVTTL 5,8

TRST# JTAG Reset Input LVTTL 7,8

TCK JTAG Clock Input LVTTL 7,8

TMS JTAG Mode Select Input LVTTL 7,8

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 19

TDI JTAG Data In Input LVTTL 7,8

TDO JTAG Data Out Output LVTTL 8

VPWR Variable Power pins. Input 5V or 12V 8

Note 1. Direction defined in protocol layer standard.

Note 2. Characteristics defined in protocol standard. Shall tolerate EIA-644 signal

levels.

Note 3. Open drain signal.

Note 4. Requires pull-up resisitor on carrier compliant with I2C Bus specification.

Note 5. Requires 10 kOhm (±5%) pull-up resistor on carrier.

Note 6. Optional signal.

Note 7. Requires termination on carrier compliant with IEEE1149.1 (JTAG).

Note 8. Signal directions are specified in relation to the XMC mezzanine card.

5.2 Pin Definitions for Secondary XMC Connectors

The standard defines two usage modes for secondary XMC connectors, Fabric Mode and User I/O mode.

Pin usage differs between the usage modes as published in the following sections.

5.2.1 Fabric Mode Pin Usage for XMC Secondary Connectors

Secondary XMC connectors used in fabric mode shall conform to Table 5-4.

5.2.2 User I/O Mode Pin Usage for XMC Secondary Connectors

Secondary XMC connectors used in User I/O mode are not required to conform to any pinout convention

including the location of ground pins. However, it is recommended that secondary XMC connectors

include the ground pins shown in Table 5-4 if possible.

Table 5-4: Secondary XMC Connector Pin Definition

A B C D E F

01 DP00+ DP00- UD DP01+ DP01- UD

02 GND GND UD GND GND UD

03 DP02+ DP02- UD DP03+ DP03- UD

04 GND GND UD GND GND UD

05 DP04+ DP04- UD DP05+ DP05- UD

06 GND GND UD GND GND UD

07 DP06+ DP06- UD DP07+ DP07- UD

08 GND GND UD GND GND UD

09 DP08+ DP08- UD DP09+ DP09- UD

10 GND GND UD GND GND UD

11 DP10+ DP10- UD DP11+ DP11- UD

12 GND GND UD GND GND UD

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 20

13 DP12+ DP12- UD DP13+ DP13- UD

14 GND GND UD GND GND UD

15 DP14+ DP14- UD DP15+ DP15- UD

16 GND GND UD GND GND UD

17 DP16+ DP16- UD DP17+ DP17- UD

18 GND GND UD GND GND UD

19 DP18+ DP18- UD DP19+ DP19- UD

5.3 JTAG Signals

This standard supports the signals required to implement Test Access Port and Boundary-Scan

Architecture, also known as JTAG, specified in IEEE1149.1. JTAG signals are available on the primary

XMC connector and on legacy PMC connectors. JTAG support is optional on the carrier and the

mezzanine. If the carrier does not support JTAG, it shall terminate its JTAG signals in an inactive state as

defined in the IEEE 1149.1 standard. If the XMC does not support JTAG, the XMC shall connect the TDI

signal to the TDO signal. This applies to the XMC connector and any existing PMC connectors.

The XMC standard requires LVTTL (3.3 volt) levels on the JTAG signals. The carrier shall not drive

signals to the XMC that exceed LVTTL levels. The XMC shall not drive signals to the carrier that exceed

LVTTL levels.

A carrier implementing legacy PMC connectors in addition to an XMC connector results in multiple

connectors with JTAG signals. Likewise, the XMC mezzanine may have an XMC connector, PMC

connectors, or both. The carrier and the XMC shall determine which connectors are present and route

the JTAG signals accordingly.

The carrier may use signal MPRESENT# to determine if the mezzanine card has an XMC connector. If

the mezzanine card does not have an XMC connector, the carrier may bypass the connector by

connecting TDI to TDO to keep the JTAG daisy chain intact.

The carrier may use the PMC BUSMODE1 signal (defined in IEEE 1386) to determine if the mezzanine

card has PMC connectors. If the mezzanine does not have PMC connectors, the carrier may bypass the

connectors by connecting TDI to TDO to keep the JTAG daisy chain intact.

If JTAG is used on an XMC mezzanine card then it shall use the XMC connector as the active connector

for JTAG interface. The mezzanine card may use signals GA[0..2] to determine if the carrier has an XMC

connector. If JTAG is used at XMC sites on a carrier then it shall use the XMC connector for the JTAG

interface.

When the XMC connector is used and the PMC connectors are present, the mezzanine shall connect the

TDI signal to TDO signal on the PMC connectors. If the carrier does not have an XMC connector, the

mezzanine card shall use the PMC connectors for the JTAG interface.

5.4 IPMI Support

The XMC mezzanine shall provide hardware definition information that may be read by an external

controller using IPMI commands and I2C serial bus transactions. The XMC shall support the I2C link and

optionally support the base IPMI commands defined in the PICMG 2.9 specification.

Data fields provided by the IPMI resource on the XMC shall include the minimum records defined in the

Platform Management FRU Information Storage Definition V1.0. It is recommended that XMCs include

the Board Info Area record for identification of the XMC. This data should be stored in a non-volatile

memory resource on the XMC.

Data fields provided by the IPMI resource on the XMC shall include the record type defined in Appendix D

(including protocol-specific fields for the implemented protocol standard) in addition to the minimum data

fields specified above.

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 21

The minimum IPMI requirements specified in this standard allow an XMC to use a simple passive device

such as a small PROM to support conforming implementations. An XMC may also use a more complex

device to provide additional features or to avoid the use of a dedicated PROM, but must in all cases

respond to the Serial EEPROM IPMI address with data responses equivalent to a Serial EEPROM.

5.5 Connector Pads and Labeling

Figure 5-2 shows the connector pad layout that shall be used for each XMC connector present on a

mezzanine card. Figure 5-3 shows the connector pad layout that shall be used for each XMC connector

present on a carrier card. The alphanumeric grid labeling shown shall override any proprietary pin

labeling conventions used by the connector manufacturer.

Figure 5-2: Mezzanine Card Connector Grid Labeling (Component Side View)

01 19

3.94

A 2.67

B

C

D

E

F

1.27 1.27

Figure 5-3: Carrier Card Connector Grid Labeling (Component Side View)

19 01

A

B

C

D

E

1.27 F

1.27

5.6 Connector Assembly

Assembly of XMC connectors shall be within +/- 0.089 mm of true position (TP). This tolerance applies to

mated pairs. If more than one mated pair is used, this is the total tolerance that is available for all mated

pairs relative to a common reference point. For multiple connector pairs this overall tolerance must be

allocated to each of the connector pairs. This allocation must be split between the XMC and the mating

connector on the carrier. TP is defined as some point on the PCB, near a connector, that is used by the

assembly equipment for the reference positioning of the connectors prior to soldering.

The angular misalignment of any connector shall not exceed 0.2 degrees, or shall not exceed 0.076 mm,

along either the length or the width.

The solder thickness variation between the connector contacts and the solder coated surfaces on the

PCB shall not exceed 0.1 mm. Excessive buildup of solder under the connector contacts will cause the

connector to be mounted too high.

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 22

5.7 Signal Routing and Electrical

This standard specifies a mezzanine to carrier board interface. It does not specify a direct mezzanine to

backplane interface. Differential signal connections of the mezzanine to the backplane are assumed to

be through active devices (for example, a fabric switch) on the carrier card.

Simulations and test card measurements were used to validate representative interconnect topologies.

Acceptable design rules will vary according to interconnect type and link speed. Test card topologies

using a total interconnect length of 10” (for example 6” on the host card and 4” on the mezzanine card)

showed acceptable results at link speeds up to 3.125Gbaud. These numbers assume FR-4 PCB material.

All traces should provide a differential impedance of 100 ohms +/- 10%.

Alternate topologies as well as support of user I/O signals are possible, but it is up to the designer to

verify these designs using accepted design practices.

With the advent of higher-speed signaling standards (i.e. Gen2/Gen3 PCIe) and alternate footprint-

compatible connector systems like VITA 61, designers are faced with a dilemma matching interconnects

with signaling standards. Table 5.5, for example, shows a comparison of PCIe signaling rates and VITA

connector standards:

Table 5-5: PCIe to VITA Connector Comparison

PCIe

3

Gen1 Gen23 Gen33

VITA 42

2.5Gbaud 5Gbaud 8Gbaud

(3.125 Gbaud1)

VITA 61

2.5Gbaud 5Gbaud 8Gbaud

(7.5 Gbaud2)

1. Application Note: SamArray® YFT/YFS Final Inch™ Designs in RapidIO Short

Run(Mezzanine) Applications, XMC Connector, 10mm Stack Height. Where this

application note refers to Gbps it is assumed that the encoding is 1 bit per baud, so

1Gbps = 1Gbaud.

2. Presentation: VITA 61 XMC 2.0 Update, Mezalok Stacking Connector, March 9, 2011,

Tyco Electronics. Where this application note refers to Gbps it is assumed that the

encoding is 1 bit per baud, so 1Gbps = 1Gbaud.

3. VITA 68.0, VPX Compliance Channel, Revision 0.27, 01 September 2011, Table 4.1-1

The table shows the maximum signaling rate for each connector standard and the signaling rate for each

generation of PCIe. Cells in red indicate scenarios where the connector does not meet the signaling

requirements of the specified PCIe generation based on the test conditions and specifications provided by

the connector manufacturer. The orange cells indicate scenarios where the connector does not meet the

signaling requirements of the specified PCIe generation, but may be close enough. Alternate conditions

like PCB routing, via construction, total lengths, and electrical tuning may be used to allow these

borderline scenarios to function properly, although it can be seen that the VITA 42 scenario offers less

margin than the VITA 61 scenario.

In order to facilitate interoperability between XMCs and carriers adhering to these VITA standards, and to

provide the largest margin possible, it is recommended that designs requiring support for PCIe Gen2 or

Gen3 use the VITA 61 standard for XMC support. Keep in mind that both mezzanine and host

connectors must match for interoperability as VITA 42 connectors do not mate with VITA 61 connectors.

Similarly, when considering other signaling protocols that utilize signaling rates greater than 3.125 Gbaud,

it is recommended that the VITA 61 standard is used for XMC support.

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 23

5.8 Power Consumption and Heat Dissipation

The maximum rated power and current demands of the XMC shall not exceed the XMC connector’s rated

current limit. Since the maximum current rating of each pin is not limited by the connector itself, designs

must also consider the current rating of the traces that connect to the power supplies. Therefore, the

recommended maximum current draw through each power pin, ground pin, trace, and via combination is

1.0A. See Table 5-1 for the pin assignments for each power and ground pin in the primary connector. If

P11 – P14 connectors are present on the module, the power and ground pin assignments identified in the

IEEE1386.1-2001 specification shall be implemented in addition to the power and ground assignments on

the primary connector.

XMCs shall operate with either 5V voltage levels or 12V voltage levels from the carrier on the VPWR pins.

Each XMC vendor shall document the current draw on the power pins. In addition, with approximately

100W of power theoretically available on an XMC module, thermal characteristics and cooling

requirements are a critical design parameter. XMC vendors should document the XMC module's thermal

characteristics and cooling requirements as part of the design, and make this information available to

system integrators. XMC vendors should document the recommended operating point with flow rate and

pressure for air cooled XMCs.

5.8.1 Carrier Voltage

Carriers shall provide 3.3V voltage levels complying with IEEE 1386.1 to all 3.3V power pins. Carriers

may provide +12V and -12V power. Acceptable tolerances appear in Table 5-6.

Carriers shall provide either 5V voltage levels or 12V voltage levels to all VPWR power pins. Acceptable

tolerances appear in Table 5-7.

The carrier vendor shall document the current carrying capability of each power supply.

Table 5-6: Voltage Level Tolerances

Voltage Level Tolerance

3.3V ± 0.3V

3.3V AUX ± 0.3V

12V ± 5%

-12V ± 5%

Table 5-7: Voltage Level Tolerances for VPWR

Voltage Level Tolerance

VPWR (if 5V) ± 5%

VPWR (if 12V) ± 5%

5.8.2 Power Sequencing

Carriers may provide power with arbitrary rise time and sequencing between different power supplies.

Carriers and mezzanines shall consider power to be stable once all power supplies are within tolerances.

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 24

6 Identification

Since this standard supports multiple protocol layer standards with similar physical characteristics,

vendors should label the XMC connectors on XMC mezzanine cards and carrier cards as described in

this section.

In addition, vendors shall publish a compatibility identification block for each XMC mezzanine card and

carrier card as described in this section.

6.1 Labels

If labeled, XMC connectors shall be labeled “XMC.n”, where n is the number identifying the protocol layer

specification supported. For example, labeled connectors supporting the VITA-42.2 Serial RapidIO

interface shall be labeled “XMC.2”. The typeface for these letters should be Arial and the size should be

8-point.

6.2 Label Locations

Labels for XMC connector receptacles located on the carrier cards shall appear on the same side as the

connector and as near the connector as possible. Labels for XMC connector plugs located on mezzanine

cards shall appear on the side of the PWB opposite the connector itself and as near the connector as

possible.

The front panel of each XMC location on the carrier or the front panel bezel of each XMC mezzanine card

may also be labeled. Any such labels should physically correspond to the location of the connector when

viewed from the front panel. For example, when viewing a carrier from the front panel with the front panel

horizontal and the XMC connector receptacles facing up, the label for connector J15 shall be on the left

side and the label for connector J16 shall be on the right side.

6.3 Identification Block

Vendors shall publish a compatibility identification block for each XMC mezzanine card or carrier card.

The identification block shall identify each implemented connector location, which protocol layer the

connector complies with, and one or more compliance keywords as appropriate for the specific protocol.

Multiple connector locations complying with the same protocol layer specification may be listed together

as one entry. Unimplemented connector locations may be omitted.

The compatibility identification block published for each XMC carrier or mezzanine card shall consist of

five rows. For XMC mezzanine cards, the top row shall list the card’s form factor. For carrier cards, the

top row shall list the largest XMC card form factor supported by the card. Defined keywords for form factor

specifications include “Standard XMC” and “Short XMC”.

The second row shall list the connector locations implemented by the card. The third row shall identify the

protocol layer implemented by the connector. The fourth row shall list the signal voltages supported over

the connector. The bottom row shall list a series of keywords describing the characteristics of the protocol

layer implementation.

Valid protocol identifiers and characteristic keywords are protocol layer specific. For XMC protocols,

identifiers and keywords shall be specified by the appropriate XMC protocol layer standard. For PMC

protocols, valid identifiers and keywords are listed in Appendix B of this standard. An example

identification block also appears in Appendix B.

The general layout of an identification block appears in Table 6-1. The table format shown is appropriate

for an XMC carrier implementing the same protocol (protocol 1) on connector locations J11-J13, and a

different protocol (protocol 2) on connector location J15. Protocol 1 requires the vendor to publish

keywords for three protocol characteristics. In contrast, protocol 2 requires the vendor to publish

keywords for only two protocol characteristics.

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 25

Table 6-1: Identification Block – General Format

Standard XMC

J11-J13 J15

(protocol 1) (protocol 2)

(keyword 1) (keyword 2) (keyword 3) (keyword 1) (keyword 2)

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 26

7 Compatibility Issues

This standard has been written to provide a high degree of interoperability between carrier boards and

mezzanine modules while still offering the designer a certain degree of flexibility to meet specific

application requirements. However, the system developer should be aware of several areas where

interoperability issues can arise.

7.1 Mechanical Interoperability

During the development of the VITA 42 standard, it became apparent that standard XMC modules would

not fit on ANSI/VITA 41.0 switch cards (see ANSI/VITA 41.0. VXS, standard). As a result the working

group decided to define a short XMC form factor that would fit on VITA 41 switch cards and possibly other

cards on which a standard sized XMC would not fit.

Therefore, system designers should be aware that while both standard XMC modules and short XMC

modules will fit on standard XMC carrier boards, standard XMC modules will not fit on short XMC carrier

boards such as those envisioned for the VITA 41 switch card.

7.2 Electrical Interoperability

The XMC.0 standard defines the mechanical form factor and leaves the electrical and protocol

specifications to the appropriate protocol layer standards. Currently, most of these protocols use electrical

signals that are either compatible or would not cause damage if inter-mated. However, as new protocol

standards emerge and are incorporated into the VITA 42 family, no guarantee of electrical signal

compatibility can be made. Therefore, system designers should be aware that inadvertently mating carrier

cards and mezzanine cards with incompatible protocols could damage either or both cards.

The XMC.0 standard defines connections on J15 for +3.3V, +12V, and -12V, and primary power pins that

can carry either 5V or 12V levels. Defining additional power inputs using "UD" pins is strongly

discouraged for protocol standards or for user I/O implementations to minimize the potential for

incompatibilities between modules with the potential to cause damage to the module, carrier or both if a

module is installed in the wrong location in a system.

7.3 System Interoperability

While the PCI bus is the prime interface for PMC modules, it is an optional interface for XMC modules.

XMC modules may or may not implement the PCI bus interface and likewise XMC carriers may or may

not support the PCI bus. Thus it is physically possible to mate an XMC module that supports PCI with a

carrier that does not, and vice versa.

Whether such combinations work correctly and make sense from a systems standpoint is a determination

left to the system integrator and is beyond the scope of this standard.

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 27

8 Appendix A: Recommendations for Protocol Layer

Standards

The intent of this document is to specify the mechanical and generic electrical requirements necessary to

provide the basis for any number of protocol layer standards built on and complying with this standard.

A protocol layer standard that builds on this standard should define, minimally, the following information:

Statements defining what compliance to the protocol layer standard means.

Connector configuration rules for any optional XMC connectors.

Signal pin assignments for any required and optional XMC connectors. Ground pin assignments

for secondary connectors should follow the ground pin assignments defined in this standard for

primary connectors.

Mechanical requirements over and above those specified in this standard.

References to any additional standards required to implement the protocol layer.

Valid identifiers and characteristic keywords for compatibility identification blocks.

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 28

9 Appendix B: Identification Block Identifiers and

Parameters for PMC Connectors

Implemented PMC connectors shall be identified in the XMC’s compatibility Identification Block using one

of the following protocol identifiers.

PCI x.y – PCI Local Bus Specification, Revision x.y, where x.y is the most current revision

complied with.

PCI-X x.y – PCI-X Local Bus Specification, Revision x.y, where x.y is the most current revision

complied with.

Connectors identified in the XMC’s Compatibility Identification Block as implementing PCI or PCI-X shall

publish three columns for implementation parameters as follows.

Supported signal levels. Valid keywords for this column include “3.3V”, “5V”, and “3.3V and 5V”.

Data width. Valid keywords for this column include “32” or “32/64”.

Clock rate. Valid keywords for this column include “x MHz” , where “x” is a number such as 33 or

a numerical range such as 33-66.

A sample identification block for PCI 2.2 compliant connectors appears below.

Table 9-1: Sample Compatibility Identification Block

J11-J13

PCI 2.2

3.3V and 5V 32/64 33-66 MHz

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 29

10 Appendix C: Connector Pin Usage on P25 for

Double-Width Cards

For double-width XMC mezzanine cards, the P25 connector, if implemented, shall conform to the primary

connector pin usage defined in Section 5 with the following modifications:

MSCL/MSDA. The XMC shall not connect to these signals on P25; the management interface shall be

implemented through P15.

GA[0..2]. The XMC shall not connect to these signals on P25; the management interface shall be

implemented through P15.

MVMRO. The XMC shall not connect to this signal on P25; the MVMRO signal on P15 shall be used.

MBIST#. The XMC shall not connect to this signal on P25; the MBIST# signal on P15 shall be used.

MRSTI#. The XMC shall not connect to this signal on P25; the MRSTI# signal on P15 shall be used.

MRSTO#. The XMC shall not connect to this signal on P25; the MRSTO# signal on P15 shall be used.

MPRESENT#. The carrier may monitor this signal on P25 to control the fabric interface on P25 if desired.

TRST#/TCK/TMS. The XMC shall not connect to these signals on P25; the JTAG interface on P15 shall

be used for JTAG functions implemented by the XMC module.

TDI/TDO. The XMC shall connect TDI to TDO on P25; the JTAG interface on P15 shall be used for JTAG

functions implemented by the XMC module.

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 30

11 Appendix D: IPMI Serial EEPROM FRU Information

11.1 Addressing

From an XMC module’s perspective, the I2C address space consists of a device address and a module

address. The four most significant bits provide the device address, which addresses a specific device on

the XMC. The three least significant bits provide the module’s address, which matches the module’s

GA[0:2] inputs. The device address provides for up to 16 addressable devices per XMC module. The

GA[0:2] inputs prevent address space collisions between multiple XMC modules on a single I2C bus

segment. Populating one I2C bus with the maximum of seven XMC sites, the bus could support a total of

112 addressable devices.

11.2 Devices

An XMC shall provide a Serial EEPROM device, or a device of some kind that emulates a Serial

EEPROM device, at address 0xAn (i.e. binary 0b1010nnn) where ‘n’ is determined by the GA[0:2] inputs.

The Serial EEPROM device shall provide sufficient storage to support FRU data compliant with the

Platform Management FRU Information Storage Definition (ISD).

An XMC may provide additional I2C devices at other addresses of the form 0xdn (binary 0bddddnnn),

where ‘d’ is an address other than binary 1010 and ‘n’ is determined by the GA[0:2] inputs.

An XMC module shall not respond to I2C addresses unless the least significant bits of the address match

the module’s GA[0:2] inputs.

11.3 FRU Data

An XMC module shall provide Field Replaceable Unit (FRU) records using the Serial EEPROM interface

described above. FRU records shall include all mandatory areas defined in the Platform Management

FRU ISD and shall also include at least one XMC-specific MultiRecord as defined below. FRU records

should include the Board Info Area defined in the ISD.

For XMC-specific MultiRecords, the MultiRecord’s header (see ISD section 16.1) shall specify OEM

record type 0xFA (see ISD section 16.2.1). The Manufacturer ID field of the Multirecord’s data portion

(see ISD section 18.7) shall specify VITA’s Organizationally Unique Identifier (OUI), 0x0012A2.

The XMC-specific MultiRecord includes the subtypes shown in Table 11-1 and Table 11-2. Note that the

tables show only the XMC-specific data portion of the XMC-specific MultiRecord. The record type, length,

checksum, and manufacturer ID fields required by the ISD MultiRecord definition are not shown.

Table 11-1: Subtype 0: base definition (fixed length, mandatory)

Field Length Description

Subtype 4 bits 0 for base definition subtype

Version 4 bits 0 for current version

Protocol Spec 4 bits 1 for 42.1, 2 for 42.2, etc. 0 is reserved for non-standard fabrics

Module Size 2 bits 0b00 = single wide, 0b01 = double wide

P16 Type 2 bits 0b00 = not present, 0b01 = fabric extension, 0b10 = user I/O

P25 Type 2 bits 0b00 = not present, 0b01 = fabric extension

P26 Type 2 bits 0b00 = not present, 0b01 = fabric extension, 0b10 = user I/O

VITA 42.10 20 bits Field defined by VITA 42.10

3.3V Power 8 bits 0 = unused, 1 = 1-50 mW, 2 = 51-100 mW, through 10 = 451-500

mW, 11 = 501-750 mW, 12 = 751-1000 mW, etc.

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 31

+12V Power 8 bits Same definition as 3.3V Power

-12V Power 8 bits Same definition as 3.3V Power

VPWR (5V) 8 bits Same definition as 3.3V Power

VPWR (12V) 8 bits Same definition as 3.3V Power

Protocol Spec N bits Field defined by protocol specification

Subtype 0 includes a base portion (bytes 1 through 9) and a protocol specific portion. The length of the

protocol specific portion is defined in the applicable protocol standard (i.e. VITA 42.1 may define 2 bytes,

or 16 bits, of protocol-specific information, in which case a VITA 42.1 MultiRecord subtype 0 will be 11

bytes long).

Table 11-2: Subtype 1: I2C device definition (variable length, optional)

Field Length Description

Subtype 4 bits 1 for I2C device definition subtype

Version 4 bits 0 for current version

Device String N bits Device address / name strings, see below

The device string portion of this MultiRecord subtype consists of 6-bit ASCII text as defined in the ISD.

The string is divided into one or more I2C device records. Each device record consists of one or more

address characters followed by one or more bytes of device name.

Address characters use the characters 0x01 through 0x0F, indicating I2C addresses with the most

significant bits corresponding to 0b0000 through 0b1111, skipping the Serial EEPROM address of

0b1010. Address characters may not be used within the device name. If the same device is used

multiple times, it may be indicated by multiple address characters prior to the device name.

The device name consists of the characters ‘0’ through ‘9’ and ‘A’ through ‘Z’. The interpretation of the

device name is outside the scope of this standard. It is recommended that the most basic form of the

device part number be used, without information such as package type, temperature range, or speed

grade.

For example, if the XMC module has a single I2C controller with a device name of “CTLR” at address

0b0000nnn, it would have the subtype 1 string “!CTLR”, where “!” is the 6-bit ASCII representation of

0x01, which in turn represents the 4 bit MSB of the address, 0x0000. If an XMC module had two

temperature sensors named “LM75” at addresses 0b0011nnn and 0b0100nnn along with the above

controller, it could have the subtype 1 string “!CTLR$%LM75”, where “$” represents 0x04, for the 4 bit

MSB address 0b0011 and “%” represents 0x05, for the 4 bit MSB address 0x0100.

Subtype 2 is reserved for use by protocol standards, although it is recommended that protocol standards

use the protocol-specific extension to subtype 0 to minimize the number of MultiRecord overhead bytes.

Other subtypes are reserved for future use.

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 32

12 Appendix A: Acknowledgements

12.1 Working Group Members

The following individuals have participated in the creation of this specification and are gratefully

acknowledged:

Participants:

Table 12-1: Working Group Members

Name Affiliation Role

Ray Alderman VITA Observer

Randy Banton Mercury Computer Systems, Inc. Participant

Steve Belvin ISBi Participant

Lee Brown Dy 4 Systems Inc. Participant

Gorky Chin VISTA Controls Corporation Observer

Danny Cohen Sun Microsystems Participant

Dick DeBock Thales Computers Participant

Paul Dozier TEK Microsystems Editor

Chris Eckert SBS Technologies, Inc Participant

Barry Ensten Radstone Participant

Michael Franco Artesyn Communication Products Participant

Jeff Harris Motorola Computer Group Observer

John Hill Sun Microsystems Participant

Timothy Ho Motorola Semiconductor Product Sector Participant

Frank Hom APW Electronic Solutions Participant

Aaron Kaiway Spectrum Signal Processing Participant

Tony Lavely Mercury Computer Systems, Inc. Sponsor

Mike Macpherson MITRE Corporation Sponsor

Joe Norris Technobox, Inc. Participant

Bill Northey FCI Electronics Participant

Gregory Novak Motorola Computer Group Sponsor / Chair

Elwood Parsons Foxconn Electronics Sponsor

Bob Patterson Tyco Electronics Participant

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 33

David Pepper GE Intelligent Platforms Participant

Robert Persons Motorola Computer Group Participant

Andrew Reddig TEK Microsystems Sponsor / Chair

Mac Rush Motorola Computer Group Participant

John Rynearson VITA Participant

Mark Schell FCI Electronics Observer

Holger Schubert MEN Mikro Electronik GMBH Participant

Ivan Straznicky Dy 4 Systems Inc. Participant

Bob Sullivan Hybricon Corporation Participant

Bruce Thomas VISTA Controls Corporation Participant

Larry Thompson NAVSEA Crane Division Observer

Robert Tufford Motorola Computer Group Participant

Frank Van Hooft Spectrum Signal Processing Participant

Randy White Dy 4 Systems Inc. Participant

Henry Wong Motorola Computer Group Participant

12.2 ANSI Ballot Group

The following individuals have participated in the balloting of this specification and are gratefully

acknowledged:

Table 12-2: ANSI Ballot Group

First Name Last Name Affiliation Role

Bryan Baraclough Lockheed Martin User

Chris Eckert GE Aviation User

Martin McGregor Producer

Joe Norris Technobox Producer

David Pepper GE Intelligent Platforms Producer

Greg Rocco MIT Lincoln Labs Research

Mac Rush Artesyn Embedded Technologies Producer

John Rynearson VITA General Interest

Herman Strass Independent General Interest

Michael Thompson Pentair General Interest

Serge Tissot Kontron Producer

Robert Voigt Northrup Grumman Electronic Systems User

Ben Winder Curtiss-Wright Defense Solutions Producer

ANSI/VITA 42.0-2008 (R2014) August 2014

Copyright © VITA 2014. All Rights Reserved. Page 34

12.3 Comments, Corrections, or Additions

Comments, corrections, or additions to this proposed standard may be forwarded to:

VITA Technical Director