Beruflich Dokumente

Kultur Dokumente

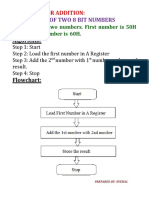

Vidyavahini First Grade College: Digital Electronics 2 Semester BCA

Hochgeladen von

subham joshiOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Vidyavahini First Grade College: Digital Electronics 2 Semester BCA

Hochgeladen von

subham joshiCopyright:

Verfügbare Formate

VIDYAVAHINI FIRST GRADE COLLEGE

Digital Electronics

2nd Semester BCA

Vidyavahini First Grade College

Near Puttanjaneya Temple, Kuvempunagar, Tumkur –

572103.

E-Mail:vvfgc.bca@gmail.com

Website:www.vidyavahini.org/bca

Contact No: 0816 – 2261130

Digital Electronics Vidyavahini First Grade College, Tumkur

Chapter-1

Number system

• Number a quantity or value expressed by a word or a symbol is called Number

• Number system a set of symbols & rules for representation of numbers is called

Number System

• They are classified into two types they are

a. Positional number system

b. Non positional number system

a. Positional number system

• The value of the digit depends on the position in which they appear in the number

Eg: decimal,binary,octal & hexa decimal number system

b. Non positional number system

In this type each symbol represents a definite value irrespective of the position in which they

appear

Eg: Roman number system.

Base or radix

The total number of different digits or symbols available in the number system is called

“base or radix”

Positional number system

The positional number system are classified into four types they are

1. Decimal number system

2. Binary number system

3. Octal number system

4. Hexa decimal number system

Decimal number system

• It is also called as Hindu Arabic numerals

• The symbols used in this system are 0,1,2,3,4,5,6,7,8,9

• The radix or base of this number system is 10

• Weight structure of this number system is

…..104 103 102 101 100 . 10-1 10-2 10-3……

Binary number system

Department of BCA Page 2

Digital Electronics Vidyavahini First Grade College, Tumkur

• The symbols used in this system are 0,1 0 & 1 are called “bits”

• Bit is an abbreviation for a binary digit

• The radix or base of this number system is 2

• Weight structure of this number system is

…..24 23 22 21 20 . 2-1 2-2 2-3……….

• The weights increases from right to left by a power of two for each bit

• The left most bit is the MSB & right most bit is the LSB

1 1 1 1 0 1 1 1 1

MSB LSB

Terms used in binary number system

• The symbols used in this system are 0,1 0 & 1 are called “bits”

• Bit is an abbreviation for a binary digit

• Nibble: A group of 4 bits called a Nibble Byte: A group of 8 bits called a Byte.

• Word: A group of 16 bits called a word or 2 Bytes is equal to 1 word

• LSB(Least significant bit):which has the lowest place value in the number

• MSB(Most significant bit):which has the highest place value in the number

Octal number system

• The symbols used in this system are 0,1,2,3,4,5,6,7

• The radix or base of this number system is 8

• Weight structure of this number system is

……..83 82 81 80 . 8-1 8-2 8-3…………

Hexa decimal number system

• The symbols used in this system are 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F

• The radix or base of this number system is 16

• Weight structure of this number system is

…..163 162 161 160 . 16-1 16-2 16-3……..

Conversions

1. Binary number system

• Decimal to binary conversion

• Binary to decimal conversion

Dept of BCA. Page 3

Digital Electronics Vidyavahini First Grade College, Tumkur

2. Octal number system

• Decimal to octal conversion

• Octal to decimal conversion

• Octal to binary conversion

• Binary to octal conversion

3. Hexa decimal number system

• Decimal to Hexa decimal conversion

• Hexa decimal to decimal conversion

• Hexa decimal to binary conversion

• Binary to Hexa decimal conversion

4.Other conversions

• Octal to Hexa decimal

• Hexa decimal to Octal

1. Binary number system

Decimal to binary conversion

In this conversion the given decimal number is repeatedly divide by 2 for integer part until the

quotient is 0 and for fraction successively multiplying by 2

Eg: Convert 28.3125(10)----(?)2

Binary to decimal conversion

1. Determine the positional value of each digit

2. Multiply the obtained value by the digit in the corresponding position

3. Sum the products calculate in the previous step to get the decimal number

26 25 24 23 22 21 20 2-1 2-2 2-3 2-4

Department of BCA Page 4

Digital Electronics Vidyavahini First Grade College, Tumkur

64 32 16 8 4 2 1 0.5 0.25 0.125 0.0625

Eg:1110.011(2)--(?)10

=1x23+1x22+1x21+1x20+0x2-1+1x2-2+1x2-3

=1x8+1x4+1x2+0x1+0x0.5+1x0.25+1x0.125

=8+4+2+0+0+0.25+0.125

1110.011(2)=14.375(10)

Octal number system

Decimal to octal conversion

In this conversion the given decimal number is repeatedly divide by 8 for integer part until the

quotient is 0 and for fraction successively multiplying by 8

Eg: Convert 549.1325(10) -----(?)(8)

Octal to decimal conversion

1. Determine the positional value of each digit

2. Multiply the obtained value by the digit in the corresponding position

3. Sum the products calculate in the previous step to get the decimal number

84 83 82 81 80 8-1 8-2 8-3

512 64 8 1 0.125 0.0156 0.00195

4096

Eg: Convert 763.375(8) ----------(?)(10)

7x82+6x81+3x80+3x8-1+7x8-2+5x8-3

7x64+6x8+3x1+3x0125+7x0.0156+5x0.00195

Dept of BCA. Page 5

Digital Electronics Vidyavahini First Grade College, Tumkur

448+48+3+0.375+0.1092+0.00975

763.375(8) = 499.49395(10)

Octal to binary conversion

1. Convert each digit of the octal number to a 3 digit binary number

2. Combine all the resulting binary groups into a single binary number

Octal Binary

0 000

1 001

2 010

3 011

4 100

5 101

6 110

7 111

Eg: 4632.51(8) -------- (?)2

4 6 3 2 . 5 1

100 110 011 010 101 001

4632.51(8) =100110011010101001(2)

Binary to octal conversion

1. The bits of the binary numbers are grouped into groups of 3 bits starting from LSB for

integer and from MSB for fraction

2. If the last group contains less than 3 bits then place 0 for those place

3. Convert each group into a octal equivalent digit

Eg:01111.1101011(2)->(?)8

1.

2.

3. 1 7 . 6 5 4

Department of BCA Page 6

Digital Electronics Vidyavahini First Grade College, Tumkur

4.17.654(8)

5. 01111.1101011(2) = 17.654(8)

Hexa decimal number system

Decimal to Hexa decimal conversion

In this conversion the given decimal number is repeatedly divide by 16 for integer part until

the quotient is 0 and for fraction successively multiplying by 16

Eg:Convert 512.625(10)-----(?)16

Hexa decimal to decimal conversion

1. Determine the positional value of each digit

2. Multiply the obtained value by the digit in the corresponding position

3. Sum the products calculate in the previous step to get the decimal number

164 163 162 161 160 16-1 16-2 16-3

4096 256 16 1 0.0625 0.0039 0.00024

65536

Eg: 36F.ABC(16)------(?)10

3x162+6x161+Fx160+Ax16-1+Bx16-2+Cx16-3

3x256+6x16+15x1+10x0.0625+11x0.0039+12x0.00024

879.67078(10)

36F.ABC(16)= 879.67078(10)

Hexa decimal to binary conversion

1. convert each digit of the Hexa decimal number to a 4 digit binary number 2.

combine all the resulting binary groups into a single binary number

Decimal Hex binary

0 0 0000

1 1 0001

2 2 0010

Dept of BCA. Page 7

Digital Electronics Vidyavahini First Grade College, Tumkur

3 3 0011

4 4 0100

5 5 0101

6 6 0110

7 7 0111

8 8 1000

9 9 1001

10 A 1010

11 B 1011

12 C 1100

13 D 1101

14 E 1110

15 F 1111

Eg: 10A4.FACE (16) ------ (?)2

1 0 A 4 . F A C E

0001 0000 1010 0100 1111 1010 1100 1110

0001000010100100.1111101011001110(2)

10A4.FACE (16) = 0001000010100100.1111101011001110(2)

Binary to Hexa decimal conversion

1. The bits of the binary numbers are grouped into groups of 4bits starting from LSB for

integer and from MSB for fraction

2. If the last group contains less than 4 bits then place 0 for those place

3. Convert each group into a Hexa decimal equivalent digit

Eg: 11100.01(2)=(?)16

1 C . 4

11100.01(2) = 1 C .4(16)

4.Other conversions

Octal to Hexa decimal

1. convert each digit of the Octal number to a 3 digit binary number

2. The bits of the binary numbers are grouped into groups of 4 bits starting from LSB for

integer and from MSB for fraction

Department of BCA Page 8

Digital Electronics Vidyavahini First Grade College, Tumkur

3. If the last group contains less than 4 bits then place 0 for those place

4. Convert each group into a Hexa decimal equivalent digit

Hexa decimal to Octal

1. convert each digit of the Hexa decimal number to a 4 digit binary number

2. The bits of the binary numbers are grouped into groups of 3 bits starting from LSB for

integer and from MSB for fraction

3. If the last group contains less than 3 bits then place 0 for those place

4. Convert each group into a octal equivalent digit

Complements of binary numbers

They are

• 1‟s complement

• 2‟s complement

1’s complement

• The 1‟s complement of a binary number is obtained by changing each 0 to 1 and 1 to 0

• Eg:101011

Dept of BCA. Page 9

Digital Electronics Vidyavahini First Grade College, Tumkur

010100->1‟s complement

2’s complement

• The 2‟s complement of a binary number is formed by taking the 1‟s complement of the

number and then adding 1 to LSB position Eg: 101011

010100->1‟s complement

1

010101->2‟s complement

Signed binary numbers

• Numbers that contain a sign bit followed by magnitude bits are called “sign magnitude

number”

• In this MSB always represents the sign whether +ve or –ve

• The remaining bits represent magnitude which is the value of the number

• The negative numbers are represented as sign magnitude,1‟s complement & 2‟s

complement

Bit->0,1

Nibble->4 bits

Byte->8 bits

Word-.2bytes->16 bits

Floating point numbers

• Floating point numbers consists of mantissa, exponent and a sign

• The Floating point numbers are represented as „any number y which is represented as

„a x rp‟

• Where a->mantissa

r-.radix

p->exponent

• Floating point numbers can be expressed in three formats

1. Single precision (32 bits)

2. Double precision (64 bits)

3. Extended precision (80 bits)

Department of BCA Page 10

Digital Electronics Vidyavahini First Grade College, Tumkur

S Exponent Mantissa

Normalization

• “The number succeeding the floating point is a non-zero number is called

normalization”

• Eg: 0.0047x109 is represented as 0.49x107

0.00236x10-7 is the normalized form is 0.236x10-9

Binary arithmetic

Binary arithmetic consists of the operations such as addition, subtraction, multiplication,

division

Binary addition

The rules of binary addition are

0+0=0

0+1=1

1+0=1

1+1=0 with a carry 1

1+1+1 with a carry 1

Addition of unsigned number

Addition of bits according to the rules of binary addition

Addition of signed numbers

There are 4 cases

1. Both positive number

2. Larger positive and smaller negative number

3. Smaller positive and larger negative number

4. Both negative numbers

Both positive numbers

1. Convert decimal to binary

2. Then add according to the rules

Eg: 128 64 32 16 8 4 2 1

64 0 1 0 0 0 0 0 0

Dept of BCA. Page 11

Digital Electronics Vidyavahini First Grade College, Tumkur

+32 0 1 0 0 0 0 0

+96 0 1 1 0 0 0 0 0 0

Larger positive and smaller negative number

1. Convert decimal to binary

2. Then take 2‟s complement for smaller negative number

3. Add according to the rules

4. Discard carry bit and represent sign bit

Eg: Add -16 from 32

step-1 128 64 32 16 8 4 2 1

+32 0 0 1 0 0 0 0 0

0 0 0 1 0 0 0 0

step-2 0 0 0 1 0 0 0 0

1's

1 1 1 0 1 1 1 1 complement

1

2's

complement 1 1 1 1 0 0 0 0

step-3 0 0 1 0 0 0 0

0 1 1 1 1 0 0 0 0

1 0 0 0 1 0 0 0 0

step-4 Ingnored carry bit

Smaller positive and larger negative number

1. Convert decimal to binary

2. Then take 2‟s complement for larger negative number

3. Add according to the rules

4. Represent sign bit Then take 2‟s complement for obtain the result

Eg: Add -32 from 20

step-1 128 64 32 16 8 4 2 1

Department of BCA Page 12

Digital Electronics Vidyavahini First Grade College, Tumkur

20 0 0 0 1 0 1 0 0

-32 0 0 1 0 0 0 0 0

-12

step-2 0 0 1 0 0 0 0 0 =>32

1 1 0 1 1 1 1 1 1's complement

1

2's complement 1 1 1 0 0 0 0 0

step-3 0 0 0 1 0 1 0 0 =>20

=>2’s com of 32 1 1 1 0 0 0 0 0

1 1 1 0 1 0 0

1 1 1 1 0 1 0 0

step 4

1's complement 0 0 0 0 1 0 1 1

1

2's complement 0 0 0 0 1 1 0 0

Both negative numbers

1. Convert decimal to binary

2. Then take 2‟s complement for both negative number

3. Add according to the rules

4. Discard carry bit and represent sign bit

5. Then take 2‟s complement for obtain the result

Eg: Add -16 from -32

step-1 128 64 32 16 8 4 2 1

-32 0 0 1 0 0 0 0 0

0 0 0 1 0 0 0 0

Take 2's complement for 32

step-2 0 0 1 0 0 0 0 0

1 1 0 1 1 1 1 1 1's complement

1

2's complement

Dept of BCA. Page 13

Digital Electronics Vidyavahini First Grade College, Tumkur

1 1 1 0 0 0 0 0

1's complement Take 2's complement for 16

0 0 0 1 0 0 0 0

2's complement 1 1 1 0 1 1 1 1

1

step-3 1 1 1 1 0 0 0 0

add

1 1 1 0 0 0 0 0

1 1 1 1 0 0 0 0

1

sign 1 1 0 1 0 0

0 0

Discard carry bit MSB is 1 i.e sign

step-4 bit=1

step-5 1 1 0 1 0 0 0

0

0 0 1

0 1 1 1 1 1's complement

1 0 0 1 1 0

2's complement

Binary subtraction

The rules of binary subtraction are

0-0=0

0-1=1 with borrow 1

1-0=1

1-1=0

Subtraction can be performed using 3 methods

a. Ordinary binary subtraction

b. Subtraction using 1‟s complement

c. Subtraction using 2‟s complement

Ordinary binary subtraction

This is the simple method of subtraction of bits according to the rules of binary subtraction

Eg:

1 0 0 1

Department of BCA Page 14

Digital Electronics Vidyavahini First Grade College, Tumkur

-0 1 0 1

0 1 0 0

1 1 0 . 1 0 1 1 1 0

-0 1 0 0 0 0 1 0 1

1 0 0 . 1 0 1 0 0 1 .

1 0 1 1 . 0 0 1

-0 1 1 1 1 0 1

0 0 1 1 . 1 0 0 .

Subtraction using 1’s complement

Unsigned numbers

There are two cases

1. The number of digits of minuend are less than the comprehend

2. The comprehend is smaller than minuend or the number of digits of comprehend are

lesser than minuend

1. The number of digits of minuend are less than the comprehend

• Inserting zero‟s to left of the minuend

• Take 1‟s complement for minuend

• Add both comprehend and minuend

• Carry that is generated is added to LSB to obtain result Eg: Subtract 1100 from

1101001

1 1 0 1 0 0

1 comprehend 1 1

0 0 minuend

step-1 Inserting zero‟s to left of the minuend

0 0 0 1 1 0 0

step-2 Take 1‟s complement for minuend

0 0 0 1 1 0 0

1 1 1 0 0 1 1 1's complement

step-3 Add both comprehend and minuend

1 1 0 1 0 0 1

1 1 1 0 0 1 1

Dept of BCA. Page 15

Digital Electronics Vidyavahini First Grade College, Tumkur

1 1 0 1 1 1 0 0

step-4 Carry that is generated is added to LSB to obtain result

1 0 1 1 1 0 0

1

1 0 1 1 1 0 1

2. The comprehend is smaller than minuend or the number of digits of comprehend are

lesser than minuend

• Inserting zero‟s to left of the comprehend

• Take 1‟s complement for minuend

• Add both comprehend and minuend

• There is no end around Carry so the result is to be again take 1‟s complement

Eg: Subtract 110100101 from 110101

1 1 0 1 0 1

comprehend 1 1 0 1 0 0 1 0

1 minuend

step-1 Inserting zero‟s to left of the comprehend

0 0 0 1 1 0 1 0 1 comprehend

step-2 Take 1‟s complement for minuend

1 1 0 1 0 0 1 0 1 minuend

0 0 1 0 1 1 0 1 0 1's

complement min

step-3 Add both comprehend and minuend

0 0 0 1 1 0 1 0 1 comprehend

0 0 1 0 1 1 0 1 0 1's

complement min

0 1 0 0 0 1 1 1 1

There is no end around Carry so the result is to be again take 1‟s

step-4 complement

0 1 0 0 0 1 1 1 1

1 0 1 1 1 0 0 0 0 Final result

Department of BCA Page 16

Digital Electronics Vidyavahini First Grade College, Tumkur

Signed numbers

Case 1: subtracting smaller number from a larger number

• Convert decimal number to binary number

• Take 1‟s complement for minuend

• Add both comprehend and minuend

• End around carry bit is added to LSB of the result

Eg: Subtract 16 from 25

step-1 Convert decimal number to binary number

25 0 0 0 1 comprehend

1 0 0 1

16 0 0 0 1 minuend

0 0 0 0

step-2 Take 1‟s complement for minuend

0 0 0 1 0 minuend

0 0 0

1 1 1 0 1 1's complement min

1 1 1

step-3 Add both comprehend and minuend

0 0 0 1 1 comprehend

0 0 1

1 1 1 0 1 1 1 1

1 0 0 0 0 1 0 0 0 1's complement min

step-4 End around carry bit is added to LSB of the result

0 0 0 0 1 0 0 0

1

0 0 0 0 1 0 0 1 Final result

Case 2: subtracting larger number from a smaller number

• Convert decimal number to binary number

• Take 1‟s complement for minuend

• Add both comprehend and minuend

• To verify the magnitude the result is converted to its 1‟s complement again

Dept of BCA. Page 17

Digital Electronics Vidyavahini First Grade College, Tumkur

Eg: Subtract 25 from 16

step-1 Convert decimal number to binary number

16 0 0 0 1 0 0

0 0 comprehend 25 0

0 0 1 1 0 0

1 minuend

step-2 Take 1‟s complement for minuend

0 00 1 1 0 0 1 minuend

1 11 0 0 1 1 0 1's complement min

step-3 Add both comprehend and minuend

0 00 1 0 0 0 0 comprehend

1 11 0 0 1 1 0 1's complement min

1 1 1 1 0 1 1 0

sign

step-4 To verify the magnitude the result is converted to its 1‟s complement again

1 1 1 1 0 1 1 0

0 0 0 0 1 0 0 1 1's complement &

final result

Subtraction using 2’s complement

Unsigned numbers

Case 1: subtracting smaller number from a larger number

• Convert decimal number to binary number

• Inserting zero‟s to left of the minuend

• Take 2‟s complement for minuend

• Add both comprehend and minuend

• Carry is ignored

Eg: Subtract 28 from 114

step-1 Convert decimal number to binary number

114 1 1 1 0 0 1

0 comprehend

28 1 1 1 0 0

minuend

Department of BCA Page 18

Digital Electronics Vidyavahini First Grade College, Tumkur

step-2 Inserting zero‟s to left of the minuend

28 0 0 1 1 1 0

0 minuend

step-3 Take 2‟s complement for minuend

0 0 1 1 1 0 0

minuend

1 1 0 0 1 0 1

1's complement

1

1 1 0 0 1 0 0 2's complement min

step-4 Add both comprehend and minuend

1 1 1 0 0 1 0 comprehend

1 1 0 0 1 0 0

1 1 0 1 0 1 1 0 2's complement min

step-5 Carry is

ignored

1 0 1 0 1 1 0 Final result

Case 2: subtracting larger number from a smaller number

• Convert decimal number to binary number

• Inserting zero‟s to left of the comprehend

• Take 2‟s complement for minuend

• Add both comprehend and minuend

• There is no end around Carry so the result is to be again take 2‟s complement

Eg: Subtract 114 from 28

step-1 Convert decimal number to binary number

28 1 1 1 0 0

comprehend

114 1 1 1 0 0 1 0

minuend

step-2 Inserting zero‟s to left of the comprehend

28 0 0 1 1 1 0 0

comprehend

Dept of BCA. Page 19

Digital Electronics Vidyavahini First Grade College, Tumkur

step-3 Take 2‟s complement for minuend

1 1 1 0 0 1 0

minuend

0 0 0 1 1 0 1

1's complement

1

0 0 0 1 1 1 0 2's complement min

step-4 Add both comprehend and minuend

0 0 1 1 1 0 0 comprehend

0 0 0 1 1 1 0 2's complement min

0 1 0 1 0 1 0

step-5 There is no end around Carry so the result is to be again take 2‟s complement

0 1 0 1 0 1 0

1 0 1 0 1 0 1 1's complement

1

1 0 1 0 1 1 0 2's complement & final result

Signed numbers

Case 1: subtracting smaller number from a larger number

• Convert decimal number to binary number

• Take 2‟s complement for minuend

• Add both comprehend and minuend

• Carry is ignored and represent sign bit

Eg: Subtract 32 from 64

step-1 Convert decimal number to binary number

128 64 32 16 8 4 2 1

64 0 1 0 0 0 0 0 0 comprehend

0 0 1 0 0 0 0 0 minuend

step-2 Take 2‟s complement for minuend

0 0 1 0 0 0 0 0 minuend

1 1 0 1 1 1 1 1 1's complement

Department of BCA Page 20

Digital Electronics Vidyavahini First Grade College, Tumkur

1

1 1 1 0 0 0 0 0 2's complement min

step-3 Add both comprehend and minuend

0 1 0 0 0 0 0 0 comprehend

1 1 0 0 0 0 0

1 0 0 1 0 0 0 0 0 1 2's complement min

step-4 Carry is ignored and represent sign bit

0 0 1 0 0 0 0

0 Final result sign

Case2: subtracting larger number from a smaller number

• Convert decimal number to binary number

• Take 2‟s complement for minuend

• Add both comprehend and minuend

• There is no end around Carry so the result is to be again take 2‟s complement

Eg: Subtract 64 from 32

step-1 Convert decimal number to binary number

128 64 32 16 8

4 2 1

32 0 0 1 0 0 comprehend

0 0 0

-64 0 1 0 0 0 minuend

0 0 0

-32

step-2 Take 2‟s complement for minuend

0 1 0 0

0 minuend

0 0

0

1 0 1 1

1 1's complement

1 1

1

1

1 1 0 0 0 0 0 0 2's complement min

step-3 Add both comprehend and minuend

0 0 1 0 0 0 0 0 comprehend

Dept of BCA. Page 21

Digital Electronics Vidyavahini First Grade College, Tumkur

1 0 0 0 0 0 0

1 1 1 0 0 0 0 0 1 2's complement min

sign

step-4 There is no end around Carry so the result is to be again take 2‟s complement

1 1 1 0 0 0 0 0

0 0 0 1 1 1 1 1 1's complement

1

0 0 1 0 0 0 0 0 2's complement & final result

Binary multiplication

In most computers multiplication is achieved using addition

In this method the multiplicand is multiplied by each multiplier digit beginning with the least

significant digit. The result of the multiplication of the multiplicand by a multiplier digit is

called a “partial product”

Partial product method of multiplication

1. Determine the sign of the product depending on whether the signs of multiplicand and

multiplier are the same or different

2. Negative number which may be in 2‟s complement form should be converted to the true

form( uncomplement form)

3. The partial products are generated starting with the least significant bit (LSB) of the

multiplier

If multiplier bit is 0.partial product is 0.if multiplier bit is 1.partial product is shifted one bit to

the left

4. The final product is obtained by adding each successive partial product to the sum of

the previous partial products

5. If the product is negative, the 2‟s complement of the product is determined. If the sign

bit is positive, the true form is retained. The sign bit is attached to the product

Eg: Multiply the signed numbers 01010011(multiplicand) & 10111011(multiplier)

1. Sign bit of multiplicand is 0 & sign bit of multiplier is 1.so the sign bit of product will be 1

2. Take 2‟s complement for multiplier

Department of BCA Page 22

Digital Electronics Vidyavahini First Grade College, Tumkur

3. Only magnitude bits are used for multiplication

4.

5. Sign of the product is 1.magnitued of product is 1011001011111. So

the final result is 1 1011001011111

Binary division

Method of binary division

1. The sign of the quotient is determined depending on whether the signs of the dividend

and divisor are the same or different, the quotient is initialized to zero

2. The divisor is subtracted from the dividend using 2‟s complement addition so as to get

the first partial remainder. a 1 is added to the quotient is incremented by 1.if this partial

remainder is positive, we move on to the next step. If this partial remainder is zero or negative,

the division is complete

3. Subtract the divisor from the partial remainder and add 1 to the quotient. If the result is

positive, repeat for the next partial remainder. If the result is zero or negative, the division is

complete

Example:Divide 01100100 by 00011001

Solution: 01100100 ->dividend

00011001->divisor

Dept of BCA. Page 23

Digital Electronics Vidyavahini First Grade College, Tumkur

1. Sign bit of both are positive. so quotient is positive. it is initialized to 00000000

2. The divisor is subtracted from the dividend so take 2‟complement for divisor

00011001->divisor

Add dividend & divisor

Discard carry bit . The sign bit is 0 so move to the next step

Add 1 to quotient

3.The divisor is subtracted from the 1st partial remainder using 2‟s complement addition

The sign bit is 0 so move to the next step

Add 1 to quotient

4.Add 2nd partial remainder with 2‟s complement of divisor

The sign bit is 0 so move to the next step

5. Add 3rd partial remainder with 2‟s complement of divisor

Department of BCA Page 24

Digital Electronics Vidyavahini First Grade College, Tumkur

The remainder is zero .so division is complete

Final product is 00000100

Digital codes

• Code is a symbolic representation of discrete elements of information which may be in

the form of numbers, letters or any other varying physical quantities

• The symbol used is a string of binary digits 0 & 1 & these are arranged according to the

rules of code. The group of bits(0 & 1) is known as a “binary code or digital code”

There are two types of digital codes

1. Numeric codes

2. Alphanumeric code(character codes)

• Numeric codes are broadly divided into 4 classes they are

1. Weighted codes

2. Self-complementing codes

3. Cyclic or reflected codes

4. Error detecting & correcting codes

Alphanumeric code (character codes)

Alphanumeric code are used to represent numbers, letters, symbols and instructions

Eg: ASCII code

Weighted codes

It obeys the positional weighting principles. In weighted code, the bits are multiplied by the

weights indicated and the sum of the weighted bits gives the decimal digit

Eg: The codes 8421(BCD), 2421 code

Binary coded decimal (BCD) [8421 code]

• BCD uses the binary number system to specify the decimal number 0 to 9.it is composed

of four bits

• The weights are assigned according to the position occupied by these digits

BCD code

Decimal 8421

Dept of BCA. Page 25

Digital Electronics Vidyavahini First Grade College, Tumkur

0 0000

1 0001

2 0010

3 0011

4 0100

5 0101

6 0110

7 0111

8 1000

9 1001

Eg: Write BCD code for a decimal number 96.42

=>9 6 . 4 2

=>1001 0110 0100 0010

=>[1001011001000010]BCD

Disadvantages of BCD

1. Only 10 possible combinations are used to represent decimal numbers. remaining six

combinations of 4 bits are wasted

2. It is difficult to obtain complements used in subtraction

The 2421 code

A weighted code is the 2421 code. Here the weight 2 is repeated twice

Decimal 2421 code

0 0000

1 0001

2 0010

3 0011

4 0100

5 1011

6 1100

7 1101

8 1110

9 1111

Self complementing codes

Department of BCA Page 26

Digital Electronics Vidyavahini First Grade College, Tumkur

• The self complementing code may or may not be weighted

• If a code is constructed such that when we replace a 1 by a 0 or 0 by a 1 in the 4 bit

code. a code for the 9‟s complement of the digit is obtained then such a code is called

self complementing code

• Example of self complementing weighted code is the 2421 code

code for Digit

2421 complement complement

Decimal code 2421 decimal

0 0000 1111 9

1 0001 1110 8

2 0010 1101 7

3 0011 1100 6

4 0100 1011 5

5 1011 0100 4

6 1100 0011 3

7 1101 0010 2

8 1110 0001 1

9 1111 0000 0

Excess-3 code

• It is an important unweighted self complementing code

• It is formed by adding 0011(3) to the BD in the normal weighted form so it is called

excess-3 or xs-3 code

• Example for self complementing non weighted code is the Excess-3 code

Digit

code for complement

Decimal Excess-3 complement decimal

0 0011 1100 9

1 0100 1011 8

2 0101 1010 7

3 0110 1001 6

4 0111 1000 5

5 1000 0111 4

6 1001 0110 3

7 1010 0101 2

8 1011 0100 1

9 1100 0011 0

Gray code

The gray code is a non weighted code. It differs from the preceding number by a single bit.

Dept of BCA. Page 27

Digital Electronics Vidyavahini First Grade College, Tumkur

So it is called the “unit distance code”. It is also called reflected code or cyclic code

Binary to gray code conversion

1. The MSB in the gray code is same as the corresponding MSB in the binary number

2. Going from left to right each adjacent pair of binary code bits are added to get the next

gray bit. The carries generated are ignored

Eg:

Gray to binary conversion

1. The MSB in the binary is the same as the corresponding MSB in the gray code

2. Going from left to right each binary code generated is added to the gray code bit in the

next adjacent position .the carries generated are ignored

Eg:

Gray

Decimal Binary code

0 0000 0000

1 0001 0001

2 0010 0011

3 0011 0010

4 0100 0110

5 0101 0111

6 0110 0101

7 0111 0100

8 1000 1100

9 1001 1101

10 1010 1111

11 1011 1110

12 1100 1010

13 1101 1011

Department of BCA Page 28

Digital Electronics Vidyavahini First Grade College, Tumkur

14 1110 1001

15 1111 1000

Error detection & correction codes

Parity bit

• Parity bit is a additional bits is used for a bit error detection

• Parity bit are of two types

1. Even parity

2. Odd parity

Even parity

If the total number of 1‟s is even in the code or number then it is called as even parity

Odd parity

If the total number of 1‟s is Odd in the code or number then it is called as Odd parity

Even parity Odd parity

BCD P BCD P

0000 0 0000 1

0001 1 0001 0

0010 1 0010 0

0011 0 0011 1

0100 1 0100 0

0101 0 0101 1

0110 0 0110 1

0111 1 0111 0

1000 1 1000 0

1001 0 1001 1

• Only single bit errors can be detected using this method if doesn‟t check for 2 bit errors

in a group

Error correction code

Hamming code

Dept of BCA. Page 29

Digital Electronics Vidyavahini First Grade College, Tumkur

• The hamming code is used not only to detect a bit error but also to identify the bit that

is in error so that it can be corrected

• The hamming code uses a number of parity bits depending on the number of information

bits, located at certain position in the code group

• The steps are

1. Number of parity bits

2. Placement of parity bits in code

3. Assignment of parity bit values

4. Detecting & correcting an error

Number of parity bits

• The number of parity bits to be included with the information bits is to be determined

by the relationship

2P>=M+P+1

P->number of parity bits

M->number of information bits

• The information bits are known but parity bit are found by trial & error method until

the relationship is satisfy

Placement of parity bits in code

• The parity bits are placed in the position that are ascending power of 2(1,2,4,8…)

1 2 3 4 5 6 7

Bits P1 P2 M1 P3 M2 M3 M4

P1,P2,P3=>parity bits

M1,M2,M3 & M4=>message bits or information bits

Assignment of parity bit values

• Each parity bit should be assigned value of 1 or 0

Bit designation P1 P2 M1 P3 M2 M3 M4

Bit position 1 2 3 4 5 6 7

Binary position 001 010 011 100 101 110 111

Information bits (Mn)

Parity bits(Pn)

• Each bit position is numbered is binary

• Information or message and parity bit locations are indicated in two rows

• Parity bit 1 checks all bit positions including itself that have 1‟s in the same

location(right most) in the binary position number i.e,p1 checks positions 1,3,5 &7

Department of BCA Page 30

Digital Electronics Vidyavahini First Grade College, Tumkur

• Parity bit 2 checks has a 1 in the middle position & so it checks positions 2,3,6 &7

• Parity bit 3 checks has a 1 in the left most in the binary position and so it checks

positions 4,5,6 &7

Detecting & correcting an error

• The number of parity checks made depend on the number o parity bits in the error

correcting code

• The method is as follows

a. Checks the p1 group for proper parity

A „0‟ represent good parity check

A „1‟ represent bad parity check

b. Repeat this for each parity group

c. The binary number formed by the result of all parity checks designates the

position of the code bit that is an error. This is the error position code

• If checks are good that means there is no error. The first parity check generate the LSB

and the last parity check generate the MSB

Problem

1. Find single error correcting code for 1001 using even parity

Solution:

a. Number of parity bits required

By relation 2p>=m+p+1

M=4

P=1 21>=4+1+1

2>=6-----F

P=2 22>=4+2+1

4>=7-------F

P=3 23>=4+3+1

8>=8-------T

So the number of parity bits is 3

The information bits are 4

Total number of bits is code 4+3=7bits

b. Placement of parity bits in code is

20,21,22,………….

1,2,4,………

c. Assignment of parity bit values

Bit designation P1 P2 M1 P3 M2 M3 M4

Dept of BCA. Page 31

Digital Electronics Vidyavahini First Grade College, Tumkur

Bit position 1 2 3 4 5 6 7

Binary position 001 010 011 100 101 110 111

Information bits (Mn) 1 0 0 1

Parity bits(Pn) 0 0 1

Parity bits are to be determined

• P1 checks position 1,3,5,7 =>-101

Total number of 1‟s is 2 for even parity P1 should be 0

P2 checks position 2,3,6,7 =>-101

Total number of 1‟s is 2 so good parity is 0

• P3 checks position 4,5,6,7 =>-001

Total number of 1‟s is 1 so bad parity is 1

The single error correcting code for information 1001 using even parity is 0011001

Problem 2

Suppose information transmitted is the code word 0011001 if it is received as 0010001, find

the error that has occurred in transmission if even parity is used

Solution: construct bit position table

Bit designation P1 P2 M1 P3 M2 M3 M4

Bit position 1 2 3 4 5 6 7

Binary position 001 010 011 100 101 110 111

Transmitted code 0 0 1 1 0 0 1

Received code 0 0 1 0 0 0 1

• Here we are using detecting and correcting an error

• There are 3 parity checks because number of parity bits is 3

First parity check

P1 checks position 1,3,5,7=0101(even number of 1‟s)->good parity=>0(LSB)

Second parity check

P2 checks position 2,3,6,7=0101(even number of 1‟s)->good parity=>0 Third

parity checks

P3 checks position 4,5,6,7=0001(odd number of 1‟s)->bad parity=>1(MSB)

• so the error position code is 100.this shows that the bit in position 4 is in error

• it is 0 in the received code but it should be a 1 so then the corrected code will be

0011001which will match the transmitted code character code

ASCII[American standard code for information interchange)

Department of BCA Page 32

Digital Electronics Vidyavahini First Grade College, Tumkur

• It is a 7 bit code proposed by ANSI(American national standard institute)

• The ASCII code is a 7 bit code with the format X6 X5 X4 X3 X2 X1 X0

Where each X is a 0 or 1

• ASCII character set

• From the table the ASCII code of the upper case letter „A‟ has a code 100 0001 whose

equivalent in decimal number is 65

• The range of ASCII set is from 0 to 127

Answer the following question

1. Give the radix of octal and hexa decimal number system (2M,DEC-2010)

2. Define radix of a number system with an example(2MNOV/DEC-2009)

3. Give 1‟s complement of 3810 (2M,DEC-2010)

4. Convert (4M,DEC-2010)

a. 358 into hexa decimal

b. 2A16 into decimal

c. 3A16 into octal (4M,NOV/DEC-2009)

d. 258 into decimal

e. 10110112 into octal (4M,OCT/NOV- 2011)

f. 458 to binary

g. 12310 to binary (4M,OCT/NOV-2012)

h. 523.218 to decimal

i. 35.128 to binary

j. 10112 to hexadecimal

5. Find the sum of decimal numbers 40 and 75 in binary addition method. (4M,DEC-2010)

Dept of BCA. Page 33

Digital Electronics Vidyavahini First Grade College, Tumkur

6. Subtract 4510 from 2510 in 2‟s complement method (3M,DEC-2010)

7. Subtract 2510 from 4010 in 2‟s complement method (3M,NOV/DEC-2009)

8. Subtract 2610 from 3610 in 2‟s complement method (3M,OCT/NOV- 2011)

9. Subtract 7710 from 9910 in 2‟s complement method (3M,OCT/NOV-2012)

10. Give 2‟s complement of 1100(2) (2M,OCT/NOV-2012)

11. The sum of decimal number 3010 and 4510 in binary addition method. (3M,OCT/NOV-

2011)

12. Explain binary multiplication procedure with an example?

13. Explain the procedure of binary division with suitable example.

14. What are BCD codes? Explain 8421 code. Mention its application (4M,NOV/DEC-2009)

15. Explain self complementing property of excess-3 code(4M,NOV/DEC-2009)

16. Define excess-3 code of a number system (3M,OCT/NOV- 2011) (OCT/NOV-2012)

17. Convert 11012 to gray code (2M,OCT/NOV- 2011)

18. Define gray code of a number system (2M,OCT/NOV-2012)

19. Explain steps involved in using hamming code for single –error correction

20. Suppose information transmitted is the code word 0101011.if it is received as 0100011,

find the error that has occurred in transmission, if even parity is used

Department of BCA Page 34

Digital Electronics Vidyavahini First Grade College, Tumkur

Chapter-2

Boolean algebra

Introduction

• In 1854 George Boole introduced a systematic treatment of logic and developed for this

purpose an algebraic system known as symbolic logic, or Boolean algebra.

• Boolean algebra is a branch of mathematics and it can be used to describe the

manipulation and processing of binary information or used in the design ,maintenance

and analysis of logical circuits in digital computers

Boolean algebra

• Boolean algebra uses Boolean variables and Boolean operators.

• Boolean variables are binary variables or symbol used to represent a logical quantity.

Some examples of Boolean variables are A, B, C, a, b, c, X, Y, and Z.

• Boolean operators are logical operators There are three basic logical operators: AND,

OR, and NOT.

• A Boolean expression is a combination of Boolean variables and Boolean operators.

• There are many Boolean expressions that are logically equivalent to one another. There

are called equivalent expressions.

• A Boolean function typically has one or more input variables and produces a result that

is based on these input values. The result can have a value of 0 or 1.

Truth Tables

• A truth table is a useful visual tool for defining the input-output relationship of binary

variables in a Boolean function.

• A function of n variables has 2n rows of possible input combinations, each row

specifying the value of the function for a different combination.

• A truth table can be used to represent one or more functions.

Complement

• It is the inverse of a variable and is indicated by a bar over the variable ex: A=>A‟

Literal:

• It is a variable or the complement of a variable

Dept of BCA. Page 35

Digital Electronics Vidyavahini First Grade College, Tumkur

The Duality Principle

• Given a Boolean expression, the dual is formed by replacing AND with OR, OR with

AND, 0 with 1, 1 with 0.

• The duality principle states that if two Boolean expressions are equal, then their duals

are also equal.

• Ex: ab+ab‟=a Dual is (a+b).(a+b‟)=a

Basic Postulates, Laws, and Theorems

Laws of Boolean Addition

x + 0 = x (Identity law in OR form)

x + 1 = 1 (Null law in OR form) Laws of

Boolean Multiplication

x 0=0 (Null law in AND form)

x 1=x (Identity law in AND form)

Idempotent Laws

x+x=x x x=x

Involution Law

(x‟)‟ = x

Laws of Complementarities

x + x‟ = 1 (Inverse law in OR form)

x x‟ = 0 (Inverse law in AND form)

Commutative Laws

x+y=y+x x y=y x

Associative Laws

(x + y) + z = x + (y + z) = x + y + z

(x y) z = x (y z) = x y z = xyz

Distributive Law

x (y+z) = x y +x z or x(y+z) = xy + xz

x+(y.z)=(x+y)(x+z) Absorption Laws

x (x+y) = x x + xy = x

De Morgan’s Laws

(x+y)’ = x’ y’

The complement of a sum of variables is equal to the product of the complements of

the individual variables

Department of BCA Page 36

Digital Electronics Vidyavahini First Grade College, Tumkur

LHS RHS

X Y X' Y' X+Y (X+Y)' ( X'.Y')

0 0 1 1 0 1 1

0 1 1 0 1 0 0

1 0 0 1 1 0 0

1 1 0 0 1 0 0

(x y)’ = x’ + y’

The complement of a product of variables is equal to the sum of the complements of

the individual variables

RHS

LHS (

X Y X' Y' X.Y (X.Y)' X'+Y')

0 0 1 1 0 1 1

0 1 1 0 0 1 1

1 0 0 1 0 1 1

1 1 0 0 1 0 0

1.Find the complement of W’X+YZ’

Sol: =(W‟X+YZ‟)‟

=(W‟X)‟.(YZ‟)‟

=(W‟‟+X‟).(Y‟+Z‟‟)

=(W+X‟).(Y‟+Z)

2. Apply Demorgan’s theorem to the expression (A+B) (B+C) (A+C)

Sol:=((A+B)(B+C)(A+C))‟

=(A+B)‟+(B+C)‟+(A+C)‟

=A‟.B‟+B‟.C‟+A‟.C‟

=A‟B‟+B‟C‟+A‟C‟

Factoring

In the reverse direction, the distributive law also expresses the process of factoring in which

the common variable X is factored out of the product terms

1.X+XZ=X

=X(1+Z)

=X(1)

Dept of BCA. Page 37

Digital Electronics Vidyavahini First Grade College, Tumkur

=X

2.(X+Y)(X+Z)=X+YZ

=XX+XZ+XY+YZ

=X+ XZ+XY+YZ

=X(1+Z+Y)+YZ

=X(1)+YZ

=X+YZ

Representations of Boolean Functions

A Boolean function can be described or represented by any one of the following:

• A Boolean expression (one of many equivalent Boolean expressions)

A truth table

• A circuit diagram (one of many equivalent circuit diagrams)

Logical functions:

Boolean expressions are represented in two forms based on their structure

1. Sum of products form (SOP) or disjunctive normal form

2. Product of sums form (POS) or conjunctive normal form

Product term

A term consisting of the product of literals or a single literal is said to be a product term

Eg: XY, X, X‟Y‟, XY‟

Sum term

A sum term consisting of the sum of literals or a single literal is said to be a sum term

Eg: X+Y, X‟+Y, X‟+Y‟, X‟

Domain of Boolean expression

It is the set of variables contained in the expression is either complemented or uncomplemented

form

Eg: AB‟+A‟BC is the set of variables ABC

SOP function:

• SOP is two or more AND functions ORed together. Or

• It is a product term or several product terms logically added

EX: 1.ABC‟+D‟EF‟+FGH+AF‟G

2. AB+BCD

POS function:

• It is two or more OR functions ANDed together. It is also known as the dual of the SOP

Department of BCA Page 38

Digital Electronics Vidyavahini First Grade College, Tumkur

Or

• It is a sum term or several sum terms logically multiplied

EX: 1.(A+B+C‟)(D‟+E+F)

2.(A+B)(C+D+E‟)

Standard SOP:

• It is also SOP but each product should contain all variables that are in the Boolean

expression. Each product term or AND function is known as min terms

• It can be represented as ∑m m->min term

• Eg: ABC‟+A‟BC+AB‟C

In the above example it has got 3 product terms containing all the 3 variables

(i.e.,A,B,C)

Conversion from SOP to standard SOP form

1. Multiply each of the product term by „1‟ which doesn‟t consist of all the variables so that

the value doesn‟t change (A.1=A)

2. Replace „1‟ by sum of complement and uncomplement of the variable which is missing in

that product term (A+A‟=1)

3. Repeat the above procedure until each product term consists of all the variables

Eg: write the following in the standard SOP form f(A,B,C)=AB’C+AB+A’

Step1:AB‟C+AB.1+A‟.1.1

Step2:AB‟C+AB(C+C‟)+A‟(B+B‟)(C+C‟)

Step3: AB‟C+ABC+ABC‟+A‟(BC+BC‟+B‟C+B‟C‟)

Step4: AB‟C+ABC+ABC‟+A‟BC+A‟BC‟+A‟B‟C+A‟B‟C‟

Standard SOP forms have 7 minterms or product terms

Assigning the value to each minterm

1. Complement of a variable is taken as „0‟ and uncomplement variable as‟1‟

2. Convert obtained binary form to its decimal equivalent

Boolean expression and truth tables

1. SOP expressions to truth table

The following steps are-

Step-1: determine the domain of expression & hence number of variables „n‟

Step-2: find the number of input combinations as 2n

Step-3: list all possible combination of binary values of the variables in the expression

Step-4: convert the SOP expression to standard form

Dept of BCA. Page 39

Digital Electronics Vidyavahini First Grade College, Tumkur

Step-5:place a 1 in the output column for each binary value that makes the standard SOP

expression a „1‟ & place a „0‟ for all remaining binary values

Example:

Develop a truth table for the standard SOP expression A’BC’+AB’C Solution:

1. Number of variables in domain n=3

2. Number of possible input combination 2n=23=8

3. Truth table

Inputs Output product

A B C X term

0 0 0 0

0 0 1 0

0 1 0 1 A'BC'

0 1 1 0

1 0 0 0

1 0 1 1 AB'C

1 1 0 0

1 1 1 0

4. The SOP expression is found to be in the standard form

5. Binary values that make the product terms in the expression equal to „1‟ are A‟BC‟=010 &

AB‟C=101

For these binary values a „1‟ is placed in the output column. for each of the remaining binary

combinations a „0‟ is place in the output column

Standard POS:

It is also POS but each sum function consists of all the variables that are in the Boolean

expression each such OR function/term is known as Max term

It can be represented as ∏M

M->max term

Eg:(A+B+C‟)(A‟+B+C)

Conversion from POS to standard POS form

1. ADD each of the sum term by „0‟ which doesn‟t consist of all the variables so that the value

doesn‟t change (A+0 =A)

2. Replace „0‟ by product of complement and uncomplement of the variable which is missing

in that sum term (A.A‟=0)

3. Expand the function by using the theorem A+BC=(A+B)(A+C)

4. Repeat the above procedure until each sum term consists of all the variables

Department of BCA Page 40

Digital Electronics Vidyavahini First Grade College, Tumkur

Eg: write the following in the standard POS form f(X,Y,Z))=(X’+Y’)(Y+Z)

Step1: (X‟+Y‟+0)(0+Y+Z)

Step2: (X‟+Y‟+ZZ‟)(XX‟+Y+Z)

Step3: (X‟+Y‟+Z) (X‟+Y‟+Z‟) (X+Y+Z) (X‟+Y+Z)

Standard POS term have 4 max terms or sum terms

Assigning the value to each max term

1. Complement of a variable is taken as „1‟ and uncomplement variable as‟0‟

2. Convert obtained binary form to its decimal equivalent

POS expression to truth table

They are-

Step-1: determine the domain of expression & hence number of variables „n‟

Step-2: find the number of input combinations as 2n

Step-3: list all possible combination of binary values of the variables in the expression Step-4:

convert the POS expression to standard form

Step-5: place a 0 in the output column for each binary value that makes the standard POS

expression a „0‟ & place a „1‟ for all remaining binary values

Example: Develop a truth table for the standard POS expression

(A+B’+C)(A+B+C’)(A’+B’+C’) Solution:

1. Number of variables in domain n=3

2. Number of possible input combination 2n=23=8 3.

Truth table

Inputs Output

A B C X Sum term

0 0 0 1

0 0 1 0 A+B+C'

0 1 0 0 A+B'+C

0 1 1 1

1 0 0 1

1 0 1 1

1 1 0 1

1 1 1 0 A'+B'+C'

4. The POS expression is found to be in the standard form

5. Binary values that make the sum terms in the expression equal to „0‟ are

(A+B‟+C)=010,(A+B+C‟)=001,(A‟+B‟+C‟)=111

For these binary values a „0‟ is placed in the output column. For each of the remaining

binary combinations a „1‟ is place in the output column

Dept of BCA. Page 41

Digital Electronics Vidyavahini First Grade College, Tumkur

Standard SOP & POS expression from truth table The

steps finding standard SOP expression from truth table-

a. List the binary values of the input variable for which the output is „1‟

b. convert each binary value to the corresponding product term

Eg:1001 can be written as AB‟C‟D

c. the SOP expression is formed by adding each individual product term for which output is a

„1‟

Example

Inputs Output

A B C X

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 1

1 0 0 1

1 0 1 0

1 1 0 1

1 1 1 1

step1; output is 1 for the binary values 011,100,110,111 step2: the

corresponding product terms are A‟BC, AB‟C‟, ABC‟,ABC

step3: output X=A‟BC+AB‟C‟+ABC‟+ABC

The steps for finding standard POS expression from truth table

a. List the binary values of the input variable for which the output is „0‟

b. convert each binary value to the corresponding sum term

eg: 1010 can be written as A‟+B+C‟+D

c .the POS expression is formed by multiplying each individual sum term for which output is

a „0‟

Example

Inputs Output

A B C X

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 1

Department of BCA Page 42

Digital Electronics Vidyavahini First Grade College, Tumkur

1 0 0 1

1 0 1 0

1 1 0 1

1 1 1 1

step1; output is 1 for the binary values 000,001,010,101

step2: the corresponding sum terms are A+B+C, A+B+C‟, A+B‟+C, A‟+B+C‟ step3:

output X= (A+B+C), (A+B+C‟) ,(A+B‟+C),(A‟+B+C‟)

Karnaugh map

• Karnaugh map provides a systematic method for simplifying Boolean expression. The

simplified expression (SOP or POS) is called the minimum expression

• K-map can be used to simplify Boolean expressions with two, three or four variables

• The number of cells in a k-map is equal to the total number of possible input variable

combinations

For a 2 variable k-map the number of cells=2n=22=4 .The variables are A&B

Each cell value is called a minterm

For a 3 variable k-map the number of cells=2n=23=8.The variables are A, B&C

Dept of BCA. Page 43

Digital Electronics Vidyavahini First Grade College, Tumkur

For a 4 variable k-map the number of cells=2n=24=16.The variables are A, B, C&D

Department of BCA Page 44

Digital Electronics Vidyavahini First Grade College, Tumkur

Cell adjacency

Cell adjacency is defined by a single variable change .cells that are differ by only one variable

are said to be adjacent so the order used in 00,01,11,10 to maintain “cell adjacency” Wrap

around adjacency

The cells in the left most columns are adjacent to the corresponding cells in the right most

columns this is called “wrap around adjacency”

Karnaugh map minimization of Boolean expressions

Minimization can be defined as the process that is used to obtain an expression containing the

fewest possible terms with the fewest possible variables

Minimization of SOP expressions

The following 3 steps

Dept of BCA. Page 45

Digital Electronics Vidyavahini First Grade College, Tumkur

1. Mapping a standard SOP expression 2.

Grouping the 1‟s

3. Summing the resultant product terms

1. Mapping a standard SOP expression

For each product term in the expression a 1 is placed in the cells corresponding to the

value of the product term

After mapping, the number of 1‟s in the k-map will be equal to the number of product

terms in the standard SOP expression

The remaining cells are filled with 0‟s

2. Grouping the 1’s

• The grouping should be done so as to maximize the size of the groups and to minimize

the number of groups

• The 1‟s are grouped to produce minimum product term

• The groups must have either 1, 2, 4, 8&16 cells each being some power of 2

• Sub-cubes

o A sub-cubes or a group is a set of exactly 2m adjacent cells containing 1‟s

• Single cell o For m=0 the sub-cubes consists of a single cell. No variables are reduced

it is an isolated 1

• Pair o For m=1 a sub-cube consists of 2m=21=2 adjacent cells

o Since m=1 grouping two adjacent cells containing 1‟s result in elimination of

one variables

• Quad

o For m=2 a sub-cube consists of 2m=22=4 adjacent cells

o Since m=2 grouping four adjacent cells containing 1‟s result in elimination of

two variables

• Octet o For m=3 a sub-cube consists of 2m=23=8 adjacent cells

o Since m=3 grouping eight adjacent cells containing 1‟s result in elimination of

three variables

Overlapping groups

The same 1 in a k-map cell may be used in more than one group so as to help in forming largest

group possible

Department of BCA Page 46

Digital Electronics Vidyavahini First Grade College, Tumkur

Rolling the map

The k map is visualized as if it is rolled so that the left side touches the right side and the top

edge touches the bottom edge

Redundant group

A group whose 1‟s are all overlapped by other groups is called a redundant group

Dept of BCA. Page 47

Digital Electronics Vidyavahini First Grade College, Tumkur

3. Summing the resultant product terms

• The product terms corresponding to each of the groups are written

• The variable that changes from the complemented to uncomplemented form or vice

versa is eliminated

Example: the SOP expression by using 4 variables is A’BCD+A’BCD’+ABCD+ABCD’

On grouping into a quad, the SOP expression will be BC

Because A changes from 0 to 1 and D changes from 1 to 0,So both variables A & D are

eliminated

Therefore A‟BCD+A‟BCD‟+ABCD+ABCD‟ can be simplified as BC

The final Boolean expression can be obtained by summing the resultant product terms

corresponding to each group this will be the minimum SOP expression

Example problem

1. Minimize the following standard SOP expression using k-map

AB’C+A’BC+A’B’C+A’B’C’+AB’C’ or f(A,B,C)= ∑m(0,1,3,4,5) or

f(A,B,C)=(m0,m1,m4,m5)

Solution:

Step1: Mapping a standard SOP expression

Department of BCA Page 48

Digital Electronics Vidyavahini First Grade College, Tumkur

Step 2: Grouping the 1’s

Step 3: Summing the resultant product terms

A‟B‟C‟+A‟B‟C+AB‟C‟+AB‟C=>B‟

A‟B‟C+A‟BC=>A‟C

The term corresponding to these groups are B‟+A‟C

Don’t care condition

• The don‟t care condition do not have any effect on the output

• For these don‟t care terms ,the output may be assigned either a 0 or a 1

• An „X‟ or „d‟ is placed in the cell for each don‟t care term

• These terms need not be covered by the sub-cubes, but can be treated as 1‟s to make

grouping so as to simplify the resulting term

Example: Using k-map simplify the expression

A’BCD+A’BCD’+A’BC’D+A’BC’D’+A’B’CD

Solution:

Dept of BCA. Page 49

Digital Electronics Vidyavahini First Grade College, Tumkur

Without using don‟t care term we can have 2 pairs. The resultant expression will be

A‟BD+A‟BC‟=>here one variable is eliminated

Using the don‟t care term we can have one group i.e. quad .The resultant expression will be

A‟B

=>Here 2 variables are eliminated so it is advantageous to use don‟t care terms in simplifying

expression using k-map

Minimization of POS expressions

The following 3 steps

1. Mapping a standard POS expression 2.

Grouping the 0‟s

3. Multiplying the resultant sum terms

1. Mapping a standard POS expression

• Each 0 is placed in a cell of k-map corresponding to the value of a sum term

• The number of 0‟s in the k=map is equal to the number of sum terms in the standard

POS expression

• The remaining cells are filled with 1‟s

2. Grouping the 0’s

• The 0‟s are grouped to produce minimum sum terms. The rules for grouping are the

same as for the grouping of 1‟s discussed earlier

3. Multiply the resultant sum terms

• The sum terms corresponding to each of the groups are written

• The variable that changes from the complemented to uncomplemented form or vice

versa is eliminated

• The final Boolean expression can be obtained by multiplying the resultant sum terms

corresponding to each group this will be the minimum POS expression

Example problem

1. Use k-map to minimize the standard POS expression

(X+Y’+Z)(X+Y’+Z’)(X’+Y’+Z)(X’+Y+Z)orf(X,Y,Z)=∏M(3,4,5,6)OR

f(X,Y,Z)=(M3+M4+M5+M6)

Solution:

Step 1: Mapping a standard POS expression

Department of BCA Page 50

Digital Electronics Vidyavahini First Grade College, Tumkur

Binary values of the expression

(X+Y‟+Z)=010

(X+Y‟+Z‟)=011

(X‟+Y‟+Z)=110

(X‟+Y+Z)=100

Step 2: Grouping 0’s

As done in the above k-map

Step 3: Multiplying the resulting sum terms

• The terms corresponding to these groups are (X+Y‟) & (X‟+Z)

• The final minimum POS expression can be written as the product of these 2 terms

corresponding to the 2 groups (X+Y‟). (X‟+Z)

Answer the following question:

1. What are minterms? Give example.(1M,NOV/DEC-2009)

2. State Boolean laws corresponding to basic logic operations. .(3M.NOV/DEC-2009)

3. State and prove demorgan‟s theorem using truth table (3M,NOV/DEC-2009)

.(3MOCT/NOV -2012)

4. Simplify the Boolean expression given using k-map. .(4M,NOV/DEC-2009)

Y=∑m(1,3,4,6,8,9,11,12,13,14)

5. Simplify the Boolean expression given below.(2M,DEC-2010)

Y=(AB+AC)‟+A‟B‟C

6. Define the terms

a. overlapping cell

b. Redundant group,

c. adjacency cells,

d. rolling a map

7. Explain the method of converting product terms to standard SOP form and sum terms to

standard POS form

8. Simplify using k-map.(4M,OCT/NOV -2011)

F=∑m(1,2,3,5,7,10,11)

9. List all Boolean postulates.

10. Simplify using k-map.(3M,OCT/NOV -2011)

F=∑m(0,1,3,9,11,2)

11. Prove that (A+B)(A+C)=A+BC. .(2M,OCT/NOV -2012)

12. Simplify using k-map.(4M,OCT/NOV -2012)

Y=∑m(0,1,2,3,8,9,10)+d(4,5,6,7,11)

13. Develop a truth table for the standard POS expression (A+B‟+C)(A+B+C‟)(A‟+B‟+C‟)

Dept of BCA. Page 51

Digital Electronics Vidyavahini First Grade College, Tumkur

Chapter-3

Logic gates

• A gate is simply an electronic circuit which operates on one or more input signals to

perform a particular logical function

• The basic gates are AND gate, OR gate & NOT gate

• NAND,NOR,EX-OR & EX-NOR gates are the other most widely used gates

AND gate:

Logic symbol AND gate:

Function:

• The AND gate is a logic element having two or more input terminals and only one

output terminal

• Its output is at logical 1(high) only when all of its inputs are at logical 1(high)

• If any one or more of the inputs are low then output of the gates will be low

Logical expression: Y=AB

Truth table

INPUTS OUTPUT

A B Y

0 0 0

0 1 0

1 0 0

1 1 1

Department of BCA Page 52

Digital Electronics Vidyavahini First Grade College, Tumkur

Application

AND gate is commonly used to enable the passage of a signal from one point to another at

certain times and to disable the passage of the signal at other times

OR gate:

Logic symbol OR gate

Function:

• The OR gate is a logic element having two or more input terminals and only one output

terminal

• The output of an OR-gate is high(1) if any one or more of its inputs are high(1),the

output is low(0) only when all of its inputs are low

Logical expression: Y=A+B

Truth table

Dept of BCA. Page 53

Digital Electronics Vidyavahini First Grade College, Tumkur

INPUTS OUTPUT

A B Y

0 0 0

0 1 1

1 0 1

1 1 1

Timing Diagram

Application

OR gate can be used in an detection and alarm system

NOT gate (inverter)

Logic symbol NOT gate

Function:

• The NOT gate is having one input and one output terminal.

• It is also called as an inverter as it inverts its input.

• It performs the operation called inversion or complementation or negation When a

high is applied to an inverter, a low will appear on its output.

Department of BCA Page 54

Digital Electronics Vidyavahini First Grade College, Tumkur

• When a low is applied to its input, a high will appear on its output

Boolean expression: Y=A‟

Truth table:

INPUTS OUTPUT

A Y Y=A'

0 1 ON

1 0 OFF

Pin Diagram

Timing Diagram

Application

NOT gates can be used to find the 1‟s complement of an 8-bitbinary number.

NAND gate:

Logic symbol:NAND gate

Function:

Dept of BCA. Page 55

Digital Electronics Vidyavahini First Grade College, Tumkur

• The NAND logical function is equivalent to AND followed by an inversion

• The output of a NAND gate is low only when all of its inputs are high.othrewise its

output is high

Boolean expression: Y= (A.B)‟

Truth table:

INPUTS OUTPUT

A B Y

0 0 1

0 1 1

1 0 1

1 1 0

NOR gate

Logic symbol: NOR gate

Department of BCA Page 56

Digital Electronics Vidyavahini First Grade College, Tumkur

Function:

• The NOR logical function is equivalent to OR followed by an inversion

• The output of a NOR gate is high only when all of its inputs are low.othrewise its output

is low

Boolean expression: Y= (A+B)‟

Truth table:

INPUTS OUTPUT

A B Y

0 0 1

0 1 0

1 0 0

1 1 0

Dept of BCA. Page 57

Digital Electronics Vidyavahini First Grade College, Tumkur

EX-OR gate

Logic symbol:EX-OR gate

Function:

• The exclusive-OR gate is a combinational circuit with two or more inputs and one

output

• The output of the EX-OR is high if one and only one input is high

• When both the inputs are equal, then the output is also low

Boolean expression: Y=A + B i.e., A‟B+AB‟

Truth table:

Department of BCA Page 58

Digital Electronics Vidyavahini First Grade College, Tumkur

INPUTS OUTPUT

A B Y

0 0 0

0 1 1

1 0 1

1 1 0

Application

An EX-OR gate can be used as a 2-bit adder

EX-NOR gate

Logic symbol: EX-NOR gate

Function:

• The exclusive-NOR gate is a combinational circuit with two or more inputs and one

output

• The EX-NOR function is the complement of an EX-OR function, and hence its output

is high only when its inputs are equal

Boolean expression: Y= (A + B)‟ i.e., A‟B‟+AB

Dept of BCA. Page 59

Digital Electronics Vidyavahini First Grade College, Tumkur

Truth table:

INPUTS OUTPUT

A B Y

0 0 1

0 1 0

1 0 0

1 1 1

Pin diagram

UNIVERSAL GATE:

Logic gates that can be used to realize any of the basic logical operations like

AND,OR NOT,NAND ,NOR,EX-OR & EX-NOR is called universal gate

EX:NAND & NOR gates are universal gates

NAND as universal gate

Desired NOT Gate NAND Construction

NAND Construction

Department of BCA Page 60

Digital Electronics Vidyavahini First Grade College, Tumkur

Desired OR Gate NAND Construction

Desired AND Gate

Desired NOR Gate NAND Construction

Desired XOR Gate NAND Construction

Dept of BCA. Page 61

Digital Electronics Vidyavahini First Grade College, Tumkur

Desired EX-NOR Gate NAND Construction

NOR as universal gate

Desired Not Gate NOR Construction

Desired OR Gate NOR Construction

NOR Construction

Desired AND Gate

Desired NAND Gate

NOR Construction

Department of BCA Page 62

Digital Electronics Vidyavahini First Grade College, Tumkur

Desired EX-OR Gate

NOR Construction

Desired XNOR Gate NOR Construction

Application

To implement a logic circuit with various gates, we require various ICs to be connected in the

circuit. but, if the same logic expression can be implemented using only NAND or only NOR

gates in the logic circuit can be used. This simplifies the implementation of logic expressions

Answer the following questions:

1. Write pin diagram of IC 7486(3M,NOV/DEC-2009)

2. What is NOR gate? Write logic symbol and truth table (3M,NOV/DEC-

2009)(DEC2010)

3. What is AND gate? Design AND gate using only (3M,DEC-2010)

4. i.NAND gate and

5. ii.NOR gate

6. Write logic symbol, Boolean expression and truth table of AND gate. (2M,OCT/NOV-

2011)

7. What is OR gate? Design OR gate using only. (3M,OCT/NOV-2011)

i.NAND gate and ii.NOR

gate

Dept of BCA. Page 63

Digital Electronics Vidyavahini First Grade College, Tumkur

8. Write pin diagram of IC 7402. (1M,OCT/NOV-2012)

9. Realize AND, OR, X-OR gate using NOR gate and NAND gate (3M,OCT/NOV2012)

10. Write timings diagram for all logic gates

Chapter-4

Arithmetic circuits

Introduction

• Logic circuit used to perform binary addition is called an adder. The Logic circuit used

to perform binary subtraction is called subtractor

• Various types of adders like half adder, full adder, parallel adder, BCD adders

• Adders and subtractors can be implemented by using NAND & NOR

• The two basic arithmetic functions of addition and subtraction can be defined by the

rules

Binary addition

Inputs Sum Carry

0+ 0 = 0 0

0+ 1 = 1 0

1+ 0 = 1 0

1+ 1 = 0 1

Binary Subtraction

Inputs Diff Borrow

0 -0 = 0 0

0 -1 = 1 1

1 -0 = 1 0

1 -1 = 0 0

Half Adder

It accepts two binary digits on its inputs and produces two binary digits on its outputs called

the sum bit and carry bit

Department of BCA Page 64

Digital Electronics Vidyavahini First Grade College, Tumkur

Logical symbol

Truth table

Inputs Outputs

A B Sum carry

0 0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

Logical expressions

Sum=AB‟ + A‟B

Sum=A B

Carry=AB

Logic diagram

Half adder using NAND gates

Disadvantage of half adder

The half adder does not have carry input from the previous stage

Full adder

The full adder circuit takes into account the carry from the previous stage. So it has three inputs

and produces two digits on its output called the sum and the carry out

Dept of BCA. Page 65

Digital Electronics Vidyavahini First Grade College, Tumkur

Logical symbol

Truth table

Inputs Outputs

A B cin Sum carry

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

Logical expression

Sum =A‟B‟C+A‟BC‟+AB‟C‟+ABC

=A‟(B‟C+BC‟)+A(B‟C‟+BC)

=A‟(B C)+A(B C)‟

Sum =A B C

Carry =A‟BC+AB‟C+ABC‟+ABC

=C(A‟B+AB‟)+AB(C‟+C)

=C(AB)+AB(1)

Carry =C(AB)+AB

Logical diagram

Department of BCA Page 66

Digital Electronics Vidyavahini First Grade College, Tumkur

Half adder implementation of full adder

Full Adder Using Nand Gate

Half Subtractor

It accepts two binary digits on its inputs and produces two binary digits on outputs called the

difference bit and borrow bit

Logical symbol

Truth table

Inputs Outputs

X Y DIFF BORROW

0 0 0 0

0 1 1 1

1 0 1 0

Dept of BCA. Page 67

Digital Electronics Vidyavahini First Grade College, Tumkur

1 1 0 0

Logical expressions

Diff =X‟Y+XY‟

Diff =X Y

Borrow=X’Y

Logical diagram

Half subtractor using NAND gate

Full Subtractor

The full subtractor accepts borrow from previous stage .so it has three inputs XYB0.It

has two outputs Difference and Borrow

Logical symbol

Truth table

Inputs Outputs

X Y B0 DIFF BORROW

0 0 0 0 0

0 0 1 1 1

0 1 0 1 1

Department of BCA Page 68

Digital Electronics Vidyavahini First Grade College, Tumkur

0 1 1 0 1

1 0 0 1 0

1 0 1 0 0

1 1 0 0 0

1 1 1 1 1

Logical expressions

DIFF =X‟Y‟B+X‟YB‟+XY‟B‟+XYB

=X‟(Y‟B+YB‟)+X(Y‟B‟+YB)

=X‟(Y B)+X(Y B)‟

DIFF=X Y B

BORROW =X‟Y‟B+X‟YB‟+X‟YB+XYB

= X‟Y‟B+XYB+X‟YB‟+X‟YB

=B(X‟Y‟+XY)+X‟Y(B‟+B)

=B(X Y)‟+X‟Y(1)

BORROW= B(X Y)‟+X‟Y

Logical diagram

Full subtractor using two half subtractors

Parallel binary adder

• Parallel binary adder can be formed by connecting two or more full adders. a single full

adder can add only two 1 bit numbers and an input carry

• Consider addition of two 4 bit numbers. a group of 4 bits is called a nibble, let the

number be A4 A3 A2 A1 & B4 B3 B2 B1

Dept of BCA. Page 69

Digital Electronics Vidyavahini First Grade College, Tumkur

C3 C2 C1

A4 A3 A2 A1

+ B4 B3 B2 B1

C4 S4 S3 S2 S1

Logic Diagram

4 Bit Parallel Binary Adder

The carries in parallel adder are handled by two methods. They are

1. Ripple carry adder

2. Carry look ahead adder

Ripple carry adder

A Ripple carry adder is one in which the carry output of each full adder is connected to the

carry input of the next higher order stage. This causes time delay because other stages cannot

operate without input carry

Carry look ahead adder

• Carry look ahead adder speeds up addition process by eliminating ripple carry delay.

The look ahead carry the output carry of each stage, and based on the inputs bits of each

stage, produces the output carry by either carry-generation or carrypropagation

• Carry-generation occurs when an output carry is produced internally by the full adder

• Carry propagation occurs when the input carry is rippled to become the output carry

4-bit binary adder-subtractor using IC 7483

Department of BCA Page 70

Digital Electronics Vidyavahini First Grade College, Tumkur

Adder-Subtractor

It is a logic circuit that can be used to perform both addition and subtraction

Logic diagram of 4-bit binary adder-subtractor

• The circuit is from right to left as in parallel adder circuit. The carry-out from each full

adder is the carry-in to the next –higher full adder.

• The first number bits are input to the full adders directly, because whether addition or

subtraction, the first number (A4 A3 A2 A1) is going to be same.

• For addition the second number (B4 B3 B2 B1) will be in true form .but in the

subtraction, the second number should be 2‟s complement form to be added. this can

be achieved by using EX-OR gates as controlled inverters.

• Each EX-OR gate has an input i.e. B4 B3 B2 B1 and another input is SUB

• With SUB=0, the Bits reaches the full adders in true form

• With SUB=1, the B bits are inverted. this gives the 1‟s complement

• The SUB line is connected to carry in of LSB full adder. this gives the 2‟s complement

of the second number

Pin Diagram Of Adder-Subtractor Circuit

Dept of BCA. Page 71

Digital Electronics Vidyavahini First Grade College, Tumkur

BCD Adder

• BCD adder is an arithmetic unit which performs operations on numbers that are stored

in BCD form.

• The BCD adder has 4 augends bits and 4 addend bits.

• BCD can have only 10 outputs 0000 to 1001

• The numbers 1010 to 1111 can be avoided by adding the bit pattern 0110

• For solving for the output conditions 1010 to 1111 using K-map,

• The Boolean expression is S4S3+S4S2 ,this is implemented using AND gates & OR

gates

• IF a carry out is generated or if any of the combinations 1010 to 1111 occur, then any

of the OR gate 3 inputs will be a 1.this is used to generate pattern 0110 to be added to

the augends using another 4-bit binary adder so as to obtain the final sum

Pin Diagram For BCD Adder

Department of BCA Page 72

Digital Electronics Vidyavahini First Grade College, Tumkur

Answer the following question

1. What is half adder? Write its truth table and logic gate circuit using XOR and basic

gates.(3M,Nov/Dec -2009) .(3M,Oct -2011)

2. What is half adder and half subtractor?.Write its truth table and logic circuit using NAND

gate

3. With the logical symbol and truth table explain full subtractor.write the logic circuit using

XOR and basic gates. .(4M,Nov/Dec -2009) .(3M,Oct -2011)

4. Write the logic gate circuit of half adder using XOR and basic gates.(1M,Dec -2010)

5. What is an adder? Draw the logic gate circuit of full-adder circuit using XOR and basic

gates explain. (3M, Dec -2010). (3M,Oct/Nov -2012)

Draw the logic circuit of full-adder using 2 half adder

6. What is half subtractor? Explain with logic diagram and truth table (3M,Dec-2010)

(3M,Oct/Nov -2012)

7. With logic circuit diagram explain the action of 4-bit binary adder-subtractor. (4M,Dec -

2010) (4M,Oct/Nov -2012)

8. With logic circuit diagram, explain the action of 4-bit binary adder. (4M,Oct -2011)

Dept of BCA. Page 73

Digital Electronics Vidyavahini First Grade College, Tumkur

Chapter-5

FLIP FLOP

• Digital circuits whose output depends entirely on the inputs to the circuits. such logic

circuits were called combinational logic circuits

• Sequential circuits are a digital circuit whose output not only depends on the current

inputs, but also on the previous state of the circuit. It involves timing and memory

devices.

• Flip flop is the basic memory element in a digital computer.

• It is used to store one bit of information with a 0 or a 1.It is also called the binary or

toggle or latch.

Characteristics of flip flop