Beruflich Dokumente

Kultur Dokumente

TH3122 004 PDF

Hochgeladen von

Sasa MitrovicOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

TH3122 004 PDF

Hochgeladen von

Sasa MitrovicCopyright:

Verfügbare Formate

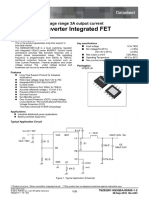

TH3122

K-Bus Transceiver with integrated Voltage Regulator

Pin Diagram

Features and Benefits

SOIC16

K-Bus Transceiver:

VS 1 16 VCC

PNP-open emitter driver with slew rate control and current limitation

EN 2 15 SENSE

BUS input voltage -24V ... 30V (independently of VS) VTR 3 14 RESET

ISO 9141 and ODBII compliant GND 4 13 GND

TH3122

GND GND

Possibility of BUS wake up

5 12

BUS 6 11 TxD

Operating voltage VS = 5.5 ... 16 V SI 7 10 RxD

SO SEN/STA

Very low standby current consumption <100 µ A

8 9

in normal mode (< 50 µ A in sleep mode)

Linear low drop voltage regulator:

Output voltage 5V± 2%

Output current max. 100mA

Output current limitation

Overtemperature shutdown

Configurable reset time (15ms/100ms) and reset threshold voltage (3.15V / 4.65V)

Low voltage detection at VS

Wake-up by K-BUS traffic and start-up capable independent of EN voltage level

Universal comparator with an input voltage range –24V … 30V and digital output

Load dump protected (40V)

Ordering Information

Part No. Temperature Code Package Code

TH3122 K ( -40ºC to 125ºC ) DF ( SOIC16, 300mil )

General Description

The TH3122 consists of a low drop voltage functions make it possible to develop simple, but

regulator 5V/100mA and a K-Bus transceiver. The powerful and cheap nodes in K-Bus systems.

transceiver is suitable for K-Bus systems conform The wide output current area and the configurable

to ISO 9141. reset time and reset voltage works together with

The combination of voltage regulator and bus many different microcontrollers.

transceiver in combination with the monitoring

3901003122 Page 1 Dec/04

Rev 004

TH3122

K-Bus Transceiver with integrated Voltage Regulator

Functional Diagram

VS VCC

Power Supply

EN Over Temp

+5V

7.8V SENSE

6.8V

+5V

Reset-Logic

VTR RESET

VTR-Logic

OSC

Wake-up

VthH

VthL

RxD

Bus-Logic TxD

BUS pnp Control

slew rate

foldback

SEN/STA

+5V

SI

VTHSI_H

VTHSI_L

SO

Figure 1 - Block Diagram

3901003122 Page 2 Dec/04

Rev 004

TH3122

K-Bus Transceiver with integrated Voltage Regulator

Functional Description

The TH3122 consists of a voltage regulator 5V/100mA Also integrated into the transceiver are a voltage and

and a K-Bus transceiver, which is a bi-directional bus time controlled reset management, power down, wake

interface device for data transfer between K-Bus and the up function and a universal comparator for extended

K-Bus protocol controller. applications.

to Wake-up

tdebWake

Logic

tdebBUS VthH

RxD Control- VthL

logic

POR

VBAT

Bit-Compare pnp-

POR

Constant-Low

Control BUS

VCC

VCC - slew rate

- IB

- foldback

TxD ESD

Vref

VCC OSC

Biasing

SENSE ESD

Figure 2 - Block Diagram K-Bus Transceiver

K-BUS Interface

The BUS Interface builds the connection between the

electromagnetic emission of the bus line, the TH3122

serial 5V bus line of the protocol controller and the 12V

has an integrated slew rate control.

K-Bus line.

The transceiver consists of a pnp-driver with slew rate

Receive Mode

control and fold-back characteristic and contains also in

the receiver a high voltage comparator followed by a The data at the pin BUS will be transferred to the pin

debouncing unit. RxD. Short spikes on the bus signal are suppressed by

the implemented debouncing circuit.

Transmit Mode

BUS

During the transmission the data at the pin TxD will be

transferred to the pin BUS. To minimize the

< tdebH < tdebL

SEN/STA

RxD

tdebH tdebL

TxD Figure 4 - Receive Mode Pulse Diagram

BUS

Figure 3 - Transmit Mode Pulse Diagram

3901003122 Page 3 Dec/04

Rev 004

TH3122

K-Bus Transceiver with integrated Voltage Regulator

Bit Compare Using this pin as an input the transmission path

can be overwritten (independent of bit-compare

If the signals at the pin TxD and the pin BUS within

and constant-low function):

a specified time tbc are not identical, the

transmission will be interrupted.

SEN/STA=”0”

If both signals at TxD and BUS are “High” within

forcing the transmission path free

the time tena the transmission will be enabled. The

SEN/STA=”1”

bit-compare-function is active when the pin SEN/

disable the transmission path

STA is open (not overwritten).

Constant Low Switch Off

A falling edge at pin TxD (from “1” to “0”) starts the

internal constant low timer (SEN/STA open).

If the low level “0” is valid for the time tlow the

transmission unit of the TH3122 will be disabled.

The receive unit is still active. A high level “1” at

TxD with a minimum pulse width of trec resets the

constant low timer.

Transmitting is not possible until TxD and BUS is

High for the time tena.

t < trec

Figure 5 - Bit Compare Pulse Diagram

SEN/STA TxD

The pin SEN/STA is bidirectional. Used as an

output the pin indicates whether the transmit-path

is enabled or disabled: SEN/STA

SEN/STA =”0”

transmission path is enabled tlow tena

SEN/STA =”1”

transmission path is disabled

Figure 6 - Constant Low Pulse Diagram

Linear Regulator and Controlling Functions

Regulator voltage level on the VTR pin (see table VTR

Programming). After tRES a rising edge on the RESET

The TH3122 has an integrated linear regulator with an

output is generated (see figure 7 - Initialization).

output voltage of 5V ±2% and an output current of max.

100mA. The regulator is switched on or off with a signal The regulator is active and can only be switched off with

on the EN pin or wakes up with a BUS signal. a falling edge on EN. The regulator remains with

EN=high in active mode and therefore the VCC voltage is

also active.

Initialization

The initialization is started if the power supply is switched

on, or after the temperature limitation has switched off

the regulator or in case of BUS traffic (wake up).

If the VCC voltage level is higher than VRESEIN, the reset

time tRES is started. This reset time is determined by the

3901003122 Page 4 Dec/04

Rev 004

TH3122

K-Bus Transceiver with integrated Voltage Regulator

VTR-Mode VRES tRes

VS VTR = GND VRES = VRES1 = 3.15V 100ms

VTR = VCC VRES = VRES2 = 4.65V 100ms

VRESEIN

VCC

VRES1/2

VTR with R ≥ 50k Ω to GND VRES = VRES1 = 3.15V 15ms

tRes trr VTR with R ≥ 50k Ω to VCC VRES = VRES2 = 4.65V 15ms

RESET

VTR-Programming

The voltage on VTR input is read out if the voltage at this

Figure 7 - Initialization pin is higher than VRESEIN . This value defines the reset

switch off voltage VRES. With the next oscillator cycle it

The input EN has an internal pull down resistor. If switches on the pull up current source if VTR=low or the

EN=high, the internal pull down current is switched off to pull down current source if VTR=high. The sources are

minimize the quiescent current. active for one oscillator cycle. The level changes during

RESET Output this procedure on VTR, which depends on the external

pull up or pull down resistors control the reset time tRes

The RESET output is switched from low to high if VS is

switched on and VCC>VRESEIN after the time tRES.

If the voltage VCC drops below VRES1 or VRES2 then the RESET Temperature Limitation

output is switched from high to low after the time trr has been If the junction temperature 150ºC < Tj < 170ºC the over

reached. temperature recognition will be active and the regulator

The voltage level for VRES1 and VRES2 and the voltage and the BUS driver will be switched off. After Tj

corresponding times tRES can be programmed via the falls below 140ºC the TH3122 will be initialized,

analogue input VTR. independently of the voltage levels on EN and BUS.

The function of the TH3122 is possible between TAmax

Wake up with BUS traffic and the switch off temperature, but small parameter

differences can appear.

If the regulator is put in standby mode it can be woken

up with the BUS interface. Every pulse on the BUS (high

pulse or low pulse) with a pulse width of min. 45 µ s will Low Voltage Detection VS

switch on the regulator. Low voltage on VS is monitored on SENSE output.

After the BUS has woken up the regulator, it can only be If VS has reached the level of VS =6.8V then the SENSE

switched off with a high level followed by a low level on output generates low level. The normal

the EN pin. operating range is VS > 7.8V and the SENSE output

generates a high level.

Reset Programming on VTR

With the VTR pin the reset switches off levels and delay Universal Comparator

time can be programmed. The TH3122 consist of a universal comparator for

The voltage on VCC influences the reset function. general use. The positive input of this comparator is

connected to the pin SI. The input voltage range of SI is

0V...VS. The input voltage is compared with a fixed

reference voltage at high or low level and the comparator

output SO drives a 5V digital signal.

3901003122 Page 5 Dec/04

Rev 004

TH3122

K-Bus Transceiver with integrated Voltage Regulator

Application Hints

Regulator Circuitry

Operating during Disturbances

The choice and dimension of the capacitor on VCC is

The absence of VS ,VCC or GND connection or ground determined by application point of view. Important

shift either alone or in any combination, do not influence parameters are the current difference on load changes

or disturb the communication between other bus nodes. and the maximum short time voltage drop.

The VCC pin must be connected to a min. 2 µ F

Undervoltage

capacitor for stable operating of the regulator in the

The reset unit secures the correct behavior of the driver whole operating range.

during undervoltage. The inputs have pull-up or pull-

down characteristics and have therefore defined voltage Short Circuit Proof

levels.

All in- and outputs are short circuit proof to battery and

With 4.5V ≤ VCC ≤ 5.25V the bus connection operates ground. A thermal shut down circuit prevents VCC and

within the correct parameters . BUS from any damage.

If VRES1 ≤ VCC ≤4.5V the TxD signal is transmitted to the

bus. The receive mode is also active. Baud Rate

If VCC < VRES1the bus driver is tristate. The TH3122 has a maximum Baud rate of 9600 Baud

SENSE and SO output the correct signal if VCC > VRES . (CBUS < 25nF, RPU > 400 Ω).

The specificated values of the input voltages on SO can’t

guaranteed.

Application Circuitry

battery reverse diode TH3122 µC

VBat VS VCC +5V

100u EN SENSE Port X.1

47n

VTR RESET Reset

GND GND

33uH GND GND 6.8u

BUS BUS TxD TxD

82p

SI RxD RxD

optional SO SEN/STA

10

Control Unit

100p

Figure 8 - Application Circuit

There should be used an LC-Filter to minimize the influence of EMI on the BUS lines.

3901003122 Page 6 Dec/04

Rev 004

TH3122

K-Bus Transceiver with integrated Voltage Regulator

Electrical Specification

All voltages are referenced to ground (GND). Positive any of these limits may do so. Long term exposure to

currents flow into the IC. The absolute maximum ratings limiting values may affect the reliability of the device.

given in the table below are limiting values that do not Reliable operation of the TH3122 is only specified within

lead to a permanent damage of the device but exceeding the limits shown in ”Operating conditions”.

Operating Conditions

Parameter Symbol Min Max Unit

Battery voltage VS 5.25 16 V

Supply voltage VCC 4.75 5.25 V

Operating ambient temperature TA -40 +125 °C

Junction temperature [1] TJ +150 °C

Absolute Maximum Ratings

Parameter Symbol Condition Min Max Unit

-1.0 16

Supply voltage at VS [2] VS T ≤ 1min - 30 V

T ≤ 500 ms - 40

-24 30

Input voltage at pin BUS [2] VINBUS V

T ≤ 500 ms - 40

Difference VS-VCC VS-VCC -0.3 40 V

Input voltage at pin EN and SI VINENSI -0.3 VS+0.3 V

Input voltage at pin VTR, TxD, SEN/STA, SO, RESET, SENSE VIN -0.3 VCC+0.3 V

Input current at pin EN, VTR, SI, SO, SEN/STA, TxD,

IIN -25 25 mA

RxD,RESET, SENSE

Input current for short circuit of pin VS and VCC IShort -500 500 mA

Power dissipation P0 Internal limited [3] [4] mW

Thermal resistance from junction to ambient RTHJA 50 K/W

Junction temperature [4] TJ 150 °C

Storage temperature TSTG -55 150 °C

______________________________

[1]

Junction temperature is defined in IEC 747-1

[2]

The current and voltage values are valid independent from each other.

[3]

The maximum power dissipation is defined by the ambient temperature and the thermal resistance. It can be calculated with

P0 =(VS-VCC)*IVCC+PBUS. PBUS is the BUS driver output with normally ≤25 mW

[4]

see over temperature protection

3901003122 Page 7 Dec/04

Rev 004

TH3122

K-Bus Transceiver with integrated Voltage Regulator

Static Characteristics

(VS = 5.25 to 16V, VCC= 4.75 to 5.25V, TA = -40 to +125°C, unless otherwise specified)

Parameter Symbol Condition Min Typ Max Unit

Linear Regulator

5.5V ≤ VS ≤ 16V

VCCn 4.95 5.0 5.05 V

TA = 25°C

Output voltage VCC VCCt 5.5V ≤ VS ≤ 16V 4.90 5.0 5.10 V

VCCh VSUP > 16V 4.95 5.0 5.25 V

VCCI 3.3 V< VS< 5.5 V VS-VD 5.1 V

VEN = VS = 12V, Pins 8-11,

Supply current, „normal mode“ ISnl 100 µA

14-16 open

Supply current, „sleep mode“ ISsleep VEN = 0V, VCC switched off 35 50 µA

VS ≥ 4.0V, IVCC = 25mA 200 mV

Drop-out voltage VD VS ≥ 4.0V, IVCC = 100mA 400 mV

VS ≥ 3.3V, IVCC = 20mA 600 mV

Output current VCC IVCC VS ≥ 3.0V 100 mA

Current limitation VCC ILVCC VS > 0V 300 mA

Load capacity Cload ESR ≤ 5Ω 2 µF

Power-on-reset threshold “VCC on” VRESEIN refered to VCC, VS > 4.6V 4.5 4.65 4.8 V

VRES2 VTR=High, VS > 0V 4.5 4.65 4.8

Power-on-reset threshold “VCC off” V

VRES1 VTR=Low, VS > 0V 3.0 3.15 3.3

SENSE-Output

VS - threshold low at SENSE VSENL 6.8 V

VS - threshold high an SENSE VSENH 7.8 V

Hysteresis SENSE VSENHYS 100 mV

Output voltage low VOL IOUT = 1mA 0.8 V

Output voltage high VOH IOUT = -1mA VCC-0.8 V

Enable-Input EN

Input voltage low VENL -0.3 1.75 V

Input voltage high VENH 2.5 VS +0.3 V

Hysteresis VENHYS 100 mV

VEN > VENH 1.8 4.0 7.5 µA

Pull-down current EN IpdEN

VEN < VENL 70 100 130 µA

Output RESET

IOUT = 1 mA, VSUP > 5.5 V 0.8 V

Output voltage low VOL

10 k Ω RESET to VCC 0.2 V

Pull-up current Ipu -500 -375 -250 µA

3901003122 Page 8 Dec/04

Rev 004

TH3122

K-Bus Transceiver with integrated Voltage Regulator

Static Characteristics (continued)

Parameter Symbol Condition Min Typ Max Unit

Comparator SI, SO

Threshold low SI VIL 1.05 1.16 V

Threshold High SI VIH 1.21 1.4 V

Hysteresis VHYS 30 mV

IOUT = 1 mA, VS > 5.5 V 0.8 V

Output voltage low at SO VOL

10 k Ω SO to VCC, VCC > 3.3V 0.4 V

Pull-up current at SO Ipu -500 -375 -250 µA

Input VTR

Threshold low VTRL 0.15 0.25 VCC

Threshold high VTRH 0.75 0.85 VCC

Output current low IOL 160 230 300 µA

VCC > 3.3 V

Output current high IOH -300 -230 -160 µA

K-Bus-Interface

Power-on-reset threshold VPOR VPOR =VRES1 3.0 3.15 3.3 V

Pull-up current TxD Ipu -500 -375 -250 µA

Pull-down current SEN/STA IpdSEN 250 375 500 µA

Pull-up current SEN/STA IpuSEN -500 -375 -250 µA

Input voltage low TxD, SEN/STA VIL 0.25 VCC

Input voltage high TxD, SEN/STA VIH 0.75 VCC

Input voltage low BUS VIL 0.45 VS

Input voltage high BUS VIH 0.55 VS

Hysteresis BUS VHYS 50 mV

0 ≤ VBUS ≤ 40 V 400 600 1500

0 ≤ VBUS ≤ 40 V

1300

Input restistance BUS RINBUS TA ≤ 125 °C kΩ

VBUS = -25V

60

TA ≤ 125 °C

VS = 12V, SENSE = low

1.2

IOUT = 40 mA

Output voltage BUS VBUS V

VS = 12V, SENSE = low

1.0

IOUT = 25 mA

Current limitation BUS ILIM VBUS > 2.5V 40 100 mA

Output voltage low RxD VOL IOUT = 1 mA 0.8 V

Output voltage high RxD VOH IOUT = -1mA VCC-0.8 V

3901003122 Page 9 Dec/04

Rev 004

TH3122

K-Bus Transceiver with integrated Voltage Regulator

Dynamic Characteristics

(5.25V ≤ VS ≤ 16V, 4.75V ≤ VCC ≤ 5.25V, -40°C ≤ TA ≤ 125°C, unless otherwise specified)

Parameter Symbol Condition Min Typ Max Unit

RESET

RVTR < 1 k Ω 70 100 140 ms

Reset time tRes

RVTR > 45 k Ω 10 15 20 ms

Reset rising time trr 3.0 6.5 10 µs

K-Bus-Interface

Slew rate BUS falling edge dV/dTfall -2.2 -1.6 -1.0

V/µs

Slew rate BUS rising edge dV/dTrise 1.0 1.6 2.2

Symmetry of Slew rate BUS dV/dTsym 0.3 V/µ s

Debouncing time BUS tdebBUS High pulse or low pulse 1.5 2.8 4.0 µs

Symmetry of debouncing BUS tdebsym 0.5 µs

Propagation delay TxD -> RxD tpd 20 µs

Symmetry of propagation delay

tpdsym 3.5 µs

TxD -> RxD

Bit compare time BUS, SENSE, TxD tbc 35 52 70 µs

Recovery time BUS, TxD trec 30 50 75 µs

Inhibit time for transmit BUS, TxD tena 0.92 1.33 1.8 ms

Constant low switch off BUS, TxD tlow 3 6 12 ms

Oscillator frequency fOSC 8 12 15 kHz

Debouncing time TxD tdeb 0.6 1.0 1.5 µs

Debouncing time EN tdeb 200 ns

Wake-up debouncing BUS tdebWake 25 45 90 µs

Propagation delay SI -> SO tpdcomp 4 11 µs

Debouncing VS-SENSE tdeb 10 17 25 µs

3901003122 Page 10 Dec/04

Rev 004

TH3122

K-Bus Transceiver with integrated Voltage Regulator

Pin Description

VS 1 16 VCC

EN 2 15 SENSE

VTR 3 14 RESET

GND 4 13 GND

TH3122

GND 5 12 GND

BUS 6 11 TxD

SI 7 10 RxD

SO 8 9 SEN/STA

Pin Name I/O Function

1 VS Supply voltage

2 EN I Enable Input voltage regulator, HV-pull-down-Input, High-active

3 VTR I Analogue Input - definition of reset time und Reset voltage level

4 GND Ground

5 GND Ground

6 BUS I/O Bi-directional bus line

7 SI I Comparator Input, HV-Input

8 SO O 5V-Comparator Output

9 SEN/STA I/O Send status

10 RxD O Receive Output, 5V-push-pull

11 TxD I 5V-Transmit Input, pull-up-Input

12 GND Ground

13 GND Ground

14 RESET O 5V-output reset, active low

15 SENSE O 5V-output of VS-Monitoring

16 VCC O Regulator output 5V/100mA

3901003122 Page 11 Dec/04

Rev 004

TH3122

K-Bus Transceiver with integrated Voltage Regulator

Mechanical Specifications

DF (SOIC16) Package Dimensions

E H

1 2 3

A1 A α

e b L

Small Outline Integrated Circiut (SOIC), DF (SOIC 16, 300 mil)

All Dimension in mm, coplanarity < 0.1 mm

D E H A A1 e b L α

min 10.1 7.40 10.00 2.35 0.10 0.33 0.40 0°

1.27

max 10.5 7.60 10.65 2.65 0.30 0.51 1.27 8°

All Dimension in inch, coplanarity < 0.004”

min 0.398 0.291 0.394 0.093 0.004 0.013 0.016 0°

0.050

max 0.413 0.299 0.419 0.104 0.012 0.020 0.050 8°

3901003122 Page 12 Dec/04

Rev 004

TH3122

K-Bus Transceiver with integrated Voltage Regulator

Assembly Information

This Melexis device is classified and qualified regarding soldering technology, solderability and moisture sensitivity level,

as defined in this specification, according to following test methods:

IPC/JEDEC J-STD-020

Moisture/Reflow Sensitivity Classification For Nonhermetic Solid State Surface Mount Devices

(classification reflow profiles according to table 5-2)

EIA/JEDEC JESD22-A113

Preconditioning of Nonhermetic Surface Mount Devices Prior to Reliability Testing

(reflow profiles according to table 2)

CECC00802

Standard Method For The Specification of Surface Mounting Components (SMDs) of Assessed Quality

EIA/JEDEC JESD22-B106

Resistance to soldering temperature for through-hole mounted devices

EN60749-15

Resistance to soldering temperature for through-hole mounted devices

MIL 883 Method 2003 / EIA/JEDEC JESD22-B102

Solderability

For all soldering technologies deviating from above mentioned standard conditions (regarding peak temperature,

temperature gradient, temperature profile etc) additional classification and qualification tests have to be agreed upon with

Melexis.

The application of Wave Soldering for SMD’s is allowed only after consulting Melexis regarding assurance of adhesive

strength between device and board.

Based on Melexis commitment to environmental responsibility, European legislation (Directive on the Restriction of the

Use of Certain Hazardous substances, RoHS) and customer requests, Melexis has installed a roadmap to qualify their

package families for lead free processes also.

Various lead free generic qualifications are running, current results on request.

For more information on Melexis lead free statement see quality page at our website:

http://www.melexis.com/html/pdf/MLXleadfree-statement.pdf

ESD Precautions

Electronic semiconductor products are sensitive to Electro Static Discharge (ESD).

Always observe Electro Static Discharge control procedures whenever handling semiconductor products.

3901003122 Page 13 Dec/04

Rev 004

TH3122

K-Bus Transceiver with integrated Voltage Regulator

Disclaimer

Devices sold by Melexis are covered by the warranty and patent indemnification provisions appearing in its

Term of Sale. Melexis makes no warranty, express, statutory, implied, or by description regarding the

information set forth herein or regarding the freedom of the described devices from patent infringement.

Melexis reserves the right to change specifications and prices at any time and without notice. Therefore,

prior to designing this product into a system, it is necessary to check with Melexis for current information.

This product is intended for use in normal commercial applications. Applications requiring extended

temperature range, unusual environmental requirements, or high reliability applications, such as military,

medical life-support or life-sustaining equipment are specifically not recommended without additional

processing by Melexis for each application.

The information furnished by Melexis is believed to be correct and accurate. However, Melexis shall not be

liable to recipient or any third party for any damages, including but not limited to personal injury, property

damage, loss of profits, loss of use, interrupt of business or indirect, special incidental or consequential

damages, of any kind, in connection with or arising out of the furnishing, performance or use of the

technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of

Melexis’ rendering of technical or other services.

© 2002 Melexis NV. All rights reserved.

For the latest version of this document, go to our website at:

www.melexis.com

Or for additional information contact Melexis Direct:

Europe and Japan: All other locations:

Phone: +32 13 67 04 95 Phone: +1 603 223 2362

E-mail: sales_europe@melexis.com E-mail: sales_usa@melexis.com

ISO/TS 16949 and ISO14001 Certified

3901003122 Page 14 Dec/04

Rev 004

Das könnte Ihnen auch gefallen

- BL15721A Meter-Bus Transceiver: FeaturesDokument11 SeitenBL15721A Meter-Bus Transceiver: Featuresercan akalanNoch keine Bewertungen

- BL15721A Meter-Bus Transceiver: FeaturesDokument11 SeitenBL15721A Meter-Bus Transceiver: Featuresercan akalanNoch keine Bewertungen

- Bd9g341aefj LBDokument30 SeitenBd9g341aefj LBFantazsta White Trash.Noch keine Bewertungen

- Soldadora UTC3843DDokument9 SeitenSoldadora UTC3843DChristian ormeñoNoch keine Bewertungen

- TB6674FAG ToshibaDokument18 SeitenTB6674FAG ToshibalucianassisNoch keine Bewertungen

- Am5890s V1.5TSDokument11 SeitenAm5890s V1.5TSflo72afNoch keine Bewertungen

- TB9000AFGDokument11 SeitenTB9000AFGLoengrin MontillaNoch keine Bewertungen

- Tea 5170Dokument9 SeitenTea 5170Erasmo Franco SNoch keine Bewertungen

- Data Sheet: TDA8547TSDokument21 SeitenData Sheet: TDA8547TSbamz pamungkasNoch keine Bewertungen

- XG7100 TransceiverDokument6 SeitenXG7100 Transceiverbettinemed2023Noch keine Bewertungen

- LNBP21Dokument20 SeitenLNBP21Mariana MoraesNoch keine Bewertungen

- XL4301 enDokument10 SeitenXL4301 enSelman ÇORANoch keine Bewertungen

- Moog-L VDT Oscillator DemodulatorDokument2 SeitenMoog-L VDT Oscillator DemodulatorLuis Jonathan Bahamaca FernandezNoch keine Bewertungen

- Multi-Output Power Supplies With Vcom Amplifier and High-Voltage Gamma Reference For LCD Tvs Max17126BDokument34 SeitenMulti-Output Power Supplies With Vcom Amplifier and High-Voltage Gamma Reference For LCD Tvs Max17126BFrank GomezNoch keine Bewertungen

- 3842a DatasheetDokument8 Seiten3842a DatasheetVịnh DemoNoch keine Bewertungen

- Ta 8429 HDokument14 SeitenTa 8429 HrikyNoch keine Bewertungen

- TMR1302 Datasheet EN V1.1Dokument5 SeitenTMR1302 Datasheet EN V1.1shreyas dasNoch keine Bewertungen

- Data Interface: DescriptionDokument11 SeitenData Interface: DescriptionDidier DoradoNoch keine Bewertungen

- Power Converters Lab ManualDokument89 SeitenPower Converters Lab ManualHari PrasadNoch keine Bewertungen

- 16120FPDokument38 Seiten16120FPCesar EljureNoch keine Bewertungen

- UC3848Dokument12 SeitenUC3848isaiasvaNoch keine Bewertungen

- Single-Stage BJT Amplifiers: Experiment-2Dokument19 SeitenSingle-Stage BJT Amplifiers: Experiment-2karan007_mNoch keine Bewertungen

- Control IC For Single-Ended and Push-Pull Switched-Mode Power Supplies (SMPS) TDA 4718 ADokument17 SeitenControl IC For Single-Ended and Push-Pull Switched-Mode Power Supplies (SMPS) TDA 4718 ASledge HammerNoch keine Bewertungen

- Utc3842 YouwangelectronicsDokument9 SeitenUtc3842 YouwangelectronicsMindSet MarcosNoch keine Bewertungen

- LM5030 Application: DC - DC Converter Utilizing The Push-Pull TopologyDokument10 SeitenLM5030 Application: DC - DC Converter Utilizing The Push-Pull TopologyEdoardoNoch keine Bewertungen

- Max 17122Dokument35 SeitenMax 17122master -DvNoch keine Bewertungen

- Fujitsu mb1502Dokument15 SeitenFujitsu mb1502haha2012Noch keine Bewertungen

- AT2003Dokument7 SeitenAT2003williamsarenas75Noch keine Bewertungen

- LD 7550 - Controlador PWMDokument10 SeitenLD 7550 - Controlador PWMTiago LeonhardtNoch keine Bewertungen

- Ec48324 FV PDFDokument11 SeitenEc48324 FV PDFАлександрNoch keine Bewertungen

- 2 SD 1669Dokument3 Seiten2 SD 1669Luis Alberto Baca VaccaroNoch keine Bewertungen

- Boost (Step-Up) WLED Driver With OVP: General DescriptionDokument8 SeitenBoost (Step-Up) WLED Driver With OVP: General DescriptiondneprashNoch keine Bewertungen

- Am5868 PDFDokument10 SeitenAm5868 PDFСергей АльохінNoch keine Bewertungen

- AM5766Dokument10 SeitenAM5766Kanthan Kanth0% (1)

- Current Sense Circuit CollectionDokument5 SeitenCurrent Sense Circuit CollectionDalla Torre CustomsNoch keine Bewertungen

- TV/VCR Tuner Ic With DC/DC Converter: FeaturesDokument21 SeitenTV/VCR Tuner Ic With DC/DC Converter: FeaturesEdsel SilvaNoch keine Bewertungen

- UTC2411Dokument3 SeitenUTC2411Lenon Salazar100% (1)

- 1ch Buck Converter Integrated FET: 12V To 76V Input Voltage Range 3A Output CurrentDokument29 Seiten1ch Buck Converter Integrated FET: 12V To 76V Input Voltage Range 3A Output CurrentDuc VoquangNoch keine Bewertungen

- Integrados KaDokument20 SeitenIntegrados KaJosé Carlos de Barros MelloNoch keine Bewertungen

- TMRPDDokument6 SeitenTMRPDPrime HydraulicsNoch keine Bewertungen

- Iso 9141 InterfaceDokument12 SeitenIso 9141 Interfacemilinda1100100% (1)

- Tca 785 DatasheetDokument18 SeitenTca 785 DatasheetCarlos SilvaNoch keine Bewertungen

- TDF8553J: 1. General DescriptionDokument47 SeitenTDF8553J: 1. General DescriptionJosé Joaquim Braga BragaNoch keine Bewertungen

- CH-4 Edc UploadDokument17 SeitenCH-4 Edc UploadOTHEOZ NFTNoch keine Bewertungen

- Tja1041 PDFDokument26 SeitenTja1041 PDFKeno0Noch keine Bewertungen

- Features General Description: Universal DC/DC ConverterDokument10 SeitenFeatures General Description: Universal DC/DC ConverterJagadheesh JagadheeshNoch keine Bewertungen

- HA17524Dokument18 SeitenHA175248403c36589584aNoch keine Bewertungen

- LMX2322Dokument14 SeitenLMX2322Igo_MichelNoch keine Bewertungen

- TLE4216G - Digifant 1.74Dokument15 SeitenTLE4216G - Digifant 1.74MecaSoftwareNoch keine Bewertungen

- TL1451Dokument14 SeitenTL1451Teyfik koyuncuNoch keine Bewertungen

- Self-Oscillating Half-Bridge Driver: Features Product SummaryDokument6 SeitenSelf-Oscillating Half-Bridge Driver: Features Product SummaryJean AlvesNoch keine Bewertungen

- TLE4266G SiemensSemiconductorGroupDokument9 SeitenTLE4266G SiemensSemiconductorGroupDuranRod2013Noch keine Bewertungen

- TSS721Dokument14 SeitenTSS721api-3744762100% (1)

- HT2273 Hot ChipDokument11 SeitenHT2273 Hot ChipАндрей ШипетунNoch keine Bewertungen

- IRAMS10UP60B: Series 10A, 600VDokument17 SeitenIRAMS10UP60B: Series 10A, 600VAngel VelasquezNoch keine Bewertungen

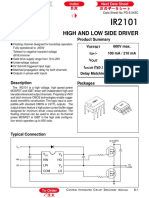

- IR2101 Datasheet PDFDokument6 SeitenIR2101 Datasheet PDFAbdul Moeez AliNoch keine Bewertungen

- Datasheet PDFDokument6 SeitenDatasheet PDFAhmed ElShoraNoch keine Bewertungen

- CD 00003131Dokument24 SeitenCD 000031314131etasNoch keine Bewertungen

- Protected Quad Power Driver: Description Features and BenefitsDokument8 SeitenProtected Quad Power Driver: Description Features and BenefitsAnkitNoch keine Bewertungen

- ErrnoDokument3 SeitenErrnoSasa MitrovicNoch keine Bewertungen

- NGSL+1 01+by+bandDokument181 SeitenNGSL+1 01+by+bandSasa MitrovicNoch keine Bewertungen

- ErrnoDokument3 SeitenErrnoSasa MitrovicNoch keine Bewertungen

- Tempfet BTS 132: FeaturesDokument11 SeitenTempfet BTS 132: FeaturesSasa MitrovicNoch keine Bewertungen

- HRDokument5 SeitenHRSasa MitrovicNoch keine Bewertungen

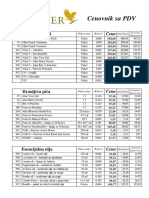

- Cenovnik Sa PDV: Forever PaketiDokument4 SeitenCenovnik Sa PDV: Forever PaketiSasa MitrovicNoch keine Bewertungen

- T5 Pin Connector Assignments Selected Connections PDFDokument10 SeitenT5 Pin Connector Assignments Selected Connections PDFSasa MitrovicNoch keine Bewertungen

- T5 Pin Connector Assignments Selected Connections PDFDokument10 SeitenT5 Pin Connector Assignments Selected Connections PDFSasa MitrovicNoch keine Bewertungen

- Can (M) G VW t5 03Dokument2 SeitenCan (M) G VW t5 03Sasa MitrovicNoch keine Bewertungen

- Log TMBAG6NEXD0028904 210446km 130765miDokument6 SeitenLog TMBAG6NEXD0028904 210446km 130765miSasa MitrovicNoch keine Bewertungen

- BC846ALT1G Series, SBC846ALT1G Series General Purpose TransistorsDokument13 SeitenBC846ALT1G Series, SBC846ALT1G Series General Purpose TransistorsSasa MitrovicNoch keine Bewertungen

- Form of The Future Progressive TenseDokument2 SeitenForm of The Future Progressive TenseSasa MitrovicNoch keine Bewertungen

- Overview of Semiconductive Shield Technology in Power Distribution CablesDokument6 SeitenOverview of Semiconductive Shield Technology in Power Distribution CablesA. HassanNoch keine Bewertungen

- Ee2259 Set1Dokument11 SeitenEe2259 Set1kaliappan45490Noch keine Bewertungen

- Wireless Power Transmission Via Solar Power SatelliteDokument25 SeitenWireless Power Transmission Via Solar Power Satelliteyuben joseph82% (34)

- Photovoltaic Silicon Wafer - SUMCO CORPORATIONDokument21 SeitenPhotovoltaic Silicon Wafer - SUMCO CORPORATIONlawrence_yuen_3Noch keine Bewertungen

- ECD Exp 4Dokument2 SeitenECD Exp 4Saad MerajNoch keine Bewertungen

- Linear Integrated Circuits - EC2254Dokument77 SeitenLinear Integrated Circuits - EC2254Muthu LakiNoch keine Bewertungen

- ESR Tester DIY - SKU136841Dokument9 SeitenESR Tester DIY - SKU136841AmbrosiousNoch keine Bewertungen

- Lab2 ASKDokument6 SeitenLab2 ASKNasly Realpe100% (2)

- Experiment #04 To Understand The Operation of Over Current RelayDokument5 SeitenExperiment #04 To Understand The Operation of Over Current RelayMuniba FatimaNoch keine Bewertungen

- VB325SP (Drive Bob - Ecosport)Dokument11 SeitenVB325SP (Drive Bob - Ecosport)Joil LeandroNoch keine Bewertungen

- TPA3138D2 10-W, 3.5-V To 14.4-V, Inductor Free, Stereo Class-D Speaker AmplifierDokument37 SeitenTPA3138D2 10-W, 3.5-V To 14.4-V, Inductor Free, Stereo Class-D Speaker AmplifierAdrianNoch keine Bewertungen

- MotorsDokument31 SeitenMotorsstraffor100% (1)

- Electronic Nose PDFDokument3 SeitenElectronic Nose PDFNur Alam ChowdhuryNoch keine Bewertungen

- 1024K NV SRAM With Phantom Clock: DS1248/DS1248PDokument19 Seiten1024K NV SRAM With Phantom Clock: DS1248/DS1248Pjoao victorNoch keine Bewertungen

- Sharif Digital Flow Introduction Part I: Synthesize & Power AnalyzeDokument128 SeitenSharif Digital Flow Introduction Part I: Synthesize & Power AnalyzejohnmechanjiNoch keine Bewertungen

- Difference Between BJT and MOSFET - Advantages & DisadvantagesDokument1 SeiteDifference Between BJT and MOSFET - Advantages & DisadvantagesShiva H. AdhikariNoch keine Bewertungen

- Light Dimmer Circuit Using TRAICDokument9 SeitenLight Dimmer Circuit Using TRAICManish Kumar sharma100% (2)

- An61546 001-61546Dokument9 SeitenAn61546 001-61546Aldrin Pascual Clavijo MéndezNoch keine Bewertungen

- Energy Scenario and Impact of Power Electronics IN 21 CenturyDokument13 SeitenEnergy Scenario and Impact of Power Electronics IN 21 Centurysanju.babaNoch keine Bewertungen

- IES - Electronics Engineering - Network TheoryDokument83 SeitenIES - Electronics Engineering - Network TheoryUsha RaniNoch keine Bewertungen

- 11 KV MV Board.Dokument10 Seiten11 KV MV Board.costea0028Noch keine Bewertungen

- Passive Components by Gayan RoshanthaDokument112 SeitenPassive Components by Gayan Roshanthabharathi vNoch keine Bewertungen

- Speed Control of DC Shunt MotorDokument7 SeitenSpeed Control of DC Shunt MotorAakash0% (1)

- 34 Top Electronic Device and Circuits Lab Viva Questions and Answers Electronic Device and Circuits Lab Viva QuestionsDokument7 Seiten34 Top Electronic Device and Circuits Lab Viva Questions and Answers Electronic Device and Circuits Lab Viva QuestionsDINESHNoch keine Bewertungen

- TIP110, T IP115: Darlington TransistorsDokument5 SeitenTIP110, T IP115: Darlington Transistorsمحمدعبدالخالق العلوانيNoch keine Bewertungen

- RL TransientDokument35 SeitenRL Transientkrish104411Noch keine Bewertungen

- Basics of Medium-Voltage Wiring - SolarPro MagazineDokument18 SeitenBasics of Medium-Voltage Wiring - SolarPro MagazinehariNoch keine Bewertungen

- Ece 112Dokument2 SeitenEce 112oledancharlesjustineNoch keine Bewertungen

- DIY Laser Burner TutorialDokument24 SeitenDIY Laser Burner TutorialArnaldo Canelas67% (3)

- Advancement in Provskite Solar CellsDokument35 SeitenAdvancement in Provskite Solar CellsPrasad Uday BandodkarNoch keine Bewertungen