Beruflich Dokumente

Kultur Dokumente

0 - Remote - Controlled Based - Thermostate PDF

Hochgeladen von

Manasa ManpoorOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

0 - Remote - Controlled Based - Thermostate PDF

Hochgeladen von

Manasa ManpoorCopyright:

Verfügbare Formate

2019 6th International Conference on Control, Decision and

Information Technologies (CoDIT’19) | Paris, France / April 23-26, 2019

Design a Universal Remote Controlled Thermostat

Based on FPGA

Alghamdi, Ali S.

Department of Electrical Engineering

College of Engineering

Majmaah University

Majmaah 11952, Riyadh Region, Saudi Arabia

aalghamdi@mu.edu.sa

Abstract— The need to control the climate has become one of future) is, mainly dependent on the experience (knowing the

the most important issues in the man daily life. At home, office, past) and the current input applied (knowing the present). The

and car …etc. It is required that the temperature stays within the history is saved in the memory units of the ASM (flip flops or

comfortable ranges. In this paper we introduce the design of a registers). The present is represented by the current inputs

thermostat, completely based on FPGA usage. Algorithmic state

applied. The future is next state to be decided by the ASM itself.

machines, ASM, are used to control the system constituents.

Temperature setting is done via the infra-red remote control unit. ASMs consist of state variables, inputs, and outputs. A state

The system is further protected by a password, entered via the said machine accepts a sequence of inputs. Each input generates a

remote control unite, to prevent unauthorized people from new internal state that is a function of the input and the previous

changing the temperature setting. The overall system consists of a state. Each input also generates an output. Finite state machines

number of submodules. Digital submodules are converted into are state machines whose state variables, inputs, and outputs

FPGA based units and implemented using VHDL code. can be enumerated. For example, an oil refinery can be modeled

by a state machine. A traffic signal can be modeled by a finite

state machine.

Index Terms— temperature control, thermostat, remote Finite state machines are of theoretic importance to

control signals, data recognition, algorithmic state machines,

ASM, finite state machine, FSM, FPGA, VHDL.

computer science because they can model many of the concepts

of interest in the discipline. Finite state machines are also called

I. INTRODUCTION finite automata.

Our main goal in this paper is to use VHDL and the FPGA

III. SYSTEM ARCHITECTURE

technology to manipulate a climate control system in such a

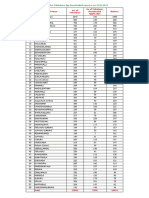

way to make the ambient temperature follow the user’s set Fig.1 shows the overall system functional units. In the center,

point. The system consists of a number of sub modules. Each there is the ASM module and its supportive units. They are all

one is designed in the block diagram level, and then converted implemented using VHDL code. The code is compiled and

to a VHDL file [1]. The overall system or better known as the converted into a binary file. The file is sent to XC3S1000 chip

top level design will be a collection of all of the above- which is already mounted on a Digilent Spartan 3-1000

mentioned modules. development board. The seven segment display and the LED

The password is a 4-digit pin number applied via a keypad array are all mounted on the development board. They provide

that will communicate through infrared radiation with an FPGA us with the compulsory information about the ASM state

development board. The development board used in this paper variables and input/output signal status for diagnosis purposes.

is the Digilent Spartan-3 prototyping board. It is equipped with It is possible throughout the design and testing processes that

a Xilinx XC3S200 FGA. the ASM gets stuck in one of its sequential states. To identify

Besides using the keypad to insert the PIN number, it is also the said problem, we should have a good state tracking method

used to insert the temperature set point. The temperature is to get a clue about the condition(s) that are forcing the state

measured using the AD595 thermocouple amplifier [2]. It is then machine to get locked at a certain state. The development board

converted to a digital value using an 8-bit analog to digital is also equipped with a number of toggle switches that supports

converter. The digitized temperature is then sent to the FPGA us to apply test signals to imitate certain input(s) or feedback

chip to compare it with the user’s set point. The air variable(s) [9]. The external infrared signal is created by any

condition/furnace control command is then generated by the infrared data transmitter. In this paper, the information source

FPGA chip. The board is also equipped with 4-digit 7- segment selected is the SONY 15-2113 remote control unit. It is the

display which is used to display both the set point and the board information supply and the tool through which a user

ambient temperature. sends information to the system (PIN code and temperature

II. ALGORITHMIC STATE MACHINES setting).

The concept of algorithmic state machine [3] [4] [5] is

originally based on the fact of a circuit that remembers the

history. Remembering history is usually, useful in deciding the

future. The ability to make a right decision (knowing the

978-1-7281-0521-5/19/$31.00 ©2019 IEEE -918-

CoDIT'19 is technical sponsored by: IEEE Systems, Man, and Cybernetics Society

Toggle

Switches

Temperatu 7-

re Sensor segment

Display

ASM and LED

7- its array

segment Supportive

Display

Modules

AC/Furnac

e

Control

Remote

IR replays

Control

Sensor

Unit

Fig. 1: ASM based IR code recognizer block diagram.

IV. SYSTEM MODULES

In this section we list the system modules with a description

for each. Four ASMs units.

a) Main_ASM module: This is the master state machine

controller. It controls the rest of the system constituents. It gives

commands and monitors the status of every module in the

system. Fig. 2 shows the state diagram of this unit. The

controller consists of 10 states. The system has one major reset

button to initialize the whole system.

State S1: In this state, MAIN_ASM, waits for a strobe from

the infrared code detector state machine module (ASM3).

While in this state, MAIN_ASM activates INS_PW signal

(insert password) to the user. It also resets all the supportive

counters. They are CNT (digit counter) and WRNG_CNT

(wrong password trial counter). It also selects the display mode

for the system (information on the four 7 segment displays).

MAIN_ASM stays in this state as long as the strobe signal

(STRB) is still low. This is an indication that ASM3 module is

still busy detecting and decoding the infrared signal it has

received from the remote control unit.

State S3: MAIN_ASM transfers to this state from S1 after

ASM3 activates the strobe signal STRB. This happens when

ASM3 finishes identifying the currently pressed remote control Fig. 2: Main controller ASM chart.

button. This transfer is accompanied by incrementing the digit

count CNT by 1. In this state, MAIN_ASM checks whether it

has received all the PIN code digits. If yes, it moves to state S5 State S7: MAIN_ASM gets into this state, every time a

and starts analyzing the received PIN code, otherwise, it moves wrong password is inserted. The wrong password counter

to state S4 and wait for the next digit. (WRNG_CNT) is incremented by 1 via a conditional output

State S4: In this state, MAIN_ASM waits for the next PIN signal (WRNG_CNT<=WRNG_CNT+1). Depending on the

digit and monitors SRTB signal. It stays in this state as long as value of WRNG_CNT counter, the next state is decided. It is S8

STRB signal is low (ASM3 is busy decoding the pressed remote if the counter exceeds the accepted limit of number of trials.

button). It moves to S3 otherwise. Otherwise, it is S3 to let the user give another attempt.

State S5: It is the state of comparing the inserted password State S8: It is the state of 4 failed password attempts. The

with that stored in the system memory (password register). The FPGA gets into hibernation for a relatively long period of time

MAIN_ASM transfers to state S7 if the two passwords match. (about 1 minute). During this period of time, the user will not

It transfers to state S6 otherwise. State S6: MAIN_ASM stays be able to try another password. It is a waiting state. After the

in this state for a while. A delay timer is initialized via a delay is over, MAIN_ASM proceeds towards S3 again.

conditional output signal, DELAY1<=X"00000000". In this State S9: MAIN_ASM gets into this state after a correct

state, a good password signal is activated and displayed to the password insertion. It is the state where temperature set point is

user (GD_PW<=’1’). The next state is state S9. selected by the user. The temperature set point is a two digit

BCD number. State S9 converts the said number into its

equivalent binary one. This is done by multiplying the tens digit

CoDIT’19 | Paris, France - April 23-26, 2019

-919-

CoDIT'19 is technical sponsored by: IEEE Systems, Man, and Cybernetics Society

by 10 then adding it to the ones digit. This state also resets the

timer counter DELAY1to 0.

State S10: This state is continuation to state S9. Here, the user

will be given few minutes to change the temperature setting

before being asked to insert the password again. This is possible

as long as ASM_MAIN is in state S10. As DELAY1 reaches its

count end, ASM_MAIN transfers back to state S1. The whole

system, then, would function as a pure temperature controller.

Any attempt to change the temperature setting, would be

preceded by password insertion and checking.

b) ADC_CONT module: This module controls and

synchronizes the operations of the analog to digital converter

unite AD7013 [6] [10]. Fig. 3 shows the state diagram of

ADC_CONT module. The state machine here is not a slave

machine. This means that is does not follow the commands of

another one. It is designed in such a way to make the ADC work

continuously without any break or halt.

State S5: It is the default state. Here ADC_CONT waits for

predefined period of time before giving the conversion order.

State S6: ADC_CONT reaches this state after the waiting

period of S5 is over (TMR counter reaches its full count). In this

state, the timer TMR is initialized to 0.

State S1: In this state, the “start conversion” command is

issued (activated by assorting signal CONV for certain period

of time equal to the count PRD2). Also the counter TMR is

incremented every clock cycle. Once the count exceeds PRD2

value, the ADC_CONT transfers to state S7.

State S7: CONV Signal is set to 0 (inactive). The CONV

signal level transfer from 0 in S6 to 1 in S1 and back to 0 in S7

initiates the conversion of the analog signal currently applied to

the ADC. The chip select (CS) and Read (RD) signals are Fig. 3: Main controller ASM chart.

deactivated in states S5, S6, S1, S7, S3 and S4 to prevent reading

any immature or invalid data from the ADC unit. This is very important to make the conversion on line and in a

State S2: In this state the ADC unit gets engaged with the real time manner.

conversion process. ADC_CONT keeps checking the BUSY c) ASM _TMP_CNTRL module: This is the third state

signal of the ADC unit. No reading is allowed in this state. Once machine module in the system. It is responsible for controlling

the ADC unit finishes the conversion, it deactivates the BUSY the furnace and the air condition units (govern these units by

signal. This causes ADC_CONT to transfer to state D1 (delay issuing appropriate ON and OFF commands). The control

state and stays there for 5 clock cycles). Then it transfers to state process is completely automatic. No man interaction is needed

S3. to change the system stetting between summer and winter

State S3: In this state ADC_CONT reads the converted data seasons. Traditional temperature controllers usually require

and saves it in its internal register DATA. This is the only that such an interaction. It is a button or switch to select the current

allows activation for the RD and CS signals. appliance to be controlled (A/C or furnace).

State S4: it is the last state in the sequence of this state Figure 4 shows the state distribution and their corresponding

machine. Here the contents of the internal register DATA are actions for ASM_TEMP_CNTRL module.

transferred to the ADC_CONT port and made available for the State S1: It is the initial state in this module. This machine is

other system constituents. ADC_CONT returns back to its initialized by the main reset button. One can notice that both of

initial state S5 to start another conversion process. It is well the furnace HT and the Air condition (A/C) are turned off. The

noticed that ADC_CONT is a free running unit. This means that machine stays in this state as long as the current temperature

it does not need a command from a higher hierarchy to start or and the temperature set point are the same. If the temperature

finalize job. All this is done automatically through the state drops below the set point, the machine jumps to state S3.

flow of the machine itself.

CoDIT’19 | Paris, France - April 23-26, 2019

-920-

CoDIT'19 is technical sponsored by: IEEE Systems, Man, and Cybernetics Society

functional blocks but piecing them together and understand

how they all work is at least as important as being able to write

the code itself. A large project like this teaches the importance

of planning, diagramming and commenting, as well as

thoroughly testing every step of the way. Had this not been

done at any stage, it would have been easy to lose track of where

we were or make it very difficult to debug any problems that

came up. Because of the use of functional block coding, we

could test and debug each function separately making it easy to

find and fix problems as they arose. This project was a ton of

work, but it was also very rewarding. As an engineer, there is

nothing better than designing, creating, and showing off a new

product. It is a relief but mostly a feeling of accomplishment

to achieve a working prototype like this.

REFERENCES

[1] [1] S. Brown and Z. Vranesic, Fundamentals of Digital Logic with

VHDL Design, 3rd ed., New York: McGraw-Hill, 2009.

[2] A. Devices, "AD594/AD595 Data sheet," 1999. [Online]. Available:

www.analog.com. [Accessed 11 Aug 2011].

[3] K. Parnell and N. Mehta, Programmable Logic Design Quick Start Hand

Book 2nd edition, Xilinx, 2002.

Fig. 4: Temperature controller state machine ASM chart.

[4] Esteban, L.; Sanchez, M.; Lopez, J.A.; Nieto-Taladriz, O.; Pedreira, P.;

Acedo, P.; , "Development of efficient FPGA-based phase meters for IR-

State S3: In this state, the heat signal (HT) is activated to turn interferometers. Optimizations for multi-channel interferometers," Real

Time Conference (RT), 2010 17th IEEE-NPSS, vol., no., pp.1-7, 24-

the furnace on, whereas AC signal is deactivated to turn the A/C

28May2010doi:10.1109/RTC.2010.5750375

off. The machine would stay in this state as long as the http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5750375&isn

measured temperature is less than the set point value. Once the umber=5750311

furnace is turned on, it will cause the temperature to rise with [5] Kehtarnavaz, N.; Mahotra, S.; , "FPGA implementation made easy for

time. applied digital signal processing courses," Acoustics, Speech and Signal

Processing (ICASSP), 2011 IEEE International Conference on

State S4: Once the temperature rises beyond the set point, the ,vol.,no.,pp.2892-2895,22-27May2011

machine transfers to state S4. In this state both of HT and AC doi:10.1109/ICASSP.2011.5947089

signals are deactivated. With time, the temperature would drop http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5947089&isn

if the current season is winter. This would cause the machine to umber=5946226

[6] Di Stefano, A.; Fiscelli, G.; Giaconia, C.G.; , "An FPGA-Based Software

jump back to sate S3. HT signal is reactivated again. This Defined Radio Platform for the 2.4GHz ISM Band," Research in

switching between S3 and S4 continues for cold weather Microelectronics and Electronics 2006, Ph. D. , vol., no., pp.73-76,0-

conditions. As the season turns gradually towards spring and 00doi:10.1109/RME.2006.1689899

http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=1689899&isn

then towards summer, we will reach the case where the

umber=35631

temperature keeps rising even when the furnace is off. This [7] C. Maxfield, The Design Warrior's Guide to FPGAs, Burlington: Mentor

usually happens during season switching from cold to hot. Graphics Corporation and Xilinx, 2004.

[8] Woei-Luen Chen; Yung-Ping Feng; Chun-Hao Pien; , "A simple

approach to the realization of an FPGA-based harmonic elimination

V. CONCLUSION AND FUTURE WORK PWM generator," Electrical Machines, 2008. ICEM 2008. 18th

International Conference on , vol., no., pp.1-5, 6-9 Sept. 2008

When this idea was first discovered and researched as a doi:10.1109/ICELMACH.2008.4799874

http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=4799874&isn

project, it was all too good to be true. The first thought was, umber=4799813

“Hasn’t this been done before” and the answer is no, not really. [9] A. Corporation, Implementing High-Performance DSP Functions in

There are similar things out there but nothing that is mass Stratix & Stratix GX Devices, Altera Corporation, 2002.

produced and nothing with all the features that this thermostat [10] FPGA Design Tutorial, 2001.

can include. Secondly, it seems like a relatively simple idea, [11] R. E. Haskell and D. M. Hanna, Learning By Example Using VHDL,

maybe too simple. Looking deeper, the VHDL programming Rochester, Michigan: Oakland University, 2007.

is actually a very complex final product. There was much [12] H. Mendenblic and W. Damman, "SIGNAL FPGA

research to do on hardware, and new circuits to be designed. IMPLEMENTATION OF A DIGITAL MODULATOR FOR DVB-S,"

15 MAY 2005. [Online]. Available: www.d-atv.com. [Accessed 13 NOV

This project required hours upon hours of writing program code 2011].

as well as testing. The scariest part was that the last thing we

could do is attempt to interface our circuit with a real home

climate control. The password protected thermostat has all the

necessary elements of a great senior project.

There was a lot of program code involved in this project, and

the only way to keep organized was through the use of

flowcharts and block diagrams. The code was written in

CoDIT’19 | Paris, France - April 23-26, 2019

-921-

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (120)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- 3 Evans V Dooley J Wright S Information TechnolDokument37 Seiten3 Evans V Dooley J Wright S Information TechnolAnna Golovko0% (1)

- Microprocessors & Its Applications CSM-3305 PDFDokument255 SeitenMicroprocessors & Its Applications CSM-3305 PDFromesh1998Noch keine Bewertungen

- An 024 Making and Receiving CSD Data CallsDokument9 SeitenAn 024 Making and Receiving CSD Data CallsHothayfaAwawdehNoch keine Bewertungen

- 98 375 html5Dokument276 Seiten98 375 html5Luis Gerardo AlonsoNoch keine Bewertungen

- Mandal Wise Volunteer Mobile App Download Report As On 31.01.2022Dokument1 SeiteMandal Wise Volunteer Mobile App Download Report As On 31.01.2022Special Cell VMCNoch keine Bewertungen

- Mitsubishi Graphic Operation Terminal GOT2000 Series (Catalog) - L08270engcDokument84 SeitenMitsubishi Graphic Operation Terminal GOT2000 Series (Catalog) - L08270engcMohamedElsawiNoch keine Bewertungen

- SJ-20100908091007-005-ZXC10 BSCB (V8.0.3.002) Controller Technical Manual PDFDokument124 SeitenSJ-20100908091007-005-ZXC10 BSCB (V8.0.3.002) Controller Technical Manual PDFengrSadiqueNoch keine Bewertungen

- VHDL Implementation of Complex Number Multiplier Using Vedic MathematicsDokument8 SeitenVHDL Implementation of Complex Number Multiplier Using Vedic MathematicsA_AyyadhNoch keine Bewertungen

- DMTSDokument5 SeitenDMTSmarkantony373Noch keine Bewertungen

- IPT ReportDokument46 SeitenIPT ReportSandeep Kumar YadlapalliNoch keine Bewertungen

- Universal Serial Bus Class Definitions For Communication DevicesDokument121 SeitenUniversal Serial Bus Class Definitions For Communication Devicese178anangNoch keine Bewertungen

- Config SSO IBM WebSphere Portal and DominoDokument25 SeitenConfig SSO IBM WebSphere Portal and DominoFernando Rodrigo DriNoch keine Bewertungen

- Chap 12Dokument14 SeitenChap 12Angela BarrNoch keine Bewertungen

- Schematics E50Dokument9 SeitenSchematics E50pronomix100% (3)

- iC-VRV: Bidirectional Μp Interface To 24VDokument12 SeiteniC-VRV: Bidirectional Μp Interface To 24VJose Maria ClaramuntNoch keine Bewertungen

- GEI-100165 Ethernet TCP-IP GEDS Standard Message Format (GSM)Dokument30 SeitenGEI-100165 Ethernet TCP-IP GEDS Standard Message Format (GSM)Mohamed Amine100% (1)

- Computer Security and Penetration Testing: Scanning ToolsDokument38 SeitenComputer Security and Penetration Testing: Scanning Toolsmervat anwarNoch keine Bewertungen

- Print Variable DataDokument24 SeitenPrint Variable DataAndrew TurnerNoch keine Bewertungen

- Loki Design DocumentDokument8 SeitenLoki Design Documenthsaavedra1Noch keine Bewertungen

- License Wizard: Installation Notes For Version 3.1Dokument26 SeitenLicense Wizard: Installation Notes For Version 3.1angusyoung1Noch keine Bewertungen

- Delphin ProfiMessage Manual enDokument219 SeitenDelphin ProfiMessage Manual enFranco LudueñaNoch keine Bewertungen

- 2G Main KPIs TroubleshootingDokument4 Seiten2G Main KPIs TroubleshootingRafiq MagdyNoch keine Bewertungen

- HTMLLDokument40 SeitenHTMLLRokesh DhanaNoch keine Bewertungen

- Cognitive TPG A760 Two-Color Thermal/Impact Hybrid Printer BrochureDokument2 SeitenCognitive TPG A760 Two-Color Thermal/Impact Hybrid Printer BrochureJohnny BarcodeNoch keine Bewertungen

- 3 Fe 68884 Aaabfmzza 01Dokument7 Seiten3 Fe 68884 Aaabfmzza 01alguialNoch keine Bewertungen

- Why & What Is Cooperative Learning at The Computer: Teaching TipsDokument8 SeitenWhy & What Is Cooperative Learning at The Computer: Teaching Tipsapi-296655270Noch keine Bewertungen

- DOSBox v0.74-3 ManualDokument21 SeitenDOSBox v0.74-3 ManualANoch keine Bewertungen

- Collaboration Edge Most Common Issues - CiscoDokument11 SeitenCollaboration Edge Most Common Issues - CiscoGustavo Andrés Mardones NovaNoch keine Bewertungen

- Expert Color Made Exceptionally EasyDokument4 SeitenExpert Color Made Exceptionally EasyicreatiaNoch keine Bewertungen