Beruflich Dokumente

Kultur Dokumente

Truth Table Capacitance: 0.6 M CMOS

Hochgeladen von

Arvie CaagaoOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Truth Table Capacitance: 0.6 M CMOS

Hochgeladen von

Arvie CaagaoCopyright:

Verfügbare Formate

CUB

Austria Mikro Systeme International

R NA53 0.6 µm CMOS

NA53 is a 5-input NAND gate with 3x drive strength.

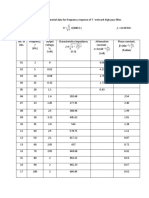

Truth Table Capacitance

A B C D E Q Ci (pF)

L X X X X H A 0.050

A

X L X X X H B B 0.050

X X L X X H C NA53 Q C 0.053

X X X L X H D D 0.056

X X X X L H E E 0.056

H H H H H L

Area Power

2

1.22 mils 14.31 µW / MHz

Delay [ns] = tpd.. = f(SL, L) with SL = Input Slope [ns] ; L = Output Load [pF]

Output Slope [ns] = op_sl.. = f(L) with L = Output Load [pF]

AC Characteristics : Tj = 25°C VDD = 5V Typical Process

AC Characteristics

SL = 0.1 SL = 2.0

Characteristics Symbol

L = 0.3 L = 2.1 L = 3.0 L = 0.3 L = 2.1 L = 3.0

tpdar 0.57 1.56 2.09 0.91 1.88 2.37

Delay A to Q

tpdaf 0.51 1.38 1.82 0.49 1.35 1.80

tpdbr 0.65 1.64 2.16 1.02 2.01 2.53

Delay B to Q

tpdbf 0.56 1.44 1.86 0.52 1.38 1.82

tpdcr 0.72 1.71 2.24 1.10 2.11 2.58

Delay C to Q

tpdcf 0.59 1.45 1.90 0.51 1.38 1.82

tpddr 0.78 1.78 2.30 1.19 2.19 2.67

Delay D to Q

tpddf 0.61 1.48 1.95 0.49 1.35 1.79

tpder 0.84 1.83 2.35 1.26 2.25 2.74

Delay E to Q

tpdef 0.61 1.50 1.92 0.44 1.30 1.73

op_slar 0.67 3.93 5.46 0.65 3.90 5.57

Output Slope A to Q

op_slaf 0.55 2.87 4.03 0.53 2.87 3.92

op_slbr 0.67 3.93 5.48 0.67 3.91 5.55

Output Slope B to Q

op_slbf 0.52 2.90 4.05 0.53 2.91 4.07

op_slcr 0.67 3.95 5.46 0.68 3.92 5.58

Output Slope C to Q

op_slcf 0.52 2.85 4.01 0.53 2.90 4.08

op_sldr 0.67 3.90 5.57 0.68 3.93 5.52

Output Slope D to Q

op_sldf 0.53 2.86 4.12 0.53 2.88 4.07

op_sler 0.68 3.88 5.53 0.67 3.93 5.57

Output Slope E to Q

op_slef 0.52 2.91 4.05 0.53 2.87 4.07

Sept. 1996 - 233 - Rev. N/C

Das könnte Ihnen auch gefallen

- Truth Table Capacitance: 0.6 M CMOSDokument2 SeitenTruth Table Capacitance: 0.6 M CMOSGuilherme CastroNoch keine Bewertungen

- 1Dokument3 Seiten1Gandhi HammoudNoch keine Bewertungen

- Modelo de EckenfelderDokument3 SeitenModelo de EckenfelderBrayan Santiago Castellanos CarranzaNoch keine Bewertungen

- Assignment 2 22Dokument4 SeitenAssignment 2 22Christila KartikaNoch keine Bewertungen

- OC CurveDokument5 SeitenOC CurveAnonymous tv3qpx2Noch keine Bewertungen

- Worked Example For Unbraced Frame Designed Colum Wind Moment MethodDokument22 SeitenWorked Example For Unbraced Frame Designed Colum Wind Moment MethodAce LowNoch keine Bewertungen

- Guia Control en Tiempo Discreto Con MATLAB TutorialDokument8 SeitenGuia Control en Tiempo Discreto Con MATLAB TutorialAthos Nikolai Campana VeraNoch keine Bewertungen

- Flume AnalysisDokument11 SeitenFlume AnalysisLarizza TesicoNoch keine Bewertungen

- Lecture 4: PID of A Spring Mass Damper SystemDokument6 SeitenLecture 4: PID of A Spring Mass Damper SystemAditya AdNoch keine Bewertungen

- Wind Load Sheet by Abid SirDokument4 SeitenWind Load Sheet by Abid SirMohammad KasimNoch keine Bewertungen

- CMOS Digital Integrated Circuits Analysis and Design 4th Edition Kang Solutions Manual DownloadDokument23 SeitenCMOS Digital Integrated Circuits Analysis and Design 4th Edition Kang Solutions Manual DownloadRodolfo Wilson100% (28)

- Plantilla Parámetros FC Vía Oral 2023 IIDokument1 SeitePlantilla Parámetros FC Vía Oral 2023 IIALEJANDRINA MARIA LLAURE MORANoch keine Bewertungen

- Wind Load at ColumnDokument2 SeitenWind Load at ColumnArijit PatraNoch keine Bewertungen

- Wind LoadDokument6 SeitenWind LoadArmie May RicoNoch keine Bewertungen

- Sullana A1012Dokument5 SeitenSullana A1012gregoryNoch keine Bewertungen

- Mani MATLAB 4Dokument3 SeitenMani MATLAB 4Gosh KreativityNoch keine Bewertungen

- Chapter 6-2Dokument16 SeitenChapter 6-2Tamer Adel MohamedNoch keine Bewertungen

- Main Plant WL SupplementaryDokument6 SeitenMain Plant WL SupplementaryArmie May RicoNoch keine Bewertungen

- 0.2 Some Basic Notions About AerodynamicsDokument27 Seiten0.2 Some Basic Notions About AerodynamicsAndreu GimenezNoch keine Bewertungen

- Distillation Tower DesignDokument65 SeitenDistillation Tower DesignAntonio SilvaNoch keine Bewertungen

- Distillation Column 1 - (D01)Dokument20 SeitenDistillation Column 1 - (D01)Patricia MirandaNoch keine Bewertungen

- Atap Baja WFDokument14 SeitenAtap Baja WFNur ResikhaNoch keine Bewertungen

- 13.1 Analog and Digital Lowpass Butterworth FilterDokument7 Seiten13.1 Analog and Digital Lowpass Butterworth FiltertempNoch keine Bewertungen

- Repaso 2Dokument77 SeitenRepaso 2Marilyn Garzón AguirreNoch keine Bewertungen

- High Pass TableDokument2 SeitenHigh Pass TableShachin DasNoch keine Bewertungen

- Chi Kuadrat Dan SmirnovDokument3 SeitenChi Kuadrat Dan SmirnovMuhandi Arso (D1011231057MUHANDIARSO)Noch keine Bewertungen

- Belcorp Tocancipá - Colombia Printed: 2/11/2018 - 8:10:19 A. M. Measured On: Spectro-Guide Sphere CRIISS File Name: Contingencia Celso - WSVDokument3 SeitenBelcorp Tocancipá - Colombia Printed: 2/11/2018 - 8:10:19 A. M. Measured On: Spectro-Guide Sphere CRIISS File Name: Contingencia Celso - WSVLuis Felipe BenavidesNoch keine Bewertungen

- Solution of Problems Chapter 4Dokument8 SeitenSolution of Problems Chapter 4Zack ZoldyckNoch keine Bewertungen

- Milestone PresentationDokument33 SeitenMilestone PresentationESTEBAN LLANONoch keine Bewertungen

- Seismic Activity 1Dokument2 SeitenSeismic Activity 1bsce.delossantos.rizza.mNoch keine Bewertungen

- RincianperhitunganDokument6 SeitenRincianperhitunganKucing PilekNoch keine Bewertungen

- Lab 7Dokument2 SeitenLab 7joy002anuNoch keine Bewertungen

- FormulasDokument1 SeiteFormulasayeshaarain780Noch keine Bewertungen

- Distillation Tower DesignDokument66 SeitenDistillation Tower DesignHavocFireNoch keine Bewertungen

- Expt. 9 Natural ConvectionDokument5 SeitenExpt. 9 Natural ConvectionPradeep DiwakarNoch keine Bewertungen

- CPVST: Fase Distribusi Fase EliminasiDokument3 SeitenCPVST: Fase Distribusi Fase EliminasiEma MohamadNoch keine Bewertungen

- Sem 2 HomeworksDokument15 SeitenSem 2 HomeworksprakshiNoch keine Bewertungen

- TemplateDokument46 SeitenTemplateprakshiNoch keine Bewertungen

- Activity Predecessor O M P PERT Mean Pert SD A B C D E F G H I JDokument7 SeitenActivity Predecessor O M P PERT Mean Pert SD A B C D E F G H I JSampurnaNoch keine Bewertungen

- EDA VHDL SimulationDokument19 SeitenEDA VHDL SimulationYQ WNoch keine Bewertungen

- For M1: Open Loop:: All 'S' 'Response' 'Time' 'Amplitude'Dokument4 SeitenFor M1: Open Loop:: All 'S' 'Response' 'Time' 'Amplitude'Rasheed ShahNoch keine Bewertungen

- Calor Lat Vap Chopey - Djra Mipg20Dokument11 SeitenCalor Lat Vap Chopey - Djra Mipg20Dan JefteNoch keine Bewertungen

- Book1 Sem 2Dokument61 SeitenBook1 Sem 2prakshiNoch keine Bewertungen

- Activity 3: Distillation With Side Stream ProblemDokument8 SeitenActivity 3: Distillation With Side Stream ProblemFerlyn Jade RanteNoch keine Bewertungen

- Data Hidrogeo DebitDokument6 SeitenData Hidrogeo DebitMahwarti Novelli PurbaNoch keine Bewertungen

- Medical Instrumentation Application and Design 4th Edition Webster Solutions ManualDokument13 SeitenMedical Instrumentation Application and Design 4th Edition Webster Solutions ManualSaraRogersrbwgd100% (15)

- Destilasi Binner & Multi KomponenDokument8 SeitenDestilasi Binner & Multi KomponenApril Rianto BaktiarNoch keine Bewertungen

- AdsorpsiDokument1 SeiteAdsorpsiAfifatut ThoyyibahNoch keine Bewertungen

- Consolidation TestDokument33 SeitenConsolidation TestAbbas tahmasebi poorNoch keine Bewertungen

- Purlin As Cold Formed Design - Rev.ADokument13 SeitenPurlin As Cold Formed Design - Rev.ADewi CuantikNoch keine Bewertungen

- AITS 1819 FT IV JEEA Paper 1 Sol PDFDokument11 SeitenAITS 1819 FT IV JEEA Paper 1 Sol PDFPrabhatSharmaNoch keine Bewertungen

- 10 C C 2.303 KT - C Log C Log: Pebc Pharmacist Evaluating ExaminationDokument1 Seite10 C C 2.303 KT - C Log C Log: Pebc Pharmacist Evaluating ExaminationbhaveshNoch keine Bewertungen

- Wind Load Is 875Dokument21 SeitenWind Load Is 875kedar sabharanjakNoch keine Bewertungen

- Sci LabDokument22 SeitenSci LabHarithuvarNoch keine Bewertungen

- Wind Load Section C - Gable RoofDokument6 SeitenWind Load Section C - Gable Rooffred anthony UeraNoch keine Bewertungen

- Cong ThucDokument3 SeitenCong Thucphucthinh221202Noch keine Bewertungen

- Mathcad - 22-ASCE Wind LoadsDokument3 SeitenMathcad - 22-ASCE Wind LoadsSok RaksaNoch keine Bewertungen

- Discrete Cosine Transform: Algorithms, Advantages, ApplicationsVon EverandDiscrete Cosine Transform: Algorithms, Advantages, ApplicationsNoch keine Bewertungen

- Diskless CloningDokument8 SeitenDiskless CloningArvie CaagaoNoch keine Bewertungen

- GUIDELINES 2017 Pinoy K Pop StarDokument9 SeitenGUIDELINES 2017 Pinoy K Pop StarArvie CaagaoNoch keine Bewertungen

- SEVENTEENDokument8 SeitenSEVENTEENArvie Caagao100% (1)

- Chapter 1Dokument46 SeitenChapter 1Arvie CaagaoNoch keine Bewertungen

- Acknowledgement I. CHAPTER I - The Problem and Its Background 1Dokument4 SeitenAcknowledgement I. CHAPTER I - The Problem and Its Background 1Arvie CaagaoNoch keine Bewertungen

- OBLICONDokument13 SeitenOBLICONZARANoch keine Bewertungen

- Ebook Principles of Corporate Finance PDF Full Chapter PDFDokument67 SeitenEbook Principles of Corporate Finance PDF Full Chapter PDFmichelle.haas303100% (28)

- GB Programme Chart: A B C D J IDokument2 SeitenGB Programme Chart: A B C D J IRyan MeltonNoch keine Bewertungen

- Leadership Assesment ToolDokument5 SeitenLeadership Assesment ToolJayeeta DebnathNoch keine Bewertungen

- Ems Accounting Term 2Dokument39 SeitenEms Accounting Term 2Paballo KoopediNoch keine Bewertungen

- Add MITx Credentials To Resume and LinkedIn PDFDokument5 SeitenAdd MITx Credentials To Resume and LinkedIn PDFRizwanNoch keine Bewertungen

- Ten Rules of NetiquetteDokument11 SeitenTen Rules of NetiquetteAriel CancinoNoch keine Bewertungen

- Social and Prof Issues Module2Dokument31 SeitenSocial and Prof Issues Module2Angelo NebresNoch keine Bewertungen

- Test Help StatDokument18 SeitenTest Help Statthenderson22603Noch keine Bewertungen

- Argumentative E-WPS OfficeDokument6 SeitenArgumentative E-WPS OfficeoneNoch keine Bewertungen

- 1GR FE LubricationDokument19 Seiten1GR FE LubricationJesus LayaNoch keine Bewertungen

- MetalsMagazine 2 2018 PDFDokument116 SeitenMetalsMagazine 2 2018 PDFJack 123Noch keine Bewertungen

- Raul C. Cosare v. Broadcom Asia Inc. and Dante ArevaloDokument4 SeitenRaul C. Cosare v. Broadcom Asia Inc. and Dante ArevaloRam Migue SaintNoch keine Bewertungen

- No. 3 - Republic vs. DiazDokument7 SeitenNo. 3 - Republic vs. DiazMark Gabriel MarangaNoch keine Bewertungen

- Assignment Brief HNHM301 The Contemporary Hospitality IndustryDokument6 SeitenAssignment Brief HNHM301 The Contemporary Hospitality IndustryTanjum Tisha100% (1)

- Auto Setting DataDokument6 SeitenAuto Setting Datahalo91Noch keine Bewertungen

- UNDCO Disability Inclusion Strategy 2022 - 2025Dokument28 SeitenUNDCO Disability Inclusion Strategy 2022 - 2025Nelson MichmeNoch keine Bewertungen

- Business Ethics Final Work Brief 2Dokument6 SeitenBusiness Ethics Final Work Brief 2KALIZA TRESSY MEGHANNoch keine Bewertungen

- Final Report Air ConditioningDokument42 SeitenFinal Report Air ConditioningAzmi Matali73% (11)

- User's Guide: Smartpack2 Master ControllerDokument32 SeitenUser's Guide: Smartpack2 Master Controllermelouahhh100% (1)

- Sample Rubrics MakingDokument4 SeitenSample Rubrics MakingKerstmis “Scale” NataliaNoch keine Bewertungen

- Balanced Scorecard Approach ReportDokument8 SeitenBalanced Scorecard Approach ReportGeryes E. Haddad100% (1)

- Triptico NIC 16Dokument3 SeitenTriptico NIC 16Brayan HMNoch keine Bewertungen

- PV1800VPM SEREIS (1-5KW) : Pure Sine Wave High Frequency Solar Inverter With MPPT InsideDokument4 SeitenPV1800VPM SEREIS (1-5KW) : Pure Sine Wave High Frequency Solar Inverter With MPPT InsideHuber CallataNoch keine Bewertungen

- Malik Tcpdump FiltersDokument41 SeitenMalik Tcpdump FiltersombidasarNoch keine Bewertungen

- Management of HondaDokument8 SeitenManagement of HondafarhansufiyanNoch keine Bewertungen

- Sydney Boys 2017 2U Accelerated Prelim Yearly & SolutionsDokument26 SeitenSydney Boys 2017 2U Accelerated Prelim Yearly & Solutions黄心娥Noch keine Bewertungen

- Battlab Report 12 FinalDokument48 SeitenBattlab Report 12 FinalLianNoch keine Bewertungen

- The World Wide WebDokument22 SeitenThe World Wide WebSa JeesNoch keine Bewertungen

- Tugas Moneter CH 4 - Dewi Lucky Aryanti Sinaga F1119025Dokument4 SeitenTugas Moneter CH 4 - Dewi Lucky Aryanti Sinaga F1119025Scream InungNoch keine Bewertungen