Beruflich Dokumente

Kultur Dokumente

4507 CPLD and FPGA Architectures

Hochgeladen von

shobiCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

4507 CPLD and FPGA Architectures

Hochgeladen von

shobiCopyright:

Verfügbare Formate

Injntu.com Injntu.

com

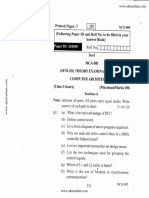

Code No: I5702/R16

M. Tech. I Semester Regular/Supple Examinations, Jan/Feb -2018

CPLD AND FPGA ARCHITECTURES AND APPLICATIONS

Common to VLSI (57), VLSID (72), VLSI System Design (61), VLSI & Micro Electronics (76)

Time: 3 Hours Max. Marks: 60

Answer any FIVE Questions

All Questions Carry Equal Marks

m

1. a Implement a BCD to Excess-3 code converter by ROM. Calculate the cross point 6M

density of the implementation?

b Explain few differences between programmable logic device and Complex 6M

programmable logic devices?

2. a Explain the concept of Programmable I/O blocks in FPGAs? 6M

co

b Briefly discuss about the applications of FPGA? 6M

3. a What is a Trade-off? Discuss about the different design Trade-offs? 6M

b Draw and explain the CLB and IO Blocks of Xilinx XC2000 architecture? 6M

4. a How the ACT3 architecture is different from ACT2 architecture? Explain the ACT3 6M

architecture in detail.

b Explain the ACT2 architecture for high fan-in example? 6M

u.

5. a Design a five bit binary counter with ACT devices? 6M

b Write a short note on a position tracker for a robot manipulator? 6M

6. a With neat block diagram, explain the architecture of Xilinx Cool Runner 6M

XCR3064XL CPLD?

b When is CPLD better suited than SPLD? List out the comparisons between those 6M

nt

two.

7. a Tabulate the comparisons of different XC3000 family members? 6M

b Write a short note on Programming Technology? 6M

8. Write a short note on 12M

j

i) Duplicated logic ii) Clock enables iii) Iterative design methodologies

*****

in

1 of 1

Injntu.com ||''|'''|''|''|'''|| Injntu.com Injntu.com

Das könnte Ihnen auch gefallen

- WWW - Manaresults.Co - In: CPLD and Fpga Architectures and ApplicationsDokument1 SeiteWWW - Manaresults.Co - In: CPLD and Fpga Architectures and ApplicationskopperundeviNoch keine Bewertungen

- WWW - Manaresults.Co - In: Answer Any FIVE Questions All Questions Carry Equal MarksDokument1 SeiteWWW - Manaresults.Co - In: Answer Any FIVE Questions All Questions Carry Equal MarksSarath Chandra SuraganiNoch keine Bewertungen

- Month & Year: March, 2019 Semester: Seventh Subject Code: 14CS IT 706 (Common To CSE and IT) Subject Name: Embedded SystemsDokument5 SeitenMonth & Year: March, 2019 Semester: Seventh Subject Code: 14CS IT 706 (Common To CSE and IT) Subject Name: Embedded Systemskeerthi mickelNoch keine Bewertungen

- VLSI Architecture and System Design subject questions on FPGA, ASIC, CPLD architecturesDokument2 SeitenVLSI Architecture and System Design subject questions on FPGA, ASIC, CPLD architecturesAshadur RahamanNoch keine Bewertungen

- 1648 Hardware Software Co DesignDokument1 Seite1648 Hardware Software Co DesigndeepikaNoch keine Bewertungen

- 09-Advanced Computer ArchitectureDokument1 Seite09-Advanced Computer Architecturesudhakar kNoch keine Bewertungen

- 8108 CMOS Analog IC DesignDokument2 Seiten8108 CMOS Analog IC Designvenu sNoch keine Bewertungen

- Intelligent Manufacturing SystemsDokument5 SeitenIntelligent Manufacturing SystemsVenkata RamuduNoch keine Bewertungen

- University Question Papers - VLSIDokument26 SeitenUniversity Question Papers - VLSIVijayNoch keine Bewertungen

- DOCUMENT SummaryDokument4 SeitenDOCUMENT SummaryIshita SharmaNoch keine Bewertungen

- 9D57106c ASIC DesignDokument1 Seite9D57106c ASIC DesignsubbuNoch keine Bewertungen

- 523 BA19 Ad 01Dokument5 Seiten523 BA19 Ad 01ramesh1926Noch keine Bewertungen

- 09-Algorithms For Vlsi Design AutomationDokument1 Seite09-Algorithms For Vlsi Design AutomationroobetNoch keine Bewertungen

- Ap7202-Asic and FpgaDokument12 SeitenAp7202-Asic and FpgaMOTHI.R MEC-AP/ECENoch keine Bewertungen

- 54124-mt - CPLD & Fpga Architecture & ApplicationsDokument1 Seite54124-mt - CPLD & Fpga Architecture & ApplicationsSRINIVASA RAO GANTANoch keine Bewertungen

- Advanced Computer ArchitectureDokument4 SeitenAdvanced Computer ArchitectureSaikumarVavilaNoch keine Bewertungen

- COMPUTER NETWORKSDokument2 SeitenCOMPUTER NETWORKSsudhakar kNoch keine Bewertungen

- Jntua University Previous Question Papers: Dept., of E.C.E, RCEWDokument4 SeitenJntua University Previous Question Papers: Dept., of E.C.E, RCEWHarshini ANoch keine Bewertungen

- Question Paper CodeDokument3 SeitenQuestion Paper CodeDinesh SrinivasanNoch keine Bewertungen

- VLSI DesignDokument7 SeitenVLSI DesignVarun ThejNoch keine Bewertungen

- M.tech Vlsi Technology and DesignDokument1 SeiteM.tech Vlsi Technology and Designsrinivas0% (1)

- Answer All The Questions Networking: (Subject With Code)Dokument4 SeitenAnswer All The Questions Networking: (Subject With Code)gunaNoch keine Bewertungen

- Fundamentals of IoT exam questionsDokument1 SeiteFundamentals of IoT exam questionsManjot KaurNoch keine Bewertungen

- Thapar Institute of Engineering & Technology, Patiala: End Semester Examination (May 2019)Dokument4 SeitenThapar Institute of Engineering & Technology, Patiala: End Semester Examination (May 2019)Forza HorizonNoch keine Bewertungen

- 8548 Digital Signal Processors ADokument1 Seite8548 Digital Signal Processors AdeepikaNoch keine Bewertungen

- Embedded System DesignDokument23 SeitenEmbedded System DesignlosssssssssNoch keine Bewertungen

- FPGA Based System DesignDokument2 SeitenFPGA Based System Designammayi9845_930467904Noch keine Bewertungen

- DICSD Question BankDokument5 SeitenDICSD Question Bankmunimunendra00Noch keine Bewertungen

- Sri Sairam College of EngineeringDokument37 SeitenSri Sairam College of EngineeringLavanya R GowdaNoch keine Bewertungen

- 18CS44 Microcontroller Embedded Systems Model Question Paper 3Dokument2 Seiten18CS44 Microcontroller Embedded Systems Model Question Paper 3Prince AdnanNoch keine Bewertungen

- 18CS44 Model Question Paper-1 With Effect From 2019-20 (CBCS Scheme)Dokument2 Seiten18CS44 Model Question Paper-1 With Effect From 2019-20 (CBCS Scheme)M.A rajaNoch keine Bewertungen

- 18CS44 Model Question Paper-1 With Effect From 2019-20 (CBCS Scheme)Dokument2 Seiten18CS44 Model Question Paper-1 With Effect From 2019-20 (CBCS Scheme)Mansi R UNoch keine Bewertungen

- Iot SIMP TieDokument3 SeitenIot SIMP TieShazNoch keine Bewertungen

- Cse Viii Advanced Computer Architectures 06CS81 Notes PDFDokument156 SeitenCse Viii Advanced Computer Architectures 06CS81 Notes PDFHarshith HarshiNoch keine Bewertungen

- Question Paper Code:: (10×2 20 Marks)Dokument2 SeitenQuestion Paper Code:: (10×2 20 Marks)Ponraj Park100% (4)

- Erts - Model 1Dokument3 SeitenErts - Model 1Ece DeptNoch keine Bewertungen

- Vlsi DesignDokument2 SeitenVlsi DesignXXXNoch keine Bewertungen

- JNTU M.Tech Question Papers, VLSI Technology DesignDokument3 SeitenJNTU M.Tech Question Papers, VLSI Technology DesignVijay SagarNoch keine Bewertungen

- 54208-mt - Design For TestabilityDokument2 Seiten54208-mt - Design For TestabilitySRINIVASA RAO GANTA100% (1)

- Nr-Vlsi Technology and DesignDokument2 SeitenNr-Vlsi Technology and DesignSudhakar SpartanNoch keine Bewertungen

- A6508 - Low Power Vlsi DesignDokument2 SeitenA6508 - Low Power Vlsi Designramanaidu1Noch keine Bewertungen

- Comparing IPv6 and IPv4, discussing Internet Key Exchange and routing protocolsDokument2 SeitenComparing IPv6 and IPv4, discussing Internet Key Exchange and routing protocolsSahil Sharma 734Noch keine Bewertungen

- WWW - Manaresults.Co - In: Answer Any FIVE Questions All Questions Carry Equal MarksDokument1 SeiteWWW - Manaresults.Co - In: Answer Any FIVE Questions All Questions Carry Equal MarksTelugu SatyanarayanaNoch keine Bewertungen

- Model Question Paper: Seventh Semester B.E. Degree Examination (2021-22) Network ManagementDokument2 SeitenModel Question Paper: Seventh Semester B.E. Degree Examination (2021-22) Network ManagementManu MãñàñNoch keine Bewertungen

- 1 Semester Model Question PapersDokument17 Seiten1 Semester Model Question PapersBalaji MohantyNoch keine Bewertungen

- 18CS44@AzDOCUMENTS inDokument6 Seiten18CS44@AzDOCUMENTS inAzeem TopNoch keine Bewertungen

- WIRELESS+AND+MOBILE+NETWORKING Seme2 2006Dokument2 SeitenWIRELESS+AND+MOBILE+NETWORKING Seme2 2006api-26171521Noch keine Bewertungen

- COA Question PaperDokument2 SeitenCOA Question PaperwahidNoch keine Bewertungen

- It 703 B Internet of Things Dec 2020Dokument2 SeitenIt 703 B Internet of Things Dec 2020Dharmendra Singh GondNoch keine Bewertungen

- Switching Theory and Logic Design - June-2015Dokument55 SeitenSwitching Theory and Logic Design - June-2015Rama HarithaNoch keine Bewertungen

- Eprvd-102 Eprds-102a - 01.12 PDFDokument2 SeitenEprvd-102 Eprds-102a - 01.12 PDFNaresh KumarNoch keine Bewertungen

- CST202 QPDokument2 SeitenCST202 QPSreedevi R KrishnanNoch keine Bewertungen

- CST202 Computer Organization and Architecture June 2022Dokument2 SeitenCST202 Computer Organization and Architecture June 2022Abhinav SNoch keine Bewertungen

- Ap7202-Asic and FpgaDokument10 SeitenAp7202-Asic and FpgaJayapalNoch keine Bewertungen

- 19ECE349-RISC Processor Design Using HDLDokument325 Seiten19ECE349-RISC Processor Design Using HDLJatin JNoch keine Bewertungen

- PlayStation Architecture: Architecture of Consoles: A Practical Analysis, #6Von EverandPlayStation Architecture: Architecture of Consoles: A Practical Analysis, #6Noch keine Bewertungen

- GameCube Architecture: Architecture of Consoles: A Practical Analysis, #10Von EverandGameCube Architecture: Architecture of Consoles: A Practical Analysis, #10Noch keine Bewertungen

- Bebop to the Boolean Boogie: An Unconventional Guide to ElectronicsVon EverandBebop to the Boolean Boogie: An Unconventional Guide to ElectronicsBewertung: 4 von 5 Sternen4/5 (3)

- MEMS and Nanotechnology Second Mid TermDokument1 SeiteMEMS and Nanotechnology Second Mid TermshobiNoch keine Bewertungen

- Fpga Question PaperDokument1 SeiteFpga Question PapershobiNoch keine Bewertungen

- MEMS and Nanotechnology Second Mid TermDokument1 SeiteMEMS and Nanotechnology Second Mid TermshobiNoch keine Bewertungen

- BTech EIC SyllabusDokument107 SeitenBTech EIC SyllabusrajeshNoch keine Bewertungen

- GHJFHDokument7 SeitenGHJFHVarun Tank100% (1)

- 963 FamilybrochureDokument4 Seiten963 FamilybrochureAbdelkader DraïNoch keine Bewertungen

- Two Years of Jet-Grouting in British ColumbiaDokument10 SeitenTwo Years of Jet-Grouting in British ColumbiaabbidubbiNoch keine Bewertungen

- Arts Q2 Lesson 1 The Art Production of Neoclassic and Romantic Periods ObjectivesDokument8 SeitenArts Q2 Lesson 1 The Art Production of Neoclassic and Romantic Periods ObjectivesCharles Dominic BuñoNoch keine Bewertungen

- Chapter 6 Plate GirderDokument23 SeitenChapter 6 Plate GirderolomuNoch keine Bewertungen

- 2530 Switch PresentationDokument33 Seiten2530 Switch PresentationNgoc The NguyenNoch keine Bewertungen

- 3com Switch 4200G Family: Configuration GuideDokument902 Seiten3com Switch 4200G Family: Configuration GuideAndré Luis Boni DéoNoch keine Bewertungen

- Citrix Virtual Desktop Handbook (7x)Dokument220 SeitenCitrix Virtual Desktop Handbook (7x)sunildwivedi10Noch keine Bewertungen

- Shop Data - Fitting Layout For HVACDokument2 SeitenShop Data - Fitting Layout For HVACDaniel AustinNoch keine Bewertungen

- 2017 Laureates Rafael Aranda, Carme Pigem and Ramon Vilalta Spain Media KitDokument26 Seiten2017 Laureates Rafael Aranda, Carme Pigem and Ramon Vilalta Spain Media KitManu ChackoNoch keine Bewertungen

- Nucor Grating Catalogue 2015Dokument64 SeitenNucor Grating Catalogue 2015Dan Dela PeñaNoch keine Bewertungen

- Sem 3okDokument31 SeitenSem 3okVishakha PatelNoch keine Bewertungen

- Nbr20012002engarp07 PDFDokument34 SeitenNbr20012002engarp07 PDFpatikkalNoch keine Bewertungen

- BoQ GRP Pipe Contructor 20180918Dokument8 SeitenBoQ GRP Pipe Contructor 20180918Mohammad SyeduzzamanNoch keine Bewertungen

- Index To SpecificationDokument29 SeitenIndex To Specificationsat palNoch keine Bewertungen

- Raft (Mat) Foundation: - A) Flat Plate - B) Flat Plate Thickened Under ColumnsDokument18 SeitenRaft (Mat) Foundation: - A) Flat Plate - B) Flat Plate Thickened Under ColumnsProf. N. El-SakhawyNoch keine Bewertungen

- General Structural/Construction Notes and Specifications: Proposed 4-Storey Residential Building W/FenceDokument1 SeiteGeneral Structural/Construction Notes and Specifications: Proposed 4-Storey Residential Building W/FenceWilbert ReuyanNoch keine Bewertungen

- Computer Important Abbreviations Quiz Online Mcq'sDokument4 SeitenComputer Important Abbreviations Quiz Online Mcq'sshahid khambroNoch keine Bewertungen

- 10a B C Year End DescriptionDokument5 Seiten10a B C Year End DescriptionMegaEyedBitsNoch keine Bewertungen

- Windows Splunk Logging Cheat Sheet - Win 7 - Win2012: DefinitionsDokument8 SeitenWindows Splunk Logging Cheat Sheet - Win 7 - Win2012: DefinitionsDeepakNoch keine Bewertungen

- CCNASv1 1 Chp08 Lab B RMT Acc VPN Instructor PDFDokument33 SeitenCCNASv1 1 Chp08 Lab B RMT Acc VPN Instructor PDFAhmadHijaziNoch keine Bewertungen

- UMTS Consistency Check RulesDokument24 SeitenUMTS Consistency Check RulesZeeNoch keine Bewertungen

- 311Dokument73 Seiten311mira01Noch keine Bewertungen

- Configure Nokia E71WiFi SIP Client With The 3300Dokument14 SeitenConfigure Nokia E71WiFi SIP Client With The 3300Angelo IonNoch keine Bewertungen

- MS C A Roofed Skeleton BOQDokument2 SeitenMS C A Roofed Skeleton BOQBrighton MUZAHURANoch keine Bewertungen

- Brocade Qualification Letter Fos 6.4.0c PDFDokument4 SeitenBrocade Qualification Letter Fos 6.4.0c PDFAshwin VijayNoch keine Bewertungen

- Euthymius and His Monastery in The Judean DesertDokument33 SeitenEuthymius and His Monastery in The Judean DesertnurodaNoch keine Bewertungen

- Building Works PDFDokument359 SeitenBuilding Works PDFManish Kumar YadavNoch keine Bewertungen

- SoftwareEngineering RESUME Bhushan WalkeDokument2 SeitenSoftwareEngineering RESUME Bhushan WalkebhushanNoch keine Bewertungen

- PPE II - Lesson PlanDokument5 SeitenPPE II - Lesson PlanAish RaviNoch keine Bewertungen