Beruflich Dokumente

Kultur Dokumente

TD 05 Corrigeee

Hochgeladen von

Nadhir MehellouOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

TD 05 Corrigeee

Hochgeladen von

Nadhir MehellouCopyright:

Verfügbare Formate

David Bouchet – Architecture des ordinateurs – Info-Spé 2011/2012

T.D. 5 – Corrigé

Constitution de plans mémoire

Exercice 1

Soit les deux mémoires de type ROM suivantes :

1. Combien peut-on former de mots de 4 bits avec la ROM1 ?

Il s’agit ici de déterminer la profondeur de la ROM1.

256 kbit = 256/4 kmot de 4 bits = 64 kmot de 4 bits.

On peut former 64 kmot de 4 bits avec la ROM1.

2. Combien peut-on former de mots de 8 bits avec la ROM2 ?

Il s’agit ici de déterminer la profondeur de la ROM2.

512 kbit = 512/8 kmot de 8 bits = 64 kmot de 8 bits.

On peut former 64 kmot de 8 bits (64 ko) avec la ROM2.

3. Quelle est la taille du bus d’adresse des deux types de ROM ?

La taille du bus d’adresse d’une mémoire se détermine à partir de sa profondeur.

64 kmot = 216 mots.

La taille du bus d’adresse des deux types de ROM est de 16 bits.

On désire réaliser une ROM2 à l’aide de deux ROM1.

4. Quel type d’assemblage doit-on réaliser ?

On passe d’un bus de donnée de 4 bits à un bus de donnée de 8 bits.

L’assemblage à réaliser est donc un assemblage en parallèle (ou en largeur).

T.D. 5 – Corrigé 1/6

David Bouchet – Architecture des ordinateurs – Info-Spé 2011/2012

5. Donnez le schéma de câblage.

Exercice 2

On dispose de plusieurs RAM1 ayant une capacité de 2048 kbit avec un bus de donnée de 4 bits, une en-

trée CS et une entrée WE. On désire réaliser une RAM2 ayant une capacité de 4 Mbit. Les bus de com-

mande et de donnée des deux RAM sont identiques.

1. Calculez la taille des bus d’adresse des deux types de RAM.

La taille du bus d’adresse d’une mémoire se détermine à partir de sa profondeur.

RAM1 : 2048 kbit = 2048/4 kmot de 4 bits = 512 kmot de 4 bits.

512 kmot = 219 mots.

La RAM1 possède 19 fils d’adresse.

RAM2 : 4 Mbit = 4/4 Mmot de 4 bits = 1 Mmot de 4 bits.

1 Mmot = 220 mots.

La RAM2 possède 20 fils d’adresse.

2. Quel type d’assemblage doit-on réaliser ?

On passe d’un bus d’adresse de 19 bits à un bus d’adresse de 20 bits.

L’assemblage à réaliser est donc un assemblage en série (ou en profondeur).

3. Combien de bits d’adresse vont servir à déterminer le CS des RAM1 ?

Ce sont les fils d’adresse supplémentaires de la RAM 2 qui vont servir à la sélection des RAM1. Ici, la

RAM2 possède un fil d’adresse de plus que la RAM1 (20 - 19 = 1).

Un seul fil d’adresse servira donc à déterminer le CS des RAM1.

T.D. 5 – Corrigé 2/6

David Bouchet – Architecture des ordinateurs – Info-Spé 2011/2012

4. Donnez le schéma de câblage.

Les entrées WE des RAM1 sont reliées directement à l'entrée WE de la RAM2. Il n’y a aucune diffi-

culté particulière pour ce type d’entrée.

Pour la sélection des RAM1, il est préférable d’utiliser un démultiplexeur piloté par le fil

d’adresse A19.

• Si A19 = 0, le CS de la RAM2 est recopié sur le CS de la première RAM1 (celle du haut sur le sché-

ma). L’autre sortie du démultiplexeur est positionnée à 0 et la seconde RAM 1 (celle du bas sur le

schéma) est désactivée.

• Si A19 = 1, le CS de la RAM2 est recopié sur le CS de la seconde RAM1. L’autre sortie du démulti-

plexeur est positionnée à 0 et la première RAM1 est désactivée.

On remarque que si CS = 0, alors les deux RAM1 sont désactivées.

5. Quelle mémoire est active lors de la lecture à l’adresse 51510 ?

C’est le fil d’adresse A19 qui pilote le démultiplexeur et qui permet la sélection de la première ou de la

seconde RAM1.

51510 = 0020316 → A19 = 0

C’est la RAM1 numéro 1 qui est activée.

6. Quelle mémoire est active lors de l’écriture à l’adresse 9A84416 ?

Il faut également déterminer la valeur du bit A19 :

9A84416 → A19 = 1

C’est la RAM1 numéro 2 qui est activée.

T.D. 5 – Corrigé 3/6

David Bouchet – Architecture des ordinateurs – Info-Spé 2011/2012

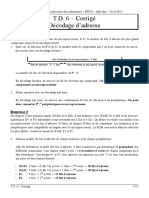

Exercice 3

Que semble faire le montage ci-dessous ?

Trouvez les erreurs et proposez un montage qui fonctionne.

Indications :

• Le nombre de ROM1 est exact.

• La capacité en bit des ROM1 est exacte.

• La taille du bus de donnée des ROM1 est exacte.

• L’assemblage en parallèle est représenté à l’horizontale.

• L’assemblage en série est représenté à la verticale.

À partir des indications, il est possible de déterminer le nombre de fils d’adresse des deux types de ROM :

ROM1 : 1 kbit = 1/4 kmot de 4 bits = 256 mots de 4 bits = 28 mots de 4 bits.

La ROM1 possède donc 8 fils d’adresse (A7:0).

ROM2 : L’assemblage en série nous indique qu’elle possède un fil d’adresse de plus que la ROM1.

La ROM2 possède donc 9 fils d’adresse (A8:0).

L’assemblage en parallèle nous indique que le bus de donnée de la ROM 2 est deux fois plus large que ce-

lui de la ROM1 : elle possède donc un bus de donnée de 8 bits (D7:0).

Une ROM ne possède jamais d’entrée WE (Write Enable), car elle n’est accessible qu’en lecture.

Il faut utiliser un démultiplexeur pour la gestion des entrées CS.

T.D. 5 – Corrigé 4/6

David Bouchet – Architecture des ordinateurs – Info-Spé 2011/2012

On obtient le schéma de câblage suivant :

Exercice 4

On désire réaliser une RAM2 de 8 ko avec un bus de donnée de 16 bits, à l’aide de plusieurs RAM 1 de 512

octets ayant un bus de donnée de 4 bits.

1. Donnez le nombre de mots et la largeur du bus d’adresse des deux types de RAM.

RAM1 : 512 octets = (512 × 8) / 4 mots de 4 bits = 1 kmot de 4 bits.

1 kmot = 210 mots.

La RAM1 possède 10 fils d’adresse.

RAM2 : 8 ko = (8 × 8) / 16 kmot de 16 bits = 4 kmot de 16 bits.

4 kmot = 212 mots.

La RAM2 possède 12 fils d’adresse.

2. Combien de mémoires doit-on assembler en série ?

On passe d’une profondeur de 1 kmot à une profondeur de 4 kmot.

Il faut assembler 4 mémoires en série (4 kmot / 1 kmot = 4).

3. Combien de mémoires doit-on assembler en parallèle ?

On passe d’un bus de donnée de 4 bits à un bus de donnée de 16 bits.

Il faut assembler 4 mémoires en parallèle (16 bits / 4 bits = 4).

T.D. 5 – Corrigé 5/6

David Bouchet – Architecture des ordinateurs – Info-Spé 2011/2012

4. Combien de bits d’adresse vont servir à déterminer le CS des RAM ?

Ce sont les deux bits d’adresse supplémentaires de la RAM2 (par rapport à la RAM1), qui vont servir

à déterminer le CS des RAM.

5. Donnez le schéma de câblage.

6. Précisez les mémoires actives pour chacune des adresses suivantes : 95A16, E0316, 1FF16, 72516.

Pour chaque adresse, il suffit de déterminer la valeur des bits A11 et A10.

• 95A16 : A11 = 1, A10 = 0 : RAM1 numéro 9, 10, 11, 12 activées.

• E0316 : A11 = 1, A10 = 1 : RAM1 numéro 13, 14, 15, 16 activées

• 1FF16 : A11 = 0, A10 = 0 : RAM1 numéro 1, 2, 3, 4 activées.

• 72516 : A11 = 0, A10 = 1 : RAM1 numéro 5, 6, 7, 8 activées.

T.D. 5 – Corrigé 6/6

Das könnte Ihnen auch gefallen

- TD2 Corrigée PDokument5 SeitenTD2 Corrigée Pfarid regraguiNoch keine Bewertungen

- Etude Et Mise en Place D'un HotSpot Wi-FiDokument135 SeitenEtude Et Mise en Place D'un HotSpot Wi-FiÀméno Algéwàlôù97% (33)

- Solution Examen LAT315 2017Dokument3 SeitenSolution Examen LAT315 2017Babi Ben80% (5)

- Station de Pompage TARGUISTEDokument11 SeitenStation de Pompage TARGUISTEkhadija eddahbyNoch keine Bewertungen

- TD 03 CorrigeDokument14 SeitenTD 03 CorrigerabehNoch keine Bewertungen

- TDs Machines Hydrauliques Et Pneumatiques PDFDokument43 SeitenTDs Machines Hydrauliques Et Pneumatiques PDFAmirouche78% (9)

- TDs Machines Hydrauliques Et Pneumatiques PDFDokument43 SeitenTDs Machines Hydrauliques Et Pneumatiques PDFAmirouche78% (9)

- TD - N°2 - EN - Systèmes À MicroprocesseurDokument7 SeitenTD - N°2 - EN - Systèmes À MicroprocesseurTimble Puteur100% (2)

- Chapitre3 Programmation en Assembleur 8086 PDFDokument100 SeitenChapitre3 Programmation en Assembleur 8086 PDFReda Tadjeddine100% (6)

- TD 2Dokument7 SeitenTD 2paroles dela6T100% (3)

- Correction TD N°3 CN RegistresDokument4 SeitenCorrection TD N°3 CN RegistresKhalil Frikha100% (1)

- QCM Sur Le MicroprocesseurDokument11 SeitenQCM Sur Le MicroprocesseurGhislaine REMONDO100% (1)

- Série AssembleurDokument3 SeitenSérie AssembleurSoufiane Aggour100% (1)

- Correction TD N°3 CN RegistresDokument4 SeitenCorrection TD N°3 CN RegistresKhalil Frikha100% (4)

- Methode HimoDokument69 SeitenMethode HimoDrancy100% (1)

- TD3 Mémoire CorrDokument37 SeitenTD3 Mémoire CorrNadia Ben NjimaNoch keine Bewertungen

- TD2 CorrigeDokument3 SeitenTD2 CorrigeMouna Ben Mohamed100% (1)

- Nizar ProgrammeDokument29 SeitenNizar Programmeiramole med100% (1)

- Adressage MemoireDokument10 SeitenAdressage MemoireLibre HamataNoch keine Bewertungen

- TD Les MémoireDokument4 SeitenTD Les Mémoirefers100% (5)

- Correction TDn°1Dokument6 SeitenCorrection TDn°1Zidi NesimNoch keine Bewertungen

- Devoir Dmoicile CorrectionDokument8 SeitenDevoir Dmoicile CorrectionSimo Light100% (1)

- Microprocesseur-8086 Exercices ResolusDokument8 SeitenMicroprocesseur-8086 Exercices Resolusyounes ghenam100% (4)

- Test QCMDokument5 SeitenTest QCMFabrice Bernard100% (1)

- 2 PerceptionDokument7 Seiten2 PerceptionMeriem M'ghari100% (1)

- TP3 Programmation Assembleur Avec EMU8086 2019Dokument4 SeitenTP3 Programmation Assembleur Avec EMU8086 2019Marouane Taibini100% (3)

- Corrige TD 1 PDFDokument3 SeitenCorrige TD 1 PDFanas67% (3)

- Exercices Sur Les CompteursDokument11 SeitenExercices Sur Les CompteursThe geek Cuesta100% (1)

- TD2 CorrigeDokument3 SeitenTD2 CorrigeAbderrahmane SmaaliNoch keine Bewertungen

- TD 1 LiaisonsschmacinmatiqueDokument6 SeitenTD 1 LiaisonsschmacinmatiqueSamba SallNoch keine Bewertungen

- TD 1 MicrocontroleurDokument5 SeitenTD 1 MicrocontroleursiloneNoch keine Bewertungen

- TP1 - Initiation Emu8086 PDFDokument2 SeitenTP1 - Initiation Emu8086 PDFAtashi Tsunagu (“Albedo”)67% (6)

- TD1 - Circuit ProgrammablebisDokument4 SeitenTD1 - Circuit ProgrammablebisMouhcine Zianee100% (2)

- TD1 Mémoires 2021Dokument3 SeitenTD1 Mémoires 2021Younesse El100% (1)

- TD CH 3 Architecture Des Ordinateurs 2Dokument1 SeiteTD CH 3 Architecture Des Ordinateurs 2Pape Moussa DiopNoch keine Bewertungen

- TD4Dokument1 SeiteTD4Mounira Tarhouni100% (1)

- TD 05 CorrigeDokument6 SeitenTD 05 CorrigeAnonymous Wpl47Bwu4Noch keine Bewertungen

- TD 06 CorrigeDokument12 SeitenTD 06 CorrigeOmar KhayyamNoch keine Bewertungen

- Corrigé TD 154Dokument3 SeitenCorrigé TD 154MBADJOUN Daniel100% (1)

- Décodage Adresse1 ProfDokument7 SeitenDécodage Adresse1 ProfBlaugranaNoch keine Bewertungen

- TD - N°2 - EN - Systèmes À Microprocesseur PDFDokument7 SeitenTD - N°2 - EN - Systèmes À Microprocesseur PDFTimble Puteur100% (1)

- CorrigéExamen 2020-2021Dokument3 SeitenCorrigéExamen 2020-2021Moujahed GassoumiNoch keine Bewertungen

- Exercices Assembleur M1 ELT ER Serie 2 Avec CorrigéDokument5 SeitenExercices Assembleur M1 ELT ER Serie 2 Avec CorrigéAmir Na DzNoch keine Bewertungen

- TD°2: Mémoiré: Exercice 1Dokument2 SeitenTD°2: Mémoiré: Exercice 1Mouna Ben Mohamed100% (5)

- Corrigé Du TD1Dokument3 SeitenCorrigé Du TD1youssef BohaNoch keine Bewertungen

- TD 1 Les Mémoires: 1. Partie ThéoriqueDokument2 SeitenTD 1 Les Mémoires: 1. Partie ThéoriqueAla DorbozNoch keine Bewertungen

- Corrigé Devoir N°1Dokument3 SeitenCorrigé Devoir N°1Colmain Nassiri100% (1)

- Exercices Corrigés Assembleur8086Dokument2 SeitenExercices Corrigés Assembleur8086Anonyme100% (3)

- Exam 2017Dokument2 SeitenExam 2017Mohamed Hmamouch100% (2)

- Exercices de RivisionDokument10 SeitenExercices de RivisionOnsNoch keine Bewertungen

- Archi TD 3 - CorrectionDokument7 SeitenArchi TD 3 - CorrectionLwd Ameny100% (1)

- TD N 2Dokument4 SeitenTD N 2Cesar Malki100% (1)

- Corrigé Série de TD N° 3Dokument5 SeitenCorrigé Série de TD N° 3Alaa MessaoudNoch keine Bewertungen

- 1-Modes D'adressage: S ° J ' P I 8086Dokument4 Seiten1-Modes D'adressage: S ° J ' P I 8086Sara Benseba67% (3)

- Travaux Dirigés-Microprocesseur MicrocontroleurDokument18 SeitenTravaux Dirigés-Microprocesseur MicrocontroleurFatima BettayebNoch keine Bewertungen

- Série 3Dokument8 SeitenSérie 3Blidi AymenNoch keine Bewertungen

- Série 5Dokument3 SeitenSérie 5Blidi AymenNoch keine Bewertungen

- TP 4 AssembleurDokument1 SeiteTP 4 AssembleurMohamed El Mourabit100% (1)

- Familiarisation Avec Le Simulateur "8085 Simulator"Dokument15 SeitenFamiliarisation Avec Le Simulateur "8085 Simulator"Med Djameleddine BougrineNoch keine Bewertungen

- TD2 MemoireDokument2 SeitenTD2 MemoireMouna Ben MohamedNoch keine Bewertungen

- C - Memoire Corrigés - CopieDokument5 SeitenC - Memoire Corrigés - CopieBrady C'est DieuNoch keine Bewertungen

- Ch6 Pal FplaDokument6 SeitenCh6 Pal Fplanoubis100% (2)

- TD 2 Mémoires-1Dokument3 SeitenTD 2 Mémoires-1القرآن الكريمNoch keine Bewertungen

- Devoir 1 Décodage DDokument4 SeitenDevoir 1 Décodage DAssia Bouhssini0% (1)

- TD1 Me ÜmoiresDokument3 SeitenTD1 Me ÜmoiresalaeelhassanyNoch keine Bewertungen

- TD5LAT54Dokument1 SeiteTD5LAT54Smati DjamelNoch keine Bewertungen

- TD1 Mémoires 2022Dokument3 SeitenTD1 Mémoires 2022Soufiane AbdelouahabNoch keine Bewertungen

- Examen Corrig Techniques de Commande Avance, Msila 2019Dokument1 SeiteExamen Corrig Techniques de Commande Avance, Msila 2019Nadhir MehellouNoch keine Bewertungen

- FORMULES HydrauliqueDokument1 SeiteFORMULES Hydrauliquefakhri100% (1)

- TP1 PDFDokument1 SeiteTP1 PDFNadhir MehellouNoch keine Bewertungen

- Module CFAO Université MascaraDokument4 SeitenModule CFAO Université MascaraNadhir Mehellou100% (2)

- For MulesDokument22 SeitenFor MulesNadhir MehellouNoch keine Bewertungen

- TD BouchafaaDokument22 SeitenTD BouchafaaNadhir Mehellou100% (2)

- AnnexesDokument9 SeitenAnnexesKoukou AmkoukouNoch keine Bewertungen

- TD 2 Liaisons Schéma CinématiqueDokument6 SeitenTD 2 Liaisons Schéma CinématiqueNadhir MehellouNoch keine Bewertungen

- VW - Catalogue AmarokDokument12 SeitenVW - Catalogue AmarokSerge Gostoli-GeorgesNoch keine Bewertungen

- TD Traitement NumeriqueDokument3 SeitenTD Traitement NumeriqueMahamat Adam Abakar GouriNoch keine Bewertungen

- Les Dimensions Symboliques de La CentralitéDokument20 SeitenLes Dimensions Symboliques de La Centraliténsm2325Noch keine Bewertungen

- Bpde Ao 57Dokument54 SeitenBpde Ao 57KarimAmariNoch keine Bewertungen

- Teste 1 Les Loisirs 8 AnoDokument5 SeitenTeste 1 Les Loisirs 8 AnoMarta Silveiro SousaNoch keine Bewertungen

- Tsae 2 BTS MSPDokument79 SeitenTsae 2 BTS MSPAbi ClémentNoch keine Bewertungen

- Dépliant Du Colloque RSEDokument2 SeitenDépliant Du Colloque RSEJad KadiriNoch keine Bewertungen

- Architecture CAMELDokument11 SeitenArchitecture CAMELfort604Noch keine Bewertungen

- CoursCompta02 03Dokument24 SeitenCoursCompta02 03Mly Al AminiNoch keine Bewertungen

- Cours de SpssDokument5 SeitenCours de SpssHamza SellamiNoch keine Bewertungen

- 101010Dokument24 Seiten101010lamour frantzNoch keine Bewertungen

- Memo Train ClassiqueDokument6 SeitenMemo Train Classiquerichard borgNoch keine Bewertungen

- Lettre de Demande de Facture Detaillee Orange 234Dokument4 SeitenLettre de Demande de Facture Detaillee Orange 234Ouail DaaliNoch keine Bewertungen

- Magazine Cio Mag 70 FinalDokument39 SeitenMagazine Cio Mag 70 FinalAguessy HermannNoch keine Bewertungen

- DP Ventilation Cle557d66-3Dokument155 SeitenDP Ventilation Cle557d66-3Abdelkrim RamdaneNoch keine Bewertungen

- Mi V 24 B1Dokument7 SeitenMi V 24 B1Dvid7887Noch keine Bewertungen

- Antidote Mode D'emploiDokument25 SeitenAntidote Mode D'emploiMre LbnsNoch keine Bewertungen

- Fours Boulangerie MAP 2020Dokument12 SeitenFours Boulangerie MAP 2020gatekaNoch keine Bewertungen

- Présentation Finale Contraintes Dans Le Sol MDS2Dokument20 SeitenPrésentation Finale Contraintes Dans Le Sol MDS2Ali EmbarecNoch keine Bewertungen

- PM60G16 FRDokument86 SeitenPM60G16 FRAtlas SENoch keine Bewertungen

- DELF A1 Web CorrigesDokument3 SeitenDELF A1 Web CorrigesMirunalini GobinathNoch keine Bewertungen

- Ch1-Couleurs (Physique Spé Première)Dokument11 SeitenCh1-Couleurs (Physique Spé Première)BesmaNoch keine Bewertungen

- D3C ELN BERROUANE MeriemWassilaDokument182 SeitenD3C ELN BERROUANE MeriemWassilasowNoch keine Bewertungen

- InsurTech AGBODAZE CynthiaDokument8 SeitenInsurTech AGBODAZE CynthiaEyram AGBODAZENoch keine Bewertungen

- Détection IncendieDokument6 SeitenDétection IncendieChawki ZerroukiNoch keine Bewertungen