Beruflich Dokumente

Kultur Dokumente

Hitad039 275

Hochgeladen von

Hla Swe Oo0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

20 Ansichten20 SeitenHitachi EX series Excavator

Originaltitel

HITAD039-275

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenHitachi EX series Excavator

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

20 Ansichten20 SeitenHitad039 275

Hochgeladen von

Hla Swe OoHitachi EX series Excavator

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 20

Section 16. Electrical Specifications

16.1 Absolute Maximum Ratings

Table 16-1 lists the absolute maximum ratings.

Table 16-1. Absolute Maximum Ratings (Preliminary)

Item Symbol___Rating Unit

Supply voltage Vee =0.310 47.0 Vv

Programming voltage Ver: 0.310 4135 vee

Input voltage Ports 1-6, 8,9 Vin Ostovec+O3

Pont? Vin -0.3 0 AVEC +03 Vv

Analog supply voltage AVec—-0.31047.0__ Vv

‘Analog input voltage ~ Van (0.3 19 AVcC +03 Vv

Operating temperature Tope Regular specifications: -2010+75 °C

Wide-range specifications: — 4010 485°C

Storage temperature Ta =55 10 +125 cc

Note: Exceeding the absolute maximum ratings shown in table 16-1 can permanently destroy

the chip.

16.2 Electrical Characteristics

16.2.1 DC Characteristics

Table 16-2 lists the DC characteristics of the SV version. Table 16-3 lists the DC characteristics of

the 3V version. Table 16-4 gives the allowable current output values of the SV version.

Table 16-5 gives the allowable current output values of the 3V version.

HITACHI

HHeacr Amerca Lid + Htachi Plaza +2000 Sera Port Phay « Grabane, CA 94005-1818 +415) 589-6300, 25

276

Table 16-2. DC Characteristics (SV Version) (Preliminary)

Conditions: Voc = 5.0V #10%, AVcc = 5.0V +10%*, Vss = AVss = OV,

Ta = -20 75°C (regular specifications), Ta = —40 to 85°C (wide-range specifications)

Measurement

Item Symbol Min __Typ Max____Unit conditions

Schmit trigger P67 ~ P62, P6o, VT 7 Vv

input voltage P86— P80, vr = = Vecx0.7_V

a P97, P94~P90_VT+-Vr_0.4 = - v

Input High voltage RES, STBY, NMI Vin Vec-07- vec+03 V

Q) MDi, MDo

EXTAL,

_ ____P77-P70 2.0 = AVec +0.3V

Input High voltage Input pins vin 2.0 = Vec+03 V

other than (1)

_ and (2) _

Input Low voltage vin - 05 v

GB) a oe _

Input Low voltage Input pins Vit ~03 - 08 v

other than (1)

and (3) above

Output High All output pins VoH Tou =-2004A.

voltage Tou =-1.0mA

Output Low All output pins Vow To. = 1.6mA

voltage Ports | and 2 Tou = 10.0mA

Input leakage RES Mink Vin = 0.5V to

current STBY, NMI, Vcc -0.5V

MDi, MDo

P77- P70 - - 10 HA Vin=0.5V to

AVcc-0.5V

Leakage current Ports 1, 2,3 (rst a a 10 HA Vin =0.5V to

in 3-state (off state) 4, 5, 6, 8.9 __Vee-0.5V

Input pull-up Ports1,2,3 -Ip 30 - 250 A Vin=0V

MOS current

Note: * Connect AVCc to the power supply (+5¥) even when the A/D and D/A converters are

not used.

HITACHI

Hac Aeveres 36 + Htaoh Plaza +2000 Sara Pont Pha» Brsbane, CA G4006-1819 (418) 589.8300,

Table 16-2. DC Characteristics (SV Version) (cont.)

Conditions: Voc = AVcc = 5.0V 410%, Vss = AVSS = OV, Ta = -20 10 75°C (regular specifications)

Ta =~40 to 85°C (wide-range specifications)

Measurement

Tem Symbol__Min_ Typ Max

Input capacitance RES (VPP) Cin - 60,

NMI = - 30

All input pins a 15

except RES.

and NMI

Current Normal Tec 1225 mA if

dissipation” operation = 16 mA f

20 mA f

Sleep mode - 8 mA f

= 10 mA f

12 mA_f

Standby modes = 001 nA

Analog supply During A/Dor Alec, - 2.0, mA

current DIA conversion

Waiting = 001 50 A

RAM standby Vram 2.0 = v

voltage

Notes: *1 Current dissipation values assume that Vitt min = Vcc ~- 0.5, ViL max = 0.5Y, all output

pins are in the no-load state, and all input pull-up transistors are off

*2 For these values it is assumed that VRAM $ Vcc < 4,.5V and VIH min = Vcc x 0.9,

HITACHI

"rach Amerca. id.» Hnach Plaza + 2000 Sera Pont Phy + Bnsane, CA 94005-1819. (45) 59.8900 Por

278

Table 16-3. DC Characteri

ics (3V Version) (preliminary)

Conditions: Vec = 3.0V #10%, AVcc = 5.0V £10%"!, Vss = AVSS = OV, Ta = -20 to 70°C

Measurement

Item Symbol__ Min Typ Max Unit_conditions

Schmitt P67— P62, Péo, VT Veex0.15_= = Vv

trigger input P8s~ P80, Vr vee x07 V_

voltage’? P97, P94~ P90 VIF-Vr- 0.2 = = v

a)

Input High RES,STBY Via vee x09 = vec+03 V

voltage? MDi, MDo

Q) EXTAL, NMI

P77- P70 Vecx07 — Avec +03 V

“Input pins veexO.7 = vec +03 V

other than (1)

and (2) above

InputLow RES,STBY | ViL 03 = “Veex0l V

voltage"?

@) Input pins 03 = Vee x 0.15 V

other than (1)

and (3) above

Output High All output pins Vor V__ low =-200nA

voltage V__Ton=-1.0mA

Output Low All output pins VoL VoL =0.8mA

voltage Ports 1 and 2 = 2 04. V. Iov=LémA

Input RES inl = = 10.0 HA Vin=0.5t0

leakage STBY, NMI, > - 10 HA Vec-0,5V

current

S = 10 HA Vin= 0510

AVcc - 0.5V

Leakage Ports 1, 2,3 rst - 10 HA Vin =0.5to

current in 4,5, 6,8,9 Vee

3-state

(off state)

Input Pors 12,3 —Ip 3 = 120. BA Vin

pull-up MOS

current

Notes: *1 Connect AVCC to the power supply (+3V) even when the A/D converter

°2 In the range 3.3V < Voc < 4.5V, for the input levels of Vik and VT*, apply the higher of

the values given for the SV and 3V versions. For Vit and V1-, apply the lower of the

values given for the 5V and 3V versions.

HITACHI

each Amevea, Lid *Hsaen Plaza +2000 Seva Pont Pray.» Brebane, CA 9005-1819 +435) 589-8300

not used.

Table 16-3. DC Characteristi

Conditions: Vec = 3.0V +10%, AVcc = 5.0V £10%"!, Vss

's (3V Version) (preliminary) (cont.)

AVS = OV, Ta = -20 to 70°C

Measurement

Item Symbol__Min Typ Max __Unit _ conditions

Input Cn =e 60pF__Vn=0V

capacitance NMI =~ 30. pF. Of= IMHz

‘All input pins = = 15 ep ee al= 5c:

except RES

and NMI

Curent Normal ke 6 - mA f=3MHz

dissipation"! operation 10 mA HZ

Sleepmode = 4 ei mA f=3MHz

= 6 12 mA f=SMHz

Standby modes*? - 001 50 BA

‘Analog During A/Dor Alec - 20 «5.0 mA —

supply D/A conversion

current Waiting = (Ocoee (Oe 1 emer

RAM backup voltage VRAM 20 - = Vv

(in standby modes)

Notes: *1 Current dissipation values assume that VI min = Vec — O.5V, ViL max = 0.5V, all output

pins are in the no-load state, and all input pull-up transistors are off,

*2 For these values it is assumed that VRam < Vcc < 2.7V and Vili min = Voc x 0.9,

Vit max = 0.3V.

HITACHI

tach Amenca, La + Heen Plaza 2000 Sara Pont Py. Bnsoane, CA 94005-1819 (475) 589.8300

279

Table 16-4, Allowable Output Current Sink Values (SV Version) (Preliminary)

Conditions: Vcc = AVcc = 5.0V #10%, Vss = AVss = OV, Ta = ~20 to 75°C (regular specifications)

Ta = 40 to 85°C (wide-range specifications)

Item Symbol Min Typ Max__ Unit

Allowable output Low Ports 1 and 2 Jou 10m

current sink (per pin) Other output pins = 20 mA

Allowable output Low Ports 1 and2,total_ Elou = = 80, mA

current sink (total) Total of all output - 120 mA

Allowable output High All output pins =Ion - - 20 mA

current sink (per pin)

Allowable output High Total of all ouput E-low

current sink (total)

40 mA

Table 16-

. Allowable Output Current Sink Values (3V Version) (Preliminary)

Conditions: Vee = 3.0V #10%, AVcc = 5.0V 410%, Vss = AVss = OV, Ta = -20 10 75°C

Ttem Symbol Min Typ Max___Unit

Allowable output Low Ports 1 and 2 Tot 2 mA

current sink (per pin) __ Other output pins = = 1 mA

Allowable outpucLow Ports Land 2, total EIou = 40 mA

current sink (total) Total of all output = = 60 mA

Allowable output High All output pins lon 5 = a mA

current sink (per pin)

Allowable output High Total of all ouput E-1on 30 mA

current sink (total)

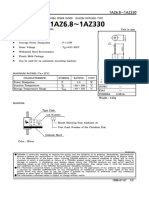

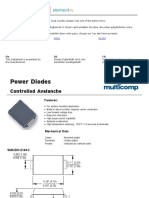

Note: To avoid degrading the reliability of the chip, be careful not to exceed the output current sink

values in tables 16-4 and 16-5. In particular, when driving a Darlington transistor pair or

LED directly, be sure to insert a current-limiting resistor in the output path. See figures 16-1

and 16-2

HITACHE

Ba iach: Amenea, Lid + Hf Pasa 2000 Sea Pont Phy.» Brisbane. CA 94005-1819 + (£15) 58.8900

Haase

Pon

Dartington

pair

Figure 16-1. Example of Circuit for Driving a Darlington Pair ($V Version)

e238

Voe

000

mm

Port t or2

LED

Figure 16-2, Example of Circuit for Driving an LED (3V Version)

16.2.2 AC Characteri

The AC characteristics are listed in three tables. Bus timing parameters are given in

table 16-6, control signal timing parameters in table 16-7, and timing parameters of the on-chip

supporting modules in table 16-8.

HITACHI

Heacn: meres, Ls. + Hesch Plaza +2000 Siera Poet Peay» Grabane. CA 94005-1819 = 415) 589-5200,

281

Table 16-6. Bus Timing (Preliminary)

Condition A: Vcc = 5.0V #10%, Vss = OV, @ = 0.5MHz to maximum operating frequency,

Ta = -20 t0 75°C (regular specifications),

Ta =—40 to 85°C (wide-range specifications)

Condition B: Voc = 3.0V +10%, Vss = OV, @ = 0.SMHz to maximum operating frequency,

Ta=-20 075°C

Condition B Condition

‘MHz 6MHz_——8MHz_—_‘10MHz Measurement

Item Symbol_Min_ Max Min Max Min Max Min_Max Unit

Clock cycle ume oe 200 2000 166.7 2000 125 2000 100 2000 ns Fig. 16-8

‘Clock pulse widih Low a - 6 - 4 - 3 - os Fig 1d

Clock pulse width High ice Pig TS

{Clock rise time je SOS OSS sig 1

Clock fall ume w SOS SS as Fig 1

‘Address delay time uo 90 70 O— 50s ‘Fig. 168

‘Address hotd time wi — 3 SOO ns Fig. 164

‘Address strobe delay ime tsp 0 30 ns Fig. 164

Write stobe delay time wo 80 = 50s Fig. 164

Suwobe delay ime wo = 50s Fig. 164

Wiite suobe pulse width wwsw 200-200 120 — as Fig. 168

‘Adiress setup time 1 ws 15m Fig. 164

“Address setup ime 2 us (105 - ~+103:~-~=«0S”~S*C*SSCSSCs Cig 1

‘Read data setup time wos 7-90 35 ms Fig. 164

Read data hold time fox ie OE eae ORE EEO. 0 =

Read data access ume* a e210 eae 70a

‘Write data delay time vnc Seer ee 12s NS NETS Bas

Write data setup time wos 10 - 20 - WO - SS as

‘Write data hold me wor 30 OSC

Wait setup ime ws OO - @ - 2 - 4% - os

‘Wait hold time om 2-1 - +10 - +10 as

‘Note: * Values at maximum operating frequency

HITACHI

282 tach Amence, Lio + Heh Pars +2000 Serva Point Phy. Brisbane. CA 8005-1819 + (815) 559-6900

Table 16-7. Control Signal Timing (Preliminary)

Condition A: Vec = 5.0V £10%, Vss = OV, @ = 0.5MHz to maximum operating frequency,

Ta = -20 to 75°C (regular specifications),

Ta = —40 to 85°C (wide-range specifications)

Condition B: Vcc = 3.0V #10%, Vss = OV, © = 0.5MHz to maximum operating frequency,

Ta = -2010 75°C

Condition B Condition a

SMH: 6MHz_8MHz__‘10MHz ‘Measurement

Item Symbol_Min_Max Min Max Min Max Max_Unit_ conditions

RES setup time mess 300-200 - 20 - = ms Fig. 16-6

RES pulse width wssw 10 0-10 tye Fig. 166

NM scupume ws 300 10-0 = ons Fig. le7

(NMI, IRQ 10 RE)

NMT hold time wm 10 LO 0 - 1 - ns Fig 167

(IRQ w RE)

Tnterrupt pulse width ww 300-200 SOs ig GT

for recovery from soft-

ware standby mode

Crysial oscillator setding osc, = 2-20 Sms Fig 1B

ime (reset)

Crystal oscillator sewing tose>_—«10) 10 ere 0 eee Ore ig 169)

sme (software standby)

HITACHI

Hach Amer, Lt. + Hach Pasa +2000 Sra Pont Pkwy.» Grstane, CA 94005-1810 (418 89.8900

283

284

Table 16-8. Timing Conditions of On-Chip Supporting Modules (Preliminary)

Condition A: Vec = 5.0V #10%, Vss = OV, ® = 0.5MHz to maximum operating frequency,

Ta = -20 to 75°C (regular specifications),

Ta =—40 to 85°C (wide-range specifications)

Condition B: Vcc = 3.0V +10%, Vss = OV, @ = 0.5MHz to maximum operating frequency,

Ta = -2010 75°C

Condition A

SMa 6MHz_—<8MHz_—_‘10MHz Measurement

Item Symbol_Min Max Min Max Min Max Min Max Unit conditions

FRI Timer outputdelay ume uro>- 150 - 100 - 100 - 100 ns Fig 1610

Timer input sewptime uns 80-50. 30 50 as Fig. 1610

Timerclockinput ees D-DD as Fig. 1611

setup time

Timer clockpulse width wrown 15 - 15 - 1S - 1S — tye Fig lead

row.

TMR Timer output delay ime Too 150-100 - 100 «100s ‘Fig 1612

“Timer reset input ts 80-0 Fi GL

setup time

Timerclockmput mcs TGA

setup time

Timer clock pulse width wwewn 1S - 15 - 1S - 15 — uw Fig lela

{ingle edge)

Timer clock pulse width truco 25° - 25 - 25 - 25 ee Fig. 16-13

(both edges) -

PWM Timer output delay time woo 150 100 100-100 ns Fig 1615

SCI Inputclock (Async) tex 2 = pane oe Fig 1616

oycle (Sync) bx 6 6 - 6 - toe Fig 1616

Transmitdaia delay xD ~—«200:~-~—«100~——=—«100 300 ns Fig. 16-16

time (Sync)

Receive daa sewpume ws 150 - 10 - 10 - 100 ns Fig. 1616

(Syne)

Receive dataholdtime wn 150 - 100 - 100 - 100 - ns Fig. 16-16

(Syne)

Input clock pulse width wexw 04 06 04 06 04 tee Fig. 1617

Ponts Ourput data delay time wa 150) 100 ns Fig. 1618

Input data setupume was 80 SO «SO. ns Fig 1618

Inputdatahold me ome 80-50-50. fs Fig 1618

HITACHI

each: Amerea Li + Hach Plaza +2000 Set Pont Phy « Basbane. CA $4005:1019 (415) 568.8900

+ Measurement Conditions for AC Characteristics

gsv

Re

Inputroutpet tina reterence levels

Low 08Y

High 20¥

Figure 16-3. Output Load Circuit

16.2.3 A/D Converter Characteristics

Table 16-9 lists the characteristics of the on-chip A/D conv!

Table 16-9. A/D Converter Characteristics (Preliminary)

Condition A: Vcc = 5.0V +10%, AVcc = 5.0V 210%, Vss = AVss = OV, @ = 0.5MHz to maximum,

‘operating frequency, Ta = -20 to 75°C (regular specifications),

Ta = ~40 10 85°C (wide-range specifications)

Condition B: Vec = 3.0V £10%, AVEC = 5.0V 10%, Vs5 = AVSS = OV. O =

‘maximum operating frequency, Ta = ~20 t0 75°C

SMHz to

Condition B Condition A

MHz oMHz ‘MHz TOME

tem Max Min Typ Max Min Typ Max Min Typ Max Unit

Resolution ss 8 @ @ ® 8 & 8 8 8 8 Bis

Conversion time «single mode} = ua oa 15.25 us

‘Analog mput capaciance OO OOO OO PF

Allowable signal source So > pH

impedance

Nonlinearity error ==

Ottset error =

a

“Absolute accuracy =

Note: * Values at maximont opera

ing frequency

HITACHI

each Amercs Li. Hsach Plazs = 2000 Sera Port Py, = Brsbane, CA 9005-1819 + (415) 555-5300

285

16.2.4 D/A Converter Characteristics

Table 16-10 lists the characteristics of the on-chip D/A converter.

Table 16-10. D/A Converter Characteristics

Condition A: Vcc = 5.0V £10%, AVcc = 5.0V £10%, Vss = AVss = OV, @ = 0.5MHz to maximum

operating frequency, Ta = -20 to 75°C (regular specifications),

Ta = 40 to 85°C (wide-range specifications)

Condition B: Voc = 3.0V £10%, AVec = 5.0V +10%, Vss = AVss = OV, 0 =

SMHz to maximum

operating frequency, Ta = -20 t0 75°C

Condition B Condition

SMHiz ontiz aMHz TMH Measurement

lem Min Typ Max Min Typ Max Min Typ Max Min Typ Max Unit conditions

Resolution 3 8 8 8 8 8 8 8 8 8 8 8 Bis

Conversiontime — — 100 — — 100 — — 100 — — 100 us 30pFload

capacitance

Abolucacumey — 21 213 — al AS — A aS — “IS (SB 2MQ toad

resistance

aes ae TSB 4MO load

resistance

16.3 MCU Operational Timing

This section provides the following timing charts:

16.3.1 Bus Timing Figures 16-4 to 16-5

16.3.2 Control Signal Timing Figures 16-6 10 16-9

16.3.3 16-Bit Free-Running Timer Timing Figures 16-10 to 16-11

16.3.4 8-Bit Timer Timing Figures 16-12 to 16-14

16.3.5 PWM Timer Timing Figure 16-15

16.3.6 SCI Timing Figures 16-16 to 16-17

16.3.7 1/0 Port Timing Figure 16-18

HrracHt

AG each Aenea. td» Haseh Plaza +2000 Sera Post Phy. «Brisbane, CA 94005-1818

5) 889.6900

16.3.1 Bus Timing

(1) Basic Bus Cycle (without Wait States) in Expanded Modes

AS, RD

Sree

(Res)

wa

Drto De

(write

Figure 16-4. Basic Bus Cycle (without Wait States) in Expanded Modes

HITACHI

each Amenca, Lie. «Hach Plaza 2000 Serra Point Phy“ Bnsbane, CR 94005-1819 = 435) 588-8900 287

(2) Basic Bus Cycle (with 1 Wait State) in Expanded Modes

rt 2 Tw 3

Bat A

38,95

Deo

(Rea)

wa

roo

(wey tare Ht

Figure 16-5. Basic Bus Cycle (with I Wait State) in Expanded Modes

16.3.2 Control Signal Timing

() Reset Input Ti

° he a a

Figure 16-6. Reset Input Timing

HITACHI

each Aenea 18 + Heach Plana +2000 Sama Pot Pay «Brisbane. CA 92005-1839 (415) 588.8500

288

(2) Interrupt Input Timing

° ~\ Ys

twmis| [ras

TROe (Eog0) of

tuws|

FAQ. (Level) sf

te

Eva

FO

— fF}

Now: |= 007

Figure 16-7, Interrupt Input Timing

HrracHt

each Amerca, Li. + Htach Plaza +2000 Sera Pont Pxwy. « Basbane, CA 4005-1819 (415) 598.00,

289

290

(3) Clock Settling Timing

tose

—

toses

iB

° fm AP ADA. rr

so

Vee.

RES

1B

HITACHI

‘each Amenea, Lid + Mach Plaza +2000 Sera Port Phy. + Grabane, CA 94005-1815 +418) S80-8000

Figure 16-8. Clock Settling Timing

(4) Clock Settling Timing for Recovery from Software Standby Mode

———

Gy,

roy %

RO.

(20.1.2) ue

Figure 16-9. Clock Settling Timing for Recovery from Software Standby Mode

16.3.3 16-Bit Free-Running Timer Timing,

) Free-Running Timer Input/Output Timing

° LS NANG \ YK VN

Freennning romana

mer courter Compare:match

too

FTon,, FTOB ‘

ins

Fria, E718,

Fric, F110

Figure 16-10. Free-Running Timer Input/Output Timing

HITACHI

tachi Amenca, Lid + Haaeh Paza +2000 Sia Pont Phy. * Brisbane, CA 54005-1819 + (415) 565-6200,

291

292

(2) External Clock Input Timing for Free-Running Timer

o f/f \_Ss* eZ

tees

Frei } aa

Terom. trea

Figure 16-11, External Clock Input Timing for Free-Running Timer

16.3.4 8-Bit Timer Timing

(1) 8-Bit Timer Output Timing

Figure 16-12, 8-Bit Timer Output Ti

(2) 8-Bit Timer Clock Input Timing

e Js ss

Tacs, Tacs

Figure 16-13. 8-Bit Timer Clock Input Timing

HITACHI

rach Amenca, Lie + Hiaeh Pasa 2000 Siena Point Pray. nsbane. CA 93005-1810 (E15) $89.80

(3) 8-Bit Timer Reset Input Timing

Tune

TMRe,

TMRI:

Timer W 00

counter

Figure 16-14, 8-Bit Timer Reset Input Timing

16.3.5 Pulse Width Modulation Timer Ti

ten, “Gna meh [

Pv, PW

Figure 16-15, PWM Timer Output Timing

16.3.6 Serial Communication Interface Timing

(1) SCI Input/Output

tse

Saal clock

(scK)

tre

Transmit

(0)

nce — Se

(xD)

Figure 16-16, SCI Input/Output Timing (Synchronous Mode)

HITACHI

rac Annes, Ls + Hise: Plaga +2000 Sera Pot Pay. » Bnsbane, CA 94006-1819 (418) 589.8900 293

294

(2) SCI Input Clock Timing

teow

sck

Ise

Figure 16-17. SCI Input Clock Timing

16.3.7 VO Port Timing

Port 1

(input)

Pong

Pon 1" St

1B (Output)

Pon

Note: * Exaopt Pac and P7110 P76

Figure 16-18. 1/0 Port Input/Output Timing

HITACHI

each Amenca. Lio + Htaem Plaza + 2000 Sera Pont Pay,“ Bisbane, CA 86005-1819 = 415) 588-8500

Das könnte Ihnen auch gefallen

- High Voltage, Current Shunt Monitor: Data SheetDokument13 SeitenHigh Voltage, Current Shunt Monitor: Data SheetHla Swe OoNoch keine Bewertungen

- HGM6300D V2.1 enDokument34 SeitenHGM6300D V2.1 enSteven BaynesNoch keine Bewertungen

- Features Description: Issi IssiDokument12 SeitenFeatures Description: Issi IssiHla Swe OoNoch keine Bewertungen

- PNP Silicon: Semiconductor Technical DataDokument4 SeitenPNP Silicon: Semiconductor Technical DataHla Swe OoNoch keine Bewertungen

- Infineon Bts5215l Ds v01 01 enDokument16 SeitenInfineon Bts5215l Ds v01 01 enchawkigenieNoch keine Bewertungen

- Silicon Switching Diodes BAS 19 BAS 21: Type Ordering Code (Tape and Reel) Marking Package Pin ConfigurationDokument4 SeitenSilicon Switching Diodes BAS 19 BAS 21: Type Ordering Code (Tape and Reel) Marking Package Pin ConfigurationHla Swe OoNoch keine Bewertungen

- Toshiba: Discrete SemiconductorsDokument2 SeitenToshiba: Discrete SemiconductorsHla Swe OoNoch keine Bewertungen

- Pzuxb Series: 1. Product ProfileDokument12 SeitenPzuxb Series: 1. Product ProfileHla Swe OoNoch keine Bewertungen

- Data Sheet: High Speed CAN TransceiverDokument17 SeitenData Sheet: High Speed CAN TransceiverGautam PrashantNoch keine Bewertungen

- Data Sheet: High Speed CAN TransceiverDokument16 SeitenData Sheet: High Speed CAN TransceiverHla Swe OoNoch keine Bewertungen

- 1AZ Zener Diode SeriesDokument3 Seiten1AZ Zener Diode SeriesHla Swe OoNoch keine Bewertungen

- Atmel 2545 8 Bit AVR Microcontroller ATmega48!88!168 SummaryDokument25 SeitenAtmel 2545 8 Bit AVR Microcontroller ATmega48!88!168 SummaryHla Swe OoNoch keine Bewertungen

- Data Sheet: High Speed CAN TransceiverDokument16 SeitenData Sheet: High Speed CAN TransceiverHla Swe OoNoch keine Bewertungen

- Atmel Quality HandbookDokument36 SeitenAtmel Quality HandbookHla Swe OoNoch keine Bewertungen

- 5-V Low-Drop Fixed Voltage Regulator TLE 4271-2: FeaturesDokument20 Seiten5-V Low-Drop Fixed Voltage Regulator TLE 4271-2: FeaturesHla Swe Oo0% (1)

- Supervisory Circuits With I C Serial 2k-Bit CMOS EEPROM, Manual Reset and Watchdog TimerDokument21 SeitenSupervisory Circuits With I C Serial 2k-Bit CMOS EEPROM, Manual Reset and Watchdog TimerHla Swe OoNoch keine Bewertungen

- Cummins Celect or Celect Plus Ecm Order Form: Midwest Ecm Repair LLCDokument1 SeiteCummins Celect or Celect Plus Ecm Order Form: Midwest Ecm Repair LLCHla Swe OoNoch keine Bewertungen

- SS32, SS33, SS34, SS35, SS36: Vishay General SemiconductorDokument4 SeitenSS32, SS33, SS34, SS35, SS36: Vishay General SemiconductorHla Swe OoNoch keine Bewertungen

- SM8 Transient SupressorDokument5 SeitenSM8 Transient SupressorSergio ReyesNoch keine Bewertungen

- 1N5819 SMDDokument2 Seiten1N5819 SMDHla Swe OoNoch keine Bewertungen

- SM8 Transient SupressorDokument5 SeitenSM8 Transient SupressorSergio ReyesNoch keine Bewertungen

- Semiconductor KF5N50PR/FR/PS/FS: Technical DataDokument7 SeitenSemiconductor KF5N50PR/FR/PS/FS: Technical DataHla Swe OoNoch keine Bewertungen

- Semiconductor KF5N50PR/FR/PS/FS: Technical DataDokument7 SeitenSemiconductor KF5N50PR/FR/PS/FS: Technical DataHla Swe OoNoch keine Bewertungen

- Btd1857A3: Cystech Electronics CorpDokument9 SeitenBtd1857A3: Cystech Electronics CorpHla Swe OoNoch keine Bewertungen

- TC4027BP, TC4027BF, TC4027BFN: TC4027B Dual J-K Master-Slave Flip FlopDokument9 SeitenTC4027BP, TC4027BF, TC4027BFN: TC4027B Dual J-K Master-Slave Flip FlopHla Swe OoNoch keine Bewertungen

- Not Recommended For New Designs: Features Package TypesDokument26 SeitenNot Recommended For New Designs: Features Package TypesLedjon BehluliNoch keine Bewertungen

- Product Data Sheet: Altira - French Socket-Outlet ROTOCLIP Tamperproof With Lamp Red CoverDokument2 SeitenProduct Data Sheet: Altira - French Socket-Outlet ROTOCLIP Tamperproof With Lamp Red CoverHla Swe OoNoch keine Bewertungen

- SH88F516 88F54 89F52V2.5 PDFDokument105 SeitenSH88F516 88F54 89F52V2.5 PDFHla Swe OoNoch keine Bewertungen

- SS14 SS16 SS110Dokument5 SeitenSS14 SS16 SS110Hla Swe OoNoch keine Bewertungen

- Description Features: Lt1766/Lt1766-5 5.5V To 60V 1.5A, 200Khz Step-Down Switching RegulatorDokument30 SeitenDescription Features: Lt1766/Lt1766-5 5.5V To 60V 1.5A, 200Khz Step-Down Switching RegulatorHla Swe OoNoch keine Bewertungen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (120)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)