Beruflich Dokumente

Kultur Dokumente

(Doi 10.1109/ISSCC.2013.6487622) Parikh, S. Kao, T. Hidaka, Y. Jian Jiang, Toda, A. Mcleod, - (IEEE 2013 IEEE International Solid-State Circuits Conference (ISSCC 2013) - San Francisco, CA (2

Hochgeladen von

sulagnadeyOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

(Doi 10.1109/ISSCC.2013.6487622) Parikh, S. Kao, T. Hidaka, Y. Jian Jiang, Toda, A. Mcleod, - (IEEE 2013 IEEE International Solid-State Circuits Conference (ISSCC 2013) - San Francisco, CA (2

Hochgeladen von

sulagnadeyCopyright:

Verfügbare Formate

ISSCC 2013 / SESSION 2 / ULTRA-HIGH-SPEED TRANSCEIVERS AND EQUALIZERS / 2.

2.1 A 32Gb/s Wireline Receiver with a Low-Frequency Figure 2.1.3 shows the implementation of the data path with 2-tap speculative

Equalizer, CTLE and 2-Tap DFE in 28nm CMOS DFE, boundary samplers and error samplers. Error samplers with a speculative

configuration are used to reduce power and area. They determine the error infor-

Samir Parikh1, Tony Kao1, Yasuo Hidaka1, Jian Jiang1, Asako Toda1, mation by applying the various DFE and reference levels combinatorially. A lin-

Scott Mcleod1, William Walker1, Yochi Koyanagi2, Toshiyuki Shibuya2, ear transconductor circuit (LTC), used in front of the error sampler, can be con-

Jun Yamada3 figured to inject 3 different currents in the signal path, each with positive/nega-

tive polarity. Thus, the LTC can provide all 8 combinations needed for specula-

1

Fujitsu Laboratories of America, Sunnyvale, CA, tive error sampling. The equalizer adaption block correlates the speculative error

2

Fujitsu Laboratories, Kawasaki, Japan, 3Fujitsu, Kawasaki, Japan samples with the data samples to select the correct error samples. One of the

current inputs in each LTC is used to add/subtract an offset compensation cur-

Standards such as OIF CEI-25G, CEI-28G and 32G-FC require transceivers oper- rent to calibrate for the offset of the sampler connected to it. In the data path, the

ating at high data rates over imperfect channels. Equalizers are used to cancel two other LTC inputs are used to perform DFE speculation by applying four dif-

the inter-symbol interference (ISI) caused by frequency-dependent channel loss- ferent level shifts for each of the four speculative paths. A digital feedback cir-

es such as skin effect and dielectric loss. The primary objective of an equalizer cuit is implemented in the data path to correctly select the two data samples

is to compensate for high-frequency loss, which often exceeds 30dB at fs/2. from the eight speculative data samples.

However, due to the skin effect in a PCB stripline, which starts at 10MHz or

lower, we also need to compensate for a small amount of loss at low frequency The CTLE and LFEQ circuits are shown in Fig. 2.1.4. The CTLE implements a zero

(e.g., 500MHz). Figure 2.1.1 shows simulated responses of a backplane channel in the signal path using source degeneration. The location of the zero is tuned by

(42.6dB loss at fs/2 for 32Gb/s) with conventional high-frequency equalizers digital control of the source-degeneration resistor (Rs1), while the location of the

only (4-tap feed-forward equalizer (FFE), 1st-order continuous-time linear equal- poles is fixed by design with the dominant pole occurring at fs/4. In contrast, the

izer (CTLE) with a dominant pole at fs/4, and 1-tap DFE) and with additional low- LFEQ implements a zero at low frequency (500MHz) through a feedback topolo-

frequency equalization. Conventional equalizers cannot compensate for the small gy. This topology implements variable gain in the feedback path to control the

amount of low-frequency loss because the slope of the low-frequency loss is too first pole, fp1, from 500MHz to 1GHz. Since the CTLE provides large boost (0 to

gentle (<3dB/dec). The FFE and CTLE do not have a pole in the low frequency 15dB) at high frequencies to compensate for dielectric loss and skin effect, while

region and hence have only a steep slope of 20dB/dec above their zero. The DFE the LFEQ implements a small amount of equalization (0 to 4dB) to compensate

cancels only short-term ISI. Effects of such low-frequency loss have often been for the gentle slope of the low frequency loss due to skin effect, their design

overlooked or neglected, because 1) the loss is small (2 to 3dB), 2) when plot- requirements are quite different. The CTLE poles are restricted to fs/4 or higher

ted using the linear frequency axis which is commonly used to show frequency and require the ability to tune the zero in relatively high frequency (1 to 8GHz)

dependence of skin effect and dielectric loss, the low-frequency loss is degener- with a wide range. As a result, the span between the first pole and zero depends

ated at DC and hardly visible (Fig. 2.1.1a), and 3) the long ISI tail of the channel only on the location of the zero. On the other hand, the only restriction in a LFEQ

pulse response seems well cancelled at first glance by conventional equalizers is that its first pole and zero must be close to each other. In other words, the

only (Fig. 2.1.1b). However, the uncompensated low-frequency loss causes non- placement of the pole-zero pair gives us two degrees of freedom; the first being

negligible long-term residual ISI, because the integral of the residual ISI magni- the center frequency, and the second being the span of the pair. In our imple-

tude keeps going up for several hundred UI. As shown by the eye diagrams in mentation, we implement a fixed zero at 500MHz and tune the first pole (fp1) in

the inset of Fig. 2.1.1(b), the residual long-term ISI results in 0.42UI data- a small frequency range above the zero.

dependent Jitter (DDJ) that is difficult to reduce further by enhancing

FFE/CTLE/DFE, but can be reduced to 0.21UI by adding a low-frequency equaliz- A die micrograph of the 28nm test chip is shown in Fig. 2.1.7. The total area of

er (LFEQ). Savoj et al. also recently reported long-tail cancellation [2]. the RX is 0.33mm2 and it consumes 240mW of power from a 0.9V supply when

operating at 32Gb/s with the CDR and related clock circuits powered down. The

In this paper, we present a 32Gb/s receiver (RX) capable of loss compensation differential input return loss is measured to be better than 10dB from 0 to

from low frequency to high frequency. Due to the addition of a LFEQ, the RX 20GHz, and is shown in Fig. 2.1.5. The receiver achieves a BER <10-12 over a 31-

compensates for low frequency losses due to skin effect while intermediate and inch PCB trace with 37dB loss at 16GHz (40dB total loss with receiver package)

high frequency losses are compensated by a CTLE up to fs/4 and by a 2-tap DFE using a TX with 3-tap FFE and 1Vpp differential swing. Figure 2.1.6(a) shows the

at fs/2. Recent work [1-2] has shown equalizers using peaking inductors/T-coils trace characteristics and Fig. 2.1.6(b) shows the measured bathtub curve. The

for bandwidth enhancement. However, the equalizers in this RX are implement- BER floor is improved from 10-7 to <10-12 with the LFEQ.

ed without passive or active inductors. The RX achieves BER<10-12 with a 32Gb/s

PRBS31 pattern over a channel with 40dB loss at 16GHz. References:

[1] J. Bulzacchelli et al., “A 28Gb/s 4-Tap FFE/15-Tap DFE Serial Link Transceiver

The RX, shown in Fig. 2.1.2, is implemented using a half-rate architecture. It in 32nm SOI CMOS Technology,” in ISSCC Dig. Tech. Papers, pp. 324-325, Feb.

consists of a T-coil-based input-termination network, CTLE, LFEQ, 2-tap specu- 2012.

lative DFE, clock recovery, and equalizer adaptation circuits. T-coils are used at [2] J. Savoj, et al., “A Wide Common-Mode Fully-Adaptive Multi-Standard

the receiver input to compensate for the capacitance of the ESD network in order 12.5Gb/s Backplane Transceiver in 28nm CMOS,” in VLSI Circuits Dig. Tech.

to meet the return-loss specifications. Boundary samplers capture the phase Papers, pp.104-105, June 2012.

error at the CTLE output and since the CTLE only cancels residual ISI up to fs/4, [3] Y. Hidaka, et al., “A 4-Channel 10.3Gb/s Transceiver with Adaptive Phase

clock recovery is performed using pattern filtering [3] to use the phase error only Equalizer for 4-to-41dB Loss PCB Channel,” in ISSCC Dig. Tech. Papers, pp.

for frequencies below fs/4. The recovered clock is generated from a half-rate ref- 346-347, Feb 2011.

erence clock with a CML-to-CMOS level converter, a duty-cycle corrector (DCC), [4] Y. Hidaka, et al., “A 4-Channel 1.25-10.3Gb/s Backplane Transceiver Macro

a four-phase generator, and independent phase interpolators for the data path With 35dB Equalizer and Sign-Based Zero-Forcing Adaptive Control,” IEEE J.

and boundary path. The speculative error sampler provides error information to Solid-State Circuits, vol. 44, no. 12, pp.3547-3559, Dec. 2009.

the equalizer adaptation block, which also uses pattern filtering [4]. In the equal-

izer adaptation block, pattern filtering is used to implement sign-based zero-

forcing (S-ZF) for adaptation of the LFEQ and CTLE circuits, to implement sign-

sign least mean square (SS-LMS) for DFE adaptation, and to correctly select the

speculative error samples. Since detection of long-term ISI (e.g., 10 to 1000UI)

is necessary for LFEQ adaptation, S-ZF is extended by dealing with the long-term

ISI in an aggregate manner.

28 • 2013 IEEE International Solid-State Circuits Conference 978-1-4673-4516-3/13/$31.00 ©2013 IEEE

ISSCC 2013 / February 18, 2013 / 1:30 PM

Figure 2.1.1: Frequency-domain and time-domain responses of a backplane

channel with and without low frequency equalization. Figure 2.1.2: Receiver block diagram.

Figure 2.1.3: Data path with two-tap speculative DFE, boundary and error

path. Figure 2.1.4: CTLE and low-frequency equalizer.

Figure 2.1.6: Measurement results: channel characteristic and bathtub

Figure 2.1.5: Receiver′s differential input return loss measurement. curves.

DIGEST OF TECHNICAL PAPERS • 29

ISSCC 2013 PAPER CONTINUATIONS

Figure 2.1.7: Die micrograph.

• 2013 IEEE International Solid-State Circuits Conference 978-1-4673-4516-3/13/$31.00 ©2013 IEEE

Das könnte Ihnen auch gefallen

- Organic Light-Emitting Transistors: Towards the Next Generation Display TechnologyVon EverandOrganic Light-Emitting Transistors: Towards the Next Generation Display TechnologyNoch keine Bewertungen

- A 5-Ghz Programmable Frequency Divider in 0.18-M Cmos TechnologyDokument5 SeitenA 5-Ghz Programmable Frequency Divider in 0.18-M Cmos TechnologyAram ShishmanyanNoch keine Bewertungen

- Blind Paper SpineDokument5 SeitenBlind Paper SpineJoao PauloNoch keine Bewertungen

- Pozzoni 2010Dokument3 SeitenPozzoni 2010يوسف إبراهيمNoch keine Bewertungen

- Design and Optimization of ÷8/9 Divider in PLL Frequency Synthesizer With Dynamic Logic (E - TSPC)Dokument5 SeitenDesign and Optimization of ÷8/9 Divider in PLL Frequency Synthesizer With Dynamic Logic (E - TSPC)himaja1Noch keine Bewertungen

- A Low Power Single Phase Clock Distribution Using VLSI TechnologyDokument5 SeitenA Low Power Single Phase Clock Distribution Using VLSI TechnologyNano Scientific Research Centre pvt ltd100% (1)

- A Low Power, and Low Signal 5-Bit 25msamples/s Pipelined ADC For Monolithic Active PixelsDokument5 SeitenA Low Power, and Low Signal 5-Bit 25msamples/s Pipelined ADC For Monolithic Active Pixelstajmjcet_123Noch keine Bewertungen

- 11 A Low-Power Single-Phase Clock MultibandDokument5 Seiten11 A Low-Power Single-Phase Clock MultibandDilip KumarNoch keine Bewertungen

- A Universal GNSS GPS Galileo Glonass BeiDokument3 SeitenA Universal GNSS GPS Galileo Glonass BeiOmer TariqNoch keine Bewertungen

- Ultra-Wideband Low Noise Amplifier Using A Cascode Feedback TopologyDokument3 SeitenUltra-Wideband Low Noise Amplifier Using A Cascode Feedback TopologyAsad AsadiNoch keine Bewertungen

- A High-Speed Continuous-Time Bandpass VHF Filter in TechnologyDokument4 SeitenA High-Speed Continuous-Time Bandpass VHF Filter in Technologyعاطف رضاNoch keine Bewertungen

- Baba Safari 2018Dokument13 SeitenBaba Safari 2018fa.elhardouziNoch keine Bewertungen

- A Low Phase Noise Tri-Band LO Generation For Ku and E Band Radios For Backhauling Point-to-Point ApplicationsDokument4 SeitenA Low Phase Noise Tri-Band LO Generation For Ku and E Band Radios For Backhauling Point-to-Point ApplicationsrinsonNoch keine Bewertungen

- Design of A 2.5Ghz Differential Cmos Lna: Z SC G C L S (L SC LDokument4 SeitenDesign of A 2.5Ghz Differential Cmos Lna: Z SC G C L S (L SC LnaveenmotamarriNoch keine Bewertungen

- Ibm PllserdesDokument3 SeitenIbm PllserdesMeeraNoch keine Bewertungen

- A 5.8-Ghz High Efficient, Low Power, Low Phase Noise Cmos Vco For Ieee 802.11ADokument4 SeitenA 5.8-Ghz High Efficient, Low Power, Low Phase Noise Cmos Vco For Ieee 802.11ARitika SinghNoch keine Bewertungen

- Fiber Based Mach-Zehnder Interferometric Structures: Principles and Required Characteristics For Efficient Modulation Format ConversionDokument9 SeitenFiber Based Mach-Zehnder Interferometric Structures: Principles and Required Characteristics For Efficient Modulation Format ConversionizamaiyusNoch keine Bewertungen

- An Fpga-Based Electronic Cochlea With Dual Fixed-Point ArithmeticDokument6 SeitenAn Fpga-Based Electronic Cochlea With Dual Fixed-Point ArithmeticcutiepiemaniNoch keine Bewertungen

- Isscc 2010 / Session 20 / Next-Generation Optical & Electrical Interfaces / 20.4Dokument3 SeitenIsscc 2010 / Session 20 / Next-Generation Optical & Electrical Interfaces / 20.4Karthikeyan GunasekaranNoch keine Bewertungen

- 10.1109-MWSCAS.2007.4488734-A Systematic System Level Design Methodology For Dual Band CMOS RF ReceiversDokument4 Seiten10.1109-MWSCAS.2007.4488734-A Systematic System Level Design Methodology For Dual Band CMOS RF ReceiversAsghar FarhadiNoch keine Bewertungen

- Design and Implementation of 2 Bit Loaded Line Phase ShifterDokument5 SeitenDesign and Implementation of 2 Bit Loaded Line Phase ShifterdhvbkhnNoch keine Bewertungen

- Design of Robust RF-MEMS Phase Shifters in Ka-BandDokument13 SeitenDesign of Robust RF-MEMS Phase Shifters in Ka-Bandloga rajesh waranNoch keine Bewertungen

- Duo Binary Modulation For Optical SystemsDokument10 SeitenDuo Binary Modulation For Optical SystemsErasmo VizzaccaroNoch keine Bewertungen

- A 2.4-Ghz Low-Flicker-Noise Cmos Sub-Harmonic ReceiverDokument11 SeitenA 2.4-Ghz Low-Flicker-Noise Cmos Sub-Harmonic ReceiverdabalejoNoch keine Bewertungen

- Research ArticleDokument10 SeitenResearch Articlerizal iskandarNoch keine Bewertungen

- A Broadband Cmos Multiplier-Based Correlator For Ir-Uwb Transceiver SocDokument4 SeitenA Broadband Cmos Multiplier-Based Correlator For Ir-Uwb Transceiver SocmiracuNoch keine Bewertungen

- A Narrow-Band CMOS FM Receiver Based On Single-Sideband Modulation IF FilteringDokument8 SeitenA Narrow-Band CMOS FM Receiver Based On Single-Sideband Modulation IF FilteringVivek RoyNoch keine Bewertungen

- 1.12-Tbs 32-QAM-OfDM Superchannel With 8.6-BsHz Intrachannel Spectral Efficiency and Space-Division Multiplexing With 60-BsHz Aggregate Spectral EfficiencyDokument3 Seiten1.12-Tbs 32-QAM-OfDM Superchannel With 8.6-BsHz Intrachannel Spectral Efficiency and Space-Division Multiplexing With 60-BsHz Aggregate Spectral Efficiencymalhiavtarsingh100% (1)

- Wireless CommunicationDokument29 SeitenWireless CommunicationRakesh MenonNoch keine Bewertungen

- A4FD1924d01 Wilkinson TheoryDokument4 SeitenA4FD1924d01 Wilkinson TheorymrzahzNoch keine Bewertungen

- A 6-b 1-GS/s 30-mW ADC in 90-nm CMOS Technology: Yuan-Ching Lien and Jri Lee National Taiwan University, Taipei, TaiwanDokument4 SeitenA 6-b 1-GS/s 30-mW ADC in 90-nm CMOS Technology: Yuan-Ching Lien and Jri Lee National Taiwan University, Taipei, TaiwanSunil PandeyNoch keine Bewertungen

- 28.8 A 21dBm-OP1dB 20.3-Efficiency - 131.8dBm Hz-Noise X-Band Cartesian-Error-Feedback Transmitter With Fully Integrated Power Amplifier in 65nm CMOSDokument3 Seiten28.8 A 21dBm-OP1dB 20.3-Efficiency - 131.8dBm Hz-Noise X-Band Cartesian-Error-Feedback Transmitter With Fully Integrated Power Amplifier in 65nm CMOSRAJANoch keine Bewertungen

- 2.4-Ghz Single-Ended Input Low-Power Low-Voltage Active Front-End For Zigbee Applications in 90 NM CmosDokument4 Seiten2.4-Ghz Single-Ended Input Low-Power Low-Voltage Active Front-End For Zigbee Applications in 90 NM CmosdilixyzNoch keine Bewertungen

- Microelectronics Journal: Habib Rastegar, Jee-Youl RyuDokument8 SeitenMicroelectronics Journal: Habib Rastegar, Jee-Youl RyuRAJAMOHANNoch keine Bewertungen

- An 11.1 Gbps Analog PRML Receiver For Electronic Dispersion Compensation of Fiber Optic CommunicationsDokument16 SeitenAn 11.1 Gbps Analog PRML Receiver For Electronic Dispersion Compensation of Fiber Optic CommunicationsGbarbarNoch keine Bewertungen

- A Single-Opamp Third Order CT Modulator With SAB-ELD-Merged Integrator and Three-Stage Hybrid Compensation OpampDokument11 SeitenA Single-Opamp Third Order CT Modulator With SAB-ELD-Merged Integrator and Three-Stage Hybrid Compensation OpampellieNoch keine Bewertungen

- A 4.5mm2 Multimodal Biosensing SoC For PPG, ECG, BIOZ and GSR Acquisition in Consumer Wearable DevicesDokument3 SeitenA 4.5mm2 Multimodal Biosensing SoC For PPG, ECG, BIOZ and GSR Acquisition in Consumer Wearable DevicesgetitabidNoch keine Bewertungen

- 12 A Low-Power Low-Noise Amplifier For EEG ECG Signal Recording ApplicationsDokument4 Seiten12 A Low-Power Low-Noise Amplifier For EEG ECG Signal Recording ApplicationsViplaw KumarNoch keine Bewertungen

- Low Noise Amplifier Design Using 0.35 Μm Sige Bicmos Technology For Wlan/Wimax ApplicationsDokument5 SeitenLow Noise Amplifier Design Using 0.35 Μm Sige Bicmos Technology For Wlan/Wimax ApplicationssunilsheelavantNoch keine Bewertungen

- Implementation of Second Order Switched Capacitors Filters With Feedback SignalDokument3 SeitenImplementation of Second Order Switched Capacitors Filters With Feedback SignalInternational Journal of Application or Innovation in Engineering & ManagementNoch keine Bewertungen

- A Low-Power, Ultra Low-Offset, 16.5-Bit DS ADC For Coulomb Counting and Fuel Gauge ApplicationDokument4 SeitenA Low-Power, Ultra Low-Offset, 16.5-Bit DS ADC For Coulomb Counting and Fuel Gauge ApplicationnsitdelhiNoch keine Bewertungen

- A Comparative Study of CMOS LNAsDokument4 SeitenA Comparative Study of CMOS LNAsMohammad Arif SaberNoch keine Bewertungen

- Study On Equalizers: Anik Sengupta Sohom DasDokument11 SeitenStudy On Equalizers: Anik Sengupta Sohom DasAnikSenguptaNoch keine Bewertungen

- PSK Demodulation (Part 1)Dokument10 SeitenPSK Demodulation (Part 1)particlereddyNoch keine Bewertungen

- NIST Freguency ResponseDokument3 SeitenNIST Freguency ResponseSomsak NavayonNoch keine Bewertungen

- Bichan - Intel - Cicc2020 - A 32Gbs NRZ 37dB SerDes in 10nm CMOS To Support PCI Express Gen 5 ProtocolDokument4 SeitenBichan - Intel - Cicc2020 - A 32Gbs NRZ 37dB SerDes in 10nm CMOS To Support PCI Express Gen 5 ProtocolzhangwenNoch keine Bewertungen

- EMI Filter Design Using High Frequency Models of The Passive ComponentsDokument6 SeitenEMI Filter Design Using High Frequency Models of The Passive ComponentsBethel TesfahunNoch keine Bewertungen

- A 15mw 3125ghz PLL For Serial Backplane Transceivers in 013m CmoDokument3 SeitenA 15mw 3125ghz PLL For Serial Backplane Transceivers in 013m CmoAhmed ShafeekNoch keine Bewertungen

- Simultaneous OTDM Demultiplexing and Detection Using An Electroabsorption ModulatorDokument3 SeitenSimultaneous OTDM Demultiplexing and Detection Using An Electroabsorption ModulatorKarthik KrNoch keine Bewertungen

- Background Optical Noises Circumvention in LED Optical Wireless Systems Using OFDMDokument10 SeitenBackground Optical Noises Circumvention in LED Optical Wireless Systems Using OFDMtariq76Noch keine Bewertungen

- A New Microstrip Diplexer Using Coupled Stepped Impedance ResonatorsDokument4 SeitenA New Microstrip Diplexer Using Coupled Stepped Impedance ResonatorsJubril AkinwandeNoch keine Bewertungen

- C13Network Management Solution For PSPON WDMPON Using DS-OCDM PDFDokument3 SeitenC13Network Management Solution For PSPON WDMPON Using DS-OCDM PDFSashaNoch keine Bewertungen

- Application: Design For ProcessDokument4 SeitenApplication: Design For ProcessjaberyemeniNoch keine Bewertungen

- 1.5GHz Negative Impedance Converter PaperDokument3 Seiten1.5GHz Negative Impedance Converter PaperNestor Alberto EscalaNoch keine Bewertungen

- Impact of The Layout Components and FiltersDokument21 SeitenImpact of The Layout Components and Filtersnexy bNoch keine Bewertungen

- Progress in Electromagnetics Research Letters, Vol. 32, 177-186, 2012Dokument10 SeitenProgress in Electromagnetics Research Letters, Vol. 32, 177-186, 2012Utah UtahNoch keine Bewertungen

- Ring FilterDokument3 SeitenRing FilterAlagiri IndiaNoch keine Bewertungen

- 06301682Dokument3 Seiten06301682rajeeseenivasanNoch keine Bewertungen

- Design and Implementation of A Low-Voltage 2.4-Ghz Cmos RF Receiver Front-End For Wireless CommunicationDokument6 SeitenDesign and Implementation of A Low-Voltage 2.4-Ghz Cmos RF Receiver Front-End For Wireless CommunicationPaul ShineNoch keine Bewertungen

- E7971v2 2Dokument80 SeitenE7971v2 2Dante MeridiusNoch keine Bewertungen

- Basic GSM NotesDokument5 SeitenBasic GSM NotesHtet Myet NaingNoch keine Bewertungen

- PD FinalDokument25 SeitenPD FinalAnusha ChidagniNoch keine Bewertungen

- Doc. Mandatory-Spares Rev. ADokument7 SeitenDoc. Mandatory-Spares Rev. AMayank SharmaNoch keine Bewertungen

- SP WIFI Solution CiscoDokument64 SeitenSP WIFI Solution CiscoRalph NassifNoch keine Bewertungen

- FiltersDokument49 SeitenFiltersZubeda MemonNoch keine Bewertungen

- AMD FirePro V7900 DatasheetDokument2 SeitenAMD FirePro V7900 DatasheetvishadkapadiaNoch keine Bewertungen

- Sinhgad Academy of Engineering, Kondhwa (BK), Pune: Multiple Choice QuestionsDokument10 SeitenSinhgad Academy of Engineering, Kondhwa (BK), Pune: Multiple Choice QuestionsAbhiti ShrivastavaNoch keine Bewertungen

- NOTEBOOK ASUS ZENBOOK DUO UX481FL-BM070T (BLUE) - INTEL CORE I5-10210U, 8GB, 512GB SSD, MX250,14 - , WIND10 - MDP IT & Electronic StoreDokument4 SeitenNOTEBOOK ASUS ZENBOOK DUO UX481FL-BM070T (BLUE) - INTEL CORE I5-10210U, 8GB, 512GB SSD, MX250,14 - , WIND10 - MDP IT & Electronic Storemahdi ningNoch keine Bewertungen

- Subject Code Subject: Microcontroller and Embedded SystemsDokument15 SeitenSubject Code Subject: Microcontroller and Embedded SystemsSaharsh RajputNoch keine Bewertungen

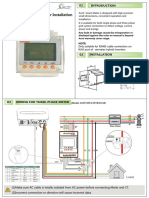

- Acrel Meter Installation Three PhaseDokument4 SeitenAcrel Meter Installation Three PhasehardaniNoch keine Bewertungen

- Pocket ZX Handheld ZX SpectrumDokument15 SeitenPocket ZX Handheld ZX SpectrumDavid ClodeNoch keine Bewertungen

- KX-TD 816 - 1232 Installation Manual Ver 6Dokument160 SeitenKX-TD 816 - 1232 Installation Manual Ver 6Ciprian VarNoch keine Bewertungen

- Operating Manual 760A, 770A and 771A DSP SubwoofersDokument24 SeitenOperating Manual 760A, 770A and 771A DSP SubwoofersNguyen Xuan HieuNoch keine Bewertungen

- Omnitik U 5hnd RVDokument1 SeiteOmnitik U 5hnd RVAntonio Edmundo Martinez AndradeNoch keine Bewertungen

- Commissioning and Integration LTE DUS - DULDokument5 SeitenCommissioning and Integration LTE DUS - DULColour BlindNoch keine Bewertungen

- Display Proximity Card Reader RDokument3 SeitenDisplay Proximity Card Reader RPeter MwanyowaNoch keine Bewertungen

- 2sa1941 & 2SC5198 - 140V - 10a - 100W - Audio AmplifierDokument4 Seiten2sa1941 & 2SC5198 - 140V - 10a - 100W - Audio Amplifiercris_powerNoch keine Bewertungen

- Sai Srujana Resume 2019Dokument2 SeitenSai Srujana Resume 2019Sai srujanaNoch keine Bewertungen

- 845-008B3A0 - gtc100202Dokument2 Seiten845-008B3A0 - gtc100202AhmadNoch keine Bewertungen

- AMS8100 Automatic Microphone Mixer: SchematicsDokument1 SeiteAMS8100 Automatic Microphone Mixer: SchematicsmirkodeNoch keine Bewertungen

- Chapter 23 CommunicationsDokument16 SeitenChapter 23 CommunicationsHrishikesh NarasimhanNoch keine Bewertungen

- Instructions CPS2 Multi Boot v2Dokument11 SeitenInstructions CPS2 Multi Boot v2Valdemar GomesNoch keine Bewertungen

- Arduino Programable 5 Pedal Switcher: by CarranDokument20 SeitenArduino Programable 5 Pedal Switcher: by CarranviniciusNoch keine Bewertungen

- MS 7267Dokument93 SeitenMS 7267Ml FalseNoch keine Bewertungen

- Hikvision Camera Supraveghere Ds 2cd2012 I PDFDokument1 SeiteHikvision Camera Supraveghere Ds 2cd2012 I PDFmariagodeanuNoch keine Bewertungen

- UBC ELEC 301 MP Report 4Dokument7 SeitenUBC ELEC 301 MP Report 4ednangiaNoch keine Bewertungen

- SyllabusDokument2 SeitenSyllabusvamshiNoch keine Bewertungen

- Dali Oberon White Paper 2020Dokument15 SeitenDali Oberon White Paper 2020mark_ferdinand_2Noch keine Bewertungen

- Li-Fi Technology: BY:-Abhishek Kumar B.Tech CSE 4 Year 1743110005Dokument23 SeitenLi-Fi Technology: BY:-Abhishek Kumar B.Tech CSE 4 Year 1743110005Nihal Roy100% (1)