Beruflich Dokumente

Kultur Dokumente

Assign1 Feb 20

Hochgeladen von

Neeraj IdnaniOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Assign1 Feb 20

Hochgeladen von

Neeraj IdnaniCopyright:

Verfügbare Formate

1. List 4 important parameters of packages.

2. What are the two challenges of packages compared to the die?

3. Explain the space transformation property of packaging and how it reduces the cost?

4. What are the three hierarchies of packaging?

5. What are the functions of packaging?

6. What are the three interconnection technologies for chip to package interconnection?

7. Find the round trip delay of a Printed Circuit board of size 6” and dielectric constant of 4.

8. An interconnect has a round trip delay of 0.4 ns, determine the minimum clock frequency

for which the transmission line model should be used.

9. What are the advantages of PTH packages compared to surface mount packages?

10. Compare the speed of propagation of a signal in embedded microstrip line and microstrip line.

11. Consider a strip line of length 4” with propagation delay and characteristic impedance

as 600ps and 50 Ω respectively. If it is to be modelled as N segments of transmission

line for a clock signal with rise time 2ns, What is the value of N? What is the inductance

of each segment of the strip line?

12. An inverter drives another inverter separated by a long interconnect which is modeled as a transmission

line with characteristic impedance of 50 Ω. The inverter has ON resistance of 10 Ω. What would

be the voltage at the load end at t = 4T where T is the propagation delay from generator to load.

Assume Vdd =5V

13. An inverter drives another inverter separated a long interconnect which is modeled as a transmission

line with characteristic impedance of 50 Ω. The inverter has ON resistance of 7.5 Ω. What would be the

voltage at the load end at t = 3T where T is the propagation delay from generator to load.

Assume Vdd=5V

14. Explain how the round trip delay of a Printed Circuit board of size 6” is 1 ns. .

15. How do you determine whether the transmission line model is required for an interconnect or not?

16. What is the inductance and capacitance per unit length of a parallel strip line with separation between

the planes and the width of the plane as d and w respectively?

17. Explain how the distance between the driver and the load affect the far end and near end cross talk ?

18. Explain how the effective inductance of vias can be minimized.

19. Explain how the decoupling capacitors reduce the simultaneous switching noise?

20. Why does the location at which the decoupling capacitor is put determine the highest frequency at

which they are effective?

21. Consider an inverter circuit driving a 1 pF capacitive load. If 500 such circuit switches binary states in

time 10 ns, What should be the maximum effective inductance , if the Power supply voltage variation

should not exceed 10% of Vdd.

22. In order to restrict the SSN to be 250mV a decoupling capacitor of 20 pF is used with a power supply

path having an effective impedance of 5 pH. What is the maximum frequency upto which the

decoupling capacitor would be effective in restricting the SSN within the limit?

23. Why is the line width decreased at the branching points in the H tree?

24. With a diagram show how either a power tree or a large buffer can minimize the skew due to clock distribution network

25. Explain why a hybrid clock distribution scheme which routes the clock through both chip and package is preferred?

26. A clock distribution network has the following characteristics: Rise/Fall Time: 1 ns , Setup/Hold Time: 1 ns and Skew and

Jitter: 1 ns, what is maximum data rate that can be used with this systems?

27. In which of the clock distribution architectures, the minimum clock frequency depends on N- the number of bits transmitted

during tf (time of flight: the time taken for the signal to travel from Tx to Rx).

28. What are the advantages and challenges in source synchronous clock distribution architecture?

29. A synchronous system uses a common clock for both Tx and Rx. Calculate the operating frequency range for this system if

tf=15ns, ta=500ps, tr=100ps, tu=500ps and no. of bits on the wire during tf is 3.

30. Write the expression for the effective inductance of the package and the maximum tolerable SSN and the number of drivers

between two chips separated by interconnects modelled as transmission line.

31. What are the three places where the decoupling capacitors can be located? Upto what frequencies these capacitors are

effective?

32. What are the major sources of EMI?

33. What are the three parameters which determine the EMI?

34. List any two techniques to minimize EMI

35. Consider an inverter circuit driving a 1 pF capacitive load. Power supply voltage variation should not exceed 10%

36. of Vdd. If 500 such circuit switches binary states in time 20 ns, What will be the effective inductance?

37. Consider a package that has a power supply inductance of 10 pH and has to support the switching of 500 on-chip circuits.

These circuits draw 10 A of current in time 0.25 ns. What is the power supply noise voltage? If this noise voltage has to be

reduced by a factor of 2, what is the value of the decoupling capacitor required?

38. A decoupling capacitor of 0.1F is capable of ensuring the fluctuation in voltage to be 0.25 V when the circuit is to be

charged over a period of 5 nsec. Determine how many 50 Ω lines can be driven by this capacitor. Assume Vdd = 5V.

39. 64 low impedance buffers are switched simultaneously. The line impedance is 50 Ω, rise time 3 nsec, output swing is 5 V. If

the inductance/ line is 1 nH, what would be voltage drop across the inductance due to power/ground connections. If the

effective inductance per pair is 2 nH, how many pairs of power/ground connections should be used to ensure the maximum

fluctuation to be 0.25 V

40. A decoupling capacitor is used to reduce the SSN due to supply and ground path whose total inductance is 10 pH and is

drawing a current of 5 A. If the maximum operating frequency upto which the decoupling capacitor is effective in reducing

the SSN is 600 MHz, find the value of the decoupling capacitance and the magnitude of SSN.

41. Create an equivalent circuit model of a loss-free 50-Ω transmission line 5 in. long for thecross section shown in Figure.

Assume that the driver has a minimum rise time of 2.5ns. Assume a dielectric constant of 4.5.

42. Assume that two components, U1 and U2, need to communicate with each other via a highspeed digital bus. The components

are mounted on a standard four-layer motherboard with the stackup shown in Figure 2.30. The driving buffers on component

U1 have an impedance of 30 Ω, an edge rate of 100 ps, and a swing of 0 to 2 V. The traces on the PCB are required to be 50

Ω and 5 in. long. The relative dielectric constant of the board (εr) is 4.0, the transmission line is assumed to be a perfect

conductor, and the receiver capacitance is small enough to be ignored. Figure depicts the circuit topology

Standard four layer motherboard stackup.

a. Determine the correct cross-sectional geometry of the PCB shown in Figure that will yield an impedance of 50 Ω.

b. Calculate the time it takes for the signal to travel from the driver, U1, to the receiver, U2.

c. Determine the wave shape seen at U2 when the system is driven by U1.

d. Create an equivalent circuit of the system.

43. Assume the two-conductor system shown in Figure, where Zo ≈ 70 Ω, the termination resistors = 70 Ω, V(input) = 1.0 V, Tr

= 100 ps, and X = 2 in. Determine the near- and far-end crosstalk magnitudes assuming the following capacitance and

inductance matrices:

44. Consider the same two-conductor system of Example 3.2. If R1 = 45 and R2 = 100 Ω, what are the respective near- and far-

end crosstalk voltages?

45. From the L and C matrices, Find the Impedance and Phase Velocity for each of the following cases:-

a. Without Crosstalk (isolated case)

b. Even Mode

c. Odd Mode

d. Also, Find the Reflection Co-efficient if Line is matched to an impedance of 65ohms.

46. Assume that a pair of coupled transmission lines is 5 in. long and a digital signal with a rise time of 100 ps is to be simulated.

Given the following inductance and capacitance matrices, calculate the characteristic impedance, the total propagation delay,

the inductive coupling factor, the number of required segments, the maximum delay per segment, and the maximum L, R, C,

G, Cm, and K values for one segment.

47.

48. Assume that two components, U1 and U2, need to communicate with each other via an 8-bitwide high-speed digital bus. The

components are mounted on a standard four-layer motherboard with the stackup shown in Figure 3.20. The driving buffers on

component U1 have an impedance of 30 Ω and a swing of 0 to 2 V. The traces on the printed circuit board (PCB) are

required to be 5 in. long with center-to-center spacing of 15 mils and impedance 50 Ω (ignoring crosstalk). The relative

dielectric constant of the board (εr) is 4.0, the transmission line is assumed to be a perfect conductor, and the receiver

capacitance is small enough to be ignored.

Figure: Cross section of PCB board

The transmission line parasitics are

mutual inductance = 0.54 nH/in.

mutual capacitance = 0.079 pF/in.

self-inductance = 7.13 nH/in. (from the Chapter 2 example)

self-capacitance = 2.85 pF/in. (from the Chapter 2 example)

a. Determine the maximum impedance variation on the transmission lines due to crosstalk.

b. Determine the maximum velocity difference due to crosstalk.

49. Explain how T and Pi terminations may be used to avoid reflections due to both odd and even mode signals.

50. Write the expressions for near end and far end cross talk when the load is (i) matched (ii) unmatched

51. Write the expression for the velocity and impedance corresponding to a bus carrying three signals when (i) all the three

signals are in phase (ii) 1st and 3rd signal are in phase and is out of phase with the middle.

52. Explain a technique to remove a cross talk? What are the disadvantages of this approach

Das könnte Ihnen auch gefallen

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Exp17 Pstest LR v09022017 Chapter 1Dokument30 SeitenExp17 Pstest LR v09022017 Chapter 1Malek MahmoudNoch keine Bewertungen

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Product Sheet: Part NumberDokument2 SeitenProduct Sheet: Part NumberLazar RaresNoch keine Bewertungen

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- PV3500 Series 4-12KW MPPTDokument4 SeitenPV3500 Series 4-12KW MPPTAra AkramNoch keine Bewertungen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Independent Project (Engineering) : Induction Motor Protection From Phase and Overheating Using Atmega MicrocontrollerDokument10 SeitenIndependent Project (Engineering) : Induction Motor Protection From Phase and Overheating Using Atmega MicrocontrollerUmer Ehsan100% (2)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Buildings 2020 Part2 Rozdz7Dokument42 SeitenBuildings 2020 Part2 Rozdz7Andrey KuznetsovNoch keine Bewertungen

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- MS 102 Applied Physics Lecture BreakupDokument1 SeiteMS 102 Applied Physics Lecture BreakupEngr. Babar KhanNoch keine Bewertungen

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- HPM10000 72V Test ResultsDokument2 SeitenHPM10000 72V Test ResultsakseerNoch keine Bewertungen

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- NORMA API-936 - Testeo A MaterialesDokument2 SeitenNORMA API-936 - Testeo A MaterialesSebastián Álcazar25% (4)

- 73 TMSS 01 R0Dokument32 Seiten73 TMSS 01 R0Ibrahim AntarNoch keine Bewertungen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Decibel-Watt (DBW)Dokument6 SeitenDecibel-Watt (DBW)Fetsum LakewNoch keine Bewertungen

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- JNTUH Syllabus 2013 M.Tech EPSDokument23 SeitenJNTUH Syllabus 2013 M.Tech EPSSRINIVASA RAO GANTANoch keine Bewertungen

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- MCGG - 22 32 62 ManualDokument14 SeitenMCGG - 22 32 62 ManualSekarNoch keine Bewertungen

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- CH 25 Practice QuestionsDokument5 SeitenCH 25 Practice QuestionsaliNoch keine Bewertungen

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- DE Midterm ExaminationDokument3 SeitenDE Midterm ExaminationHades Vesarius RiegoNoch keine Bewertungen

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

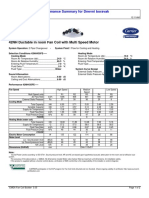

- Performance Summary For Dnevni Boravak: 42NH Ductable in Room Fan Coil With Multi Speed MotorDokument2 SeitenPerformance Summary For Dnevni Boravak: 42NH Ductable in Room Fan Coil With Multi Speed Motorvelikimag87Noch keine Bewertungen

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Capacitance and Inductance Measurements Using An Oscilloscope PDFDokument10 SeitenCapacitance and Inductance Measurements Using An Oscilloscope PDFfernandofsvNoch keine Bewertungen

- Nes 526 PDFDokument4 SeitenNes 526 PDFDIPAKNoch keine Bewertungen

- Assignment #1 - Themro II - Spring 2024Dokument3 SeitenAssignment #1 - Themro II - Spring 2024Mai DweikatNoch keine Bewertungen

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- CapacitorDokument12 SeitenCapacitoryodioioioiNoch keine Bewertungen

- 11 33Dokument102 Seiten11 33Ali BeanNoch keine Bewertungen

- Work Ower EnergyDokument31 SeitenWork Ower EnergyOmprakash Dhaka100% (2)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- Reid Vapour PressureDokument6 SeitenReid Vapour PressureTeal TealyNoch keine Bewertungen

- MS-N - Technical CatalogueDokument44 SeitenMS-N - Technical CatalogueOle BudiNoch keine Bewertungen

- 11 Electrical SafetyDokument30 Seiten11 Electrical SafetyPrakash RaoNoch keine Bewertungen

- AERODYN2 Part 5 Fundamentals of Flight Mechanics For Steady FlightDokument25 SeitenAERODYN2 Part 5 Fundamentals of Flight Mechanics For Steady FlightSecretNoch keine Bewertungen

- Astm C29Dokument4 SeitenAstm C29Amit GabaniNoch keine Bewertungen

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Fundamental Characteristics of Circuit BreakerDokument4 SeitenFundamental Characteristics of Circuit Breakerdejanoski_aNoch keine Bewertungen

- IJTS Naturalconvectionheattransferinsideanopenverticalpipe-InfluenceofLDPrDokument12 SeitenIJTS Naturalconvectionheattransferinsideanopenverticalpipe-InfluenceofLDPrmartin sabusNoch keine Bewertungen

- Chiller Type From ASHRAE 90 1Dokument2 SeitenChiller Type From ASHRAE 90 1Karuna KaranNoch keine Bewertungen

- Module 1 KinematicsDokument34 SeitenModule 1 KinematicsSean Van UmmersenNoch keine Bewertungen

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)