Beruflich Dokumente

Kultur Dokumente

CT2 Asic

Hochgeladen von

skarthikpriya0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

18 Ansichten1 Seitect

Originaltitel

CT2-ASIC

Copyright

© © All Rights Reserved

Verfügbare Formate

DOC, PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenct

Copyright:

© All Rights Reserved

Verfügbare Formate

Als DOC, PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

18 Ansichten1 SeiteCT2 Asic

Hochgeladen von

skarthikpriyact

Copyright:

© All Rights Reserved

Verfügbare Formate

Als DOC, PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 1

Reg. No.

SRM INSTITUTE OF SCIENCE AND TECHNOLOGY

SRM INSTITUTE OF SCIENCE AND TECHNOLOGY CYCLE TEST – I Feb-2019

CYCLE TEST – I Feb-2019 VI Semester – Electronics& Communication Engineering

VI Semester – Electronics& Communication Engineering 15EC327E – ASIC Design

15EC327E – ASIC Design Duration: 45 Mins Max. Marks: 25

Duration: 45 Mins Max. Marks: 25 PART – A (5 X 1 = 5 Marks)

PART – A (5 X 1 = 5 Marks) Answer ALL Questions

Answer ALL Questions

1. Design cost comes under which category

1. Design cost comes under which category a.Variable cost b. Fixed cost c. Low cost d. High cost

a.Variable cost b. Fixed cost c. Low cost d. High cost 2. AOI221 CMOS logic cell has how many transistor

2. AOI221 CMOS logic cell has how many transistor a. 10 b.12 c.14 d.8

a. 10 b.12 c.14 d.8 3. Which design style has the shortest manufacturing lead time

3. Which design style has the shortest manufacturing lead time a.Full custom b. Standard Cell c. Gate array d. FPGA

a.Full custom b. Standard Cell c. Gate array d. FPGA 4. Advantage of PT when compared to TG

4. Advantage of PT when compared to TG a)less no. of Transistor b)Faster c)Easy to design d)passes

a)less no. of Transistor b)Faster c)Easy to design d)passes good 0 & 1

good 0 & 1 5. PMOS acts as ………….device

5. PMOS acts as ………….device a)Pull up b)pull down c)pull back d)pull side

a)Pull up b)pull down c)pull back d)pull side

PART – B (2 X 4 = 8 Marks)

PART – B (2 X 4 = 8 Marks) Answer ANY TWO questions

Answer ANY TWO questions

6. Sketch the schematic of a OAI321 and AOI22 gate.

6. Sketch the schematic of a OAI321 and AOI22 gate. 7. Realize 2:1 MUX and 2 i/p NOR using transmission gate.

7. Realize 2:1 MUX and 2 i/p NOR using transmission gate. 8. Write the steps involved in CMOS fabrication process.

8. Write the steps involved in CMOS fabrication process.

PART – C (1 X 12 = 12 Marks)

PART – C (1 X 12 = 12 Marks) Answer ALL questions

Answer ALL questions

9. a. Explain the various steps involved in ASIC design flow

9. a. Explain the various steps involved in ASIC design flow OR

OR b. Implement sequential logic cells using Transmission gates

b. Implement sequential logic cells using Transmission gates

Reg. No.

Das könnte Ihnen auch gefallen

- CS3CO29-EC-EI3CO07-IT3CO09-OE00005 Digital ElectronicsDokument3 SeitenCS3CO29-EC-EI3CO07-IT3CO09-OE00005 Digital Electronicschouhanraman822Noch keine Bewertungen

- CS 801D PDFDokument4 SeitenCS 801D PDFarnab paulNoch keine Bewertungen

- MST-I or II Paper FormatDokument2 SeitenMST-I or II Paper FormatAnonymous mRCnYKz7xBNoch keine Bewertungen

- Ajay Kumar Garg Engineering College, Ghaziabad: Department of CSEDokument2 SeitenAjay Kumar Garg Engineering College, Ghaziabad: Department of CSEGaurav Singh RawatNoch keine Bewertungen

- WWW - Manaresults.Co - In: II B. Tech I Semester Model Question Paper Oct/Nov - 2017 Switching Theory and Logic DesignDokument4 SeitenWWW - Manaresults.Co - In: II B. Tech I Semester Model Question Paper Oct/Nov - 2017 Switching Theory and Logic Designbadiganti tejakrishnaNoch keine Bewertungen

- Vlsi Model Question Paper 3 (June 2021)Dokument4 SeitenVlsi Model Question Paper 3 (June 2021)PushpalathaNoch keine Bewertungen

- 5228 PDFDokument4 Seiten5228 PDFddNoch keine Bewertungen

- Electronic Design Automation (Ecen 2106) 2020Dokument4 SeitenElectronic Design Automation (Ecen 2106) 2020abhishekkumarjhafbgNoch keine Bewertungen

- Computer Networks (BEG374CO)Dokument1 SeiteComputer Networks (BEG374CO)Subas ShresthaNoch keine Bewertungen

- Btech Cse 8 Sem Vlsi Design 2013Dokument7 SeitenBtech Cse 8 Sem Vlsi Design 2013Samshul Ajam AnsariNoch keine Bewertungen

- CS302 - Analog and DigitalDokument5 SeitenCS302 - Analog and DigitalGaitonde GaneshNoch keine Bewertungen

- B.E. (Computer Science and Engineering) - B' Section B.E. (Computer Science and Engineering) - B' SectionDokument1 SeiteB.E. (Computer Science and Engineering) - B' Section B.E. (Computer Science and Engineering) - B' SectionVishalini ChinnathuraiNoch keine Bewertungen

- Vlsi QP 21,22Dokument11 SeitenVlsi QP 21,22Arunitha ArulnathanNoch keine Bewertungen

- VLSI 設計導論 期末作業: Y AAA BB CCCDokument2 SeitenVLSI 設計導論 期末作業: Y AAA BB CCC陳禹翔Noch keine Bewertungen

- CS 801D PDFDokument4 SeitenCS 801D PDFarnab paulNoch keine Bewertungen

- Digital Electronics - I. Marks: 100 Time: 180 Minutes: 1. A) B) C) D)Dokument8 SeitenDigital Electronics - I. Marks: 100 Time: 180 Minutes: 1. A) B) C) D)Jc R. Poorana ChandranNoch keine Bewertungen

- Acseh0304 (DLD) 2Dokument5 SeitenAcseh0304 (DLD) 2yt608118Noch keine Bewertungen

- Digital Vlsi Design (Ecen 3201) - 2017Dokument2 SeitenDigital Vlsi Design (Ecen 3201) - 2017gaurav kumarNoch keine Bewertungen

- Digital Systems Design: Time Allotted: 3 Hrs Full Marks: 70Dokument4 SeitenDigital Systems Design: Time Allotted: 3 Hrs Full Marks: 70Vikash KumarNoch keine Bewertungen

- Vlsi Model Question Paper 1 (June 2021)Dokument3 SeitenVlsi Model Question Paper 1 (June 2021)PushpalathaNoch keine Bewertungen

- Vlsi Model Question Paper 2 (June 2021)Dokument3 SeitenVlsi Model Question Paper 2 (June 2021)PushpalathaNoch keine Bewertungen

- 2011 Advanced Computer Architecture: CS/B.TECH (CSE) /SEM-4/CS-403/2011Dokument7 Seiten2011 Advanced Computer Architecture: CS/B.TECH (CSE) /SEM-4/CS-403/2011Avik MitraNoch keine Bewertungen

- Ece Question PapaerDokument4 SeitenEce Question PapaerAbhinavRahaNoch keine Bewertungen

- CG Paper PUT - SECTION ADokument2 SeitenCG Paper PUT - SECTION Akundan kumarNoch keine Bewertungen

- 9V To 22V: Level Translator Output DriverDokument2 Seiten9V To 22V: Level Translator Output DriverMutharasu SNoch keine Bewertungen

- Greedy Method ApproachDokument8 SeitenGreedy Method ApproachBhavin VaghelaNoch keine Bewertungen

- HMK 4 ARCDokument3 SeitenHMK 4 ARCskeletorfearsmeNoch keine Bewertungen

- JUNE 2013: Code: AE74 Subject: VLSI DESIGNDokument3 SeitenJUNE 2013: Code: AE74 Subject: VLSI DESIGNMahadevNoch keine Bewertungen

- Midterm 11 So LsDokument7 SeitenMidterm 11 So LsMohamedNoch keine Bewertungen

- In A Logic Circuit A Hazard Is Independent FormDokument11 SeitenIn A Logic Circuit A Hazard Is Independent Formwin papasanNoch keine Bewertungen

- Design and Analysis of Algorithms (Cse-It) - May-2014Dokument5 SeitenDesign and Analysis of Algorithms (Cse-It) - May-2014Nagababu PachhalaNoch keine Bewertungen

- OU - 1607 OU - 1607: FACULTY OF EngineeringDokument15 SeitenOU - 1607 OU - 1607: FACULTY OF EngineeringSrikanth RenikuntaNoch keine Bewertungen

- C H1074 Pages: 2: Answer Any Two Full Questions, Each Carries 15 MarksDokument2 SeitenC H1074 Pages: 2: Answer Any Two Full Questions, Each Carries 15 MarksDeepak KumarNoch keine Bewertungen

- 08ab303 - Digital Logic CircuitsDokument3 Seiten08ab303 - Digital Logic CircuitsChandru RamaswamyNoch keine Bewertungen

- Kec 302 Digital System DesignDokument2 SeitenKec 302 Digital System DesignAditya KasaudhanNoch keine Bewertungen

- Exit Exam Mode1 ECE ComputerDokument54 SeitenExit Exam Mode1 ECE ComputerBerentoNoch keine Bewertungen

- Cat1 3 It W 2021 22Dokument2 SeitenCat1 3 It W 2021 22Rutvik BucheNoch keine Bewertungen

- Switching Theory and Logic Design Oct-Nov 2020Dokument2 SeitenSwitching Theory and Logic Design Oct-Nov 2020VEMANA DHANESHNoch keine Bewertungen

- EC2354 - Nov 2011 - AU QP Anna University Exams - VLSIDokument3 SeitenEC2354 - Nov 2011 - AU QP Anna University Exams - VLSISHARANYANoch keine Bewertungen

- University Question Papers - VLSIDokument26 SeitenUniversity Question Papers - VLSIVijayNoch keine Bewertungen

- 2011 Eda For Vlsi Design: CS/B.TECH (ECE) (Separate Supple) /SEM-7/EC-702/2011Dokument7 Seiten2011 Eda For Vlsi Design: CS/B.TECH (ECE) (Separate Supple) /SEM-7/EC-702/2011John CaterNoch keine Bewertungen

- KTUweb - CS 352may19 PDFDokument8 SeitenKTUweb - CS 352may19 PDFRekha V RNoch keine Bewertungen

- Ec209 - FinalDokument3 SeitenEc209 - FinalthegreatarshiyaNoch keine Bewertungen

- Btech Cse 4 Sem Advance Computer Architecture 2012Dokument7 SeitenBtech Cse 4 Sem Advance Computer Architecture 2012souravnaskar12578954Noch keine Bewertungen

- Gate Sample PaperDokument7 SeitenGate Sample Papershettyashwin19Noch keine Bewertungen

- SLR-PK - 278: SLRPK278Dokument4 SeitenSLR-PK - 278: SLRPK278Mayur HanchateNoch keine Bewertungen

- EdaDokument4 SeitenEdaJyotirmoy GuhaNoch keine Bewertungen

- Guessing Papers 1-2-12th Electronics Sub Code C2Dokument6 SeitenGuessing Papers 1-2-12th Electronics Sub Code C2snigdhagulhane0922Noch keine Bewertungen

- Mock Test Day-1Dokument5 SeitenMock Test Day-1sweta sharmaNoch keine Bewertungen

- QuestionsdsaDokument26 SeitenQuestionsdsaSiddharth SharmaNoch keine Bewertungen

- Bca 101Dokument4 SeitenBca 101Avirup ShomeNoch keine Bewertungen

- Vlsi Question PapersDokument1 SeiteVlsi Question PapersjahnaviNoch keine Bewertungen

- VLSI DESIGN Bit PaperDokument2 SeitenVLSI DESIGN Bit Papervenkiscribd444Noch keine Bewertungen

- Information TechnologyDokument7 SeitenInformation TechnologyDEVANAND ANoch keine Bewertungen

- Apio 2008Dokument9 SeitenApio 2008Adam Muhammad SyachNoch keine Bewertungen

- Comp SC 18Dokument8 SeitenComp SC 18Masiur RahamanNoch keine Bewertungen

- Digital Electronic & Fundamentals of Microprocessor: B.E. Third Semester (Information Technology) (C.B.S.)Dokument2 SeitenDigital Electronic & Fundamentals of Microprocessor: B.E. Third Semester (Information Technology) (C.B.S.)Hamit BisaneNoch keine Bewertungen

- 1 Semester Model Question PapersDokument17 Seiten1 Semester Model Question PapersBalaji MohantyNoch keine Bewertungen

- De 5Dokument2 SeitenDe 5PADMANABAN SNoch keine Bewertungen

- Instructors: Dr. Phillip JonesDokument44 SeitenInstructors: Dr. Phillip JonesskarthikpriyaNoch keine Bewertungen

- Cla1 - EhosDokument4 SeitenCla1 - EhosskarthikpriyaNoch keine Bewertungen

- Conference ContentDokument2 SeitenConference ContentskarthikpriyaNoch keine Bewertungen

- MPC University LAB QuestionsDokument4 SeitenMPC University LAB QuestionsskarthikpriyaNoch keine Bewertungen

- SRM Institute of Science & Technology - Academic Curricula (2019 Part Time Regulations) 37Dokument2 SeitenSRM Institute of Science & Technology - Academic Curricula (2019 Part Time Regulations) 37skarthikpriyaNoch keine Bewertungen

- NBA QP FORMAT - Cycle Test 01 - III Yr - EHOSDokument6 SeitenNBA QP FORMAT - Cycle Test 01 - III Yr - EHOSskarthikpriyaNoch keine Bewertungen

- Cpre 288 - Introduction To Embedded Systems: Instructors: Dr. Phillip JonesDokument89 SeitenCpre 288 - Introduction To Embedded Systems: Instructors: Dr. Phillip JonesskarthikpriyaNoch keine Bewertungen

- Short Channel Effects and ScalingDokument23 SeitenShort Channel Effects and ScalingskarthikpriyaNoch keine Bewertungen

- Conference ContentDokument2 SeitenConference ContentskarthikpriyaNoch keine Bewertungen

- The Interntional Womens Day 1Dokument1 SeiteThe Interntional Womens Day 1Karthik SekharNoch keine Bewertungen

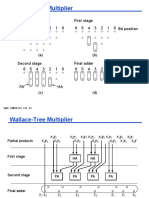

- Wallace-Tree Multiplier: 6 5 4 3 2 1 0 6 5 4 3 2 1 0 Partial Products First Stage Bit PositionDokument2 SeitenWallace-Tree Multiplier: 6 5 4 3 2 1 0 6 5 4 3 2 1 0 Partial Products First Stage Bit PositionskarthikpriyaNoch keine Bewertungen

- Water 1Dokument1 SeiteWater 1skarthikpriyaNoch keine Bewertungen

- Short Channel Effects and ScalingDokument23 SeitenShort Channel Effects and ScalingskarthikpriyaNoch keine Bewertungen

- 18CSC202J Set1Dokument1 Seite18CSC202J Set1skarthikpriyaNoch keine Bewertungen

- Display 090920122425 Phpapp01 PDFDokument37 SeitenDisplay 090920122425 Phpapp01 PDFNihar PandaNoch keine Bewertungen

- Verilog Quiz1Dokument2 SeitenVerilog Quiz1skarthikpriyaNoch keine Bewertungen

- 18CSC202J Set1 Even Reg NoDokument1 Seite18CSC202J Set1 Even Reg NoskarthikpriyaNoch keine Bewertungen

- 18CSC202J Set2 ODD Reg NoDokument1 Seite18CSC202J Set2 ODD Reg NoskarthikpriyaNoch keine Bewertungen

- M.E CSE Curriculum and Syllabus PDFDokument99 SeitenM.E CSE Curriculum and Syllabus PDFskarthikpriyaNoch keine Bewertungen

- 18CSC202J Set2Dokument1 Seite18CSC202J Set2skarthikpriyaNoch keine Bewertungen

- 8251 Material PDFDokument31 Seiten8251 Material PDFskarthikpriyaNoch keine Bewertungen

- UML - Deployment Diagrams - Tutorialspoint PDFDokument3 SeitenUML - Deployment Diagrams - Tutorialspoint PDFskarthikpriyaNoch keine Bewertungen

- M.E CSE Curriculum and Syllabus PDFDokument99 SeitenM.E CSE Curriculum and Syllabus PDFskarthikpriyaNoch keine Bewertungen

- UML - Component Diagrams - Tutorialspoint PDFDokument3 SeitenUML - Component Diagrams - Tutorialspoint PDFskarthikpriyaNoch keine Bewertungen

- 8251 Material PDFDokument31 Seiten8251 Material PDFskarthikpriyaNoch keine Bewertungen

- CDC Question TemplateDokument4 SeitenCDC Question TemplateskarthikpriyaNoch keine Bewertungen

- UML - Component Diagrams - Tutorialspoint PDFDokument3 SeitenUML - Component Diagrams - Tutorialspoint PDFskarthikpriyaNoch keine Bewertungen

- Display 090920122425 Phpapp01 PDFDokument37 SeitenDisplay 090920122425 Phpapp01 PDFNihar PandaNoch keine Bewertungen

- SCS1202 - Object Oriented Programming Unit 2 Classes and ObjectsDokument17 SeitenSCS1202 - Object Oriented Programming Unit 2 Classes and ObjectsakjissNoch keine Bewertungen

- Xilinx SDKDokument11 SeitenXilinx SDKskarthikpriyaNoch keine Bewertungen

- TILE-Gx8072 ProcessorDokument2 SeitenTILE-Gx8072 Processorraees74Noch keine Bewertungen

- Agile Maturity ModelDokument27 SeitenAgile Maturity ModelfredcyrilNoch keine Bewertungen

- Integration of User Experience (UX), Customer Experience (CX) and Brand Experience (BX) With B2B and B2C ModelsDokument11 SeitenIntegration of User Experience (UX), Customer Experience (CX) and Brand Experience (BX) With B2B and B2C ModelsRashi DesaiNoch keine Bewertungen

- Smartengine 0521 LowDokument17 SeitenSmartengine 0521 Lowatif_aman123Noch keine Bewertungen

- AE111-IT Application Tools in Business 2021Dokument20 SeitenAE111-IT Application Tools in Business 2021PANELA, Jericho F.Noch keine Bewertungen

- Unit 3: Combinational Circuit DesignDokument30 SeitenUnit 3: Combinational Circuit DesignKarn AroraNoch keine Bewertungen

- IPSecDokument25 SeitenIPSecDinesh ParasharNoch keine Bewertungen

- Market Basket Analysis Using Improved FP-treeDokument4 SeitenMarket Basket Analysis Using Improved FP-treeIIR indiaNoch keine Bewertungen

- Sorting and SearchDokument27 SeitenSorting and SearchPawan KumarNoch keine Bewertungen

- ALC1024 v2-05 UsersGuideDokument105 SeitenALC1024 v2-05 UsersGuideEinmerckNoch keine Bewertungen

- Dlmcssesp01 Course BookDokument148 SeitenDlmcssesp01 Course BookAhmet Hayri KınacılarNoch keine Bewertungen

- ResumeDokument1 SeiteResumeUladzislau SazanovichNoch keine Bewertungen

- Medical Appointment Booking SystemDokument7 SeitenMedical Appointment Booking Systemsegun67% (3)

- Computational Science - ICCS 2023Dokument751 SeitenComputational Science - ICCS 2023Vehpi YILDIRIMNoch keine Bewertungen

- 02-Steps To Analyze AWR Report in OracleDokument8 Seiten02-Steps To Analyze AWR Report in OracleAnonymous 8RhRm6Eo7hNoch keine Bewertungen

- Wearable ComputerDokument9 SeitenWearable Computerhowida nafaaNoch keine Bewertungen

- Satellite - Client Configuration GuideDokument40 SeitenSatellite - Client Configuration Guideseafish666666Noch keine Bewertungen

- Tle CSS9 Q2 M1Dokument15 SeitenTle CSS9 Q2 M1yvon maccella fernandoNoch keine Bewertungen

- AC126 - 6B - Below 60% Parts Report - 13.04.2023Dokument3 SeitenAC126 - 6B - Below 60% Parts Report - 13.04.2023sivasakthiNoch keine Bewertungen

- Opposition Report To "Cloud Based Payroll Management System"Dokument3 SeitenOpposition Report To "Cloud Based Payroll Management System"bekirm1Noch keine Bewertungen

- Compactlogix P1Dokument20 SeitenCompactlogix P1eumetallicaNoch keine Bewertungen

- 1Z0-066 Dumps - Oracle Database ExamDokument8 Seiten1Z0-066 Dumps - Oracle Database ExamThomas WilliamNoch keine Bewertungen

- HCIA-WLAN V2.0 Training PDFDokument24 SeitenHCIA-WLAN V2.0 Training PDFandreu cerdan50% (2)

- Um Qs en PC Worx Express 7632 en 02Dokument108 SeitenUm Qs en PC Worx Express 7632 en 02Benjamin AlarconNoch keine Bewertungen

- Pardot SpecialistDokument7 SeitenPardot SpecialistrajNoch keine Bewertungen

- Network CablesDokument16 SeitenNetwork CablesQueen It isNoch keine Bewertungen

- Space Invaders TutorialDokument38 SeitenSpace Invaders TutorialcitisoloNoch keine Bewertungen

- School of Information Technology & Engineering Digital Assignment I SWE 3002: Information System Security Team-4Dokument19 SeitenSchool of Information Technology & Engineering Digital Assignment I SWE 3002: Information System Security Team-4Shivareddy 1922Noch keine Bewertungen

- BRKCCT 2007Dokument71 SeitenBRKCCT 2007IVAN CASTAÑEDA MARQUEZNoch keine Bewertungen

- p424 KowalskiDokument13 Seitenp424 KowalskiMaya Ria AgustinNoch keine Bewertungen