Beruflich Dokumente

Kultur Dokumente

Average Current Mode Control in Power Electronic Converters - Analog

Hochgeladen von

Satya NV0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

376 Ansichten5 SeitenAverage Current Mode Control (ACMC) is a general purpose, highperformance all-round control method for power electronic converters. It uses a high gain, wide bandwidth Current Error Amplifier (CEA) to force the average of one current within the converter, typically the inductor current, to follow the demanded current reference with very small error. A hybrid analog-digital control implementation of ACMC is proposed.

Originalbeschreibung:

Originaltitel

AVERAGE CURRENT MODE CONTROL IN POWER ELECTRONIC CONVERTERS – ANALOG

Copyright

© Attribution Non-Commercial (BY-NC)

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenAverage Current Mode Control (ACMC) is a general purpose, highperformance all-round control method for power electronic converters. It uses a high gain, wide bandwidth Current Error Amplifier (CEA) to force the average of one current within the converter, typically the inductor current, to follow the demanded current reference with very small error. A hybrid analog-digital control implementation of ACMC is proposed.

Copyright:

Attribution Non-Commercial (BY-NC)

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

376 Ansichten5 SeitenAverage Current Mode Control in Power Electronic Converters - Analog

Hochgeladen von

Satya NVAverage Current Mode Control (ACMC) is a general purpose, highperformance all-round control method for power electronic converters. It uses a high gain, wide bandwidth Current Error Amplifier (CEA) to force the average of one current within the converter, typically the inductor current, to follow the demanded current reference with very small error. A hybrid analog-digital control implementation of ACMC is proposed.

Copyright:

Attribution Non-Commercial (BY-NC)

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 5

AVERAGE CURRENT MODE CONTROL IN POWER ELECTRONIC CONVERTERS – ANALOG

VERSUS DIGITAL

K. D. Purton * and R. P. Lisner**

*Department of Electrical and Computer System Engineering, Monash University, Australia,

and Switch Mode Power Conversion P/L, Melbourne, Australia

**Department of Electrical and Computer System Engineering,

Monash University, Australia

Abstract

This paper presents Average Current Mode Control (ACMC) as a general purpose, high-

performance all-round control method for AC-DC conversion, DC-DC conversion, and DC-

AC conversion (including grid-feed inverters). A detailed examination of the typical analog

circuit implementation and waveforms, based on simulations and experimental results, is used

to explain how ACMC achieves superior performance. Several reported digital

implementations are critically examined. Finally a hybrid analog-digital control

implementation of ACMC is proposed.

1. INTRODUCTION “PWM Conductance Control” appears to be the first to

Average Current Mode Control (ACMC) is typically a use the output of an “integrator-zero” compensated

two loop control method (inner loop, current; outer CEA and a linear ramp as inputs to the PWM

loop, voltage) for power electronic converters. Many comparator. This approach was developed

of these applications have been in the higher switching commercially by Unitrode [4].

frequency, lower power segment (up to 10kW, at The usual implementation of ACMC relies on analog

20kHz and above), but this is changing. A 30kW three operational amplifiers as error amplifiers, and makes

phase inverter using analog ACMC has been reported use of wide-band sensing of the inductor current, to

[1]. The main distinguishing feature of ACMC, as include both the AC and DC components. Figure 1

compared with peak current mode control, is that shows a basic buck converter with synchronous

ACMC uses a high gain, wide bandwidth Current rectification. The voltage waveform representing the

Error Amplifier (CEA) to force the average of one inductor current is connected to one input of the CEA

current within the converter, typically the inductor with large gain at DC and low frequencies to force the

current, to follow the demanded current reference with average value of the inductor current to follow the

very small error, as a controlled current source. current reference, which is connected to the other

Advantages of ACMC include large noise margin, no input.

requirement for additional slope compensation, easy

current limit implementation, excellent voltage and

current regulation, simple compensation, good

behaviour in both continuous and discontinuous

inductor current modes, and has inherent Vin and Vout

feed-forward properties. All this is achieved with only

a slight increase in complexity over earlier schemes.

2. PRINCIPLES OF OPERATION

An early paper on average current control was

published by Papathomas and Giacopelli of Bell Labs

in 1979 [2]. This used digital hardware (no computer)

rather than analog hardware. A current controlled

oscillator clocked a counter and when this count

(proportional to the inductor average current) matched

a current reference count, the switch was turned off. A

more conventional analog approach was reported by Figure 1. Simplified schematic of buck converter

O’Sullivan et al of the European Space Centre in 1988 with synchronous rectifier and average current

[3], in which the authors claimed to have been using mode control regulating output voltage.

this scheme for the previous decade. Their so-called

Figure 2 shows real waveforms in a low power test

circuit. Fig. 2 (a) shows regulation of the average

inductor current (Iout) at 0.5A, Fig. 2 (b) at 1.0A, and

Fig. 2 (c) at 1.5A. The CEA output is an inverted and

amplified version of the difference between the

inductor current and the current reference signal, with

a positive DC offset. This CEA output is then

compared with a large amplitude ramp waveform at

the converter switching frequency, at the inputs to a

Pulse Width Modulation (PWM) comparator. These

sawtooth waveforms intersect at two points in each

cycle, defining the rise and fall instants of the PWM

pulse train to the switches. If the reference input to the

CEA is the output of a suitably compensated voltage

Error Amplifier (VEA), the average inductor current

will be controlled to force the converter output voltage Figure 2 (b). Oscilloscope printout of

to track the voltage reference. If the CEA reference is experimental buck converter with ACMC.

a half-sine waveform, the average inductor current Duty cycle is around 50%, and Iout is around

will track this, eg, to force a sinusoidal current into the 1A. Note that inductor current (bottom trace)

power grid via an unfolding bridge.

minimum is zero, not negative, under these

The comparison of the wide band inductor current conditions.

waveform with the PWM ramp waveform results in an

inherent fast feed-forward of input and output voltage

changes, without involving the feedback loops and

without direct monitoring. Since the up-slope and

down-slope of the inductor current waveform are

proportional to the input and output voltages, any

change in these slopes results in immediate adjustment

of PWM duty cycle. Clamping the CEA reference

input limits the converter inductor current. This is

often the output current and so an adjustable output

current limit is easily implemented.

Figure 2 (c). Oscilloscope printout of

experimental buck converter with ACMC.

Duty cycle is around 75%, and Iout is around

1.5A. Note that inductor current (bottom trace)

minimum is positive under these conditions.

Compensation of the CEA is based upon high gain at

Figure 2 (a). Oscilloscope printout of DC and low frequencies. This is what forces the

experimental buck converter with ACMC. average of the controlled current, typically the

Large sawtooth is switching frequency ramp inductor current, to track the current reference. This

input to PWM comparator. Smaller sawtooth integrator function is implemented by R1 and C1 in

is CEA output to other input of PWM Fig. 1. At the zero frequency, determined by C1 and

comparator. Middle trace is PWM output to R2, the CEA gain is levelled off and a phase boost

main switch. Duty cycle is around 25%, Iout is back towards zero degrees of lag, from the constant 90

around 0.5A. Bottom trace is the buck inductor degrees of phase lag from the integrator, results. The

current waveform. Note that under these actual flat gain above the zero frequency is determined by

running conditions with a synchronous R2/R1. A higher frequency pole (C2, R2) rolls off the

rectifier, inductor current is actually negative gain near the switching frequency. The Bode plot of

for part of the switching cycle. such a compensator is shown in Fig. 3.

The less commonly listed disadvantages of digital

control include:

• software development is tedious, error-prone, and

time consuming, and hence expensive

• microcomputers and DSPs suffer from noise

interference, and generate large amounts of

noise − they rely on good layout, bypassing,

shielding, ground-plane techniques, etc as do

analog systems

• sampling and quantisation result in steps in time

Figure 3. Bode plot of a typical compensated and amplitude, which degrade accuracy and

analog ACMC current error amplifier. The performance

magnitude response (3 straight line segments)

• the hoped-for component reduction due to large-

shows the low frequency high gain roll-off of

scale integration is usually lost in the number of

the integrator component, the mid-band

constant gain after the zero component, and support ICs (many of which are analog) and

the high frequency roll-off due to the second discrete components

pole. The phase response (inverted bathtub • due to the clocked, serial nature of digital

shape) shows the phase boost improving the computers, everything they do takes time. Simply

phase margin. put, the more complex the task, the longer it

(Vertical: -20dB → +60db and 0° → +180°, takes. This time delay results in phase lag, which

horizontal: 1 Hz → 1 MHz) detracts from performance.

3. ANALOG CONTROL VERSUS Digital controllers are typically mixed-mode

DIGITAL CONTROL controllers. The real world is analog, and must be

processed by analog circuitry before being digitally

Analog control processed. Amplifiers, summers, buffers, level-

shifters, precision rectifiers, anti-aliasing filters,

The commonly listed advantages of analog control voltage references, sample and holds, analog to digital

include: converters, digital to analog converters, final filters,

• relative simplicity etc typically require op-amps. A digital

• lower cost implementation of ACMC may require more analog

• wider bandwidth circuitry than would an analog implementation, yet

• small delay between cause and effect can result in lesser performance with a much higher

cost. The component cost of an analog

• finer resolution of time and amplitude

implementation, involving a few op-amps, a

The commonly listed disadvantages include: comparator, a 555 timer, CMOS logic, and some

• a fixed and relatively simple functionality resistors and capacitors, may be no more than,

say, $US1.50 in quantity manufacture. The

• susceptibility to noise, ageing and drift development time may be a few days. Compare this to

• a large number of components. a digital implementation. The hardware cost will be

considerably more, coupled with the added software

Digital control

cost. The overall cost will be many times more, and

The commonly listed advantages of digital control the performance worse.

include:

Accuracy, reliability, repeatability, and freedom from

• programmability

ageing and drift are not necessarily intrinsic to digital

• the possibility of intelligent, adaptive, linear or controllers, nor absent from analog controllers.

non-linear control Analog controllers depend on resistors and capacitors

• the possibility of self-calibration and self- in feedback networks to set gains and frequency

diagnosis etc response. Components of adequate specification with

• accuracy, reliability, repeatability tight tolerance, low drift, and a small temperature

• ability to communicate with other systems coefficient are available. Digital controllers generally

• no ageing or drift require a lot of analog support circuitry which, in turn,

must be adequate for the task (and typically is).

• large noise margins.

While typical analog circuitry cannot compete with switching period delays between parameter

the possible intelligence and adaptability of control measurement and control response by extrapolating to

using a digital computer, non-linear analog control a future response from past measurements. While this

can be very practical and cost effective. For example, predicting of the future based on past trends may be

consider the non-linear functions within a Unitrode helpful if things keep going the way they have been,

UC3854 analog power factor controller IC: like some weather forecasting approaches; such a

multiplication, squaring, and division. A very fast scheme cannot compete with a fast analog controller

fuzzy logic controller, with complex non-linear when the unexpected occurs.

properties, can be built from analog components.

4. INVERTER CONTROL INCORPORATING

There are many digital controllers doing good work

GAIN SCHEDULING

now in industry, for example in variable speed,

variable voltage AC induction motor drives. When a PWM inverter is synthesizing an AC

Computers, ranging from single chip microcontrollers waveform from a relatively constant DC input, the

to advanced DSP processors, are being used by the duty cycle is adjusted from near zero at the zero

thousands. Upon closer examination, it appears that crossings, to near maximum at the peaks. Depending

these devices are not primarily being used as fast, on the topology of the power converter chosen, this

precise compensators for good transient response, but variation will alter the controller compensation

rather as versatile, flexible, adaptive system requirements to a greater or lesser extent. One of the

supervisors. For example, generation of three-phase most difficult to optimise is the buck-boost, or flyback

PWM with variable amplitude, variable frequency, is DC-DC converter, used with an unfolding stage.

readily done with one powerful CPU. It can also be Schlecht [8] reported the use of time varying feedback

done well with analog ICs and discrete components. gains to counteract the 120Hz time dependant

However, using a microcontroller to do this is more in response of the flyback topology when used in an

the role of a modulator rather than a compensator. A inverter. The result was closed loop poles that

digital PID control function is usually tacked on, to remained stationary, making possible sharper cusps in

avoid using more external circuitry. the half-sine waveforms and so reduced distortion in

the current waveform.

Digital computer implementations of ACMC have

been reported. Some of these have relied on a brute

force sampled version of the analog approach. In [5], Buck derived converters are more common at higher

Holme and Manning reported a digital ACMC power levels than buck-boost types, and less

scheme. A powerful DSP processor, combined with a demanding to control. Even so, the control-to-output

very fast ADC and a digital hardware PWM module, transfer function varies with duty cycle [9] and

sampled the inductor current many times per improved inverter control can result from time varying

switching period to locate the peak value. The current compensation, as opposed to fixed parameters.

samples, along with samples of Vin and Vout were

processed to force the average inductor current to

track a reference. However, this takes time, and a two- 5. HYBRID ANALOG – DIGITAL ACMC

switching-period delay resulted between sampling and One approach to optimising performance and cost is to

PWM adjustment. This sampling/processing time combine both analog and digital techniques as

delay translates to a considerable phase lag, which appropriate. The authors are investigating a hybrid

greatly complicated stability issues. Of even more ACMC scheme for grid-feed inverters based on a fast

concern is the unmentioned orders of magnitude analog core for optimum tracking and regulation,

increase in cost and complexity of this digital copy combined with an economic micro-controller. The

over the analog approach, to achieve an inferior result. primary task of the latter is to generate the required

If the digital approach resulted in some worthwhile reference, and to adjust gains and corner frequencies

improvement, then a cost-benefit analysis may justify by digitally controlled resistances, according to

it. monitored conditions, such as the operating point

within the AC waveform at the time, and the nature of

Other forms of digital current mode control have been the load. Such adaptive-gain-scheduling non-linear

proposed, such as the predictive approach; for control is able to improve on both the pure analog and

example, those by Holmes and Martin [6], and Gow pure digital control schemes, with minimum cost.

and Manning [7]. These aim to compensate for multi-

An example of time varying gains is shown in 7. REFERENCES

figure 4. The CEA gain is increased near the zero [1] Fraser, M. E., and Manning, C. D, “Performance

crossings to improve the tracking of the average of Average Current Mode Controlled PWM

inductor current, forcing it to more closely follow the Inverter with High Crest Factor Load”, Power

sinusoidal reference, and so reducing cross-over Electronics and Variable Speed Drives, 26-28

distortion. The slightly fuzzy trace is Vout, the smooth October 1994, Conference Publication No. 399,

IEE, pp. 661-666.

trace is the sinusoidal reference. Maintaining this

higher gain throughout the entire half cycle would [2] Papathomas, T. V., and Giacopelli, J. N., “Digital

result in sub-harmonic oscillation near the peaks, and Implementation of an Average Current Controlled

greater distortion. For illustration, only one step in the Switching Regulator”, IEEE PESC, 1979, pp.

CEA gain is shown, for better results more steps are 155-161.

used.

[3] O’Sullivan, D., Spruyt, H., and Crausaz, A.,

“PWM Conductance Control”, IEEE PESC, 1988,

pp.351-359.

[4] Dixon, L. H., “Average Current Mode Control of

Switching Power Supplies”, Unitrode Power

Supply Design Seminar SEM-700, 1990,

pp. 5-1 to 5-14.

[5] Holme, P. R., and Manning, C. D., “Digital

Control of High Frequency PWM Converters”,

EPE Proceedings, Brighton, 1993, pp. 260-265.

Figure 4. Sinusoidal output voltage waveform

(50Hz) of an inverter with ACMC. Region

shown is each side of the zero crossing. The [6] Holmes, D. G., and Martin, D. A.,

smooth line is the sinusoidal reference. The “Implementation of a Direct Digital Predictive

Current Controller for Single and Three Phase

fuzzy line is the actual Vout waveform. The

Voltage Source Inverters”, IEEE IAS Meeting,

switched increase in the CEA gain near the

1996, pp. 906-913.

zero crossing has reduced the crossover

distortion. Vout now more closely tracks the

reference in this region. [7] Gow, J. A., and Manning, C. D., “Novel Fast-

Acting Predictive Current Mode Controller for

(Vertical: -10V → +10V, Power Electronic Converters”, IEE Proc.-Electr.

horizontal: 4.0 msec → 16.0 msec, Power Applications, Vol. 148, No. 2,

zero-crossing at 10.0 msec) March 2001, pp. 133-139.

6. CONCLUSIONS

[8] Schlecht, M. F., “Time-varying Feedback Gains

Analog ACMC is superior to digital current mode for Power Circuits with Active Waveshaping”,

control from the two important considerations of IEEE PESC, 1981, pp. 52-59.

speed of response and cost. The system advantages of

digital computers can be combined with the above

advantages of analog ACMC by creating a hybrid of [9] Cooke, P., “Modelling Average Current Mode

the two, producing a result which is greater than the Control”, IEEE APEC, 2000, pp. 256-262.

sum of the individual parts.

Das könnte Ihnen auch gefallen

- Variable Speed AC Drives with Inverter Output FiltersVon EverandVariable Speed AC Drives with Inverter Output FiltersNoch keine Bewertungen

- Power Electronics IntroductionDokument18 SeitenPower Electronics Introductionsagar378Noch keine Bewertungen

- 9A02304 Basic Electrical & Electronics EngineeringDokument8 Seiten9A02304 Basic Electrical & Electronics EngineeringsivabharathamurthyNoch keine Bewertungen

- Vector ScopeDokument3 SeitenVector ScopeAhLevChaNoch keine Bewertungen

- All Classroom Class ExamplesDokument51 SeitenAll Classroom Class ExamplesAhmed Sabri0% (1)

- DC - Ac Inv.Dokument82 SeitenDC - Ac Inv.Jegadeeswari GNoch keine Bewertungen

- Effect of Source Inductance in 3Ø Full WaveDokument12 SeitenEffect of Source Inductance in 3Ø Full WaveUmashankar Subramaniam100% (1)

- Scilab - Power Electronics Devices, Circuits and Application - Muhammad. H. RashidDokument241 SeitenScilab - Power Electronics Devices, Circuits and Application - Muhammad. H. RashidMoyses Naves de MoraesNoch keine Bewertungen

- BEE Assignment Even 2020Dokument5 SeitenBEE Assignment Even 2020Aditya PatelNoch keine Bewertungen

- Questions 1Dokument11 SeitenQuestions 1anvithaNoch keine Bewertungen

- 3 Line ConverterDokument10 Seiten3 Line ConverterJay Romar PabianiaNoch keine Bewertungen

- ELEG312+Homework+ 6+solutionsDokument16 SeitenELEG312+Homework+ 6+solutionsMạnh TuấnNoch keine Bewertungen

- DC Link CurrentDokument8 SeitenDC Link CurrentsubbannaNoch keine Bewertungen

- RGPV Syllabus Btech Ee 5 Sem All SubjectsDokument17 SeitenRGPV Syllabus Btech Ee 5 Sem All SubjectsSandeep TaleNoch keine Bewertungen

- Chapter 7 of Fundamentals of MicroelectronicsDokument33 SeitenChapter 7 of Fundamentals of MicroelectronicsjenellaneNoch keine Bewertungen

- CBPSD-lab Manual PDFDokument40 SeitenCBPSD-lab Manual PDFShiv Rajput80% (10)

- 5 BJT e PDFDokument78 Seiten5 BJT e PDFSebastian LMNoch keine Bewertungen

- Load Flow Matrices IIT Roorkee Notes NPTELDokument88 SeitenLoad Flow Matrices IIT Roorkee Notes NPTELconsultrail100% (1)

- Single Line Power Network Diagram-KashmirDokument1 SeiteSingle Line Power Network Diagram-KashmirMirza Abdul WarisNoch keine Bewertungen

- 12V To 120V DC - DC Converter Using Power Electronics For Higher Efficiency and Reliable OperationDokument23 Seiten12V To 120V DC - DC Converter Using Power Electronics For Higher Efficiency and Reliable OperationRaghav ChawlaNoch keine Bewertungen

- Electri Circuits Lab Manual 1Dokument11 SeitenElectri Circuits Lab Manual 1Sri RoNoch keine Bewertungen

- Lab Report On ECE 210 Lab1Dokument6 SeitenLab Report On ECE 210 Lab1Joanne Lai100% (1)

- "Bridge B2HZ" For The Control of A DC MotorDokument16 Seiten"Bridge B2HZ" For The Control of A DC MotorhadiNoch keine Bewertungen

- Chapter9 Braking DCDokument43 SeitenChapter9 Braking DCFrozenTuxNoch keine Bewertungen

- Simulation of Switching ConvertersDokument103 SeitenSimulation of Switching ConvertersAshok KumarNoch keine Bewertungen

- 1 Boost - Design (Assign 1)Dokument1 Seite1 Boost - Design (Assign 1)deivasigamaniNoch keine Bewertungen

- Electrical Drives Ans ControlsDokument40 SeitenElectrical Drives Ans Controlsjeyasaravanan77Noch keine Bewertungen

- Class Test - 22423Dokument6 SeitenClass Test - 22423Samadhan ThokalNoch keine Bewertungen

- ELG3311: Solutions For Assignment 1: Problem 2-6Dokument14 SeitenELG3311: Solutions For Assignment 1: Problem 2-6tesfayregs gebretsadik100% (1)

- Reference Frame Theory PDFDokument42 SeitenReference Frame Theory PDFSubaragavanNoch keine Bewertungen

- 8049Dokument239 Seiten8049adnantanNoch keine Bewertungen

- Chapter 8. Reference Circuits An Intuitive Approach (Analog IC Design An Intuitive Approach)Dokument19 SeitenChapter 8. Reference Circuits An Intuitive Approach (Analog IC Design An Intuitive Approach)Minh Hai RungNoch keine Bewertungen

- Unit Vii Fet AmplifiersDokument14 SeitenUnit Vii Fet AmplifiersAadarsha timilsinaNoch keine Bewertungen

- Clark and Park TransformationDokument9 SeitenClark and Park Transformationjm.mankavil6230100% (1)

- Electrical Machines I Lab Twisted QuestionsDokument4 SeitenElectrical Machines I Lab Twisted QuestionsPranav MenonNoch keine Bewertungen

- Protective Relaying QuizDokument3 SeitenProtective Relaying QuizCattleya Tabor PeñalosaNoch keine Bewertungen

- Ee8004 Modern Power Converters SyllabusDokument2 SeitenEe8004 Modern Power Converters SyllabussignjpcoeNoch keine Bewertungen

- Luo ConverterDokument6 SeitenLuo ConverterAndrei CocorNoch keine Bewertungen

- Power System Simulation - Prof - Jain B. Marshel - ScilabDokument72 SeitenPower System Simulation - Prof - Jain B. Marshel - ScilabJerry ValdezNoch keine Bewertungen

- Circuit Debugging Round1Dokument4 SeitenCircuit Debugging Round1Saravanan JaganNoch keine Bewertungen

- Topology Investigation For Front End DC-DC Power Conversion For Distributed Power SystemDokument332 SeitenTopology Investigation For Front End DC-DC Power Conversion For Distributed Power Systemwouter81100% (4)

- Design and Micro Controller Implementation of A Three Phase SCR Power ConverterDokument8 SeitenDesign and Micro Controller Implementation of A Three Phase SCR Power ConverterIsmael Ochoa JimenezNoch keine Bewertungen

- Chapter 5: Speed-Torque Characteristics of Electric MotorsDokument46 SeitenChapter 5: Speed-Torque Characteristics of Electric MotorsFrozenTuxNoch keine Bewertungen

- Giza Systems Ss Zigzag Calculation Xls SheetDokument1 SeiteGiza Systems Ss Zigzag Calculation Xls SheetMohamed ShafeyNoch keine Bewertungen

- Power Electronics Lab ManualDokument89 SeitenPower Electronics Lab ManualPartha DewriNoch keine Bewertungen

- BJT Diff AmplifierDokument15 SeitenBJT Diff AmplifierAdrià Amézaga SàrriesNoch keine Bewertungen

- AC DC DrivesDokument13 SeitenAC DC Drives322399mk7086Noch keine Bewertungen

- Quiz QuestionsDokument3 SeitenQuiz Questionssaiphaneendra_m100% (1)

- ZVS-ZCS Bidirectional Full-Bridge DC-DC ConverterDokument6 SeitenZVS-ZCS Bidirectional Full-Bridge DC-DC ConverterPradhapndk100% (1)

- Inductor Design Methodology For Power Electronics Applications PDFDokument6 SeitenInductor Design Methodology For Power Electronics Applications PDFpedrovilknNoch keine Bewertungen

- Buck Converter With Current Mode ControlDokument1 SeiteBuck Converter With Current Mode ControlMasaruNakaegawaNoch keine Bewertungen

- r7310205 Electrical Machines IIIDokument4 Seitenr7310205 Electrical Machines IIIsivabharathamurthyNoch keine Bewertungen

- Assignment 1 EPSD LabDokument1 SeiteAssignment 1 EPSD LabChvyNoch keine Bewertungen

- Parallel Capacitor Inverter With Feedback DiodesDokument9 SeitenParallel Capacitor Inverter With Feedback DiodesJayant Kirpekar100% (1)

- Investigation of the Usefulness of the PowerWorld Simulator Program: Developed by "Glover, Overbye & Sarma" in the Solution of Power System ProblemsVon EverandInvestigation of the Usefulness of the PowerWorld Simulator Program: Developed by "Glover, Overbye & Sarma" in the Solution of Power System ProblemsNoch keine Bewertungen

- Digital Signal Processing Systems: Implementation Techniques: Advances in Theory and ApplicationsVon EverandDigital Signal Processing Systems: Implementation Techniques: Advances in Theory and ApplicationsNoch keine Bewertungen

- Power Electronics Converters and their Control for Renewable Energy ApplicationsVon EverandPower Electronics Converters and their Control for Renewable Energy ApplicationsArezki FekikNoch keine Bewertungen

- Self-Oscillating Resonant AC/DC Converter Topology For Input Power-Factor CorrectionDokument11 SeitenSelf-Oscillating Resonant AC/DC Converter Topology For Input Power-Factor CorrectionJie99Noch keine Bewertungen

- LM25005, LM25010: Buck Regulator Topologies For Wide Input/Output Voltage DifferentialsDokument10 SeitenLM25005, LM25010: Buck Regulator Topologies For Wide Input/Output Voltage DifferentialsBejoy ThomasNoch keine Bewertungen

- Three-Phase Unity Power FactorDokument10 SeitenThree-Phase Unity Power FactorSatya NV0% (1)

- 3-Phase Power Factor Correction, Using Vienna Rectifier ApproachDokument13 Seiten3-Phase Power Factor Correction, Using Vienna Rectifier Approachvdiaz1Noch keine Bewertungen

- Some Topologies of High Quality RectifiersDokument6 SeitenSome Topologies of High Quality RectifiersSatya NVNoch keine Bewertungen

- SingleDokument7 SeitenSingleSatya NVNoch keine Bewertungen

- PWM RectDokument5 SeitenPWM RectSatya NVNoch keine Bewertungen

- PWM Regenerative RectifiersDokument15 SeitenPWM Regenerative RectifiersSatya NVNoch keine Bewertungen

- Power Factor Correction Using Single PhaseDokument5 SeitenPower Factor Correction Using Single PhaseSatya NVNoch keine Bewertungen

- Line Current Harmonics Reduduction by Using RectifiersDokument8 SeitenLine Current Harmonics Reduduction by Using RectifiersSatya NVNoch keine Bewertungen

- A New Three-Phase Power-Factor Correction (PFC)Dokument8 SeitenA New Three-Phase Power-Factor Correction (PFC)Satya NVNoch keine Bewertungen

- Performance Analysis of Direct Power Controlled PWM Rectifier Under Disturbed AC Line VoltageDokument6 SeitenPerformance Analysis of Direct Power Controlled PWM Rectifier Under Disturbed AC Line VoltagecuterithikaNoch keine Bewertungen

- Modeling and Control of Three Phase Boost Rectifiers ViaDokument3 SeitenModeling and Control of Three Phase Boost Rectifiers ViaSatya NVNoch keine Bewertungen

- A Review of Three-Phase Improved Power QualityDokument20 SeitenA Review of Three-Phase Improved Power QualitySatya NV100% (1)

- A Three-Phasteh Ree-Switcthw O-Leveplw M RectifierDokument5 SeitenA Three-Phasteh Ree-Switcthw O-Leveplw M RectifierSatya NVNoch keine Bewertungen

- 2000 PWM Boost Type RectifierDokument4 Seiten2000 PWM Boost Type RectifierSatya NVNoch keine Bewertungen

- PSI AP Physics C - Gauss's Law Multiple Choice QuestionsDokument7 SeitenPSI AP Physics C - Gauss's Law Multiple Choice Questionsanthony solorzanoNoch keine Bewertungen

- Pankaj Final Industrial Training Report 1234Dokument36 SeitenPankaj Final Industrial Training Report 1234pankaj madhheshiyaNoch keine Bewertungen

- 2N3055A (NPN), MJ15015 (NPN), MJ15016 (PNP) Complementary Silicon High Power TransistorsDokument6 Seiten2N3055A (NPN), MJ15015 (NPN), MJ15016 (PNP) Complementary Silicon High Power TransistorsvdăduicăNoch keine Bewertungen

- 2784Dokument4 Seiten2784heribertosfaNoch keine Bewertungen

- Dynasty 200 DXUser ManualDokument98 SeitenDynasty 200 DXUser ManualBill100% (1)

- Dangote Elevator SPL List NewDokument1 SeiteDangote Elevator SPL List NeweliasNoch keine Bewertungen

- Gate-2019 Original Paper - EE/0Dokument33 SeitenGate-2019 Original Paper - EE/0hemanth katkamNoch keine Bewertungen

- E&I QAP's - Submitted To Contractor HZADokument33 SeitenE&I QAP's - Submitted To Contractor HZASuraj ShettyNoch keine Bewertungen

- General CNC InformationDokument63 SeitenGeneral CNC InformationCristopher EntenaNoch keine Bewertungen

- Voltage Amplification, Trail Cable Length & Power ShovelsDokument9 SeitenVoltage Amplification, Trail Cable Length & Power ShovelsMaikPortnoyNoch keine Bewertungen

- Marking Codes Small Signal Transistors and DiodesDokument40 SeitenMarking Codes Small Signal Transistors and DiodesSlimane SlimaneNoch keine Bewertungen

- 20039-11 B11R D11C UniverseDokument225 Seiten20039-11 B11R D11C UniverseDaniel Alex SánchezNoch keine Bewertungen

- Transicool Carrier Xarios - Technical ManualDokument80 SeitenTransicool Carrier Xarios - Technical Manualsimon_someone21788% (24)

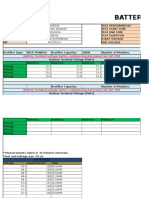

- Battery Autonomy Test For Makongo Songas Dar543Dokument11 SeitenBattery Autonomy Test For Makongo Songas Dar543Paul Lazaro Lalah SulleNoch keine Bewertungen

- Physics 1 - Class XIIDokument311 SeitenPhysics 1 - Class XIISunil Nahata100% (1)

- Metal Fire Alarm Station Ms-700U Series: FeaturesDokument2 SeitenMetal Fire Alarm Station Ms-700U Series: FeaturesRicardo TitoNoch keine Bewertungen

- DuFlex Flexible CablesDokument23 SeitenDuFlex Flexible CablesAli FarooqNoch keine Bewertungen

- bc337 PDFDokument4 Seitenbc337 PDFgerluccioniNoch keine Bewertungen

- Rasuwagadhi Hydropower Company LimitedDokument3 SeitenRasuwagadhi Hydropower Company LimitedSubhash MishraNoch keine Bewertungen

- Ae-6b Service Manual 488Dokument52 SeitenAe-6b Service Manual 488fontanieroNoch keine Bewertungen

- Battery StorageDokument44 SeitenBattery StorageMuruganNoch keine Bewertungen

- ELTEK Valere Hybrid SolutionsDokument8 SeitenELTEK Valere Hybrid SolutionsAnonymous jnG2gQEbHNoch keine Bewertungen

- Mind Mapping of WeldingDokument8 SeitenMind Mapping of WeldingFadlanbunglonNoch keine Bewertungen

- W Series Data Sheet 125, 250 Watt AC-DC and DC-DC DIN-Rail Mount ConvertersDokument28 SeitenW Series Data Sheet 125, 250 Watt AC-DC and DC-DC DIN-Rail Mount ConvertersTommy DwiNoch keine Bewertungen

- Hatta PropagationDokument2 SeitenHatta PropagationnikoabdulNoch keine Bewertungen

- Y500 User Manual enDokument115 SeitenY500 User Manual enLêĐứcDũngNoch keine Bewertungen

- Lenovo Legion 5 Pro 16 HMMDokument66 SeitenLenovo Legion 5 Pro 16 HMMJorge LaraNoch keine Bewertungen

- DatasheetDokument7 SeitenDatasheetRon de CañaNoch keine Bewertungen

- Wire Loss CalculatorDokument6 SeitenWire Loss CalculatorPatrick McCourtNoch keine Bewertungen

- 14 Switching Devices Catalog Vol1 Tab2 Ca08100003eDokument126 Seiten14 Switching Devices Catalog Vol1 Tab2 Ca08100003eMusab yassinNoch keine Bewertungen