Beruflich Dokumente

Kultur Dokumente

Getting To Know Vivado: Course Workbook

Hochgeladen von

takaca400 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

12 Ansichten54 SeitenOriginaltitel

Working_With_Vivado_P3

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

12 Ansichten54 SeitenGetting To Know Vivado: Course Workbook

Hochgeladen von

takaca40Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 54

Getting to Know Vivado

Course Workbook

Copyright 2020 Adiuvo Engineering & Training, Ltd. 1

Table of Contents

About this Workbook Page 3

Pre-Lab: Workshop Pre-requisites Page 4

Lab 3: Advanced Vivado Page 7

Copyright 2020 Adiuvo Engineering & Training, Ltd. 2

About this Workbook

This workbook is designed to be used in conjunction with the Getting to Know Vivado

course.

The contents of this workbook are created by Adiuvo Engineering & Training, Ltd.

If you have any questions about the contents or need assistance, please contact Adam

Taylor at adam@adiuvoengineering.com.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 3

Pre-Lab

Workshop Pre-requisites

Copyright 2020 Adiuvo Engineering & Training, Ltd. 4

Pre-Lab

Required Hardware

There is no required hardware for this course.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 5

Pre-Lab

Downloads and Installations

Step 1 – Download and install the following at least one day prior to the workshop. This may take a

significant amount of time and drive space.

Vivado 2020.1 Download

Source Project Files Download

Lab 2 must be completed

Copyright 2020 Adiuvo Engineering & Training, Ltd. 6

Lab 3

Advanced Vivado

Copyright 2020 Adiuvo Engineering & Training, Ltd. 7

Lab 3

Lab 3: Advanced Vivado

Step 1 – Open the project created in part two.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 8

Lab 3

Lab 3: Advanced Vivado

Step 2 – In the TCL window, check the PWD and change directory to the location containing your

project. Then enter the command write_project_tcl average.tcl.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 9

Lab 3

Lab 3: Advanced Vivado

Step 3 – This will write a project description in TCL to the project directory.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 10

Lab 3

Lab 3: Advanced Vivado

Step 4 – Open the TCL file and change the project name from 01_Vivado to 01_Vivado_rebuild.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 11

Lab 3

Lab 3: Advanced Vivado

Step 5 – Close the current project and type source average.tcl. in the TCL window.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 12

Lab 3

Lab 3: Advanced Vivado

Step 6 – This will rebuild the project exactly as before from the TCL file.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 13

Lab 3

Lab 3: Advanced Vivado

Step 7 – Open the block design and click on the + symbol to add in IP. In the search bar, enter ILA

and then double click on the ILA (Integrated Logic Analyzer) to add in the IP core.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 14

Lab 3

Lab 3: Advanced Vivado

Step 8 – Double click on the ILA to customize it.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 15

Lab 3

Lab 3: Advanced Vivado

Step 9 – Change the monitor type to Native.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 16

Lab 3

Lab 3: Advanced Vivado

Step 10 – Set the number of probes to 5.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 17

Lab 3

Lab 3: Advanced Vivado

Step 11 – Click on the Probe Ports Tab and set the widths of PROBE3 to 8 and PROBE4 to 12, click

OK.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 18

Lab 3

Lab 3: Advanced Vivado

Step 12 – The block diagram should now show the ILA with five ports and a clock input.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 19

Lab 3

Lab 3: Advanced Vivado

Step 13 – Connect up the ILA as shown below. This will provide us visibility of all input and output of

the average block.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 20

Lab 3

Lab 3: Advanced Vivado

Step 14 – Click on the + symbol to add in IP and type VIO in the search box. Double click on the VIO

symbol.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 21

Lab 3

Lab 3: Advanced Vivado

Step 15 – When the VIO is added onto the block diagram, double click it to customize and explore the

three tabs. Leave it all unchanged and click OK.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 22

Lab 3

Lab 3: Advanced Vivado

Step 16 – Select the RST_0 line and delete it.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 23

Lab 3

Lab 3: Advanced Vivado

Step 17 – Connect the VIO probe output to the RST and ILA.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 24

Lab 3

Lab 3: Advanced Vivado

Step 18 – Connect the RST_0 input to the VIO Probe in.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 25

Lab 3

Lab 3: Advanced Vivado

Step 19 – From the Menu bar, select Tools → Create and Package IP. Select Next when the dialog

opens.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 26

Lab 3

Lab 3: Advanced Vivado

Step 20 – Select Package your current project and then Next.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 27

Lab 3

Lab 3: Advanced Vivado

Step 21 – Select the location the IP should be saved in and click Next.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 28

Lab 3

Lab 3: Advanced Vivado

Step 22 – Click on Finish.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 29

Lab 3

Lab 3: Advanced Vivado

Step 23 – This will open a package view in the project. Enter Name, Version and Company URL.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 30

Lab 3

Lab 3: Advanced Vivado

Step 24 – Click on the Compatibility tab. This defines what FPGA / SoC the core will work with.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 31

Lab 3

Lab 3: Advanced Vivado

Step 25 – Click on + and select Add Family Explicitly.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 32

Lab 3

Lab 3: Advanced Vivado

Step 26 – In the resultant dialog, select All Families and Parts and Production from the Life-cycle.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 33

Lab 3

Lab 3: Advanced Vivado

Step 27 – This will make the IP core available to all families and devices.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 34

Lab 3

Lab 3: Advanced Vivado

Step 28 – Click on Ports and Interfaces. This should show all the blocks’ inputs and outputs.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 35

Lab 3

Lab 3: Advanced Vivado

Step 29 – Click on Customization. This shows the symbol.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 36

Lab 3

Lab 3: Advanced Vivado

Step 30 – Click on Settings.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 37

Lab 3

Lab 3: Advanced Vivado

Step 31 – Select Create archive of IP and click OK.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 38

Lab 3

Lab 3: Advanced Vivado

Step 32 – Click on Review and Package and then Package IP.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 39

Lab 3

Lab 3: Advanced Vivado

Step 33 – This should show the message below. Click OK.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 40

Lab 3

Lab 3: Advanced Vivado

Step 34 – You will see a ZIP file of the component in the directory you identified to save the IP in.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 41

Lab 3

Lab 3: Advanced Vivado

Step 35 – Close the project and create a new Vivado project. In the wizard, click Next, then enter the

name and location and click Next again.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 42

Lab 3

Lab 3: Advanced Vivado

Step 36 – Select RTL Project and Next, followed by Next again.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 43

Lab 3

Lab 3: Advanced Vivado

Step 37 – Click Next on the Constraints tab. On the Default Part, select the ZCU104 board and click

Next.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 44

Lab 3

Lab 3: Advanced Vivado

Step 38 – On the final page of the Project Summary, click OK.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 45

Lab 3

Lab 3: Advanced Vivado

Step 39 – From the menu bar, select Window → IP Catalog.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 46

Lab 3

Lab 3: Advanced Vivado

Step 40 – Right click on the Vivado Repository and select Add Repository.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 47

Lab 3

Lab 3: Advanced Vivado

Step 41 – In the open dialog, select Create New Folder and name it IP and click Select.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 48

Lab 3

Lab 3: Advanced Vivado

Step 42 – This will show a dialog indicating that one repository was added.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 49

Lab 3

Lab 3: Advanced Vivado

Step 43 – This will add in the repository. Right click on it and select Add IP to Repository.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 50

Lab 3

Lab 3: Advanced Vivado

Step 44 – Select the component ZIP file in the file dialog and click OK.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 51

Lab 3

Lab 3: Advanced Vivado

Step 45 – You should now see the IP core in the library ready to go in our new design.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 52

Lab 3

Lab 3: Advanced Vivado

Step 46 – Create a block design and type in the search bar average. Double click on the

design_1_wrapper_V1_0 which comes up.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 53

Lab 3

Lab 3: Advanced Vivado

Step 47 – This will add in the Average block we have created and we are ready to go reusing it in our

new developments.

Copyright 2020 Adiuvo Engineering & Training, Ltd. 54

Das könnte Ihnen auch gefallen

- Working With Vivado P2Dokument59 SeitenWorking With Vivado P2takaca40Noch keine Bewertungen

- Visual Basic.NET at Work: Building 10 Enterprise ProjectsVon EverandVisual Basic.NET at Work: Building 10 Enterprise ProjectsNoch keine Bewertungen

- Getting To Know Vivado: Course WorkbookDokument53 SeitenGetting To Know Vivado: Course Workbooktakaca40Noch keine Bewertungen

- 2.1.2.3 Packet Tracer - Blinking An LED Using Blockly - ILMDokument13 Seiten2.1.2.3 Packet Tracer - Blinking An LED Using Blockly - ILMDanh Huynh0% (1)

- PIC Projects and Applications using C: A Project-based ApproachVon EverandPIC Projects and Applications using C: A Project-based ApproachBewertung: 4 von 5 Sternen4/5 (2)

- Lab 05Dokument25 SeitenLab 05karthikp207Noch keine Bewertungen

- It File SampleDokument18 SeitenIt File SampleSaurabh SainiNoch keine Bewertungen

- 2.2.1.4 Packet Tracer - Simulating IoT Devices - M0517010Dokument5 Seiten2.2.1.4 Packet Tracer - Simulating IoT Devices - M0517010Astika IstiningrumNoch keine Bewertungen

- Monalyn Señaris - 2.2.1.4 Packet Tracer - Simulating IoT DevicesDokument5 SeitenMonalyn Señaris - 2.2.1.4 Packet Tracer - Simulating IoT DevicesMonalyn SeñarisNoch keine Bewertungen

- Answer Ley m1Dokument5 SeitenAnswer Ley m1GowthamanNoch keine Bewertungen

- Monalyn Señaris - 2.2.1.4 Packet Tracer - Simulating IoT DevicesDokument5 SeitenMonalyn Señaris - 2.2.1.4 Packet Tracer - Simulating IoT DevicesMonalyn SeñarisNoch keine Bewertungen

- LabVIEW 1 Day ExercisesDokument23 SeitenLabVIEW 1 Day Exercisesrashid sharifNoch keine Bewertungen

- Labview Core 2 Exercises: Instruments Not For DistributionDokument102 SeitenLabview Core 2 Exercises: Instruments Not For DistributionAmín ACNoch keine Bewertungen

- 15 ModuleDiscovery LabDokument12 Seiten15 ModuleDiscovery LabJavier Omar GinezNoch keine Bewertungen

- Irjet V9i6482Dokument4 SeitenIrjet V9i6482ÀDÂRSHk10Noch keine Bewertungen

- Articulo 6-SMEDDokument8 SeitenArticulo 6-SMEDRenzo LozanoNoch keine Bewertungen

- 2 2 1 4Dokument6 Seiten2 2 1 4Ralph ValenzuelaNoch keine Bewertungen

- 2.2.1.4 Packet Tracer - Simulating IoT DevicesDokument5 Seiten2.2.1.4 Packet Tracer - Simulating IoT DevicesMuhammad AkbarNoch keine Bewertungen

- Create a Simple ARM Cortex-A9 Zynq Design and Blink an LEDDokument20 SeitenCreate a Simple ARM Cortex-A9 Zynq Design and Blink an LEDMUHAMMAD AFZALNoch keine Bewertungen

- 2.1.2.3 Packet Tracer - Blinking An LED Using BlocklyDokument11 Seiten2.1.2.3 Packet Tracer - Blinking An LED Using BlocklyAnggita Aulia0% (1)

- 2.2.1.4 Packet Tracer - Simulating IoT DevicesDokument6 Seiten2.2.1.4 Packet Tracer - Simulating IoT DevicesHalima AqraaNoch keine Bewertungen

- Up Down CounterDokument20 SeitenUp Down Countersumi36117Noch keine Bewertungen

- ICD LabDokument50 SeitenICD Labk10Noch keine Bewertungen

- LabVIEW Arduino v1Dokument4 SeitenLabVIEW Arduino v1Piloi100% (2)

- LabVIEW TM Core 2 Course Manual-1-10Dokument10 SeitenLabVIEW TM Core 2 Course Manual-1-10陳彥勳Noch keine Bewertungen

- LabView Core 2 Course Manual PDFDokument130 SeitenLabView Core 2 Course Manual PDFAlejandroNoch keine Bewertungen

- Manufacturing WorkshopDokument6 SeitenManufacturing WorkshopAnailé Del Carmen PeñaNoch keine Bewertungen

- Train for CLAD certification in LabVIEWDokument2 SeitenTrain for CLAD certification in LabVIEWSuryaCharanPaidipalliNoch keine Bewertungen

- I Find Your Lack of LabVIEW Programming Speed DisturbingDokument24 SeitenI Find Your Lack of LabVIEW Programming Speed DisturbingTibiro TibiroNoch keine Bewertungen

- ITL202 - ktu qbankDokument5 SeitenITL202 - ktu qbankManoj KumarNoch keine Bewertungen

- LabVIEW-Arduino Data Acquisition and TelemetryDokument38 SeitenLabVIEW-Arduino Data Acquisition and TelemetryReymi ThenNoch keine Bewertungen

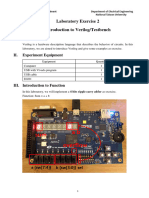

- University of Perpetual Help System Dalta Las Pinas Campus: College of Engineering Electtrical Engineering DepartmentDokument14 SeitenUniversity of Perpetual Help System Dalta Las Pinas Campus: College of Engineering Electtrical Engineering DepartmentKiel DalisayNoch keine Bewertungen

- Conect Labview PLCDokument3 SeitenConect Labview PLCWicho AnayaNoch keine Bewertungen

- AAL Exercise ManualDokument268 SeitenAAL Exercise Manualsu weiNoch keine Bewertungen

- Electrical Engineering Department - ITU EE - L: Digital System Design LabDokument13 SeitenElectrical Engineering Department - ITU EE - L: Digital System Design LabJunaid KhalidNoch keine Bewertungen

- Sabari Shree SDokument15 SeitenSabari Shree S19F026 Mohan Raam.SNoch keine Bewertungen

- Course Title: Iot Based Product Design L T P/ S SW/F W Total Credit UnitsDokument4 SeitenCourse Title: Iot Based Product Design L T P/ S SW/F W Total Credit UnitsSrishti SanyalNoch keine Bewertungen

- Vivado TutorialDokument31 SeitenVivado Tutorialujwala_512Noch keine Bewertungen

- New DSD Manual Rvitm (4-7)Dokument72 SeitenNew DSD Manual Rvitm (4-7)Spam SpamNoch keine Bewertungen

- LabVIEW-Arduino Interfacing For Data Aqcuisition and Telemetry SystemDokument38 SeitenLabVIEW-Arduino Interfacing For Data Aqcuisition and Telemetry SystemCandidoMolanesNoch keine Bewertungen

- Certificate of Completion: Regie BaliguatDokument1 SeiteCertificate of Completion: Regie Baliguatregie baliguatNoch keine Bewertungen

- 2.2.1.4 Packet Tracer - Simulating IoT Devices Ep2Dokument5 Seiten2.2.1.4 Packet Tracer - Simulating IoT Devices Ep2Diego SotomayorNoch keine Bewertungen

- "JAVA" "Ezbiz Technologies Pvt. LTD.": A Summer Training Report OnDokument51 Seiten"JAVA" "Ezbiz Technologies Pvt. LTD.": A Summer Training Report OnHarshit SinghNoch keine Bewertungen

- Embedded Systems Lab Manual-Sem-IDokument17 SeitenEmbedded Systems Lab Manual-Sem-IAnand DuraiswamyNoch keine Bewertungen

- Industrial Training Sample Report - AIETMDokument17 SeitenIndustrial Training Sample Report - AIETMtej.shekhawat16Noch keine Bewertungen

- It Report Abhay 45Dokument44 SeitenIt Report Abhay 45arjun.jaygadi.9Noch keine Bewertungen

- Siemens Simatic-Iot2020-EnDokument2 SeitenSiemens Simatic-Iot2020-EnThanachai TengjirathanapaNoch keine Bewertungen

- Release Notes IoT Gateway 1.2.1Dokument13 SeitenRelease Notes IoT Gateway 1.2.1luanNoch keine Bewertungen

- Zynq FPGA Labs 23Dokument51 SeitenZynq FPGA Labs 23MOHAMED ABDELMALEKNoch keine Bewertungen

- Catalog DoBotDokument5 SeitenCatalog DoBotAchmadErry100% (1)

- Modeling With PV Elite Lesson GuideDokument323 SeitenModeling With PV Elite Lesson Guideasif67% (3)

- Labview Core I & II BrochureDokument3 SeitenLabview Core I & II BrochureHemantha KumarNoch keine Bewertungen

- 06 LabVIEW Interface For Arduino (LIFA)Dokument6 Seiten06 LabVIEW Interface For Arduino (LIFA)Cleber José de SouzaNoch keine Bewertungen

- Musical Signal Processing With LabVIEWDokument40 SeitenMusical Signal Processing With LabVIEWJude SudarioNoch keine Bewertungen

- 2) Assignment QuestionDokument6 Seiten2) Assignment QuestionWeng Hoe CheahNoch keine Bewertungen

- PlantPAx 5.0 Early Adopter Lab 2 - Highly Integrated HARTDokument32 SeitenPlantPAx 5.0 Early Adopter Lab 2 - Highly Integrated HARTdelgadoerwuinNoch keine Bewertungen

- Lab 2Dokument13 SeitenLab 26rmbg4yjg8Noch keine Bewertungen

- PAN9 EDU210 Lab 12Dokument29 SeitenPAN9 EDU210 Lab 12GenestapowerNoch keine Bewertungen

- PLECS Model Quick Start Guide DS50002997ADokument37 SeitenPLECS Model Quick Start Guide DS50002997Atakaca40Noch keine Bewertungen

- Designing Silicon Carbide (Sic) Based DC Fast Charging System: Key Challenges, Design Considerations, and Building ValidationDokument31 SeitenDesigning Silicon Carbide (Sic) Based DC Fast Charging System: Key Challenges, Design Considerations, and Building Validationtakaca40Noch keine Bewertungen

- Microzed Chronicles: Device Trees: Search All Content BlogDokument7 SeitenMicrozed Chronicles: Device Trees: Search All Content Blogtakaca40Noch keine Bewertungen

- Getting Started with Vivado Workshop Part 2Dokument4 SeitenGetting Started with Vivado Workshop Part 2takaca40Noch keine Bewertungen

- The New Standard For Model Sharing and Collaboration: EbookDokument8 SeitenThe New Standard For Model Sharing and Collaboration: Ebooktakaca40Noch keine Bewertungen

- Scilab FMI Toolbox - Datasheet 2019Dokument2 SeitenScilab FMI Toolbox - Datasheet 2019takaca40Noch keine Bewertungen

- Getting To Started With Vivado Workshop Presentation Session1Dokument4 SeitenGetting To Started With Vivado Workshop Presentation Session1takaca40Noch keine Bewertungen

- Edge AIDokument156 SeitenEdge AItakaca4067% (3)

- Dspic Control Board: For Industrial ApplicationsDokument5 SeitenDspic Control Board: For Industrial Applicationstakaca40Noch keine Bewertungen

- Implementation of A Multi-Level Power Electronic InverterDokument11 SeitenImplementation of A Multi-Level Power Electronic Invertertakaca40Noch keine Bewertungen

- Using Python and Sockets: System Power Supply ProgrammingDokument6 SeitenUsing Python and Sockets: System Power Supply Programmingtakaca40Noch keine Bewertungen

- Kickd Pic32 Ubl ManualDokument18 SeitenKickd Pic32 Ubl Manualtakaca40Noch keine Bewertungen

- Compiled Tips'N Tricks Guide PIC Micro Controller - MicrochipDokument137 SeitenCompiled Tips'N Tricks Guide PIC Micro Controller - MicrochipAlexandre Magnus Fernandes GuimarãesNoch keine Bewertungen

- Best Way To Download Xilinx Design Tools - Community ForumsDokument5 SeitenBest Way To Download Xilinx Design Tools - Community Forumstakaca40Noch keine Bewertungen

- USB Frequency Counter and Voltmeter ProjectDokument63 SeitenUSB Frequency Counter and Voltmeter ProjectGarra Crema StoneNoch keine Bewertungen

- BUFR PrepBUFR User Guide v1Dokument82 SeitenBUFR PrepBUFR User Guide v1Fernando Nicolás Arellano GuerreroNoch keine Bewertungen

- QoS + PCQ MikrotikDokument4 SeitenQoS + PCQ MikrotikFranklin PintoNoch keine Bewertungen

- Classes: Python Method ReprDokument3 SeitenClasses: Python Method ReprGeorge IskanderNoch keine Bewertungen

- ICAS Administration English Online PDFDokument4 SeitenICAS Administration English Online PDFemilyNoch keine Bewertungen

- Lampiran 3 - Tatacara Penggunaan IDB Analyzer PDFDokument11 SeitenLampiran 3 - Tatacara Penggunaan IDB Analyzer PDFzulhariszan abd mananNoch keine Bewertungen

- Cisco 2900 and 3900 Series Hardware Installation: Americas HeadquartersDokument226 SeitenCisco 2900 and 3900 Series Hardware Installation: Americas Headquartersdiego valladolidNoch keine Bewertungen

- Adnan Masood - Automated Machine Learning - Hyperparameter Optimization, Neural Architecture Search, and Algorithm Selection With Cloud Platforms (2021, Packt Publishing LTD) - Libgen - LiDokument312 SeitenAdnan Masood - Automated Machine Learning - Hyperparameter Optimization, Neural Architecture Search, and Algorithm Selection With Cloud Platforms (2021, Packt Publishing LTD) - Libgen - LiSayantan Roy100% (3)

- Control System AdvancementsDokument15 SeitenControl System AdvancementstungluongNoch keine Bewertungen

- STAN Statistika 12 PDFDokument25 SeitenSTAN Statistika 12 PDFPembelajaran Jarak JauhNoch keine Bewertungen

- 8M-BIT SERIAL FLASH MEMORY WITH 4KB SECTORS AND DUAL I/O SPIDokument50 Seiten8M-BIT SERIAL FLASH MEMORY WITH 4KB SECTORS AND DUAL I/O SPImartin sembinelliNoch keine Bewertungen

- Introduction To Unix and Linux For DeveloperDokument84 SeitenIntroduction To Unix and Linux For DeveloperRashi ChoudharyNoch keine Bewertungen

- Dell Ispiron 15 3541 13283-1 CEDAR AMD Beema A00Dokument104 SeitenDell Ispiron 15 3541 13283-1 CEDAR AMD Beema A00Jesús MenciaNoch keine Bewertungen

- Business Architect Essentials 8.7 GA Exercise GuideDokument347 SeitenBusiness Architect Essentials 8.7 GA Exercise GuideEDUARDO CIRILO BERMAN ALARCONNoch keine Bewertungen

- Guide To Cloudsimexample1.Java Simulation Workflow: Cloudsim Setup Using Eclipse IdeDokument15 SeitenGuide To Cloudsimexample1.Java Simulation Workflow: Cloudsim Setup Using Eclipse Ideshazrah JamshaidNoch keine Bewertungen

- Red Black TreeDokument72 SeitenRed Black TreeChitra S SrinivasanNoch keine Bewertungen

- Auditing OS and NetworksDokument35 SeitenAuditing OS and Networksangie rosalesNoch keine Bewertungen

- Denon AVR-2113 PDFDokument222 SeitenDenon AVR-2113 PDFboroda2410100% (5)

- Clipperton Island Case - PDF - Justice - Crime & ViolenceDokument2 SeitenClipperton Island Case - PDF - Justice - Crime & ViolenceMarlon DizonNoch keine Bewertungen

- Spring Boot: Working With Application Runner: - by RAGHU SIR, Naresh ITDokument4 SeitenSpring Boot: Working With Application Runner: - by RAGHU SIR, Naresh ITVenkat GowdaNoch keine Bewertungen

- TLB4 Manual EN 1Dokument72 SeitenTLB4 Manual EN 1max_ingNoch keine Bewertungen

- Fuzzy Logic 1Dokument20 SeitenFuzzy Logic 1PiyushNoch keine Bewertungen

- Tcs Bancs Webservice Repository Document - InwarddirectcreditcorrectiontransactionDokument8 SeitenTcs Bancs Webservice Repository Document - InwarddirectcreditcorrectiontransactionMuhammad Sheharyar MohsinNoch keine Bewertungen

- Windows Startup Processes and Scheduled TasksDokument7 SeitenWindows Startup Processes and Scheduled TasksbryamNoch keine Bewertungen

- VLOG 4: Subtraction of Decimals (Flow)Dokument3 SeitenVLOG 4: Subtraction of Decimals (Flow)Earl CalingacionNoch keine Bewertungen

- UkkoS Manual ENDokument23 SeitenUkkoS Manual ENFrederik CAÑABINoch keine Bewertungen

- IColor Cove MX Powercore ProductGuideDokument16 SeitenIColor Cove MX Powercore ProductGuideNMTĐ A Vương Phòng kỹ thuậtNoch keine Bewertungen

- Error Detection DechniquesDokument16 SeitenError Detection Dechniquesmithilesh kumar masterNoch keine Bewertungen

- Azure - Lab 05Dokument11 SeitenAzure - Lab 05vikibabuNoch keine Bewertungen

- Replicate Sales Order To c4c - Ordem Enviada para c4cDokument3 SeitenReplicate Sales Order To c4c - Ordem Enviada para c4cRenato Souza Lopes Lisboa de AssisNoch keine Bewertungen

- Topic 6 Proper Use of Basic FacilitiesDokument20 SeitenTopic 6 Proper Use of Basic FacilitiesPrincess Sarah Mae AmistadNoch keine Bewertungen

- How to Do Nothing: Resisting the Attention EconomyVon EverandHow to Do Nothing: Resisting the Attention EconomyBewertung: 4 von 5 Sternen4/5 (421)

- The Internet Con: How to Seize the Means of ComputationVon EverandThe Internet Con: How to Seize the Means of ComputationBewertung: 5 von 5 Sternen5/5 (6)

- Web Copy That Sells: The Revolutionary Formula for Creating Killer Copy That Grabs Their Attention and Compels Them to BuyVon EverandWeb Copy That Sells: The Revolutionary Formula for Creating Killer Copy That Grabs Their Attention and Compels Them to BuyBewertung: 4 von 5 Sternen4/5 (13)

- Monitored: Business and Surveillance in a Time of Big DataVon EverandMonitored: Business and Surveillance in a Time of Big DataBewertung: 4 von 5 Sternen4/5 (1)

- Ultimate Guide to LinkedIn for Business: Access more than 500 million people in 10 minutesVon EverandUltimate Guide to LinkedIn for Business: Access more than 500 million people in 10 minutesBewertung: 5 von 5 Sternen5/5 (5)

- Ultimate Guide to YouTube for BusinessVon EverandUltimate Guide to YouTube for BusinessBewertung: 5 von 5 Sternen5/5 (1)

- The Social Media Bible: Tactics, Tools, and Strategies for Business SuccessVon EverandThe Social Media Bible: Tactics, Tools, and Strategies for Business SuccessBewertung: 3.5 von 5 Sternen3.5/5 (19)

- A Great Online Dating Profile: 30 Tips to Get Noticed and Get More ResponsesVon EverandA Great Online Dating Profile: 30 Tips to Get Noticed and Get More ResponsesBewertung: 3.5 von 5 Sternen3.5/5 (2)

- Get Into UX: A foolproof guide to getting your first user experience jobVon EverandGet Into UX: A foolproof guide to getting your first user experience jobBewertung: 4.5 von 5 Sternen4.5/5 (5)

- The Ultimate LinkedIn Sales Guide: How to Use Digital and Social Selling to Turn LinkedIn into a Lead, Sales and Revenue Generating MachineVon EverandThe Ultimate LinkedIn Sales Guide: How to Use Digital and Social Selling to Turn LinkedIn into a Lead, Sales and Revenue Generating MachineNoch keine Bewertungen

- How to Create Cpn Numbers the Right way: A Step by Step Guide to Creating cpn Numbers LegallyVon EverandHow to Create Cpn Numbers the Right way: A Step by Step Guide to Creating cpn Numbers LegallyBewertung: 4 von 5 Sternen4/5 (27)

- Branding: What You Need to Know About Building a Personal Brand and Growing Your Small Business Using Social Media Marketing and Offline Guerrilla TacticsVon EverandBranding: What You Need to Know About Building a Personal Brand and Growing Your Small Business Using Social Media Marketing and Offline Guerrilla TacticsBewertung: 5 von 5 Sternen5/5 (32)

- TikTok Algorithms 2024 $15,000/Month Guide To Escape Your Job And Build an Successful Social Media Marketing Business From Home Using Your Personal Account, Branding, SEO, InfluencerVon EverandTikTok Algorithms 2024 $15,000/Month Guide To Escape Your Job And Build an Successful Social Media Marketing Business From Home Using Your Personal Account, Branding, SEO, InfluencerBewertung: 4 von 5 Sternen4/5 (4)

- Ten Arguments for Deleting Your Social Media Accounts Right NowVon EverandTen Arguments for Deleting Your Social Media Accounts Right NowBewertung: 4 von 5 Sternen4/5 (388)

- Photographic Rendering with VRay for SketchUpVon EverandPhotographic Rendering with VRay for SketchUpBewertung: 5 von 5 Sternen5/5 (2)

- A History of Video Games in 64 ObjectsVon EverandA History of Video Games in 64 ObjectsBewertung: 4.5 von 5 Sternen4.5/5 (26)

- The No-Code Startup: The complete guide to building apps without codeVon EverandThe No-Code Startup: The complete guide to building apps without codeNoch keine Bewertungen

- Music Production for Beginners: How to Make Professional Electronic Dance Music, The Ultimate 3 in 1 Bundle for Producers (Synthesizer Explained, The Ultimate Melody Guide & Mixing EDM Music)Von EverandMusic Production for Beginners: How to Make Professional Electronic Dance Music, The Ultimate 3 in 1 Bundle for Producers (Synthesizer Explained, The Ultimate Melody Guide & Mixing EDM Music)Noch keine Bewertungen

- Kill All Normies: Online Culture Wars From 4Chan And Tumblr To Trump And The Alt-RightVon EverandKill All Normies: Online Culture Wars From 4Chan And Tumblr To Trump And The Alt-RightBewertung: 3.5 von 5 Sternen3.5/5 (126)

- Digital Gold: The Beginner's Guide to Digital Product Success, Learn Useful Tips and Methods on How to Create Digital Products and Earn Massive ProfitsVon EverandDigital Gold: The Beginner's Guide to Digital Product Success, Learn Useful Tips and Methods on How to Create Digital Products and Earn Massive ProfitsBewertung: 5 von 5 Sternen5/5 (3)

- iPhone Photography: A Ridiculously Simple Guide To Taking Photos With Your iPhoneVon EverandiPhone Photography: A Ridiculously Simple Guide To Taking Photos With Your iPhoneNoch keine Bewertungen

- Your Network Is Your Net Worth: Unlock the Hidden Power of Connections for Wealth, Success, and Happiness in the Digital AgeVon EverandYour Network Is Your Net Worth: Unlock the Hidden Power of Connections for Wealth, Success, and Happiness in the Digital AgeBewertung: 3.5 von 5 Sternen3.5/5 (43)