Beruflich Dokumente

Kultur Dokumente

DNSD 339 F

Hochgeladen von

rajeshdaveOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

DNSD 339 F

Hochgeladen von

rajeshdaveCopyright:

Verfügbare Formate

advertisement

An Autoranging True RMS Converter – Design Note 339

Philip Karantzalis and Jim Mahoney

Introduction True RMS voltage detection is most commonly required

The LTC®1966 is a true RMS-to-DC converter that uses a to measure complex amplitude and time varying signals,

∆Σ computational technique to make it dramatically sim- such as machine or engine vibration monitoring and

pler to use, significantly more accurate, lower in power complex AC power line load monitoring. Sometimes

consumption and more flexible than conventional log- these applications require accurate input signal mea-

antilog RMS-to-DC converters. The LTC1966 RMS-to-DC surement over an extremely wide dynamic range—even

converter has an input signal range from 5mVRMS to more than the 50dB range of the LTC1966. One solution

1.5VRMS (a 50dB dynamic range with a single 5V supply is to add an autoranging function to the LTC1966, thus

rail) and a 3dB bandwidth of 800kHz with signal crest , LTC and LT are registered trademarks of Linear Technology Corporation.

factors up to four.

RMS-DC CONVERTER LT1783 BUFFER

5V 84.5k

0.01µF 5V 1µF

0.1µF

4 – 2

1

0.1µF VDD LT1783 OUTPUT

499Ω 2 5 3 +

IN1 OUT

5

0.01µF LTC1966 1µF

0.1µF 0.1µF

3 6

IN2 0_RTN –5V

10k 10k EN GND VSS

5V

0.1µF WINDOW

1 8 8 1 4 7.15k 19.6k

OUT V+ COMPARATOR

2 7

AGND G2 10k

118k

PROGRAMMABLE

10µF LTC6910-2 LTC6700-1

GAIN AMPLIFIER

3 6

INPUT IN G1 400mV REF

4 5

V– G0

–5V

– + – +

2 5

0.1µF V+ 5V

0.1µF

SET GAIN

LOGIC BLOCK

(UP/DN COUNTER 1

AND CONTROL LOGIC) 5V 5V

10k 10k

GAIN TOO HIGH

DOWN RANGE

GAIN TOO LOW

UP RANGE

Q0

Q1 DIGITAL

LATCHED OUTPUTS

Q2 OUTPUTS

CLOCK Q3

5V 5V

5 1

OUT V+

1µF 1 6 LTC6900 0.1µF

VIN SHDN 4 2 1M

5V DIV GND

LTC1983-5 3

3.9Ω 2 5 SET

DN339 F01

–5V VOUT GND

10µF 10µF 3 4

C+ C–

LOOP TIMING CLOCK

1µF

NEGATIVE VOLTAGE GENERATOR

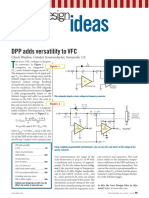

Figure 1. An Autoranging True RMS-to-DC Converter

06/04/339

effectively expanding the dynamic range of the measuring gain of 64, signals as low as 150µVRMS are converted. At

system. Versatility is certainly an advantage of this ap- the minimum gain setting of 1, the input range is 1.5VRMS.

proach. Figure 1 shows a true RMS-to-DC autoranging For a system to determine the RMS signal level both the

converter which has an input signal dynamic range of DC output and the control code must be read (digital

80dB, making it suitable to a wide range of applications. outputs Q3, Q2, Q1 and Q0).

Autoranging Expands Input Dynamic Range The circuit has three operating conditions, a linear range,

The autoranging loop of Figure 1 uses an LTC6910-2 an over range and an under range. These three conditions

programmable gain amplifier (PGA) to provide gain in are described as follows:

front of the LTC1966. Under control of a 3-bit input code, Linear range: The digital output (Q3, Q2, Q1, and Q0) is in

the LTC6910-2 provides gain in binary-weighted incre- the range 0001 to 0111 and the analog output is within the

ments (gain is set to 1, 2, 4, 8, 16, 32 or 64). An LT®1783 up-range and down-range voltage range. In the linear

op amp follower buffers the LTC1966 DC output and range, the input voltage in RMS is equal to the DC output

drives an LT6700-1-based window comparator (the voltage divided by the PGA gain. For example, if the output

LT6700-1 combines two micropower, low voltage com- voltage is 64mV and the digital code is 0111, then the

parators with a 400mV reference). The window compara- input voltage in RMS is equal to 64mV divided by 64. The

tor has two logic outputs that go low when the DC output circuit’s conversion error is less than 1% for an LTC1966

voltage extends beyond or below two preset threshold input voltage range of 50mVRMS to 1.5VRMS and

levels. The comparator outputs enable the clocking of an increases to 5% for the lowest input of 9.5mVRMS. The 1%

up/down counter that increases or decreases the front- error bandwidth is 6kHz.

end gain of the LTC6910-2 as required. An LTC6900

single resistor programmable oscillator controls the Over range: The digital output is 0000, the input signal is

response time of the autoranging loop. too high and the auto range circuit cannot provide less gain.

The 0001 to 0000 transition indicates an over range signal

Circuit Description condition. The PGA gain in this condition is set to 1.

The entire circuit is biased from a single 5V supply. The

Under range: The digital output is 1000, the input signal

input signal is AC coupled with filtering added in the

is too low and the auto range circuit cannot provide more

LTC1966 input. The autoranging true RMS-to-DC conver-

sion bandwidth is 12Hz to 32kHz. An LTC1983-5 charge gain. The transition of the digital output from 0111 to 1000

indicates an under range signal condition. The PGA gain

pump inverter provides a negative supply for the input

in this condition is set to the maximum of 64.

PGA and output buffer. This allows their inputs and

outputs to operate linearly to zero volts. The thresholds Conclusion

for the window comparator are set to 9.5mV and 1.5V. At The autoranging converter shown here expands the

power on it is assumed that there is no input signal dynamic range of the LTC1966 to 80dB, making it

present and the PGA gain is set to the maximum value of extremely versatile. This useful circuit example com-

64. When an applied signal causes the DC output to bines a variety of special function circuits available from

exceed the 1.5V down-range threshold, the gain control Linear Technology. The LTC1966 true RMS-to-DC con-

up/down counter is clocked down by one count. Any gain verter, the LTC6910-2 programmable gain amplifier, the

change is delayed by one second to ensure that the PGA LT6700-1 window comparator with built-in reference,

and LTC1966 have plenty of time to settle. The gain the LTC6900 resistor programmable oscillator, the

continues to clock down until the output signal remains LTC1983-5 charge pump voltage inverter and an LT1783

within the window. Conversely when an input signal rail-to-rail op amp are all used to handle the analog signal

magnitude is reduced to a level to cause the DC output to conditioning. The logic block shown on Figure 1 can be

fall below the 9.5mV up-range threshold, the gain is implemented with discrete logic, a low cost microcon-

clocked up to a higher value. With a maximum front-end troller or a portion of an FPGA.

Data Sheet Download

http://www.linear.com For applications help,

call (408) 432-1900, Ext. 2156

dn339f LT/TP 0604 305K • PRINTED IN THE USA

Linear Technology Corporation

1630 McCarthy Blvd., Milpitas, CA 95035-7417

(408) 432-1900 ●

FAX: (408) 434-0507 ● www.linear.com LINEAR TECHNOLOGY CORPORATION 2004

Das könnte Ihnen auch gefallen

- Flyback Controller Improves Cross Regulation For Multiple Output ApplicationsDokument2 SeitenFlyback Controller Improves Cross Regulation For Multiple Output Applications邹昊芃Noch keine Bewertungen

- High Power Synchronous Buck Converter Delivers Up To 50A: Design Note 156 Dale EagarDokument2 SeitenHigh Power Synchronous Buck Converter Delivers Up To 50A: Design Note 156 Dale Eagarghimpe--Noch keine Bewertungen

- Features: LT1010 Fast 150ma Power BufferDokument16 SeitenFeatures: LT1010 Fast 150ma Power BufferArie DinataNoch keine Bewertungen

- Features: LT1010 Fast 150ma Power BufferDokument16 SeitenFeatures: LT1010 Fast 150ma Power BufferArie DinataNoch keine Bewertungen

- Features: LT1010 Fast 150ma Power BufferDokument16 SeitenFeatures: LT1010 Fast 150ma Power BufferArie DinataNoch keine Bewertungen

- Current controls halogen lamp dimmingDokument1 SeiteCurrent controls halogen lamp dimmingB M SinghNoch keine Bewertungen

- Switching Regulator Allows Alkalines To Replace Nicads: Design Note 41 Brian HuffmanDokument2 SeitenSwitching Regulator Allows Alkalines To Replace Nicads: Design Note 41 Brian HuffmanВячеслав ГлушакNoch keine Bewertungen

- Features Description: Ltc1665/Ltc1660 Micropower Octal 8-Bit and 10-Bit DacsDokument18 SeitenFeatures Description: Ltc1665/Ltc1660 Micropower Octal 8-Bit and 10-Bit DacsKhalid BenaribaNoch keine Bewertungen

- AN-1348 LM3670 Evaluation Board: User's GuideDokument10 SeitenAN-1348 LM3670 Evaluation Board: User's GuideTesterNoch keine Bewertungen

- High Power Synchronous Buck Converter Delivers Up To 50ADokument2 SeitenHigh Power Synchronous Buck Converter Delivers Up To 50ABerat GündoğanNoch keine Bewertungen

- Linear Voltage Fan Speed Control Using Microchip's TC64X FamilyDokument4 SeitenLinear Voltage Fan Speed Control Using Microchip's TC64X FamilyAdnen GuedriaNoch keine Bewertungen

- 1154 FCDokument18 Seiten1154 FCZekeZer0xNoch keine Bewertungen

- Features Descriptio: LTC1624 High Efficiency SO-8 N-Channel Switching Regulator ControllerDokument28 SeitenFeatures Descriptio: LTC1624 High Efficiency SO-8 N-Channel Switching Regulator ControllervetchboyNoch keine Bewertungen

- dn359f PDFDokument2 Seitendn359f PDFo penNoch keine Bewertungen

- dn359f PDFDokument2 Seitendn359f PDFo penNoch keine Bewertungen

- Leadchip-Lc2127cb5tr C571475Dokument6 SeitenLeadchip-Lc2127cb5tr C571475Oscar Andres Ramirez AmayaNoch keine Bewertungen

- Iw1710-01 For 12V@1.5A Adapter DesignDokument17 SeitenIw1710-01 For 12V@1.5A Adapter DesignИван АлексиевNoch keine Bewertungen

- 1571fDokument16 Seiten1571fSanele LangaNoch keine Bewertungen

- Voltage Reference Scalling Techniques Increase The Accuaracy of The Converter As Well As The ResolutionDokument6 SeitenVoltage Reference Scalling Techniques Increase The Accuaracy of The Converter As Well As The Resolutionmehdi.bzinebNoch keine Bewertungen

- 8V To 35V, 3.0A 1ch Buck Converter With Integrated FET: DatasheetDokument21 Seiten8V To 35V, 3.0A 1ch Buck Converter With Integrated FET: DatasheetArdhi Purna bagasNoch keine Bewertungen

- 60V Step-Down DC/DC Converter Maintains High Effi Ciency: Design Note 269 Mark W. MarosekDokument2 Seiten60V Step-Down DC/DC Converter Maintains High Effi Ciency: Design Note 269 Mark W. MarosekMes BenNoch keine Bewertungen

- Clap SwitchDokument1 SeiteClap SwitchSaravana_Kumar_4984Noch keine Bewertungen

- LNK364PNDokument2 SeitenLNK364PNJose Benavides100% (2)

- Power Factor Corrector: Minidip SO8 Ordering Numbers: L6561 (Minidip) L6561D (SO8)Dokument11 SeitenPower Factor Corrector: Minidip SO8 Ordering Numbers: L6561 (Minidip) L6561D (SO8)Karim CocasNoch keine Bewertungen

- Switching From The L6561 To The L6562: AN1757 Application NoteDokument9 SeitenSwitching From The L6561 To The L6562: AN1757 Application Notedeilyn rivasNoch keine Bewertungen

- LTNB (lt1616fs)Dokument16 SeitenLTNB (lt1616fs)CeasarNoch keine Bewertungen

- LM3500 Synchronous Step-Up DC/DC Converter For White LED ApplicationsDokument26 SeitenLM3500 Synchronous Step-Up DC/DC Converter For White LED ApplicationsIngenieria MultifuncionalNoch keine Bewertungen

- M63975FPDokument5 SeitenM63975FPnk7562527Noch keine Bewertungen

- L6561Dokument11 SeitenL6561Gilson3DNoch keine Bewertungen

- Description Features: Ltc3426 1.2Mhz Step-Up DC/DC Converter in Sot-23Dokument12 SeitenDescription Features: Ltc3426 1.2Mhz Step-Up DC/DC Converter in Sot-23Carlos AntouryNoch keine Bewertungen

- Features: LT1176/LT1176-5 Step-Down Switching RegulatorDokument8 SeitenFeatures: LT1176/LT1176-5 Step-Down Switching RegulatorDreavus HashirobiNoch keine Bewertungen

- TNY278PNDokument4 SeitenTNY278PNJose BenavidesNoch keine Bewertungen

- Di-91 Design Idea Tinyswitch-Iii: 12 W Universal Input CV AdapterDokument2 SeitenDi-91 Design Idea Tinyswitch-Iii: 12 W Universal Input CV Adapterahmed chaouki ChamiNoch keine Bewertungen

- RMS-to-DC Conversion Just Got EasyDokument2 SeitenRMS-to-DC Conversion Just Got Easyzeropoint_romeoNoch keine Bewertungen

- Data Sheet MKP1584Dokument17 SeitenData Sheet MKP1584aafeletronicaNoch keine Bewertungen

- Tps 65135Dokument28 SeitenTps 65135Arthit SomrangNoch keine Bewertungen

- ML13055 Wideband FSK Receiver: Legacy Device: Motorola MC13055Dokument9 SeitenML13055 Wideband FSK Receiver: Legacy Device: Motorola MC13055StuxnetNoch keine Bewertungen

- Robot Schematic PDFDokument1 SeiteRobot Schematic PDFSaad Imran δδNoch keine Bewertungen

- Features: Lt1375/Lt1376 1.5A, 500Khz Step-Down Switching RegulatorsDokument29 SeitenFeatures: Lt1375/Lt1376 1.5A, 500Khz Step-Down Switching RegulatorsSergio MuriloNoch keine Bewertungen

- Lm3280 Adjustable Step-Down DC-DC Converter and 3 Ldos For RF Power ManagementDokument27 SeitenLm3280 Adjustable Step-Down DC-DC Converter and 3 Ldos For RF Power ManagementEliecer MenesesNoch keine Bewertungen

- Lm3280 Adjustable Step-Down DC-DC Converter and 3 Ldos For RF Power ManagementDokument26 SeitenLm3280 Adjustable Step-Down DC-DC Converter and 3 Ldos For RF Power ManagementAdi PopaNoch keine Bewertungen

- VFC PDFDokument7 SeitenVFC PDFtommy99Noch keine Bewertungen

- Features Descriptio: Lt3503 1A, 2.2Mhz Step-Down Switching Regulator in 2Mm × 3Mm DFNDokument20 SeitenFeatures Descriptio: Lt3503 1A, 2.2Mhz Step-Down Switching Regulator in 2Mm × 3Mm DFNBrett HufnagleNoch keine Bewertungen

- Williams 05 - 2000-2011 - EDNDokument215 SeitenWilliams 05 - 2000-2011 - EDNAdrian PowellNoch keine Bewertungen

- LTC6401-8 - Data SheetsDokument16 SeitenLTC6401-8 - Data Sheetsl2000316Noch keine Bewertungen

- SSM 2120 Nivel Detector dn126Dokument8 SeitenSSM 2120 Nivel Detector dn126Edson Francisco SilvaNoch keine Bewertungen

- General Description Features: 380Khz, 18V/2A Synchronous Step-Down DC-DC ConverterDokument19 SeitenGeneral Description Features: 380Khz, 18V/2A Synchronous Step-Down DC-DC Converteroscar1162001Noch keine Bewertungen

- U - LM1117, Lm1117iDokument14 SeitenU - LM1117, Lm1117iAzzar YiğesenNoch keine Bewertungen

- Skilling DocumentDokument10 SeitenSkilling DocumentMLM TELUGU GAMERSNoch keine Bewertungen

- Eecs412 Lab1Dokument4 SeitenEecs412 Lab1Josué TriveñoNoch keine Bewertungen

- Features Descriptio: LT1304/LT1304-3.3/LT1304-5 Micropower DC/DC Converters With Low-Battery Detector Active in ShutdownDokument16 SeitenFeatures Descriptio: LT1304/LT1304-3.3/LT1304-5 Micropower DC/DC Converters With Low-Battery Detector Active in ShutdownDen LunNoch keine Bewertungen

- Mic Preamplifier A008Dokument1 SeiteMic Preamplifier A008Freddy Peters100% (1)

- 1310 FsDokument12 Seiten1310 FsMohamed HaddadNoch keine Bewertungen

- Descriptio Features: LT1505 Constant-Current/Voltage High Efficiency Battery ChargerDokument16 SeitenDescriptio Features: LT1505 Constant-Current/Voltage High Efficiency Battery ChargerCarlos Henrique RibasNoch keine Bewertungen

- TMG0565 TitanMicroDokument10 SeitenTMG0565 TitanMicroekrem kayaNoch keine Bewertungen

- Ask DemodDokument28 SeitenAsk DemodHarsh mishraNoch keine Bewertungen

- 3727 FCDokument32 Seiten3727 FCtommy99Noch keine Bewertungen

- SP4403 SipexCorporationDokument14 SeitenSP4403 SipexCorporationasepNoch keine Bewertungen

- Pen Drive LoggerDokument1 SeitePen Drive LoggerrajeshdaveNoch keine Bewertungen

- PRDokument1 SeitePRrajeshdaveNoch keine Bewertungen

- Digital To Analog ConversionDokument15 SeitenDigital To Analog ConversionAbdul RaufNoch keine Bewertungen

- Product Selection Guide 1 1Dokument2 SeitenProduct Selection Guide 1 1rajeshdaveNoch keine Bewertungen

- GW - XS PLUS+ - Datasheet - EMEA-ENDokument2 SeitenGW - XS PLUS+ - Datasheet - EMEA-ENAdamu OnakpaNoch keine Bewertungen

- Soft Starters Lovato PDFDokument9 SeitenSoft Starters Lovato PDFamdatiNoch keine Bewertungen

- NES2527B-30: Gaas Mes FetDokument5 SeitenNES2527B-30: Gaas Mes FetJMFNoch keine Bewertungen

- Bosch PAViRO Controller SpecsDokument3 SeitenBosch PAViRO Controller SpecsMihai ConstantinescuNoch keine Bewertungen

- Soft Start Circuit For Peak Current Mode DC-DC ConverterDokument5 SeitenSoft Start Circuit For Peak Current Mode DC-DC ConverterHassan SharghiNoch keine Bewertungen

- Dell Se178wfpc Service Manual PDFDokument73 SeitenDell Se178wfpc Service Manual PDFBoata EtaNoch keine Bewertungen

- Remote-Controlled Home Automation System Via Bluetooth Home NetworkDokument6 SeitenRemote-Controlled Home Automation System Via Bluetooth Home NetworkLeonardoR.deOliveiraNoch keine Bewertungen

- Instruction Book Iqan-Xa2: Publ No HY17-8385-IB/UK Edition 0505Dokument38 SeitenInstruction Book Iqan-Xa2: Publ No HY17-8385-IB/UK Edition 0505Munawar DoankNoch keine Bewertungen

- RM2048XE: 2.0kW 48V DC Modular RectifiersDokument2 SeitenRM2048XE: 2.0kW 48V DC Modular Rectifiersalways_975382984100% (2)

- Price List MSRP For WEB PDFDokument3 SeitenPrice List MSRP For WEB PDFnavneetNoch keine Bewertungen

- Band Pass Filter Design for 2m Ham RadioDokument5 SeitenBand Pass Filter Design for 2m Ham RadioBoban JovanovicNoch keine Bewertungen

- FlowPulse Especificacion PDFDokument1 SeiteFlowPulse Especificacion PDFricardo4roNoch keine Bewertungen

- Design Plan NNG Feed Through CreationDokument21 SeitenDesign Plan NNG Feed Through CreationNguyen HungNoch keine Bewertungen

- Uniwill M50ea0 Rev B SCHDokument31 SeitenUniwill M50ea0 Rev B SCHshibilvNoch keine Bewertungen

- Magnetic Resonant Coupling Based Wireless PowerDokument7 SeitenMagnetic Resonant Coupling Based Wireless PowerHartantoNoch keine Bewertungen

- EE221 Ch12 SolDokument9 SeitenEE221 Ch12 SolHarish PallaNoch keine Bewertungen

- 01 Semiconductor TheoryDokument32 Seiten01 Semiconductor TheoryAnmay MishraNoch keine Bewertungen

- RRU3942 Product Description 10-06-14Dokument20 SeitenRRU3942 Product Description 10-06-14Angel Javier RuizNoch keine Bewertungen

- ERI Equipment SpecificationDokument2 SeitenERI Equipment SpecificationAnonymous gq7UQAwNoch keine Bewertungen

- CPS GRCP-User Manual-Oct 2008Dokument18 SeitenCPS GRCP-User Manual-Oct 2008Nur DiphylleiaNoch keine Bewertungen

- High Power FM MicDokument3 SeitenHigh Power FM Micmi1350Noch keine Bewertungen

- Channel Estimation TechniquesDokument37 SeitenChannel Estimation TechniquesYahia SelimNoch keine Bewertungen

- MTech ECE Syllabus of Singhania UniversityDokument18 SeitenMTech ECE Syllabus of Singhania UniversityPrashant SinhaNoch keine Bewertungen

- Power Electronics Circuits Devices and Applications by Muhammad H RashidDokument602 SeitenPower Electronics Circuits Devices and Applications by Muhammad H Rashidkartik balojiNoch keine Bewertungen

- Dell PowerEdge T420 Spec SheetDokument2 SeitenDell PowerEdge T420 Spec SheetWebAntics.com Online Shopping StoreNoch keine Bewertungen

- A History of Microwave Filter Research, Design, and DevelopmentDokument15 SeitenA History of Microwave Filter Research, Design, and Developmentsanjeevsoni64Noch keine Bewertungen

- Programming FundamentalsDokument35 SeitenProgramming FundamentalsAli SarmadNoch keine Bewertungen

- Tracker TeamDokument1.707 SeitenTracker TeamAbu Abdullah YaserNoch keine Bewertungen

- 1/2-inch MCCD sensor PAL color camerasDokument20 Seiten1/2-inch MCCD sensor PAL color camerasxiguang sunNoch keine Bewertungen

- The Potential Shake-Up in Semiconductor Manufacturing Business ModelsDokument5 SeitenThe Potential Shake-Up in Semiconductor Manufacturing Business ModelsFelipe RegisNoch keine Bewertungen

- Off-Grid Projects: Step-by-Step Guide to Building Your Own Off-Grid SystemVon EverandOff-Grid Projects: Step-by-Step Guide to Building Your Own Off-Grid SystemNoch keine Bewertungen

- CCNA: 3 in 1- Beginner's Guide+ Tips on Taking the Exam+ Simple and Effective Strategies to Learn About CCNA (Cisco Certified Network Associate) Routing And Switching CertificationVon EverandCCNA: 3 in 1- Beginner's Guide+ Tips on Taking the Exam+ Simple and Effective Strategies to Learn About CCNA (Cisco Certified Network Associate) Routing And Switching CertificationNoch keine Bewertungen

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionVon EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionBewertung: 4.5 von 5 Sternen4.5/5 (542)

- Evaluation of Some Websites that Offer Virtual Phone Numbers for SMS Reception and Websites to Obtain Virtual Debit/Credit Cards for Online Accounts VerificationsVon EverandEvaluation of Some Websites that Offer Virtual Phone Numbers for SMS Reception and Websites to Obtain Virtual Debit/Credit Cards for Online Accounts VerificationsNoch keine Bewertungen

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionVon EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionBewertung: 4 von 5 Sternen4/5 (331)

- CEH Certified Ethical Hacker Practice Exams, Third EditionVon EverandCEH Certified Ethical Hacker Practice Exams, Third EditionNoch keine Bewertungen

- Computer Networking: The Complete Beginner's Guide to Learning the Basics of Network Security, Computer Architecture, Wireless Technology and Communications Systems (Including Cisco, CCENT, and CCNA)Von EverandComputer Networking: The Complete Beginner's Guide to Learning the Basics of Network Security, Computer Architecture, Wireless Technology and Communications Systems (Including Cisco, CCENT, and CCNA)Bewertung: 4 von 5 Sternen4/5 (4)

- High Performance Loudspeakers: Optimising High Fidelity Loudspeaker SystemsVon EverandHigh Performance Loudspeakers: Optimising High Fidelity Loudspeaker SystemsBewertung: 4 von 5 Sternen4/5 (1)

- AWS Certified Solutions Architect Study Guide: Associate SAA-C02 ExamVon EverandAWS Certified Solutions Architect Study Guide: Associate SAA-C02 ExamNoch keine Bewertungen

- Computer Systems and Networking Guide: A Complete Guide to the Basic Concepts in Computer Systems, Networking, IP Subnetting and Network SecurityVon EverandComputer Systems and Networking Guide: A Complete Guide to the Basic Concepts in Computer Systems, Networking, IP Subnetting and Network SecurityBewertung: 4.5 von 5 Sternen4.5/5 (13)

- Hacking: A Beginners Guide To Your First Computer Hack; Learn To Crack A Wireless Network, Basic Security Penetration Made Easy and Step By Step Kali LinuxVon EverandHacking: A Beginners Guide To Your First Computer Hack; Learn To Crack A Wireless Network, Basic Security Penetration Made Easy and Step By Step Kali LinuxBewertung: 4.5 von 5 Sternen4.5/5 (67)

- The Compete Ccna 200-301 Study Guide: Network Engineering EditionVon EverandThe Compete Ccna 200-301 Study Guide: Network Engineering EditionBewertung: 5 von 5 Sternen5/5 (4)

- AWS Certified Cloud Practitioner Study Guide: CLF-C01 ExamVon EverandAWS Certified Cloud Practitioner Study Guide: CLF-C01 ExamBewertung: 5 von 5 Sternen5/5 (1)

- 8051 Microcontroller: An Applications Based IntroductionVon Everand8051 Microcontroller: An Applications Based IntroductionBewertung: 5 von 5 Sternen5/5 (6)

- Advanced Antenna Systems for 5G Network Deployments: Bridging the Gap Between Theory and PracticeVon EverandAdvanced Antenna Systems for 5G Network Deployments: Bridging the Gap Between Theory and PracticeBewertung: 5 von 5 Sternen5/5 (1)

- The Ultimate Kali Linux Book - Second Edition: Perform advanced penetration testing using Nmap, Metasploit, Aircrack-ng, and EmpireVon EverandThe Ultimate Kali Linux Book - Second Edition: Perform advanced penetration testing using Nmap, Metasploit, Aircrack-ng, and EmpireNoch keine Bewertungen

- Understanding Automotive Electronics: An Engineering PerspectiveVon EverandUnderstanding Automotive Electronics: An Engineering PerspectiveBewertung: 3.5 von 5 Sternen3.5/5 (16)

- Lithium-Ion Battery: The Power of Electric Vehicles with Basics, Design, Charging technology & Battery Management SystemsVon EverandLithium-Ion Battery: The Power of Electric Vehicles with Basics, Design, Charging technology & Battery Management SystemsBewertung: 5 von 5 Sternen5/5 (2)

- Computer Networking: The Complete Guide to Understanding Wireless Technology, Network Security, Computer Architecture and Communications Systems (Including Cisco, CCNA and CCENT)Von EverandComputer Networking: The Complete Guide to Understanding Wireless Technology, Network Security, Computer Architecture and Communications Systems (Including Cisco, CCNA and CCENT)Noch keine Bewertungen

- Introduction to Power System ProtectionVon EverandIntroduction to Power System ProtectionNoch keine Bewertungen

- C++ Programming Language: Simple, Short, and Straightforward Way of Learning C++ ProgrammingVon EverandC++ Programming Language: Simple, Short, and Straightforward Way of Learning C++ ProgrammingBewertung: 4 von 5 Sternen4/5 (1)

- Ramblings of a Mad Scientist: 100 Ideas for a Stranger TomorrowVon EverandRamblings of a Mad Scientist: 100 Ideas for a Stranger TomorrowNoch keine Bewertungen

- The Fast Track to Your Technician Class Ham Radio License: For Exams July 1, 2022 - June 30, 2026Von EverandThe Fast Track to Your Technician Class Ham Radio License: For Exams July 1, 2022 - June 30, 2026Bewertung: 5 von 5 Sternen5/5 (1)