Beruflich Dokumente

Kultur Dokumente

Fiche Pratique 1

Hochgeladen von

lange6810 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

14 Ansichten5 SeitenCopyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

14 Ansichten5 SeitenFiche Pratique 1

Hochgeladen von

lange681Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 5

UNIVERSITE ABDELHAMID IBN BADIS – MOSTAGANEM

FACULTE DES SCIENCES ET DE LA TECHNOLOGIE

Département Génie électrique

Fiche pratique N°1

I. Carte de développement FPGA ALTERA DE2

I. Schéma fonctionnel du panneau DE2

II. Les ressources de la carte FPGA DE2

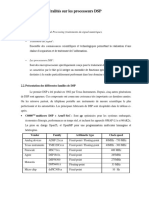

Cyclone II Device Resources EP2C35C672C6

LEs 33,216

M4K RAM blocks (4 Kbits plus 512 parity bits 105

Total RAM bits 483,840

Embedded multipliers 35

PLLs 4

Maximum user I/O pins 475

484-Pin Fine Line BGA -6, -7, -8

LAB Columns 60

LAB Rows 35

III. Dispositif de configuration de la carte de développement DE2

4.1. Configuration du FPGA en mode JTAG

La figure suivante montre l'installation de configuration de JTAG. Pour télécharger un

train de bits de configuration dans le cyclone II FPGA, exécuter les étapes suivantes :

1. S'assurer qu'est mis sous tension au panneau DE2

2. Relier le câble fourni d'USB au port USB Blaster sur le panneau DE2

3. Configurer le circuit de programmation de JTAG en plaçant le commutateur de

RUN/PROG dans la position de RUN.

4. Le FPGA peut maintenant être programmé en utilisant le module de programmeur

de Quartus II pour choisir un dossier de train de bits de configuration avec le

fichier d’extension « .sof ».

4.2. Configurant l'EPCS16 en AS mode

La figure suivante montre l’installation de configuration. Pour télécharger un train de bits

de configuration dans le dispositif d'EPCS16 EEPROM, exécuter les étapes suivantes :

1. S'assurer qu'est mis sous tension au panneau DE2

2. Relier le câble fourni d'USB au port USB Blaster sur le panneau DE2

3. Configurer le circuit de programmation de JTAG en plaçant le commutateur

RUN/PROG dans la position PROG.

4. L’EPCS16 peut maintenant être programmé en utilisant le module de programmeur

de Quartus II à choisir un dossier de train de bits de configuration avec fichier

d’extension « .pof ».

5. Une fois que l'opération de programmation est terminé, placer le commutateur

RUN/PROG de nouveau à la position RUN.

6. remettre à zéro la carte de développement DE2 ; cette action cause les nouvelles

données de configuration dans le dispositif EPCS16 d'être chargées dans l’FPGA.

IV. Logiciel de développement Quartus II

Pour plus du détail sur l’utilisation du Quartus II consulté le fichier « tut_quartus_intro_vhdl.pdf ».

5.1. Crée un nouveau programme VHDL

Note : il faut toujours nommé le fichier vhdl avec le même nom de l’entité du programme.

5.1. Crée un fichier de simulation

Remarque importante pour le VHDL

1. Dans un système à microprocesseur, les instructions sont exécutées les unes à la suite

des autres.

2. Avec VHDL il faut essayer de penser à la structure qui va être générée par le

synthétiseur pour écrire une bonne description.

3. L’assignation conditionnelle :

if condition then instructions

[elsif condition then instructions]

[else instructions]

end if ;

4. L’assignation sélective :

case signal_de_slection is

when valeur_de_sélection => instructions

[when others => instructions]

end case;

5. Affectation sélective :

with SIGNAL_DE_SELECTION select

SIGNAL <= expression when valeur_de_selection,

[expression when valeur_de_selection,]

[expression when others];

6. Affectation conditionnelle :

SIGNAL <= expression when condition

[else expression when condition]

[else expression];

7. Opérateur de concaténation : &.

S1 <= A & B & "01" ;

8. Affectation simple :

BUS <= "1001" ; -- BUS = 9 en « binaire »

BUS <= X"9" ; -- BUS = 9 en « hexadécimal »

Das könnte Ihnen auch gefallen

- TP ProjetDokument25 SeitenTP ProjetMayna LamemNoch keine Bewertungen

- TD Fpga Cs 2015Dokument5 SeitenTD Fpga Cs 2015hakim100% (1)

- Mémoire 1Dokument7 SeitenMémoire 1lange681Noch keine Bewertungen

- TP N°1 - Prise en Main de L'environnement APIDokument5 SeitenTP N°1 - Prise en Main de L'environnement APIlange681Noch keine Bewertungen

- TP N°2 DSPDokument2 SeitenTP N°2 DSPlange681Noch keine Bewertungen

- Mise en Oeuvre GrafcetDokument12 SeitenMise en Oeuvre GrafcetMohammed Amine KenedNoch keine Bewertungen

- TD1 Séquentiel-ConvertiDokument2 SeitenTD1 Séquentiel-Convertilange681Noch keine Bewertungen

- TP N°2 - Mise en Oueuvre D APIDokument4 SeitenTP N°2 - Mise en Oueuvre D APIlange681Noch keine Bewertungen

- Mémoire 1Dokument7 SeitenMémoire 1lange681Noch keine Bewertungen

- TD 4Dokument1 SeiteTD 4lange681Noch keine Bewertungen

- solution-TD N°2Dokument2 Seitensolution-TD N°2lange681Noch keine Bewertungen

- TD 2Dokument1 SeiteTD 2lange681Noch keine Bewertungen

- TP N°1 DSPDokument1 SeiteTP N°1 DSPlange681Noch keine Bewertungen

- TD 1Dokument1 SeiteTD 1lange681Noch keine Bewertungen

- TD 3Dokument1 SeiteTD 3lange681Noch keine Bewertungen

- Solution-TD N°1Dokument5 SeitenSolution-TD N°1lange681Noch keine Bewertungen

- Cours Sur Les MEMS de La Conception À La Fabrication Des MEMSDokument5 SeitenCours Sur Les MEMS de La Conception À La Fabrication Des MEMSlange681Noch keine Bewertungen

- Chapitre 4-1 DSPDokument7 SeitenChapitre 4-1 DSPlange681Noch keine Bewertungen

- Chapitre 2 DSPDokument3 SeitenChapitre 2 DSPlange681Noch keine Bewertungen

- Chapitre 3 DSPDokument4 SeitenChapitre 3 DSPlange681Noch keine Bewertungen

- TP1 PooDokument1 SeiteTP1 Poolange681Noch keine Bewertungen

- Chapitre 1 DSPDokument7 SeitenChapitre 1 DSPlange681Noch keine Bewertungen

- CHP II-La Mesure Et Les Capteurs IndustrielsDokument129 SeitenCHP II-La Mesure Et Les Capteurs Industrielslange681Noch keine Bewertungen

- Les Systèmes À Énergies AutonomesDokument5 SeitenLes Systèmes À Énergies Autonomeslange681Noch keine Bewertungen

- Proposition de Sujets ExposéDokument1 SeiteProposition de Sujets Exposélange681Noch keine Bewertungen

- Sea Cours 2 Et 3Dokument2 SeitenSea Cours 2 Et 3lange681Noch keine Bewertungen

- Solutions Desexercices duTP03Dokument12 SeitenSolutions Desexercices duTP03lange681Noch keine Bewertungen

- Tableaux Et Pointeurs en C++Dokument10 SeitenTableaux Et Pointeurs en C++lange681Noch keine Bewertungen

- TP02 Programmation Orientée ObjetDokument1 SeiteTP02 Programmation Orientée Objetlange681Noch keine Bewertungen

- TP01 Programmation Orientée ObjetDokument1 SeiteTP01 Programmation Orientée Objetlange681Noch keine Bewertungen

- TP01Dokument8 SeitenTP01lange681Noch keine Bewertungen

- M1 Ese Poo TP6Dokument1 SeiteM1 Ese Poo TP6lange681Noch keine Bewertungen

- Chap6 PDFDokument19 SeitenChap6 PDFmohcenNoch keine Bewertungen

- TD5 CircuitSequentiel3Dokument4 SeitenTD5 CircuitSequentiel3Ahmed Yacine abdelmalekNoch keine Bewertungen

- VVVF Repairing Tips Fermator DoorDokument13 SeitenVVVF Repairing Tips Fermator DoorNunFraNoch keine Bewertungen

- Le MicroprocesseurDokument34 SeitenLe MicroprocesseurLameck IkorivyizaNoch keine Bewertungen

- InformatiqueDokument3 SeitenInformatiqueMarouane TaibiniNoch keine Bewertungen

- TD3 ArchitectureDokument9 SeitenTD3 ArchitectureDhafer MezghaniNoch keine Bewertungen

- Chap I Le Microprocesseur - 2020 PDFDokument11 SeitenChap I Le Microprocesseur - 2020 PDFabnouNoch keine Bewertungen

- Cours de Program Mat Ion - Chap 01 - Carte de Test PIC16F876Dokument8 SeitenCours de Program Mat Ion - Chap 01 - Carte de Test PIC16F876soumaminoNoch keine Bewertungen

- Cours Microcontrôleur Microprocesseur 48Dokument6 SeitenCours Microcontrôleur Microprocesseur 48hafedhNoch keine Bewertungen

- 2018contrôle6800 PDFDokument4 Seiten2018contrôle6800 PDFMiiā ĘlNoch keine Bewertungen

- FAHMI TPDokument10 SeitenFAHMI TPINISSIRE FHDNoch keine Bewertungen

- Micoprocesseur - Microcontrolleur - PIC16F84Dokument90 SeitenMicoprocesseur - Microcontrolleur - PIC16F84Najwa NajmNoch keine Bewertungen

- Amplificateurs Opérationnels TD 01Dokument2 SeitenAmplificateurs Opérationnels TD 01EL Arroufy MustaphaNoch keine Bewertungen

- Les Registres de l'UALDokument6 SeitenLes Registres de l'UALhafsa midiniNoch keine Bewertungen

- DS Archi Avancees 2020Dokument3 SeitenDS Archi Avancees 2020Mohamed Ben Mustapha -Noch keine Bewertungen

- Systemes Logiques Chapitre7Dokument11 SeitenSystemes Logiques Chapitre7SamirSaSamirNoch keine Bewertungen

- Fiche de TD3 AO USTO 2023 2024 BEKKOUCHEDokument2 SeitenFiche de TD3 AO USTO 2023 2024 BEKKOUCHEkadi kadiNoch keine Bewertungen

- M15 - Logique Séquentielle GE-REEDokument58 SeitenM15 - Logique Séquentielle GE-REEKesraoui HichemNoch keine Bewertungen

- Architecture D'un Poste de TravailDokument41 SeitenArchitecture D'un Poste de Travaildualcorefree67% (3)

- Cours 6809 CIDokument121 SeitenCours 6809 CISoubkiNoch keine Bewertungen

- TP01 MicroprpcesseurDokument19 SeitenTP01 MicroprpcesseurHanae BoutabaNoch keine Bewertungen

- PageDokument17 SeitenPageSofiane AltairNoch keine Bewertungen

- Ele119 CompletDokument276 SeitenEle119 CompletayoubNoch keine Bewertungen

- Techno Tle f2Dokument134 SeitenTechno Tle f2Ange Dmi100% (2)

- RapportDokument12 SeitenRapportRajae RaNoch keine Bewertungen

- TD RévisionDokument3 SeitenTD RévisionFer DaliNoch keine Bewertungen

- Architecture Des OrdinateursDokument19 SeitenArchitecture Des Ordinateursnajla_sassi7146Noch keine Bewertungen

- Exercice de Logique SequentielleDokument30 SeitenExercice de Logique SequentielleKhawla BenzinebNoch keine Bewertungen