Beruflich Dokumente

Kultur Dokumente

Fascicule TP Systeme Logique 2 v2018

Hochgeladen von

Gharby Nour ElhoudaOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Fascicule TP Systeme Logique 2 v2018

Hochgeladen von

Gharby Nour ElhoudaCopyright:

Verfügbare Formate

Atelier système logique 2 1er Année LMD

TRAVAUX PRATIQUES N°1

Les bascules

I. Equipements :

La maquette de simulation (Simulateur logique), modules ETS-83002 et ETS-83004

Fils de connections.

II. Objectifs :

Etudier le fonctionnement des différentes bascules

III. Rappels :

Les Bascules sont des éléments bistables, c'est-à-dire des éléments ayant deux états stables

de fonctionnement .Le passage d’un état à un autre est ordonnée par un ou plusieurs

signaux de commande. Les bascules permettent la réalisation des circuits séquentiels (l’état

des sorties dépend à la fois de l’état actuel des entrées et des états antérieurs des sorties).

La bascule RS est un circuit permettant la mémorisation d’un bit, elle a deux entrées :

S pour Set (mise à un) et R pour reset (mise à zéro).

IV. Travail demandé :

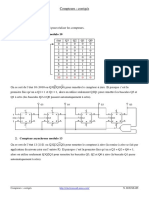

1. Réalisation d’une bascule RS asynchrone à partir des portes « NAND ».

En utilisant le bloc ETS-83004, réaliser le montage de la figure 1 en reliant les entrées 𝑆̅ et 𝑅̅ aux

interrupteurs SW1 et SW2 et les sorties Q et 𝑄̅ aux indicateurs L1 et L0.

Figure 1

a- Remplir la table de vérité réduite.

𝑆̅ 𝑅̅ Q ̅

Q Actions

ISET Nabeul 1 Génie Electrique

Atelier système logique 2 1er Année LMD

̅ ̅

b- Relier les deux entrées 𝑆 et 𝑅 à l’interrupteur d’impulsion 𝑨, donner plusieurs impulsions ̅

simultanément aux entrée 𝑆̅ et 𝑅̅ . que penser vous de la stabilité des sorties.

Conclure :

........................................................................................................................................................

........................................................................................................................................................

2. Réalisation d’une bascule RS asynchrone à partir des portes « NOR ».

En utilisant le bloc du kit ETS-83002, réaliser une bascule RS à base des portes logiques NOR

Figure 2

Shunter les jonctions :.................................................................................................

Remplir la table de vérité.

S R Q ̅

Q Actions

B=................

C=.................

D= Q

E=...............

3. Le bascule D

̅ . Elle est

La bascule D est un opérateur séquentiel, elle possède une entrée D et deux sorties Q et Q

obtenue à partir d’une bascule RS pour laquelle on impose S=𝑅̅ =D

Avec

D = entrée

CK= :...............

PR =.................

CL=..................

ISET Nabeul 2 Génie Electrique

Atelier système logique 2 1er Année LMD

a- Construction d’une bascule D à partir d’une bascule 𝑆̅ 𝑅̅

En utilisant le bloc a du kit ETS-83004 et la portes logique NAND (U2A), trouver une structure

pour réaliser la bascule D.

Remplir la table de vérité

S=D 𝑆̅=𝐷

̅ Q 𝑄̅

b- Construction d’une bascule D Flip-Flop

On veut réaliser la bascule D Flip-Flop tout en utilisant le bloc a du kit ETS-83004

Relier l’entrée J et CK aux interrupteurs SW1 et SW2.

Les sorties Q et 𝑄̅ aux diodes L1 et L2.Shunter les jonctions 2, 3, 4, 5,6 et 7.

Compléter le chronogramme suivant tout en respectant l’état de CK et l’entrée J=D.

t

CK

D t

Q t

𝑄̅

t

ISET Nabeul 3 Génie Electrique

Atelier système logique 2 1er Année LMD

Compléter le chronogramme suivant tout en respectant l’état de CK et les entrées J et K.

CK t

t

J

t

K

Q t

𝑄̅Q t

Conclure :

....................................................................................................................................................................

....................................................................................................................................................................

.......................................................................

ISET Nabeul 4 Génie Electrique

Atelier système logique 2 1er Année LMD

TRAVAUX PRATIQUES N°2

Synthèse des systèmes logiques séquentiels

asynchrones par la méthode de Huffman

A. Equipements :

- La maquette de simulation (Simulateur logique)

- Plaque à essai

- Le circuit : 7400

- Fils de connections

B. Cahier de charges

La commande d’un moteur électrique M est obtenue par l’action sur deux boutons poussoirs

(m : marche et a : arrêt)

Le fonctionnement est le suivant :

- Au repos, aucun des boutons n’est actionnées le moteur est en arrêt.

- Quand on appui sur m, on désire que le moteur se mette à tourner.

- Lorsque m est relâché le moteur continu à tourner jusqu'à l’appui sur le bouton d’arrêt a.

- Plusieurs cas à étudier pour l’action simultanée sur m et a

I. Arrêt prioritaire.

II. Marche prioritaire.

III. Priorité au changement d’état.

IV. Priorité à l’état antérieur.

C. Travail demandé :

1. Effectuer la synthèse de chaque cas par la méthode de Huffman.

2. Transformer les équations trouvées en utilisant des portes Nand à 2 entrées.

3. Tester le fonctionnement (sur plaque à essai) en remplissant une table de vérité pour chaque

cas.

Brochage du circuit 7400

ISET Nabeul 5 Génie Electrique

Atelier système logique 2 1er Année LMD

Méthode de Huffman :

ISET Nabeul 6 Génie Electrique

Atelier système logique 2 1er Année LMD

D. Documents Réponses :

I. Arrêt prioritaire.

1) Diagramme des états (des transitions) :

1

4

00 10 00 01

2 3 4

1 2 3 4

2

0 1 1 0

5 2 2 4

11 5

5 5

0

2) Matrice primitive :

ma 00 01 11 10 M

Etats

E1 4 _ 2 0

1

E2 3 _ 5 1

2

E3 4 _ 2 1

3

E4 1 5 _ 0

4

E5 _ 4 5

2 0

3) Simplification et Polygone de liaison :

1 ≠ 3 E1 E2

× ×

× E3

Groupements : E1-E4-E5 ; E2-E3

× ×

E1-E4 ; E2-E3-E5

E5 E4

4) Matrice réduite (solution N° 1) :

ma 00 01 11 10

Etats

E1 - E4 - E5 2

1 4 5

E2 - E3 4 5

3 2

ISET Nabeul 7 Génie Electrique

Atelier système logique 2 1er Année LMD

5) Matrice réduite codée :

2 Groupements = 21 c.à.d. 1 Seule Variable d’excitation secondaire x

ma 00 01 11 10

x

0 2

1 4 5

1 4 5

3 2

6) Matrice d’excitation secondaire :

ma 00 01 11 10

0 0 0 0 1

X=ā(m+x)

1 1 0 0 1 X=(ā │m) │ (ā │x )

8) Matrice de sortie :

ma 00 01 11 10

0 0 0 0 φ

M= x

1 1 φ φ 1

8) Schéma électrique : 9) Logigramme :

X m

ā &

m a

&

X M

&

&

ISET Nabeul 8 Génie Electrique

Atelier système logique 2 1er Année LMD

II. Marche prioritaire.

1) Diagramme des états (des transitions) :

2) Matrice primitive :

3) Simplification et Polygone de liaison :

...................................................................................................................................................

4) Matrice réduite (solution N° ):

5) Codage des états et Matrice réduite codée :

.............................................................................................................................

ISET Nabeul 9 Génie Electrique

Atelier système logique 2 1er Année LMD

6) Matrice d’excitation secondaire :

7) Matrice de sortie :

8) Schéma électrique : 9) Logigramme :

ISET Nabeul 10 Génie Electrique

Atelier système logique 2 1er Année LMD

III. Priorité au changement d’état:

1) Diagramme des états (des transitions) :

2) Matrice primitive :

3) Simplification et Polygone de liaison :

...................................................................................................................................................

4) Matrice réduite (solution N° ):

5) Codage des états et Matrice réduite codée :

.............................................................................................................................

ISET Nabeul 11 Génie Electrique

Atelier système logique 2 1er Année LMD

6) Matrice d’excitation secondaire :

7) Matrice de sortie :

8) Schéma électrique : 9) Logigramme :

ISET Nabeul 12 Génie Electrique

Atelier système logique 2 1er Année LMD

IV. Priorité à l’état antérieur :

1) Diagramme des états (des transitions) :

2) Matrice primitive :

3) Simplification et Polygone de liaison :

...................................................................................................................................................

4) Matrice réduite (solution N° ):

5) Codage des états et Matrice réduite codée :

.............................................................................................................................

ISET Nabeul 13 Génie Electrique

Atelier système logique 2 1er Année LMD

6) Matrice d’excitation secondaire :

7) Matrice de sortie :

8) Schéma électrique : 9) Logigramme :

ISET Nabeul 14 Génie Electrique

Atelier système logique 2 1er Année LMD

TRAVAUX PRATIQUES N°3

Les compteurs synchrones et asynchrones

I. Equipements

La maquette de simulation (Simulateur logique)

Plaque à essai

Les circuits : 7476 - 7408

Fils de connections

II. Travail demandé :

Partie I

1. Tester le fonctionnement d’une bascule JK , remplir sa table de vérité

2. Réaliser le montage suivant

3. Compléter le chromnograme et remplir le tableau des états

4. Quelle est le rôle du montage, proposer un nom.

..................................................................................................................................................................................

ISET Nabeul 15 Génie Electrique

Atelier système logique 2 1er Année LMD

5. Compléter le schéma de câblage en utilisant le brochage normalisé. Vous utiliserez une diode

électroluminescente en série avec une résistance de protection pour visualiser la sortie.

GND GND

+ VCC

74 00 7476 7476

+ Vcc

GND + Vcc

Partie II

1. Réaliser le montage suivant

2. Terminer le chromnograme et remplir le tableau des états

3. Quelle est le rôle du montage, proposer un nom.

..................................................................................................................................................................................

ISET Nabeul 16 Génie Electrique

Atelier système logique 2 1er Année LMD

Partie III

1. Réaliser le montage, compléter le chronogramme , donner son rôle et proposer un nom .

Conclure :

...................................................................................................................................

...................................................................................................................................

...................................................................................................................................

Annexes

ISET Nabeul 17 Génie Electrique

Atelier système logique 2 1er Année LMD

TRAVAUX PRATIQUES N°4

Les registres

I. Equipements :

La maquette de simulation (Simulateur logique)

Plaque à essai

Les circuits : 7474 – 7408 - 74LS194

Fils de connections

II. Travail demandé :

Partie A

1. Tester le fonctionnement d’une bascule D , remplir sa table de vérité

2. Réaliser le montage suivant

3. Compléter le chronogramme et donner le tableau des états

4. Quelle est le rôle du montage, proposer un nom.

..................................................................................................................................................................................

5. Réaliser le montage suivant

ISET Nabeul 18 Génie Electrique

Atelier système logique 2 1er Année LMD

6. Compléter le chronogramme et donner le tableau des états

7. Quelle est le rôle du montage, proposer un nom.

...................................................................................................................................................................

8. Réaliser le montage suivant

ISET Nabeul 19 Génie Electrique

Atelier système logique 2 1er Année LMD

9. Compléter le chronogramme et donner le tableau des états

10. Quelle est le rôle du montage, proposer un nom.

..................................................................................................................................................................................

11. Réaliser le montage

ISET Nabeul 20 Génie Electrique

Atelier système logique 2 1er Année LMD

12. Compléter le chronogramme et donner le tableau des états

On considéra que le signal « READ » est toujours au niveau logique haut

13. Quelle est le rôle du montage, proposer un nom.

.........................................................................................................................................................................

ISET Nabeul 21 Génie Electrique

Atelier système logique 2 1er Année LMD

14. Réaliser le montage ci-dessous puis compléter le chronogramme et donner le tableau des états

15. Quelle est le rôle du montage, proposer un nom.

.........................................................................................................................................................................

ISET Nabeul 22 Génie Electrique

Atelier système logique 2 1er Année LMD

Partie A : Registres intégrés :

1) Compléter le schéma suivant pour réaliser un registre SISO décalage à droite avec le CI : 741LS94 (Annexe1),

en prenant (E) comme entrée et (S) sortie.

2) ̅̅̅̅̅

𝑀𝑅="1",

Supposons qu’on a chargé le registre CLK SR QA QB QC QA

par (ABCD)=(O11O) avec (S1S0)=(11). 0 X 0 1 1 0

Puis on revient au mode (S1S0)=(01), 1 1

a- Que signifie ce mode ? 2 0

……………………………………………………………

b- Compléter le tableau suivant : 3 0

4 0

3) Compléter le schéma suivant pour réaliser un registre PIPO avec le CI : 741LS94 (Annexe1),

en prenant (A , B , C , D) comme entrées et (QA , QB , QC , QD) comme sorties.

ISET Nabeul 23 Génie Electrique

Atelier système logique 2 1er Année LMD

Annexe 1

ISET Nabeul 24 Génie Electrique

Atelier système logique 2 1er Année LMD

TRAVAUX PRATIQUES N°5

Les compteurs intégrés

I. Equipements :

La maquette de simulation (Simulateur logique)

Plaque à essai

Les circuits : 74LS90 - 4024 -74LS161-74LS192

Fils de connections

II. Travail demandé :

Préambule :

- Pour chaque exercice, donner le câblage et valider le fonctionnement.

1- Compteur simple :

On souhaite utiliser le compteur décimal 74LS90 pour réaliser un compteur diviseur par 10.

Le symbole et l’explication est donné ci-dessous.

Explication de la norme IEEE/ANSI utilisée pour ce composant :

R01 CTR

& CT=0

“CTR” indique un compteur. R02

R91

& Z3

“CT” indique le compteur (les sorties Q). R92

DIV 2

“CT=0” indique que si R01 . R02 = 1 , on met le compteur à 0. CKA +

QA

3CT= 1

“Z3” agit sur 3CT=1 et 3CT=3, si R91 . R92 = 1 , on met QA=1 et DIV 5

0 QB

QD =1. CKB +

CT QC

“+” indique l’horloge de comptage. 3CT=4 2 QD

Donner ci-dessous le schéma de câblage pour R01 CTR

& CT=0

obtenir un compteur diviseur par 10. R02

R91

& Z3

Valider le fonctionnement du montage. R92

DIV 2

CKA +

QA

3CT= 1

DIV 5

0 QB

CKB +

CT QC

3CT=4 2 QD

ISET Nabeul 25 Génie Electrique

Atelier système logique 2 1er Année LMD

2- Compteur à étage : CTR 7

Dans certaine application, on souhaite réaliser des diviseurs 0 Q0

CP + 1 Q1

de fréquence. On utilise alors généralement des compteurs

2 Q2

à étage.

CT Q3

Donner ci-contre le câblage pour réaliser un diviseur par 32. MR CT=0 Q4

Q5

Valider le fonctionnement du montage. Q6

6

3- Etude d’un compteur/décompteur avec CD4024

chargement parallèle asynchrone :

Dans cette partie, on utilise un compteur/décompteur 74LS192 dont les caractéristiques constructeurs sont

données en Annexe 1.

3.1. Utilisation des compteurs/décompteurs à chargement parallèle asynchrones :

Dans les exercices suivants, effectuer la saisie et la simulation des différents compteurs mis en œuvre.

Valider le fonctionnement de ces compteurs.

3.1.1. Compteur modulo 10 {0, 1, 2, …, 9} : 3.1.2. Décompteur {5, 4, …, 0} :

CT=0 CTRDIV 10 CT=0 CTRDIV 10

2+ 2+

G1 G1

1- 1-

G2 G2

C3 C3

3D 3D

1CT=9 CO 1CT=9 CO

2CT=0 BO 2CT=0 BO

ISET Nabeul 26 Génie Electrique

Atelier système logique 2 1er Année LMD

3.1.3. Réaliser le montage suivant :

Donner la fonction réalisée par ce montage : …………………………………………………………………………………..

4- Etude d’un compteur/décompteur avec chargement parallèle synchrone :

On utilise un compteur 74LS161 dont les caractéristiques sont données en Annexe 2.

Donner le schéma de câblage de ce compteur.

4.1. Compteur {0,1,…,14,15} 4.2. Compteur {10,11,…,15}

CT=0 CTR 4 CT=0 CTR 4

M1 M1

M2 M2

G3 G3

G4 G4

C5/2,3,4 + C5/2,3,4 +

1,5D 1,5D

3CT=15 3CT=15

RC0 RC0

ISET Nabeul 27 Génie Electrique

Atelier système logique 2 1er Année LMD

Annexe 1

Symbole et fonctionnement du compteur BCD (ou compteur par 10)

74LS192. CLR CT=0 CTRDIV 10

UP 2+

Explication de la norme IEEE/ANSI utilisée pour ce composant : G1 CO

1CT=9

- “CTRDIV 10” compteur /décompteur par 10 DOWN 1-

BO

2CT=0

- “CT” indique le compteur (les sorties Q) G2

LOAD C3

- “G1” entrée qui agit sur l’entrée “1-”

- “G2” entrée qui agit sur l’entrée “2+” A QA

3D

- “1-” entrée de décomptage

B QB

- “2+” entrée de comptage

- “C3” entrée qui agit sur les entrées “3D” C QC

- “1CT=9” sortie active si pas “G1” et si “CT=9” D QD

- “2CT=0” sortie active si pas “G2” et si “CT=0”

- “3D” entrées de chargement parallèle

- “Q” sortie compteur/décompteur

CLR

LOAD

UP

DOWN

QA

QB

QC

QD

CO

BO

0 7 8 9 0 1 2 1 0 9 8 7

Count UP Count DOWN

Clear Preset

ISET Nabeul 28 Génie Electrique

Atelier système logique 2 1er Année LMD

Annexe 2

Symbole et fonctionnement du compteur 4 bits (ou compteur par 16) 74LS161.

CLR CT=0 CTR 4

LOAD M1

M2

Clear outputs to zero. Asynchronous clear. ENT G3

ENP G4

CLK C5/2,3,4 +

(Synchronous clear: 74LS163)

A 1,5D QA

Preset to binary twelve.

DATA B QB DATA

Inhibit. INPUTS OUTPUTS

C QC

D QD

3CT=15 RCO

CLR

LOAD

CLK

ENP

ENT

QA

QB

QC

QD

RCO

COUNT INHIBIT

ASYNC PRESET

CLEAR

ISET Nabeul 29 Génie Electrique

Atelier système logique 2 1er Année LMD

ANNEXES

ISET Nabeul 30 Génie Electrique

Atelier système logique 2 1er Année LMD

ISET Nabeul 31 Génie Electrique

Atelier système logique 2 1er Année LMD

ISET Nabeul 32 Génie Electrique

Das könnte Ihnen auch gefallen

- Suite - Logique Séquentielle (Chapitre 6 - Chapitre 7 - Chapitre 8) - (Les Bascules - Les CompteursDokument15 SeitenSuite - Logique Séquentielle (Chapitre 6 - Chapitre 7 - Chapitre 8) - (Les Bascules - Les CompteursFares ChetouhNoch keine Bewertungen

- TD1 CLS2021Dokument3 SeitenTD1 CLS2021Nadhir BndNoch keine Bewertungen

- Correction Ex1 - 2 - 3 - 5 - 13 - 14série de FourierDokument8 SeitenCorrection Ex1 - 2 - 3 - 5 - 13 - 14série de Fourierfiras njehiNoch keine Bewertungen

- DDC - Etude Des Systèmes Échantillonnés EDokument57 SeitenDDC - Etude Des Systèmes Échantillonnés Erajaa latifiNoch keine Bewertungen

- Sujet Corrige EF Maths2 ST 18-19Dokument5 SeitenSujet Corrige EF Maths2 ST 18-19Chikhaoui AbdellahNoch keine Bewertungen

- TD 01Dokument1 SeiteTD 01Abdou HarcheNoch keine Bewertungen

- td3FIng 19-20Dokument2 Seitentd3FIng 19-20badrNoch keine Bewertungen

- Examen 2eme LPA VFDokument4 SeitenExamen 2eme LPA VFJacques JeanNoch keine Bewertungen

- Exercices AsservissementDokument4 SeitenExercices AsservissementZakaria BellahceneNoch keine Bewertungen

- TD3. Série Et Transformée de Fourier PDFDokument1 SeiteTD3. Série Et Transformée de Fourier PDFBeyaz ÇiçekNoch keine Bewertungen

- Exam CorrectionDokument7 SeitenExam CorrectionNarita JijiNoch keine Bewertungen

- Magazine 1 Filtrage Des SignauxDokument97 SeitenMagazine 1 Filtrage Des SignauxHoussein ElyatimNoch keine Bewertungen

- TD 6 (Ex Et Sol)Dokument9 SeitenTD 6 (Ex Et Sol)anass sbniNoch keine Bewertungen

- TD 03Dokument2 SeitenTD 03Soufiane SajidNoch keine Bewertungen

- Généralités Sur Les Signaux PDFDokument9 SeitenGénéralités Sur Les Signaux PDFHamdiNoch keine Bewertungen

- DevoirDokument2 SeitenDevoirIhssan KH100% (1)

- Emd9899 PDFDokument9 SeitenEmd9899 PDFJawab 24Noch keine Bewertungen

- Examen Commande Optimale 2020-2021Dokument1 SeiteExamen Commande Optimale 2020-2021zakaria zezezzeNoch keine Bewertungen

- Suite Suj Exam OP-2017-2018Dokument5 SeitenSuite Suj Exam OP-2017-2018AliOucharNoch keine Bewertungen

- Corrig EpreuveDokument9 SeitenCorrig EpreuvesalahNoch keine Bewertungen

- TD4 Stabilité SolutionDokument3 SeitenTD4 Stabilité SolutionSàmi BmNoch keine Bewertungen

- Math Pour Ling Exercice 2Dokument6 SeitenMath Pour Ling Exercice 2TECH NEWSNoch keine Bewertungen

- TD 5 SolutionDokument5 SeitenTD 5 Solutionphysiquesmp33Noch keine Bewertungen

- Chapitre 3. Analyse de FourierDokument12 SeitenChapitre 3. Analyse de FourierBeyaz ÇiçekNoch keine Bewertungen

- TD Regul PDFDokument11 SeitenTD Regul PDFSouhaib LoudaNoch keine Bewertungen

- Analyse Des Systemes Lineaires Continus Dans Le Domaine TemporelDokument17 SeitenAnalyse Des Systemes Lineaires Continus Dans Le Domaine TemporelBasma BENESSALIHNoch keine Bewertungen

- Ex Regul AsservDokument7 SeitenEx Regul Asservjaouad_ker100% (1)

- Tp3iia3 PDFDokument2 SeitenTp3iia3 PDFAziz MahfoudhiNoch keine Bewertungen

- ReseauDokument8 SeitenReseaupaulNoch keine Bewertungen

- TD2 SolutionDokument3 SeitenTD2 SolutionMedChoukairi100% (1)

- TD1 AutomatiqueDokument1 SeiteTD1 AutomatiqueSalah Eddine EL AbbadiNoch keine Bewertungen

- TD3 Sequentielle1 Corr PDFDokument17 SeitenTD3 Sequentielle1 Corr PDFAmineAbNoch keine Bewertungen

- Examen Final SEER-1+ GECSI-1 2018 2019 Pour TD de RévisionDokument1 SeiteExamen Final SEER-1+ GECSI-1 2018 2019 Pour TD de RévisionMounaim MatiniNoch keine Bewertungen

- TDTDDokument110 SeitenTDTDIbtissem DERRARNoch keine Bewertungen

- TD7 - Traitement de Singal - 2018 - 2019Dokument9 SeitenTD7 - Traitement de Singal - 2018 - 2019nait ahmed hasnaNoch keine Bewertungen

- Chapitre 1 2 Algebre de Boole Et Fonctions LogiquesDokument20 SeitenChapitre 1 2 Algebre de Boole Et Fonctions LogiquesIddir YuderNoch keine Bewertungen

- TPs Automatique 1Dokument6 SeitenTPs Automatique 1HolaNoch keine Bewertungen

- TD 1 - SMP-S6Dokument1 SeiteTD 1 - SMP-S6Said Boustta100% (1)

- TD 1 - Traitement Du SignalDokument2 SeitenTD 1 - Traitement Du SignalMohamed DjezzarNoch keine Bewertungen

- Selection C PDFDokument166 SeitenSelection C PDFMalick DiopNoch keine Bewertungen

- Aut215 PDFDokument197 SeitenAut215 PDFKhalil HsaineNoch keine Bewertungen

- TD7: Séries de Fourier: Bts Esa Prof: Ismail OuariagliDokument3 SeitenTD7: Séries de Fourier: Bts Esa Prof: Ismail OuariagliCrazy ytNoch keine Bewertungen

- Final Ele1300 h2008Dokument11 SeitenFinal Ele1300 h2008Youssef YoussefNoch keine Bewertungen

- E C Bascules D 3 Merged FAITDokument9 SeitenE C Bascules D 3 Merged FAITMohamed MathématicienNoch keine Bewertungen

- Dimension D'un Espace Vectoriel: Exercice 1Dokument8 SeitenDimension D'un Espace Vectoriel: Exercice 1Judicaël SekaNoch keine Bewertungen

- Chapitre II - SNL - Plan de PhaseDokument68 SeitenChapitre II - SNL - Plan de PhaseThinhinane KaguyaNoch keine Bewertungen

- Fiche Transformée de Laplace 2010-2011 RDokument4 SeitenFiche Transformée de Laplace 2010-2011 RRodrigue patrice Njounhassi koagneNoch keine Bewertungen

- Correction TD 1Dokument6 SeitenCorrection TD 1Ameny MellahNoch keine Bewertungen

- Séries Numériques 17Dokument73 SeitenSéries Numériques 17Anonymous mq6GyX3rjNoch keine Bewertungen

- Cours - S1 - EI - LogiqueCombinatoire - Chapitre IIIDokument10 SeitenCours - S1 - EI - LogiqueCombinatoire - Chapitre IIIoudjouadjNoch keine Bewertungen

- TD1signal IGTT1 2012Dokument2 SeitenTD1signal IGTT1 2012sevemasseNoch keine Bewertungen

- TD 1: Systèmes Logiques Et Architecture Des Ordinateurs: Filière: 1 Année Licence InformatiqueDokument4 SeitenTD 1: Systèmes Logiques Et Architecture Des Ordinateurs: Filière: 1 Année Licence Informatique4qh5xx7g6vNoch keine Bewertungen

- A1TDS22 TD3 Suite CorrigéDokument10 SeitenA1TDS22 TD3 Suite CorrigéBoualem MestafaNoch keine Bewertungen

- TD4 CorrigéDokument4 SeitenTD4 CorrigéNorbert DurandNoch keine Bewertungen

- Espaces Préhilbertiens - Distance À Un Sous-Espace VectorielDokument3 SeitenEspaces Préhilbertiens - Distance À Un Sous-Espace VectorielHamza PrintoOsNoch keine Bewertungen

- 144 Tdautomatique Tsi SpeDokument4 Seiten144 Tdautomatique Tsi SpeYoussef SadikNoch keine Bewertungen

- C CompteursDokument7 SeitenC CompteursyayaNoch keine Bewertungen

- Corrige Epreuves de Math2017 GenieDokument3 SeitenCorrige Epreuves de Math2017 GenieGharby Nour ElhoudaNoch keine Bewertungen

- Systeme LogiqueDokument19 SeitenSysteme LogiqueGharby Nour ElhoudaNoch keine Bewertungen

- TP ManagementDokument14 SeitenTP ManagementGharby Nour ElhoudaNoch keine Bewertungen

- TP CaoDokument4 SeitenTP CaoGharby Nour Elhouda100% (1)

- DomotiqueDokument7 SeitenDomotiqueGharby Nour ElhoudaNoch keine Bewertungen

- TD Systeme Temps RéelDokument4 SeitenTD Systeme Temps RéelGharby Nour ElhoudaNoch keine Bewertungen

- Plan D'affaireDokument14 SeitenPlan D'affaireGharby Nour ElhoudaNoch keine Bewertungen

- Exercice 1Dokument1 SeiteExercice 1Gharby Nour ElhoudaNoch keine Bewertungen

- Exercice 2Dokument3 SeitenExercice 2Gharby Nour ElhoudaNoch keine Bewertungen

- Compte Rendu TP 2Dokument3 SeitenCompte Rendu TP 2Gharby Nour ElhoudaNoch keine Bewertungen

- Commentaire LittéraireDokument2 SeitenCommentaire LittéraireMalorie ArnaultNoch keine Bewertungen

- MSD TP 3Dokument19 SeitenMSD TP 3Maroua LHNoch keine Bewertungen

- CITROËN Berlingo PEUGEOT Partner (11/2002Dokument5 SeitenCITROËN Berlingo PEUGEOT Partner (11/2002JeanFrancoisFigueroa67% (3)

- Planif HAFF Livre Encyclopedie Prépa PhyiqueDokument14 SeitenPlanif HAFF Livre Encyclopedie Prépa PhyiqueNicolas OlvNoch keine Bewertungen

- Chamoa P PsidpDokument147 SeitenChamoa P PsidpMustapha FejjiNoch keine Bewertungen

- Flux Complet Sur SAP MM-PP-SDDokument34 SeitenFlux Complet Sur SAP MM-PP-SDranya ochiNoch keine Bewertungen

- Dictionnaire Des Mots SavantsDokument183 SeitenDictionnaire Des Mots Savantsbradbader100% (2)

- Guide Eth PDFDokument41 SeitenGuide Eth PDFparfaitNoch keine Bewertungen

- COMB W5 711E OX DC 308L IX A+ WHIRLPOOL ElectroDokument1 SeiteCOMB W5 711E OX DC 308L IX A+ WHIRLPOOL ElectroMohamedm38Noch keine Bewertungen

- Emplois Du Temps Filière LST - S5Dokument12 SeitenEmplois Du Temps Filière LST - S5Ab'Dél AliNoch keine Bewertungen

- Transformation Lente Et Rapide: ActivitésDokument6 SeitenTransformation Lente Et Rapide: ActivitésAbd Elmooti HijaziNoch keine Bewertungen

- Les Codes de La SeductionDokument7 SeitenLes Codes de La SeductionFernando RamosNoch keine Bewertungen

- Construire en Vienne Le Mag'Dokument76 SeitenConstruire en Vienne Le Mag'eloise_joyeuxNoch keine Bewertungen

- Etude de Cas MIRLACDokument4 SeitenEtude de Cas MIRLACAwa Fleur YattaraNoch keine Bewertungen

- Eclairagisme Public Au Maroc (Autosaved)Dokument8 SeitenEclairagisme Public Au Maroc (Autosaved)Tb SoufianeNoch keine Bewertungen

- Exercices SGBDDokument2 SeitenExercices SGBDAsma100% (2)

- These Adal AhnaibaDokument618 SeitenThese Adal Ahnaibamohamedcadif2023Noch keine Bewertungen

- Ali El AbadiDokument18 SeitenAli El AbadiAli El abadiNoch keine Bewertungen

- KP1394+KP SeriesDokument4 SeitenKP1394+KP SeriesRavaglioliNoch keine Bewertungen

- Corrigé - Exam Comp Principal 2019 2020Dokument6 SeitenCorrigé - Exam Comp Principal 2019 2020Héroïne CNNoch keine Bewertungen

- Automatisme Pour Portails Battants Bl3924mcb Moteur Portail Battant Cardin 24v Notice CardinDokument48 SeitenAutomatisme Pour Portails Battants Bl3924mcb Moteur Portail Battant Cardin 24v Notice Cardin45x2phh5j9Noch keine Bewertungen

- 459268execution de Chapes Le Document PDFDokument6 Seiten459268execution de Chapes Le Document PDFmoulawainNoch keine Bewertungen

- Calcul HydrologiqueDokument7 SeitenCalcul HydrologiqueFatre 1980Noch keine Bewertungen

- WSP With SharePointDokument16 SeitenWSP With SharePointMuta BarukaNoch keine Bewertungen

- 07 Corrigé Du Sujet Bac SC 2014pDokument2 Seiten07 Corrigé Du Sujet Bac SC 2014pAlaa MiledNoch keine Bewertungen

- Naissance D'une Fonction: Audit InterneDokument52 SeitenNaissance D'une Fonction: Audit InterneYassine SalmiNoch keine Bewertungen

- Reconnaissance CRSDokument26 SeitenReconnaissance CRSGaspard GlanzNoch keine Bewertungen

- CH VII. DéversementDokument7 SeitenCH VII. DéversementAli EmbarecNoch keine Bewertungen

- TD8 Energie Notions EssentiellesDokument4 SeitenTD8 Energie Notions EssentiellesMOUSS LOUSSNoch keine Bewertungen

- L'identité Cachée Dans L'empreinte DigitaleDokument2 SeitenL'identité Cachée Dans L'empreinte DigitalebainkssNoch keine Bewertungen