Beruflich Dokumente

Kultur Dokumente

Logika Kombinasi II (Lie)

Hochgeladen von

Fahmi MhuyOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Logika Kombinasi II (Lie)

Hochgeladen von

Fahmi MhuyCopyright:

Verfügbare Formate

CSE221- Logic Design, Spring 2003 5-May-09

EE207: Digital Systems I,

Semester I 2003/2004

CHAPTER 3 -iii:

Combinational Logic Design –

Multiplexers/Demultiplexers

(Sections 3.7)

Overview

n Multiplexers (MUXs

(MUXs))

n Functionality

n Circuit implementation with MUXs

n Demultiplexers

5-May-09 Chapter 3 -iii: Combinational Logic Design (3.7) 2

Chapter 3-iii: Combinational Logic Design

(Section 3.7) 1

CSE221- Logic Design, Spring 2003 5-May-09

Multiplexer

n “Selects

Selects”” binary information from one of

many input lines and directs it to a single

output line.

n Also known as the “selector

selector”” circuit,

n Selection is controlled by a particular set of

inputs lines whose # depends on the # of the

data input lines.

n For a 2 n-to

to--1 multiplexer, there are 2n data

input lines and n selection lines whose bit

combination determines which input is

selected.

5-May-09 Chapter 3 -iii: Combinational Logic Design (3.7) 3

MUX

Enable

2n Data Data

Inputs Output

Input

Select

5-May-09 Chapter 3 -iii: Combinational Logic Design (3.7) 4

Chapter 3-iii: Combinational Logic Design

(Section 3.7) 2

CSE221- Logic Design, Spring 2003 5-May-09

Remember the 2 – 4 Decoder?

Sel(3)

S1

Sel(2)

S0 Sel(1)

Sel(0)

Mutually Exclusive

(Only one O/P asserted

at any time

5-May-09 Chapter 3 -iii: Combinational Logic Design (3.7) 5

4 to 1 MUX

DataFlow

D3:D0

Dout

4

Control

4

2-4

Decoder

Sel(3:0)

2

S1:S0

5-May-09 Chapter 3 -iii: Combinational Logic Design (3.7) 6

Chapter 3-iii: Combinational Logic Design

(Section 3.7) 3

CSE221- Logic Design, Spring 2003 5-May-09

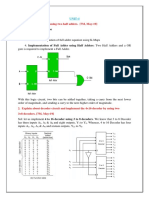

4-to-1 MUX (Gate level)

Control Section

Three of these signal

inputs will always be 0.

The other will depend on

the data value selected

5-May-09 Chapter 3 -iii: Combinational Logic Design (3.7) 7

Multiplexer (cont.)

n Until now, we have examined single-

single- bit

data selected by a MUX. What if we

want to select m-

m-bit data/words?

à Combine MUX blocks in parallel with

common select and enable signals

n Example: Construct a logic circuit that

selects between 2 sets of 4-

4- bit inputs

(see next slide for solution).

5-May-09 Chapter 3 -iii: Combinational Logic Design (3.7) 8

Chapter 3-iii: Combinational Logic Design

(Section 3.7) 4

CSE221- Logic Design, Spring 2003 5-May-09

Example: Quad 2-to-1 MUX

n Uses four 4- 4-to

to--1

MUXs with

common select (S)

and enable (E).

n Select line chooses

between Ai ’s and

Bi ’s. The selected

four--wire digital

four

signal is sent to

the Yi ’s

n Enable line turns

MUX on and off

(E=1 is on).

5-May-09 Chapter 3 -iii: Combinational Logic Design (3.7) 9

Implementing Boolean functions

with Multiplexers

n Any Boolean function of n variables can

be implemented using a 2n -1-to

to--1

multiplexer. A MUX is basically a

decoder with outputs ORed together,

hence this isn’

isn’t surprising.

n The SELECT signals generate the

minterms of the function.

n The data inputs identify which minterms

are to be combined with an OR.

5-May-09 Chapter 3 -iii: Combinational Logic Design (3.7) 10

Chapter 3-iii: Combinational Logic Design

(Section 3.7) 5

CSE221- Logic Design, Spring 2003 5-May-09

Example

•F(X,Y,Z) = X’Y’Z + X’YZ’ + XYZ’ + XYZ = Sm(1,2,6,7)

•There are n=3 inputs, thus we need a 22-toto--1 MUX

•The first n-

n-1 (=2) inputs serve as the selection lines

5-May-09 Chapter 3 -iii: Combinational Logic Design (3.7) 11

Efficient Method for

implementing Boolean functions

n For an n-variable function (e.g (e.g.,

., f(A,B,C,D)):

n Need a 2n-1 line MUX with n-1 select lines.

n Enumerate function as a truth table with

consistent ordering of variables (e.g. (e.g.,, A,B,C,D)

n Attach the most significant n-1 variables to the n-1

select lines (e.g.

(e.g.,, A,B,C)

n Examine pairs of adjacent rows (only the least

significant variable differs, e.g. e.g.,, D=0 and D=1).

n Determine whether the function output for the

(A,B,C,0) and (A,B,C,1) combination is (0,0), (0,1),

(1,0), or (1,1).

n Attach 0, D, D’ D’, or 1 to the data input

corresponding to (A,B,C) respectively.

5-May-09 Chapter 3 -iii: Combinational Logic Design (3.7) 12

Chapter 3-iii: Combinational Logic Design

(Section 3.7) 6

CSE221- Logic Design, Spring 2003 5-May-09

Another Example

n Consider F(A,B,C) = ∑ m(1,3,5,6). We can

implement this function using a 4-4-to

to--1

MUX as follows.

n The index is ABC. Apply A and B to the

S1 and S 0 selection inputs of the MUX

(A is most sig, S 1 is most sig.)

n Enumerate function in a truth table.

5-May-09 Chapter 3 -iii: Combinational Logic Design (3.7) 13

MUX Example (cont.)

A B C F

0 0 0 0

When A=B=0, F=C 0 0 1 1

0 1 0 0

When A=0, B=1, F=C 0 1 1 1

1 0 0 0

When A=1, B=0, F=C 1 0 1 1

1 1 0 1

When A=B=1, F=C’ 1 1 1 0

5-May-09 Chapter 3 -iii: Combinational Logic Design (3.7) 14

Chapter 3-iii: Combinational Logic Design

(Section 3.7) 7

CSE221- Logic Design, Spring 2003 5-May-09

MUX implementation of F(A,B,C)

= ∑m(1,3,5,6)

A

B

C

C

F

C

C’

5-May-09 Chapter 3 -iii: Combinational Logic Design (3.7) 15

Or Simply….

C 11

C 10

F

C 01

C 00

A B

5-May-09 Chapter 3 -iii: Combinational Logic Design (3.7) 16

Chapter 3-iii: Combinational Logic Design

(Section 3.7) 8

CSE221- Logic Design, Spring 2003 5-May-09

A larger Example

5-May-09 Chapter 3 -iii: Combinational Logic Design (3.7) 17

MUX as a Universal Gate

n We can construct OR, AND, and NOT gates

using 2-

2-to

to--1 MUXs

MUXs.. Thus, 2-

2 -to

to--1 MUX is a

universal gate.

NOT AND

OR

x1

z = x 1+ x 1’x0 z = 0x + 1x’ = x’ z = x 1x 0 + 0x 0’ = x 1x 0

= x 1x 0’ + x 1x 0 + x 1’x0 = x 1 + x 0

5-May-09 Chapter 3 -iii: Combinational Logic Design (3.7) 18

Chapter 3-iii: Combinational Logic Design

(Section 3.7) 9

CSE221- Logic Design, Spring 2003 5-May-09

Demultiplexers (DMUX)

n Performs the inverse of a multiplexing

operation:

n Receives data from a single line

n

n Transmit it to one of the 2 possible output

lines

n Selection of a specific output is controlled

by the n select lines

n Demultiplexers are basically decoders! For

example, a 2-

2 -to

to--4 DMUX is a 2-

2-to

to--4

decoder with enable input.

5-May-09 Chapter 3 -iii: Combinational Logic Design (3.7) 19

Chapter 3-iii: Combinational Logic Design

(Section 3.7) 10

Das könnte Ihnen auch gefallen

- Multiplexer and DemultiplexerDokument5 SeitenMultiplexer and DemultiplexerAdebayo AdebariNoch keine Bewertungen

- 16-1 Mux Using 8-1 Mux, 4-1mux, and 2-1 MuxDokument4 Seiten16-1 Mux Using 8-1 Mux, 4-1mux, and 2-1 Muxsatishbojjawar148458% (19)

- Analog Implementation of The Soft-Max FunctionDokument4 SeitenAnalog Implementation of The Soft-Max Function曾惟Noch keine Bewertungen

- Chapter4: Combinational Logic: Originally by Reham S. Al-MajedDokument14 SeitenChapter4: Combinational Logic: Originally by Reham S. Al-Majedرغوووودي رغووووديNoch keine Bewertungen

- MultiplexerDokument16 SeitenMultiplexerPARTEEK RANANoch keine Bewertungen

- 271 7Dokument0 Seiten271 7Usman Sabir100% (1)

- CS 8351 Digital Principles and System Design: MultiplexersDokument25 SeitenCS 8351 Digital Principles and System Design: Multiplexerspadmaa1Noch keine Bewertungen

- Efficient Multiplexer Synthesis TechniquesDokument8 SeitenEfficient Multiplexer Synthesis TechniquesModin HbNoch keine Bewertungen

- Implementing Boolean Function Over Multiplexer: ObjectivesDokument3 SeitenImplementing Boolean Function Over Multiplexer: ObjectivesALviNoch keine Bewertungen

- Identification of MIMO Systems by TS Fuzzy Models: Input-OutputDokument6 SeitenIdentification of MIMO Systems by TS Fuzzy Models: Input-Outputchoc_ngoay1Noch keine Bewertungen

- MATLAB Programming Tutorial - Version 05-: Electromagnetic Fields Theory (BEE3113)Dokument32 SeitenMATLAB Programming Tutorial - Version 05-: Electromagnetic Fields Theory (BEE3113)Johnjoseph Vera100% (1)

- Com Bi National LogicDokument168 SeitenCom Bi National LogicpinokyuNoch keine Bewertungen

- Design A Full Adder by Using Two Half Adders. (7M, May-19)Dokument10 SeitenDesign A Full Adder by Using Two Half Adders. (7M, May-19)Sri Silpa Padmanabhuni100% (1)

- EE2174: Digital Logic and LabDokument48 SeitenEE2174: Digital Logic and LabPRAVIN GNoch keine Bewertungen

- Multiplexer and De-Multiplexer: Rab Nawaz Khan JadoonDokument31 SeitenMultiplexer and De-Multiplexer: Rab Nawaz Khan JadoonMuhammad ShahbazNoch keine Bewertungen

- FRP PDFDokument19 SeitenFRP PDFmsl_cspNoch keine Bewertungen

- Digital Basic - 1 PDFDokument6 SeitenDigital Basic - 1 PDFjeravi84Noch keine Bewertungen

- 03-CS Space Division Switching 1ppsDokument60 Seiten03-CS Space Division Switching 1ppsRaghav ChaudharyNoch keine Bewertungen

- Design of Spreading Permutations For MIMO-CDMA Based On Space-Time Block CodesDokument3 SeitenDesign of Spreading Permutations For MIMO-CDMA Based On Space-Time Block CodesBalaram KvNoch keine Bewertungen

- Lab 10 Mux & DeMuxDokument9 SeitenLab 10 Mux & DeMuxsafdarmunir070Noch keine Bewertungen

- FPGA Implementation of Soft Output Viterbi Algorithm Using Memoryless Hybrid Register Exchange MethodDokument9 SeitenFPGA Implementation of Soft Output Viterbi Algorithm Using Memoryless Hybrid Register Exchange MethodAnonymous e4UpOQEPNoch keine Bewertungen

- Efficient Implementation of A Pseudorandom Sequence Generator For High-Speed Data CommunicationsDokument8 SeitenEfficient Implementation of A Pseudorandom Sequence Generator For High-Speed Data CommunicationsRekhaPadmanabhanNoch keine Bewertungen

- Soft-Output Sphere Decoding Performance and Implementation Aspects PDFDokument6 SeitenSoft-Output Sphere Decoding Performance and Implementation Aspects PDFTiến Anh VũNoch keine Bewertungen

- A Software For S-Box Performance Analysis and TestDokument4 SeitenA Software For S-Box Performance Analysis and TestAgustin Aboytes100% (1)

- Question BankDokument6 SeitenQuestion BankPrashantyelekarNoch keine Bewertungen

- CMPS Lab ManualDokument64 SeitenCMPS Lab Manualomi ChavanNoch keine Bewertungen

- Large Margin Multi Channel Analog To Digital Conversion With Applications To Neural ProsthesisDokument8 SeitenLarge Margin Multi Channel Analog To Digital Conversion With Applications To Neural ProsthesisAdrian PostavaruNoch keine Bewertungen

- EE6301 DLC Unit 2 Part A Q&ADokument6 SeitenEE6301 DLC Unit 2 Part A Q&AVigneswaran VigneshNoch keine Bewertungen

- Eecs 967 - Project Mmse Multiuser Detection: Vijaya Chandran Ramasami (Kuid 698659)Dokument34 SeitenEecs 967 - Project Mmse Multiuser Detection: Vijaya Chandran Ramasami (Kuid 698659)Aseem RaseedNoch keine Bewertungen

- Solutions Manual For Digital Communications in PracticeDokument48 SeitenSolutions Manual For Digital Communications in PracticecasdeaNoch keine Bewertungen

- Meshfree Shape Function From Moving Least SquareDokument13 SeitenMeshfree Shape Function From Moving Least SquareJeetender Singh KushawahaNoch keine Bewertungen

- Optimal Power Consumption For Co-Operative Adhoc NetworkDokument4 SeitenOptimal Power Consumption For Co-Operative Adhoc NetworkseventhsensegroupNoch keine Bewertungen

- (System) Verilog Tutorial: Aleksandar MilenkovićDokument56 Seiten(System) Verilog Tutorial: Aleksandar MilenkovićAbhinav TallapallyNoch keine Bewertungen

- DSP - Manual PartDokument12 SeitenDSP - Manual PartShivani AgarwalNoch keine Bewertungen

- Enumeration of The Minimal Node Cutsets Based On Necessary Minimal PathsDokument8 SeitenEnumeration of The Minimal Node Cutsets Based On Necessary Minimal PathsIAES IJAINoch keine Bewertungen

- Interconnection Networks: Crossbar Switch, Which Can Simultaneously Connect Any Set ofDokument11 SeitenInterconnection Networks: Crossbar Switch, Which Can Simultaneously Connect Any Set ofgk_gbuNoch keine Bewertungen

- Question Bank For Digital Signal Processing Regulation 2013Dokument8 SeitenQuestion Bank For Digital Signal Processing Regulation 2013PRIYA RAJINoch keine Bewertungen

- Multiplexer and DemultiplexerDokument12 SeitenMultiplexer and Demultiplexermarck_camamaNoch keine Bewertungen

- TG10 2Dokument5 SeitenTG10 2m0hmdNoch keine Bewertungen

- Mux Ra1911004010178Dokument10 SeitenMux Ra1911004010178Shivanshu TripathiNoch keine Bewertungen

- DocumentDokument50 SeitenDocumentPragati PriyadarshineeNoch keine Bewertungen

- Floating-Point Bitwidth Analysis Via Automatic DifferentiationDokument8 SeitenFloating-Point Bitwidth Analysis Via Automatic Differentiationarthur-pham-5188Noch keine Bewertungen

- Building Blocks For Digital Design: Adders, Registers, and MultiplexersDokument33 SeitenBuilding Blocks For Digital Design: Adders, Registers, and Multiplexerspkn.11ee56Noch keine Bewertungen

- Software Process and RequirementDokument25 SeitenSoftware Process and RequirementUnicorn54Noch keine Bewertungen

- Using The Confusion Matrix For Improving Ensemble ClassifiersDokument5 SeitenUsing The Confusion Matrix For Improving Ensemble ClassifiersRitu YadavNoch keine Bewertungen

- A Novel Architecture of RNS Based Lifting Integer Wavelet Transform (Iwt) and Comparative Study With Other Binary and Non-Binary DWTDokument9 SeitenA Novel Architecture of RNS Based Lifting Integer Wavelet Transform (Iwt) and Comparative Study With Other Binary and Non-Binary DWTAnonymous e4UpOQEPNoch keine Bewertungen

- ECE522 Pre-Test1 SolutionsDokument11 SeitenECE522 Pre-Test1 SolutionsJohnny Tagal100% (1)

- Paper 3Dokument10 SeitenPaper 3RakeshconclaveNoch keine Bewertungen

- Mayo: Optimized Implementation With Revised Parameters For Armv7-MDokument22 SeitenMayo: Optimized Implementation With Revised Parameters For Armv7-Mandre moreiraNoch keine Bewertungen

- Combinational Circuits Part IIDokument8 SeitenCombinational Circuits Part IIchans08Noch keine Bewertungen

- LCS Lab 3Dokument14 SeitenLCS Lab 3Zainab AshrafNoch keine Bewertungen

- Hoang 2017Dokument12 SeitenHoang 2017Luis Martínez RamírezNoch keine Bewertungen

- Multiplexer and DemultiplexerDokument18 SeitenMultiplexer and DemultiplexerTara SharmaNoch keine Bewertungen

- EE2174: Digital Logic and LabDokument48 SeitenEE2174: Digital Logic and LabPrathap VuyyuruNoch keine Bewertungen

- The Matlab ... : OverviewDokument6 SeitenThe Matlab ... : OverviewUsama JavedNoch keine Bewertungen

- Analytical Modeling of Wireless Communication SystemsVon EverandAnalytical Modeling of Wireless Communication SystemsNoch keine Bewertungen

- Integer Optimization and its Computation in Emergency ManagementVon EverandInteger Optimization and its Computation in Emergency ManagementNoch keine Bewertungen

- Multiple Models Approach in Automation: Takagi-Sugeno Fuzzy SystemsVon EverandMultiple Models Approach in Automation: Takagi-Sugeno Fuzzy SystemsNoch keine Bewertungen

- Kronecker Products and Matrix Calculus with ApplicationsVon EverandKronecker Products and Matrix Calculus with ApplicationsNoch keine Bewertungen