Beruflich Dokumente

Kultur Dokumente

VLSI Design

Hochgeladen von

qwertyuiopOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

VLSI Design

Hochgeladen von

qwertyuiopCopyright:

Verfügbare Formate

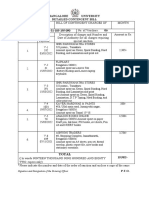

EC1354 VLSI DESIGN

KINGS

COLLEGE OF ENGINEERING

DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

QUESTION BANK

SUB.NAME : VLSI DESIGN SUBJECT CODE : EC 1354

BRANCH : EEE YEAR / SEMESTER : III / VI

______________________________________________________________ _

UNIT – I

MOS TRANSISTOR THEORY AND PROCESS TECHNOLOGY

PART-A

1. What is meant by “Epitaxy”?

2. What is isolation?

3. What is the special feature of Twin-Tub process?

4. What are the various processes used in SOI?

5. What is siliside?

6. What is LDD?

7. What is LOCOS?

8. Give the advantages of IC?

9. What is Depletion mode Device?

10. Name the four generations of Integration Circuits?

11. Name the types of Integrated Circuits?

12. Give the basic process for IC fabrication.

13. What are the various steps in Silicon wafer preparation?

14. What are the advantages of Silicon-on-Insulator process?

15. What are the advantages of CMOS process?

16. What are the different MOS layers?

17. Why NMOS technology is preferred more than PMOS technology?

18. What are the different operating regions an MOS transistor?

Kings College of Engineering, Punalkulam

EC1354 VLSI DESIGN

PART-B

1. a) Explain the operation of NMOS Enhancement transistor? (8)

b) Derive the Threshold voltage for NMOS Enhancement transistor? (8)

2. a) Explain about the body effect of MOS transistors. (6)

b) Derive the design equations for MOS devices (4)

c) What do you mean by channel length modulation (6)

3. a) Explain the second order effects with their equations. (10)

b) Explain small signal AC characteristics with its design equations. (6)

4. Explain the fabrication of PMOS transistor and its substrate fabrication Process.

(16)

5. Explain different fabrication process of CMOS transistor (16)

UNIT-II

INVERTERS AND LOGIC GATES

PART-A

1. Define noise margin.

2. Define Rise Time.

3. What is body effect?

4. What is low noise margin?

5. What is stick diagram?

6. What are Lambda (O) - based design rules?

7. Define a super buffer.

8. Give the CMOS inverter DC transfer characteristics and operating regions

9. Give the various color coding used in stick diagram?

10. Define Delay time

11. Give the different symbols for transmission gate.

12. Compare between CMOS and bipolar technologies.

13. What are the static properties of complementary CMOS Gates?

14. Draw the circuit of a nMOS inverter

15. Draw the circuit of a CMOS inverter

Kings College of Engineering, Punalkulam

EC1354 VLSI DESIGN

PART-B

1. List out the layout design rule. Draw the physical layout for one basic gate and two

universal gates. (16)

2. Explain the complimentary CMOS inverter DC characteristics. (16)

3. Write short notes on:

(a) Noise Margin (10)

(b) Rise Time (3)

(c) Fall Time (3)

4. Briefly discuss about the following:

a) Pseudo-NMOS inverter (8)

b) Saturated Load inverters (4)

c) Cascade inverter (4)

5. a. Explain the concept of static and dynamic CMOS design (8)

b. Explain the construction and operation of transmission gates (8)

UNIT III

CIRCUIT CHARACTERISATION AND PERFORMANCE ESTIMATION

PART-A

1. What are the issues to be considered for circuit characterization and performance

estimation?

2. Give the formula for resistance of a uniform slab of conducting material.

3. What are the factors to be considered for calculating total load capacitance on the

output of a CMOS gate?

4. What are the components of Power dissipation?

5. What is meant by path electrical effort?

6. Define crosstalk.

7. Define scaling.

8. What are the factors to be considered for transistor scaling?

9. Define constant voltage scaling.

10. What are the sources to be considered for design margin?

Kings College of Engineering, Punalkulam

EC1354 VLSI DESIGN

PART-B

1. Explain in detail about the following:

a) Resistance estimation (8)

b) Inductance estimation (8)

2. Explain about routing capacitance with neat diagram. (16)

3. With neat diagram explain about power dissipation. (16)

4. Briefly explain about the following:

a) CMOS transistor sizing (8)

b) Design margining (8)

5. Explain about scaling of MOS transistor dimensions and charge sharing. (16)

UNIT –IV

VLSI SYSTEM COMPONENTS CIRCUITS AND SYSTEM

LEVEL PHYSICAL DESIGN

PART-A

1. Write the difference between encoder and priority encoder.

2. Draw the CMOS implementation of 4-to-1 MUX using transmission gates.

3. Give the verilog coding for 4-bit magnitude comparator.

4. Draw the wheel floor plan

5. What is meant by clock distribution?

6. Design a circuit for finding the 9's compliment of a BCD number using 4-bit

binary adder and some external logic gates

7. What is physical verification?

8. Mention the levels at which testing of a chip can be done

9. What are the approaches in design for testability?

10. What is known as boundary scan register?

11. Design a set of CMOS gates to implement the sum function.

PART-B

1. Give the design procedure for 8 bit carry look ahead adder. (16)

2. Design a multiplier for the given sequence: (16)

Kings College of Engineering, Punalkulam

EC1354 VLSI DESIGN

a1 a2 a3 a4 a5 x b1 b2 b3

3. Draw the basic physical design for the inverter AND, OR and half-adder. (16)

4. Explain in detail about manufacturing of test principles. (16)

5. Explain the concept of clock distribution and power distribution. (16)

UNIT – V

VERILOG HARDWARE DESCRIPTION LANGUAGE

PART – A

1. What is Verilog?

2. What are identifiers?

3. What are gate primitives?

4. What is a FPGA?

5. Give the two blocks in behavioral modeling.

6. Define FSM.

7. Give the XILINX FPGA architecture

8. What is Switch-level modeling?

9 What is an antifuse?

10. What are the different types of modeling Verilog?

PART-B

1. Design a 4-bit carry look ahead adder and write the verilog HDL for it. (16)

2. Design 4X1 multiplexer and write the HDL for it in all four modeling: (16)

3. Briefly explain behavioral modeling(all functions) with an example: (16)

4. Design and develop a project in HDL to compare x5x4x3x2x1x0 with y5y4y3y2y1y0.

Check the output by means of test bench. (16)

5. Explain the following with an example:

i) Tasks and functions (4)

ii) Test bench for multiplexer (4)

iii) Difference between always and initial (4)

iv) Blocking and non-blocking statements (4)

6. Explain with a neat sketch the architecture of CLB’S available in xilinx XC 3000

series FPGA (16)

----------------------------

Kings College of Engineering, Punalkulam

Das könnte Ihnen auch gefallen

- Ec 1354 Vlsi DesignDokument5 SeitenEc 1354 Vlsi Designdhasarathan_rajaNoch keine Bewertungen

- University Question Papers - VLSIDokument26 SeitenUniversity Question Papers - VLSIVijayNoch keine Bewertungen

- Vlsi Design - Department of Electronics and CommunicationDokument6 SeitenVlsi Design - Department of Electronics and CommunicationAnirnya SamantaNoch keine Bewertungen

- Ec 1354Dokument5 SeitenEc 1354kvnelavarasiNoch keine Bewertungen

- VLSI AssignDokument5 SeitenVLSI AssignSrideviasokanNoch keine Bewertungen

- Chapter - ICDokument9 SeitenChapter - ICbelyalamgirNoch keine Bewertungen

- Vlsi QP 21,22Dokument11 SeitenVlsi QP 21,22Arunitha ArulnathanNoch keine Bewertungen

- VlsiDokument3 SeitenVlsiAngel JothiNoch keine Bewertungen

- Question Paper Code: X10348: Reg. NoDokument2 SeitenQuestion Paper Code: X10348: Reg. NoJaikumar RajendranNoch keine Bewertungen

- Time: 3 Hours Full Marks: 70Dokument3 SeitenTime: 3 Hours Full Marks: 70pikluNoch keine Bewertungen

- Ec2354 Vlsi DesignDokument13 SeitenEc2354 Vlsi Designjgssb85Noch keine Bewertungen

- A1429 VlsiDokument8 SeitenA1429 VlsiratnamsNoch keine Bewertungen

- VLSIDesignDokument5 SeitenVLSIDesignVenkatesh KolatiNoch keine Bewertungen

- Vlsi Important QuestionsDokument2 SeitenVlsi Important QuestionsJoshua KumaresanNoch keine Bewertungen

- Be Winter 2022Dokument2 SeitenBe Winter 2022kaushal.21beect008Noch keine Bewertungen

- EC2354 - VLSI DesignDokument2 SeitenEC2354 - VLSI DesignSriramNoch keine Bewertungen

- Vlsi Model 4-QPDokument2 SeitenVlsi Model 4-QPsanthoshNoch keine Bewertungen

- Valliammai Engineering College: Department ofDokument10 SeitenValliammai Engineering College: Department ofmaheshwarivikas1982Noch keine Bewertungen

- EC19641-VLSI Design Part B Question BankDokument2 SeitenEC19641-VLSI Design Part B Question BankmyavananNoch keine Bewertungen

- Question BankDokument9 SeitenQuestion BankNiyas AhamedNoch keine Bewertungen

- 18EI56Dokument6 Seiten18EI56Rocky BhaiNoch keine Bewertungen

- 523 BA19 Ad 01Dokument5 Seiten523 BA19 Ad 01ramesh1926Noch keine Bewertungen

- VLSI DesignDokument1 SeiteVLSI DesignSurendar AviNoch keine Bewertungen

- 2 Ec2354 - Vlsi DesignDokument2 Seiten2 Ec2354 - Vlsi Designkrishna_ScrbidNoch keine Bewertungen

- EC2354 - Nov 2011 - AU QP Anna University Exams - VLSIDokument3 SeitenEC2354 - Nov 2011 - AU QP Anna University Exams - VLSISHARANYANoch keine Bewertungen

- EC8095 QB VLSI DesignDokument10 SeitenEC8095 QB VLSI DesignBhuvana EshwariNoch keine Bewertungen

- SEPTEMBERDokument3 SeitenSEPTEMBERRocky BobeeNoch keine Bewertungen

- M.Tech I Semester Supplementary Examinations February/March 2018Dokument1 SeiteM.Tech I Semester Supplementary Examinations February/March 2018baburao_kodavatiNoch keine Bewertungen

- Ec6601 QB RejinpaulDokument5 SeitenEc6601 QB RejinpauljohnarulrajNoch keine Bewertungen

- VLSID R20 Q BankDokument4 SeitenVLSID R20 Q BankSATYA SRI LIKHITHA DUSANAPUDINoch keine Bewertungen

- Assignment-2 Vlsi 29.04.2023Dokument1 SeiteAssignment-2 Vlsi 29.04.2023040-NishanthNoch keine Bewertungen

- VLSI DESIGN Question Bank: Unit 1Dokument12 SeitenVLSI DESIGN Question Bank: Unit 1Babu GundlapallyNoch keine Bewertungen

- Code No: R05320402Dokument4 SeitenCode No: R05320402chvsrsettiNoch keine Bewertungen

- Gujarat Technological UniversityDokument1 SeiteGujarat Technological UniversityHet ShahNoch keine Bewertungen

- r05410207 Vlsi DesignDokument7 Seitenr05410207 Vlsi Design9010469071Noch keine Bewertungen

- Previous PapersDokument12 SeitenPrevious PapersKaran SanaNoch keine Bewertungen

- VlSI Design OU Question PaperDokument1 SeiteVlSI Design OU Question PapershivagurramNoch keine Bewertungen

- EM506 VLSI ArchitectureDokument5 SeitenEM506 VLSI ArchitecturePrakash Velayudham VNoch keine Bewertungen

- Eprvd-102 Eprds-102a - 01.12 PDFDokument2 SeitenEprvd-102 Eprds-102a - 01.12 PDFNaresh KumarNoch keine Bewertungen

- Ei2403 Vlsi DesignDokument10 SeitenEi2403 Vlsi DesignSaravanan MathiNoch keine Bewertungen

- Ei2353:Digital System Design: Question BankDokument3 SeitenEi2353:Digital System Design: Question BanknithyadeceNoch keine Bewertungen

- Vlsi QP 1Dokument6 SeitenVlsi QP 1Sailesh PosaniNoch keine Bewertungen

- Be Summer 2021Dokument2 SeitenBe Summer 2021Sandip SolankiNoch keine Bewertungen

- Ec2203 Digital ElectronicsDokument8 SeitenEc2203 Digital ElectronicspappujayaNoch keine Bewertungen

- Previous Question PapersDokument4 SeitenPrevious Question Papersshaker423Noch keine Bewertungen

- Jntu Vlsi Systems DesignDokument5 SeitenJntu Vlsi Systems Design9010469071Noch keine Bewertungen

- VLSI PapersDokument6 SeitenVLSI PapersSandip SolankiNoch keine Bewertungen

- BE - Semester-VI Examination B.E. (Ec) Semester Vi Subject Code: Subject Name: VLSI Technology and Design Date: Time: Total Marks: 70 InstructionsDokument1 SeiteBE - Semester-VI Examination B.E. (Ec) Semester Vi Subject Code: Subject Name: VLSI Technology and Design Date: Time: Total Marks: 70 Instructionshiren467_ecNoch keine Bewertungen

- Ec1311 Com EngDokument4 SeitenEc1311 Com EngRameez FaroukNoch keine Bewertungen

- Roll No.: B. TechDokument3 SeitenRoll No.: B. TechShivani VarshneyNoch keine Bewertungen

- 2008 Anna UniversityDokument1 Seite2008 Anna UniversitysasitsnNoch keine Bewertungen

- Question PDFDokument12 SeitenQuestion PDFjushwanth100% (1)

- CS 801D PDFDokument4 SeitenCS 801D PDFarnab paulNoch keine Bewertungen

- See Cmos Vlsi Jan 2020Dokument3 SeitenSee Cmos Vlsi Jan 20201ms21ec132Noch keine Bewertungen

- VLSI Design 2010 Sept CUSATDokument1 SeiteVLSI Design 2010 Sept CUSATvineethvrr5948Noch keine Bewertungen

- Token Ring Technology ReportVon EverandToken Ring Technology ReportNoch keine Bewertungen

- Computational Liquid Crystal Photonics: Fundamentals, Modelling and ApplicationsVon EverandComputational Liquid Crystal Photonics: Fundamentals, Modelling and ApplicationsNoch keine Bewertungen

- Lecture003 Reversible LogicDokument53 SeitenLecture003 Reversible LogickunalsanghviNoch keine Bewertungen

- VLSI Design LabDokument47 SeitenVLSI Design LabqwertyuiopNoch keine Bewertungen

- Isolated Bidirectional Full-Bridge DC-DC Converter With A Flyback SnubberDokument62 SeitenIsolated Bidirectional Full-Bridge DC-DC Converter With A Flyback SnubberqwertyuiopNoch keine Bewertungen

- Electrical JournalsDokument2 SeitenElectrical JournalsnithinrmuNoch keine Bewertungen

- Clinck Service LogDokument1 SeiteClinck Service LogqwertyuiopNoch keine Bewertungen

- X'merDokument13 SeitenX'mervatsalNoch keine Bewertungen

- A First Course in Electrical and Computer Engineering PDFDokument321 SeitenA First Course in Electrical and Computer Engineering PDFRigoberto CuellarNoch keine Bewertungen

- Sage Publications, LTDDokument25 SeitenSage Publications, LTDAntonio ScaliaNoch keine Bewertungen

- Fieldwork Exercise 2: 4 Thailand Geography Olympiad Chiang Mai University Tuesday, 10 May 2022 Time: 13:30-16:30Dokument12 SeitenFieldwork Exercise 2: 4 Thailand Geography Olympiad Chiang Mai University Tuesday, 10 May 2022 Time: 13:30-16:30Sun CharoenratNoch keine Bewertungen

- Byzantium Notes CultureDokument6 SeitenByzantium Notes Culturepatrick cairoliNoch keine Bewertungen

- Post Purchase Cognitive DissonanceDokument18 SeitenPost Purchase Cognitive DissonancePawan DihiyeNoch keine Bewertungen

- Lecture 6 OptimizationDokument41 SeitenLecture 6 Optimizationaku_la100% (2)

- Renub Research: Singapore Medical Tourist Arrivals, Medical Tourism Market & Forecast To 2015Dokument13 SeitenRenub Research: Singapore Medical Tourist Arrivals, Medical Tourism Market & Forecast To 2015api-114525849Noch keine Bewertungen

- Tablet Coamoxiclave (Amoxicillin +clavulanic Acid) Indications and DosDokument2 SeitenTablet Coamoxiclave (Amoxicillin +clavulanic Acid) Indications and DosShumaila Iftikhar Iftikhar AhmadNoch keine Bewertungen

- Truth Beyond Paradox (Final Download)Dokument217 SeitenTruth Beyond Paradox (Final Download)andreas waneyNoch keine Bewertungen

- Industrial Automation Lab: Project ProposalDokument3 SeitenIndustrial Automation Lab: Project ProposalAmaan MajidNoch keine Bewertungen

- Defining Your Core ValuesDokument2 SeitenDefining Your Core ValuesMaria Elizabeth Smith100% (2)

- SelcalDokument4 SeitenSelcalAvinash KashyapNoch keine Bewertungen

- Graphics View FrameworkDokument7 SeitenGraphics View FrameworkTxkti BabelNoch keine Bewertungen

- Bilingual First Language Acquisition: January 2008Dokument11 SeitenBilingual First Language Acquisition: January 2008Katsiaryna HurbikNoch keine Bewertungen

- Liphardt ResumeDokument4 SeitenLiphardt Resumeapi-398834878Noch keine Bewertungen

- Safety EducationDokument5 SeitenSafety EducationOwen Silva NaldozaNoch keine Bewertungen

- Big Breakfasts Help Us Burn Double The CaloriesDokument4 SeitenBig Breakfasts Help Us Burn Double The CaloriesBastian IgnacioNoch keine Bewertungen

- Odisha PWD Registration in CDMSDokument2 SeitenOdisha PWD Registration in CDMSSabyasachi Naik (Zico)Noch keine Bewertungen

- IRC CodesDokument23 SeitenIRC CodesabhijithavalNoch keine Bewertungen

- SiteDokument6 SeitenSiteMikeNoch keine Bewertungen

- AEM-Large Deformation AnalysisDokument37 SeitenAEM-Large Deformation AnalysisPinakin GoreNoch keine Bewertungen

- Indra: Detail Pre-Commissioning Procedure For Service Test of Service Water For Unit 040/041/042/043Dokument28 SeitenIndra: Detail Pre-Commissioning Procedure For Service Test of Service Water For Unit 040/041/042/043AnhTuấnPhanNoch keine Bewertungen

- AwanishTrivedi PastryChefDokument3 SeitenAwanishTrivedi PastryChefChandra MohanNoch keine Bewertungen

- 3.2 Server Maintenance Administration PlanDokument30 Seiten3.2 Server Maintenance Administration PlanAG Network ResourcesNoch keine Bewertungen

- Evaporator Pressure Regulating Valve SporlanDokument16 SeitenEvaporator Pressure Regulating Valve SporlanSubramanian gokul100% (1)

- Generic List - MOH PHCs-March-2023Dokument11 SeitenGeneric List - MOH PHCs-March-2023drabdulrabbNoch keine Bewertungen

- SyllabusDokument3 SeitenSyllabuspan tatNoch keine Bewertungen

- Training Wall Height On Convergent Stepped SpillwaysDokument10 SeitenTraining Wall Height On Convergent Stepped Spillwayschutton681Noch keine Bewertungen

- Proposed USG Boral Ceiling System For Tropicana MiyuDokument5 SeitenProposed USG Boral Ceiling System For Tropicana MiyuLorraineNoch keine Bewertungen

- First ContingencyDokument2 SeitenFirst Contingencymanju bhargavNoch keine Bewertungen

- Self-Assessment Observation and Assessment of Child DevelopmentDokument3 SeitenSelf-Assessment Observation and Assessment of Child Developmentapi-508676940Noch keine Bewertungen