Beruflich Dokumente

Kultur Dokumente

Customizable System Interfaces Add Value To Embedded Processors

Hochgeladen von

stevesalmOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Customizable System Interfaces Add Value To Embedded Processors

Hochgeladen von

stevesalmCopyright:

Verfügbare Formate

W H I T E PA P E R

Clay Turner,

Applications Engineer;

James Doublesin,

Applications Engineer;

Steve Kipisz,

Customizable system

Applications Engineer;

Texas Instruments

interfaces add value to

Introduction

embedded processors

Standard interfaces integrated into an embedded

Matching an application’s requirements with an

processor helps ease a system designer’s work embedded processor’s set of standard interfaces

by providing interoperability with other products seldom results in a perfect match. Customizable

and reducing design cost and cycle time. But interfaces help fill the gaps.

they can also make the choice of an embedded

processor a bit problematic.

Realizing the importance of standard interfac-

es, embedded processor vendors such as Texas Since the PRU contains two packet data structure processor cores, it can be utilizied to pro-

Instruments (TI), offer products with various vide real-time processing resources while the uPP is a good fit for system processors requiring

combinations of embedded memory and periph- interfaces with high-speed DACs, ADCs, digital signal processors (DSPs) and FPGAs capable of

eral interfaces. The goal is to match, as best as data transfers of the order of 250 MB/s.

possible, the requirements of typical embedded In addition to providing an overview of the PRU and uPP architectures and benefits, this white

applications. paper will also describe TI’s implementations of various standard interfaces including the USB,

Unfortunately, not all applications fit neatly into SATA, DDR and EMAC and their variants.

the definition of “typical”. In this situation, the

system designer may need to select a processor PRU: Real-time processing

that integrates one or more interfaces that the The PRU is a small, 32-bit processing engine with a four-bus architecture allowing instruc-

application does not require, or, may have to add tions to be fetched and executed concurrently with data transfers. Additionally, external status

an external circuit to provide needed functionality information can be reflected in an internal processor status register.

adding extra cost in the solution. At times, both Available on the Sitara™ ARM® microprocessors (MPUs) platform, TI designed a large

are required. amount of flexibility into the PRU to enable a wide range of functions. For example, PRU has

To address this problem, TI developed two cir- full visibility of the host system’s resources, including all system memory, input/output (I/Os)

cuits, the programmable real-time unit (PRU) and and interrupts.

the universal Parallel Port (uPP), that are flexible To minimize its on-chip footprint, TI maintained the PRU’s internal resources relatively mod-

enough to take the place of a peripheral interface est with four KBytes of instruction memory and 512 Bytes of data memory. Additionally, the

or other function(s). For example, the PRU offers PRU provides its own GPIOs with latencies measured in nanoseconds.

system designers the flexibility to configure an The PRU can be programmed with simple assembly code to implement custom logic. The

interface to networks including controller area instruction set is divided into four categories:

network (CAN), PROFIBUS and various commu-

nications applications. 1. to move data in or out of the processor’s internal registers

2. to perform arithmetic operations

2 Texas Instruments

3. to perform logical operations

4. to control program flow

In addition to being an I/O replacement, the PRU can be programmed to execute a variety of control, moni-

toring or other functions not available on-chip. This flexibility is helpful in applications encompassing control

requirements that do not match those available on any of the standard processor configurations.

Frequently used industrial interfaces that PRU can implement include:

• Process Field Bus (PROFIBUS): A standard for field bus communication in automation technology.

It has two implementations. PROFIBUS Decentralized Peripherals (DP): For sensors and actuators and

utilizes a centralized controller. PROFIBUS Process Automation (PA) monitors measuring equipment with a

process-control system.

• CAN-Lite bus: Typically, CAN networks consist of sensors, actuators and other control devices. These

devices are not connected directly to the bus, but through a host processor and a CAN controller.

• IEEE 1588 or precision protocol (PTP): A high-precision time-stamping capability for time synchroni-

zation protocol used in network measurement and control systems.

• IO-LINK: Up to eight UARTs can be configured with the PRU to support the new process automation

standard that links sensors and actuators to control devices.

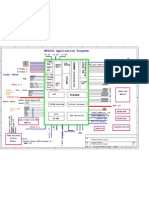

Figure 1 illustrates how the PRU running interacts in a PROFIBUS DP master and slave application. It can

also be configured as industrial Ethernet (PROFINET) slaves and for sampling and signal conditioning.

ARM9™ / DSP – 300 MHz

ROM/

Application Interface EEPROM

Application

DP Stack

DP Stack FMS Stack 128K

Data

PRU (PDSP) – 150 MHz RAM

Fieldbus Data Link Host – API Utilities, OVM, PLL

FDL

ASPC2 MSG, FDL STM Watchdog

Frame

Framer, Scheduler Timer

Byte

RX TX CF eCAP

Bit

UART

12 Mbit 13× overs.

Figure 1. PRU implemented in a PROFIBUS application

Customizable system interfaces add value to embedded processors March 2011

Texas Instruments 3

Without the PRU, the PROFIBUS interface shown in Figure 1 would typically be implemented in a 32-pin

ASIC in a DIP package. Eliminating the ASIC from the design saves about U.S. $5 to system cost and the

PRU solution also saves board space and design time. Both master and slave PROFIBUS functionality can be

implemented using the PRU.

uPP: A configurable The basic architecture of the uPP includes separate, parallel data buses that can be configured to handle

parallel data bus more than one word length. Data widths of eight to 16 bits per channel are possible. The uPP also has an

internal DMA block so data transfers do not draw down the CPU’s MIPS budget. Single or double data rates

and multiple data packing formats are also part of the uPP’s features.

The uPP is available on a variety of TI DSPs such as processors with the TMS320C674x cores, an

OMAP-L138 device with a C674x core and the AM1x Sitara ARM9™ MPUs. Unlike serial peripherals such

as SPI and UARTs, uPP offers designers the advantages of a parallel data bus with a data width of eight to

16 bits per channel.

When running at its maximum clock speed of 75 MHz, uPP transfers data much faster than the serial port

peripherals. For example, a single 16-bit uPP channel operating at 75 MHz is as much as 24 times faster

than a SPI peripheral operating at 50 MHz.

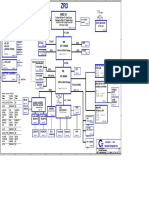

A simplified uPP block diagram is shown in Figure 2.

uPP Peripheral

Configuration Data Pins (A)

CPU Registers

I/O Channel

A Control Pins

(A)

Memory

Internal Data Pins (B)

DMA I/O Channel

B Control Pins

(B)

CPU

Interrupt

Figure 2. uPP simplified block diagram.

Features of the uPP include:

• Two independent channels with separate data buses

• Channels can operate in same or opposing directions simultaneously

• I/O speeds up to 75 MHz with 8–16-bit data width per channel

• Internal DMA – leaves chip-level EDMA free

Customizable system interfaces add value to embedded processors March 2011

4 Texas Instruments

• Simple protocol with few control pins (configurable: 2–4 per channel)

• Single and double data rates (use one or both edges of clock signal)

• Double data rate imposes a maximum clock speed of 37.5 MHz

• Multiple data packing formats for 9–15-bit data widths

• Data interleave mode (single channel only)

uPP bears some resemblance to another TI peripheral dedicated to configurable data handling, the host

port interface (HPI). While the two hold various similarities, they differ significantly. Like HPI, uPP offers a

high-speed parallel data bus. Unlike HPI, however, uPP does not grant direct memory access to an external

device; and, it requires I/O transfers to be queued by device software. Perhaps the biggest difference is that

uPP is considerably faster than HPI and possess much simpler protocol.

uPP can be configured to have one or two channels, 8- or 16-bit words, and either one-way or two-way

data transfer simultaneously. Table 1 shows both theoretical and experimental data speeds for several oper-

ating modes.

A comparison to HPI is included on the bottom row of the table. The uPP peripheral has a maximum clock

speed of 75 MHz but can support a clock of only 50 MHz in the two-channel, one-way, 16-bit configuration.

Table 1.

Theoretical Realistic

uPP Mode (MB/s) (MB/s)

1 ch, 8-bit 75 60

1 ch, 16-bit 150 120

2 ch, 1 way, 8-bit 150 120

2 ch, 1 way, 16-bit 200 160

2 ch, 2 way, 8-bit 150 120

2 ch, 2 way, 16-bit 300 240

HPI (16 bit) – 50

In addition to the two custom peripherals described above, TI offers a range of standard peripherals. Al-

though the interface itself conforms to a standard, in many instances, the on-chip implementation is specific

to TI and offers greater efficiency or performance.

EMAC The EMAC module provided by TI provides a complete on-chip subsystem that implements an efficient

interface between the core processor and the external Ethernet network. It supports 10Base-T (10 Mb/s)

and 100Base-TX (100 Mb/s) in either half- or full-duplex mode, and 1000Base-T (1000 Mb/s) in full-duplex

mode, with hardware flow control and quality-of-service (QoS) support.

The functionality specified for the physical layer (PHY) by the IEEE 802.3 Ethernet standard is implemented

in a management data input/output (MDIO) module. The MAC layer of the protocol is implemented by the

EMAC.

Customizable system interfaces add value to embedded processors March 2011

Texas Instruments 5

The EMAC module has a communications port programming interface (CPPI) buffer manager that manages

8K Bytes of CPPI RAM. Four 32-bit words are used as buffer descriptors that point to buffers in the processor

memory.

The control registers of the EMAC and MDIO modules are memory mapped into device memory space. The

MDIO module implements an 802.3 serial management interface to control up to 32 Ethernet PHYs over a

shared two-wire bus.

Application software utilizes the MDIO module to configure the auto-negotiation parameters of each PHY

attached to the EMAC, retrieve the negotiation results and configure required parameters in the EMAC mod-

ule for correct operation. The module is designed to allow almost transparent operation of the MDIO interface,

with very little maintenance from the core processor. A single MDIO is shared by both EMACs.

Both the EMAC and MDIO modules access the system core through MAC control module, which also

optimizes data flow. In completely integrated solutions such as embedded processors from TI, the custom

interface is considered integral to the EMAC/MDIO peripheral.

A complete EMAC subsystem is illustrated in Figure 3.

EMAC Subsystem

Control Module

DMA 8K CPPI C0

DMA Bus

Master RAM Interrupt

C1 Interrupts

Register Bus Combiner

C2

EMAC MDIO

Interrupts Interrupts

EMAC MDIO

Module Module

MII/RMII Bus MDIO Bus

Figure 3. EMAC subsystem.

Given that Ethernet is so widely used, embedded processors typically integrate one or more EMAC inter-

faces on chip. There is some variation in the way different vendors implement the complete EMAC subsystem

described above. The quality and extent of software support and libraries for implementing Ethernet inter-

faces is another decision point in choosing an embedded processor vendor.

USB The universal serial bus (USB) interface describes three device classes of primary interest to design engi-

neers. The USB human interface device (HID) class interfaces to keyboards, mice and oscilloscopes. USB

communication device class (CDC) was created for modems and faxes but supports simple networking with

Customizable system interfaces add value to embedded processors March 2011

6 Texas Instruments

its interface for transmitting Ethernet packets. Similarly, USB mass storage device (MSD) targets hard disk

drives and other storage media.

USB 2.0 is by far the most common USB variant. It has three speed options:

• High-speed (480 Mbps)

• Low-speed (1.5Mbps), and

• Full-speed (12 Mbps)

The specification also defines three basic devices, host controllers, hubs and peripherals.

USB 2.0 utilizes a tiered-star topology with a hub at the center of each star. Each wire segment is a point-

to-point connection between the host and a hub or function, or a hub connected to another hub or function.

The addressing scheme used for devices in a USB 2.0 system allows for up to 127 devices to be con-

nected to a single host. Any combination of hubs or peripherals is allowed.

TI adds value to its USB implementations by having available royalty-free software libraries to target spe-

cific USB functionality. Instead of writing their own code to implement the interface, system designers simply

make a function call.

An example of a comprehensive sub-set of USB functions is offered for TI Sitara™ processors. It includes

code to implement the following functionality:

• Peripheral devices:

• HID keyboard

• HID mouse

• CDC Serial

• Mass storage

• Audio

• Device firmware upgrade

• Oscilloscope

• Host examples:

• Mass storage

• HID keyboard

• HID mouse

In 2007, the USB 3.0 Promoter Group was formed to create a faster USB variant that will be backward

compatible with previous USB standards but deliver ten times the data of USB 2.0. USB 3.0 uses a new

signaling scheme. Backward compatibility is maintained by keeping the USB 2.0 two-wire interface.

Customizable system interfaces add value to embedded processors March 2011

Texas Instruments 7

DDR2/Mobile DDR Created to provide high-performance memory transfers, DDR2 transfers data on the rising and falling edges

of the bus clock signal and operates at a high bus speed that its predecessor, DDR, to achieve a total off our

data transfers per internal clock cycle. A simplified DDR2 controller interface and its relationship to the DDR2

memory chip and core logic are shown in Figure 4.

in

in

out

out

Figure 4. Simplified DDR2 controller implementation

The memory control block issues accesses from memory to the application-specific core logic or vice

versa. The read physical block handles external signal timing that captures data during read cycles; and the

write physical block manages the issuance of clock and data with the appropriate external signal timing.

A byte-wide, bidirectional data strobe (DQS) is transmitted externally along with data (DQ) for capture. DQS

is transmitted edge-aligned by the controller during reads to memory and center aligned during writes to

memory. On-chip delay-lock loops (DLLs) are used to clock out DQS and corresponding DQs. This assures

that they can track each other during changes in voltage and temperature.

DDR2 SRAMs have differential clock inputs to reduce the effects of duty cycle variations on clock inputs.

DDR2 SRAMs also support data mask signals to mask data bits during write cycles.

Mobile DDR (MDDR), also referred to as low-power double-data-rate memory (LPDDR), operates at

1.8 volts as opposed to the more traditional 2.5 volts and is commonly used in portable electronics. As with

all DDR memory, the double data rate is achieved by transferring data on both clock edges of the device.

SATA The serial ATA (SATA) bus connects host bus adapters to mass storage devices such as hard disk drives and

optical drives. SATA’s serial data format uses two differential pairs and can support interfaces to data storage

devices at both 1.5 Gbits/s and 3.0 Gbits/s line speeds.

SATA attains its high performance in part by implementing an advanced system memory structure to ac-

commodate high-speed serial data. The advanced host controller interface (AHCI) memory structure contains

a generic area for control and status and a command list data table. Each entry in the command list table

contains information for programming a SATA device as well as a pointer to a descriptor table for transferring

data between system memory and the device.

Most SATA controllers support hot swapping and the use of a port multiplier to increase the number of

devices that can be attached to the single HBA port. The SATA standard includes a long list of features but

few SATA controllers support all of them. Features supported by TI include:

• Support for the AHCI controller spec 1.1

• Integrated SERDES PHY

Customizable system interfaces add value to embedded processors March 2011

8 Texas Instruments

• Integrated Rx and Tx data buffers

• Support for SATA power management features

• Internal DMA engine per port

• Hardware-assisted native command queuing (NCQ) for up to 32 entries

• 32-bit addressing

• Support for a port multiplier

• Activity LED support

• Mechanical presence detect

Conclusion Although standard interfaces play a critical role in designing systems that are interoperable, low cost and

require less time to design, their utility is still limited for a design team that needs to differentiate its product.

Designers should research chip vendors for a wide variety of standard interfaces in multiple combinations.

High-quality software libraries that help implement the interfaces efficiently are other differentiating factors

for chip vendors. Offering an additional level of flexibility is also helpful and can be accomplished by configu-

rable interfaces such as TI’s PRU and uPP. By providing numerous options in tools kits, system designers can

be creative while simultaneously keeping component costs low.

Important Notice: The products and services of Texas Instruments Incorporated and its subsidiaries described herein are sold subject to TI’s standard terms and

conditions of sale. Customers are advised to obtain the most current and complete information about TI products and services before placing orders. TI assumes no

liability for applications assistance, customer’s applications or product designs, software performance, or infringement of patents. The publication of information

regarding any other company’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Sitara is a trademark of Texas Instruments Incorporated. All other trademarks are the property of their respective owners.

© 2011 Texas Instruments Incorporated SPRY162

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements,

and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should

obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are

sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard

warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where

mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and

applications using TI components. To minimize the risks associated with customer products and applications, customers should provide

adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right,

or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information

published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a

warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual

property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied

by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive

business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional

restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all

express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not

responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably

be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing

such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and

acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products

and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be

provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in

such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are

specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military

specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at

the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are

designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated

products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

Products Applications

Audio www.ti.com/audio Communications and Telecom www.ti.com/communications

Amplifiers amplifier.ti.com Computers and Peripherals www.ti.com/computers

Data Converters dataconverter.ti.com Consumer Electronics www.ti.com/consumer-apps

DLP® Products www.dlp.com Energy and Lighting www.ti.com/energy

DSP dsp.ti.com Industrial www.ti.com/industrial

Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical

Interface interface.ti.com Security www.ti.com/security

Logic logic.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Power Mgmt power.ti.com Transportation and www.ti.com/automotive

Automotive

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com Wireless www.ti.com/wireless-apps

RF/IF and ZigBee® Solutions www.ti.com/lprf

TI E2E Community Home Page e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2011, Texas Instruments Incorporated

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5795)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Spark ArticleDokument26 SeitenSpark ArticlestevesalmNoch keine Bewertungen

- Geb TGV enDokument61 SeitenGeb TGV enstevesalmNoch keine Bewertungen

- Street Triple SDokument245 SeitenStreet Triple SstevesalmNoch keine Bewertungen

- Maths Predicts Earthquakes: Digikey - Co.UkDokument28 SeitenMaths Predicts Earthquakes: Digikey - Co.UkstevesalmNoch keine Bewertungen

- EPN Marzo 2011Dokument80 SeitenEPN Marzo 2011stevesalmNoch keine Bewertungen

- Tutorial Using SPI in F2833x F2803x TargetDokument22 SeitenTutorial Using SPI in F2833x F2803x TargetAnDres RodriguezNoch keine Bewertungen

- TechnicalReferenceManual CY8C29x66 CY8C27x43Dokument568 SeitenTechnicalReferenceManual CY8C29x66 CY8C27x43trnealNoch keine Bewertungen

- Simulation Set 2Dokument4 SeitenSimulation Set 2Harsh ThakurNoch keine Bewertungen

- Assignment 1Dokument2 SeitenAssignment 1RachuNoch keine Bewertungen

- Ciscoc 240 M 4Dokument90 SeitenCiscoc 240 M 4sanjayNoch keine Bewertungen

- Ram RomDokument42 SeitenRam Rommohit mishraNoch keine Bewertungen

- 2 Mbit SPI Serial Flash: FeaturesDokument27 Seiten2 Mbit SPI Serial Flash: FeaturesBrahimiNoch keine Bewertungen

- Beep CodesDokument5 SeitenBeep CodesAkibo Tunde Williamson DaviesNoch keine Bewertungen

- Setup and Hold Time": Static Timing Analysis (STA) Basic (Part 3c) - VLSI ConceptsDokument14 SeitenSetup and Hold Time": Static Timing Analysis (STA) Basic (Part 3c) - VLSI ConceptsKeerthiKalyanNoch keine Bewertungen

- PT2272Dokument18 SeitenPT2272Ahmad FahmiNoch keine Bewertungen

- Ibm X3650 ServerDokument2 SeitenIbm X3650 ServerAshok ChowdaryNoch keine Bewertungen

- Digital Integrated Circuits: A Design PerspectiveDokument78 SeitenDigital Integrated Circuits: A Design Perspectiveapi-127299018Noch keine Bewertungen

- Chapter 1 Introduction To The Semiconductor Industry 2005 VLSI TECH.1Dokument28 SeitenChapter 1 Introduction To The Semiconductor Industry 2005 VLSI TECH.1samactrangNoch keine Bewertungen

- 20051121142600Dokument1 Seite20051121142600bc77a4637Noch keine Bewertungen

- CH04 COA9e Cache Memory RepairedDokument42 SeitenCH04 COA9e Cache Memory RepairedHuy ChuNoch keine Bewertungen

- EE 134 Final Project Report - Knight RiderDokument14 SeitenEE 134 Final Project Report - Knight RiderSatyajit BaliyanNoch keine Bewertungen

- What's VHDL? Basic Concept: VHDL Very Hard Difficult LanguageDokument57 SeitenWhat's VHDL? Basic Concept: VHDL Very Hard Difficult Languagedeepakk_alpineNoch keine Bewertungen

- Mpa Question Bank1Dokument16 SeitenMpa Question Bank1Sharon FrancisNoch keine Bewertungen

- Nodemcu: An Open Source IOT PlatformDokument13 SeitenNodemcu: An Open Source IOT PlatformTelugu ETechNoch keine Bewertungen

- High Test CoverageDokument58 SeitenHigh Test CoverageAdhi SuruliNoch keine Bewertungen

- Cypress Intro To BLE System DesignDokument93 SeitenCypress Intro To BLE System Designmark363Noch keine Bewertungen

- 04 - Intro Lego RCX CodeDokument53 Seiten04 - Intro Lego RCX CodegatobravoNoch keine Bewertungen

- Sun Fundamentals Course2 Feb15Dokument150 SeitenSun Fundamentals Course2 Feb15Tom KielyNoch keine Bewertungen

- TS6. Memory OrganizationDokument5 SeitenTS6. Memory Organization黄佩珺Noch keine Bewertungen

- Cadence Tutorial PDFDokument61 SeitenCadence Tutorial PDFJinesh Kb100% (1)

- MSI PM8PM-V ManualDokument87 SeitenMSI PM8PM-V ManualMats Ägrim JohanssonNoch keine Bewertungen

- Acer Aspire 3050, 5050 Quanta ZR3 DA0ZR3MB6E0 DA0ZR3MB6C1Dokument31 SeitenAcer Aspire 3050, 5050 Quanta ZR3 DA0ZR3MB6E0 DA0ZR3MB6C1essemirNoch keine Bewertungen

- University of Hawaii EE 361L Getting Started With Artix-7 Digilent Basys3 Board Lab 4.1Dokument13 SeitenUniversity of Hawaii EE 361L Getting Started With Artix-7 Digilent Basys3 Board Lab 4.1karkeraNoch keine Bewertungen

- Reduced Instruction Set Computers: (Make Hardware Simpler, But Quicker)Dokument30 SeitenReduced Instruction Set Computers: (Make Hardware Simpler, But Quicker)irenedevasahayamNoch keine Bewertungen