Beruflich Dokumente

Kultur Dokumente

Cxa1645 TV Encoder

Hochgeladen von

korrekaminosOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Cxa1645 TV Encoder

Hochgeladen von

korrekaminosCopyright:

Verfügbare Formate

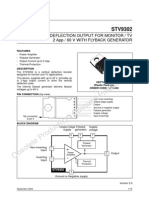

CXA1645P/M

RGB Encoder For the availability of this product, please contact the sales office.

Description The CXA1645P/M is an encoder IC that converts analog RGB signals to a composite video signal. This IC has various pulse generators necessary for encoding. Composite video outputs and Y/C outputs for the S terminal are obtained just by inputting composite sync, subcarrier and analog RGB signals. It is best suited to image processing of personal computers and video games. Features Single 5V power supply Compatible with both NTSC and PAL systems Built-in 75 drivers (RGB output, composite video output, Y output, C output) Both sine wave and pulse can be input as a subcarrier. Built-in band pass filter for the C signal and delay line for the Y signal Built-in R-Y and B-Y modulator circuits Built-in PAL alternate circuit Burst flag generator circuit Half H killer circuit Applications Image processing of video games and personal computers Block Diagram and Pin Configuration

GND2 24 ROUT 23 GOUT 22 BOUT 21 CVOUT 20 VCC2 19 FO 18 YTRAP 17 YOUT 16 COUT 15 VREF 14 IREF 13

24 pin DIP (Plastic)

24 pin SOP (Plastic)

Structure Bipolar silicon monolithic IC Absolute Maximum Ratings 14 V Supply voltage VCC Operating temperature Topr 20 to +75 C Storage temperature Tstg 65 to +150 C Allowable power PD CXA1645P 1250 mW dissipation CXA1645M 780 mW Recommended Operating Condition Supply voltage VCC1, 2 5.0 0.25

VIDEO OUT R-OUT G-OUT B-OUT

Y/C MIX

75 DRIVER

75 DRIVER REGULATOR

DELAY

CLAMP

SYNC ADD BPF R-Y Modulator

MATRIX

B-Y Modulator PHASE SHIFTER PULSE GEN

CLAMP

CLAMP

CLAMP

SIN-PULSE

1 GND1

2 RIN

3 GIN

4 BIN

5 NC

6 SCIN

7 NPIN

8 BFOUT

9 YCLPC

10 SYNCIN

11 NC

12 VCC1

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

E93411A41-ST

CXA1645P/M

Pin Description Pin No. Symbol Pin voltage Equivalent circuit

Externally applied voltage Description Ground for all circuits other than RGB, composite video and Y/C output circuits. The leads to GND2 should be as short and wide as possible.

VCC1

GND1

0V

2 3 4

RIN GIN BIN

Black level when clamped 2.0V

100

180

GND1

ICLP

NC

VCC1

100

Analog RGB signal inputs. Input 100%, = 1Vp-p (max.). To minimize clamp error, input at as low impedance as possible. ICLP turns ON only in the burst flag period.

NO CONNECTION

SCIN

20P 20k 129 20k 2.5V 100 GND1

Subcarrier input. Input 0.4 to 0.5Vp-p sine wave or pulse. Refer to Notes on Operation, Nos. 3 and 5.

VCC1 80k

68k

NPIN

1.7V

7 3k

Pin for switching between NTSC and PAL modes NTSC: VCC, PAL: GND

32k GND1

VCC1

BFOUT

H : 3.6V L : 3.2V

8 129 25 25 GND1

BF pulse monitoring output. Incapable of driving a 75 load.

CXA1645P/M

Pin No.

Symbol

Pin voltage

Equivalent circuit

Description

VCC1 129

YCLPC

2.5V

Pin to determine the Y signal clamp time constant. Connect to GND via a 0.1F capacitor.

5 1.6V GND1

VCC1 40k

10

SYNC IN

2.2V

10 4k

Composite sync signal input. Input TTLlevel voltages. L ( 0.8V): SYNC period H ( 2.0V)

2.2V GND1

12

VCC1

5.0V

Power supply for all circuits other than RGB, composite video and Y/C output circuits. Refer to Notes on Operation. Nos. 4 and 10.

VCC1

13

IREF

2.0V

13 129 50 GND1

Pin to determine the internal reference current. Connect to GND via a 47k resistor.

VCC1

14

VREF

4.0V

14

Internal reference voltage. Connect a decoupling capacitor of approximately 10F. Refer to Notes on Operation, Nos. 4 and 7.

GND1

CXA1645P/M

Pin No.

Symbol

Pin voltage

Equivalent circuit

Description

VCC2 VCC1 600

15

COUT

2.2V

Chroma signal output. Capable of driving a 75 load.

15

10k

20k

Refer to Notes on Operation, Nos. 6 and 9.

GND2

VCC2 VCC1 600

16

YOUT

Black level 1.3V

Y signal output. Capable of driving a 75 load.

16

10k

20k

Refer to Notes on Operation, Nos. 6 and 9.

GND2

VCC1

17

YTRAP

Black level 1.6V

8.5k 17 1.5k 0.5P

Pin for reducing cross color caused by the subcarrier frequency component of the Y signal. When the CVOUT pin is in use, connect a capacitor or a capacitor and an inductor in series between YTRAP and GND. Decide capacitance and inductance, giving consideration to cross color and the required resolution. No influence on the YOUT pin. Refer to Notes on Operation, No. 8.

GND1 Input resistance 1.5k

VCC1

18

FO

2.0V

18 129 50 GND1

Internal filter fo adjustment pin. Connect to GND via the following resistor according to the NTSC or PAL mode. NTSC: 20k (1%) PAL : 16k (1%)

CXA1645P/M

Pin No.

Symbol

Pin voltage

Equivalent circuit

Description Power supply for RGB, composite video and Y/C output circuits. Decouple this pin with a large capacitor of 10F or above as a high current flows. Refer to Notes on Operation, Nos. 4 and 10.

19

VCC2

5.0V

VCC2 VCC1 600

20

CVOUT

Black level 1.2V

Composite video signal output. Capable of driving a 75 load.

20 20k

GND2

500

VCC2 VCC1

10k

Refer to Notes on Operation, Nos. 6 and 9.

21 22 23

BOUT GOUT ROUT

Black level 1.7V

21 22 23 5.5k

Analog RGB signal outputs. Capable of driving a 75 load. Refer to Notes on Operation, Nos. 6 and 9.

200 GND1 GND2

24

GND2

0V

Ground for RGB, composite video and Y/C output circuits. The leads to GND1 should be as short and wide as possible.

CXA1645P/M

Electrical Characteristics

(Ta = 25C, VCC = 5V, See the Electrical Characteristics Measurement Circuit.)

S1 S2 S3 S4 S5 Measurement Conditions No input signal, SG5: CSYNC TTL level, SG4: SIN wave 3.58MHz 0.5Vp-p Fig. 1 Min. Typ. Max. Unit Measu RIN rement SYNC GIN SCIN NPIN FO point IN BIN ICC1 2V SG4 5V SG5 20k

Item

Symbol

Current consumption 1 Current consumption 2 (R, G, BOUT)

ICC1

31 mA 12

ICC2

ICC2

VO (R) RGB output voltage VO (G) VO (B) fC (R) RGB output frequency characteristics fC (G) fC (B) (YOUT & CVOUT) Output sync level R100%: Y level G100%: Y level B100%: Y level White 100%: Y level VO (YS1/2) VO (YR1/2)

SG1 SG2 SG3 SG1 SG2 SG3 2V 2V

D E F D E F

SG1 to SG3: DC direct coupling 2.5VDC, 1.0Vp-p f = 200kHz Pin 9 = Clamp voltage Fig. 2 SG1 to SG3: DC direct coupling 2.5VDC, 1.0Vp-p f = 200kHz/5MHz Pin 9 = Clamp voltage Fig. 3

0.64

0.71

0.78

Vp-p

3.0

dB

SG1 0V VO (YG1/2) to SG3 VO (YB1/2) VO (YW1/2)

5V SG5 20k

B/C

SG1 to SG3: 100% color bar input, 1.0Vp-p (Max.) SG5: CSYNC TTL level Fig. 4 SG1 to SG3: DC direct coupling 2.5VDC, 1.0Vp-p f = 200kHz/5MHz Pin 9 = Clamp voltage Fig. 3

0.26 0.17 0.35 0.065 0.6

0.29 0.21 0.42 0.08 0.71

0.33 0.26 0.49 0.095 0.82

Vp-p V V V V

Output frequency characteristics

fC (Y1/2)

SG1 to 0V SG3

5V

2V

20k

3.0

dB

Clamp voltage: voltage appearing at Pin 9 when CSYNC is input.

CXA1645P/M

S1 Item Symbol

S2

S3

S4

S5 Measurement Conditions Min. Typ. Max. Unit

Measu RIN rement SYNC GIN SCIN NPIN FO point IN BIN

(COUT & CVOUT) Burst level R chroma ratio R phase G chroma ratio G phase B chroma ratio B phase Burst width Burst position VO (BN1/2) R/BN1/2 R1/2 G/BN1/2 G1/2 B/BN1/2 B1/2 SG1 to SG4 SG3 SG1 to SG3: 100% color bar input, 1.0Vp-p (Max.) SG4: SIN wave, 3.58MHz 0.5Vp-p SG5: CSYNC TTL level Fig. 5 0.2 2.84 94 2.65 231 2.01 337 2.5 0.4 A/C SG1 to SG4 SG3 SG1 to SG3: No signal, SG4: SIN wave, 3.58MHz 0.5Vp-p SG5: CSYNC TTL level 3.58MHz component measured. Fig. 6 SG1 to SG3: No signal, SG4: SIN wave, 4.43MHz 0.5Vp-p SG5: CSYNC TTL level Fig. 6 0.9 125 215 1.0 135 225 0.25 3.16 104 2.95 241 2.24 347 2.75 0.6 0.3 3.48 114 3.25 251 2.47 357 3.2 0.75 deg s s deg deg Vp-p

5V SG5 20k

tW (B) 1/2 tD (B) 1/2

Carrier leak

VL1/2

5V SG5 20k

20

mVp-p

PAL burst level ratio

K (BP1/2) PAL1/2 SG1 to SG4 GND SG5 16k SG3

1.1 145 deg 235

PAL burst phase PAL1/2

Clamp voltage: voltage appearing at Pin 9 when CSYNC is input.

Electrical Characteristics Measurement Circuit

75 F 5V 220 16k 20k NTSC S5 75 NC 17 16 15 14 13 75 18 0.01 47 0.1 220 220 220 10 47k

75 E

75 D

75 C

75 B

75 A

220

220

75 21 20 19

75

75

75

PAL ICC2

24

23

22

VIDEO OUT Y/C MIX 75 DRIVER 75 DRIVER B-OUT

R-OUT

G-OUT

REGULATOR

DELAY CLAMP BPF R-Y Modulator

SYNC ADD

MATRIX

8

B-Y Modulator CLAMP SIN-PULSE PHASE SHIFTER PULSE GEN 4 7 S2 PAL 0.1 SG2 0.1 SG3 S1 NC 5 6 8 NC S3 NTSC 9 0.1 SG4 SIN 0.5Vp-p 5V 2V

CLAMP

CLAMP

10

11 NC S4

12

S1

S1

ICC1 A 0.01 SG5 CSYNC 5V 47

0.1 SG1

2V

CXA1645P/M

SG1 to SG3 100% color bar (1Vp-p max.)

CXA1645P/M

Measuring Signals and Output Waveforms

SG4 0.5Vp-p SCIN SG5 SYNC IN 64s 4.5s f = 3.58MHz 2.0V 0.8V SG5 SYNC IN SG1 RIN SG2 GIN SG3 BIN SG1 to 3 RIN GIN BIN DEF point ROUT GOUT BOUT VO 2.5V 1.0Vp-p BC point YOUT CVOUT Vo (YB) Vo (YW) Vo (YG) Vo (YR) Vo (YS) 1.0Vp-p 64s 4.5s 10s 1.0Vp-p 2.0V 0.8V

Fig. 1

1.0Vp-p

f = 200kHz

Fig. 4

Fig. 2

SG4 0.5Vp-p SCIN f = 3.58MHz

SG1 to 3 RIN GIN BIN DEF BC point ROUT GOUT BOUT YOUT CVOUT 2.5V 1.0Vp-p

SG5 SYNC IN 64s 4.5s 10s VO Vo (5MHz) Vo (200kHz) SG2 GIN SG1 RIN

2.0V 0.8V

f = 200kHz/5MHz

1.0Vp-p

Fig. 3

fc = 20log

1.0Vp-p

SG3 BIN SG4 0.5Vp-p SCIN f = 3.58MHz/ 4.43MHz SG4 SYNC IN C point CVOUT Vo (BN) A point COUT VL K (BP) = Vo (BN) Vo (BN) Vo (BN) 64s 4.5s Vo (BN) VL Vo (BN) tW (B) 2.0V 0.8V A point COUT VO (CB) VO (CG) VO (CR) VO (BN) C point CVOUT tD (B) VO (BN) VO (CG) VO (CB) VO (CR) tW (B)

1.0Vp-p

R/BN = G/BN = B/BN =

VO (CR) VO (BN) VO (CG) VO (BN) VO (CB) VO (BN)

Fig. 5

Fig. 6 9

CXA1645P/M

Application Circuit (NTSC mode)

R OUT 220 75 24 23 G OUT 220 75 22 B OUT 220 75 21 CV OUT 220 0.01 75 20 19 47 20k 18 1% NC 17 75 16 75 15 14 13 C OUT 220 Y OUT 220 10 47k 0.1

VCC +5V

VIDEO OUT R-OUT G-OUT B-OUT

Y/C MIX

75 DRIVER

75 DRIVER REGULATOR

DELAY

CLAMP

SYNC ADD BPF R-Y Modulator

MATRIX

B-Y Modulator PHASE SHIFTER PULSE GEN

CLAMP

CLAMP

CLAMP

SIN-PULSE

5 NC

8 NC

9 0.1

10

11 NC 0.01

12

0.1

0.1

0.1 SCIN SYNC IN Metal film resistor 1%

47

R IN

G IN

B IN

Application Circuit (PAL mode)

R OUT 220 75 24 23 G OUT 220 75 22 B OUT 220 75 21 CV OUT 220 0.01 75 20 19 47 16k 18 1% C OUT 220 75 16 Y OUT 220 75 15 14 13 10 47k 0.1

VCC +5V

NC 17

VIDEO OUT R-OUT G-OUT B-OUT

Y/C MIX

75 DRIVER

75 DRIVER REGULATOR

DELAY

CLAMP

SYNC ADD BPF R-Y Modulator

MATRIX

B-Y Modulator PULSE GEN

CLAMP

CLAMP

CLAMP

SIN-PULSE

PHASE SHIFTER

5 NC

8 NC

9 0.1

10

11 NC

12

0.1

0.1

0.1 SCIN SYNC IN Metal film resistor 1% 0.01 47

R IN

G IN

B IN

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

10

CXA1645P/M

Description of Operation Analog RGB signals input from Pins 2, 3 and 4 are clamped in the clamping circuit and output from Pins 23, 22 and 21, respectively. The matrix circuit performs operations on each input signal, generating luminance signal Y and color difference signals R-Y and B-Y. The Y signal enters the delay line to adjust delay time with the color signal C. Then, after addition of the CSYNC signal input from Pin 10, the Y signal is output from Pin 16. A subcarrier input from Pin 6 is input to the phase shifter, where its phase is sfited 90. Then, the subcarrier is input to the modulators and modulated by the R-Y signal and the B-Y signal. Modulated subcarriers are mixed, sent to the band pass filter to eliminate higher harmonic components and finally output from Pin 15 as the C signal. At the same time, Y and C signals are mixed and output from Pin 20 as the composite video signal.

Burst Signal The CXA1645P/M generates burst signals at the timing shown below according to the composite sync signal input. H synchronization

SYNC IN (TTL level) tD (B) tW (B)

C VIDEO OUT Burst signal

COUT

tD (B)

tW (B)

V synchronization

ODD SYNC IN EVEN

ODD C VIDEO OUT EVEN Burst signal Synchronizing signal

11

CXA1645P/M

Notes on Operation Be careful of the following when using the CXA1645P/M. 1. This IC is designed for image processing of personal computers and video games. When using the IC in other video devices, make thorough investigations on image quality. 2. Be sure that analog RGB signals are input at 1.0Vp-p maximum and have low enough impedance. High impedance may affect color saturation, hue, etc. Inputting RGB signals in excess of 1.3Vp-p may disable the clamp operation. 3. The SC input (Pin 6) can be either a sine wave or a pulse in the range from 0.4 to 5.0Vp-p. However, when a pulse is input, its phase may be shifted several degrees from that of the sine wave input. In the IC, the SC input is biased to 1/2 VCC. Accordingly, when a 5.0Vp-p pulse is input and the duty factor deviates from 50%, High- and Low-level pulse voltages may exceed VCC and GND in the IC, which causes subcarrier distortion. In such a case, be very careful that the duty factor keeps to 50%. 4. When designing a printed circuit board pattern, pay careful attention to the routing of the VCC and GND leads. To decouple the VCC and VREF pins, use tantalum, ceramic or other capacitors with good frequency characteristics. Ground the capacitors by connections shown below as closely to each IC pin as possible. Try to design the leads as short and wide as possible. VCC1, VREF VCC2 ... GND1 ... GND2

Design the pattern so that VCC (or VREF) is connected to GND via a capacitor at the shortest distance. 5. SC and SYNC input pulses Attach a resistor and a capacitor to eliminate high-frequency components of SC (Figure A) and SYNC (Figure B) before input. Fig. A

2.2k 5P

Fig. B

2.2k 47P

Be careful not to input pulses containing high-frequency components. Otherwise, high-frequency components may flow into VCC, GND and peripheral parts, resulting in malfunctions. 6. Connecting an external resistor to the 75 driver output pin A capacitance of several dozen picofarads at each pin may start oscillation. To prevent oscillation, design the pattern so that a 75 resistor is mounted near the pin (see Figure C). Fig. C

75 Make these leads short.

When any of the 75 driver output pins is not in use, leave it unconnected and design the pattern so that no parasitic capacitance is generated on the printed circuit board. 12

CXA1645P/M

7. VREF pin (Pin 14) Do not connect this pin to an external load that might cause AC signals to flow, which will cause IC malfunctions. When connecting a DC load, make sure that the current flowing from this pin is kept below 2mA. 8. YTRAP pin (Pin 17) There are the following two means of reducing cross color generated by subcarrier frequency components contained in the Y signal. (1) Install a capacitor of 30 to 68pF between YTRAP and GND. Decide the capacitance by conducting image evaluation, etc., giving consideration to both cross color and resolution. Relations between capacitance and image quality are as follows: Capacitance Cross color Resolution 30pF 68pF Large Small High Low

17 C

(2)

Connect a capacitor C and an inductor L in series between YTRAP and GND. When the subcarrier 1 frequency is fo, the values C and L are determined by the equation fo = . Decide the values in 2 LC image evaluation, etc., giving consideration to both cross color and resolution. Relations between inductor values and image quality are as follows: Inductor value Cross color Resolution Small Large Large Small High Low

17 C L

For instance, L = 68H and C = 28pF are recommended for NTSC. It is necessary to select an inductor L with a sufficiently small DC resistance. Method (2) is more useful for achieving a higher resoluation than method (1). When an even higher resolution is necessary, use of the S terminal (YOUT and COUT) is recommended. 9. Driving COUT (Pin 15), YOUT (Pin 16), CVOUT (Pin 20), and B.G.R OUT (Pins 21, 22 and 23) outputs In Pin Description, "Capable of driving a 75 load" means that the pin can drive a capacitor +75 +75 load shown in the figure below. In other words, the pin is capable of driving a 150 load in AC.

75 PIN 75 220F

Keep in mind that the pin is incapable of driving a 150 load in DC load in DC direct coupling. 10. This IC employs a number of 75 driver pins, so oscillation is likely to occur when measures described in Nos. 4 and 6 are not taken thoroughly. Be very careful of oscillation in printed circuit board design and carry out thorough investigations in the actual driving condition.

13

CXA1645P/M

Package Outline CXA1645P

Unit: mm

24PIN DIP (PLASTIC) 400mil

+ 0.1 05 0.25 0.

13

+ 0.4 30.2 0.1

24

+ 0.3 8.5 0.1

10.16

0 to 15

1 2.54

12

0.5 0.1 1.2 0.15

3.0 MIN

0.5 MIN

PACKAGE STRUCTURE

PACKAGE MATERIAL SONY CODE EIAJ CODE JEDEC CODE DIP-24P-01 DIP024-P-0400-A LEAD TREATMENT LEAD MATERIAL PACKAGE WEIGHT EPOXY RESIN SOLDER PLATING COPPER / 42 ALLOY 2.0g

CXA1645M

24PIN SOP (PLASTIC)

+ 0.4 15.0 0.1 24 13

+ 0.4 3.7 0.1

+ 0.4 1.85 0.15

0.15

+ 0.3 5.3 0.1

7.9 0.4

+ 0.2 0.1 0.05

0.45 0.1

1.27

+ 0.1 0.2 0.05

0.12 M

PACKAGE STRUCTURE

MOLDING COMPOUND SONY CODE EIAJ CODE JEDEC CODE SOP-24P-L01 SOP024-P-0300-A LEAD TREATMENT LEAD MATERIAL PACKAGE WEIGHT EPOXY/PHENOL RESIN SOLDER PLATING

COPPER ALLOY / 42ALLOY

0.3g

14

0.5 0.2

12

6.9

Das könnte Ihnen auch gefallen

- High Resolution Display Predriver CXA1779PDokument10 SeitenHigh Resolution Display Predriver CXA1779PCristian Camilo Lara MonteroNoch keine Bewertungen

- Skhi 22B DatasheetDokument9 SeitenSkhi 22B DatasheetRakesh RoyNoch keine Bewertungen

- Mc13281fyp PDFDokument16 SeitenMc13281fyp PDFCalin LuchianNoch keine Bewertungen

- TMPA 8823-5VA4 Service Manual: IC Functions and I2C Bus ControlDokument16 SeitenTMPA 8823-5VA4 Service Manual: IC Functions and I2C Bus ControlAndy AnsahNoch keine Bewertungen

- GS1881, GS4881, GS4981Dokument15 SeitenGS1881, GS4881, GS4981Azmi PlgNoch keine Bewertungen

- Ilicore: Video If Processor For B/W TV Cd1366CpDokument5 SeitenIlicore: Video If Processor For B/W TV Cd1366CpmarcelobetoNoch keine Bewertungen

- High-power dual audio amplifier technical data sheetDokument8 SeitenHigh-power dual audio amplifier technical data sheetGirishNoch keine Bewertungen

- Chassis Sanyo Con UOC TMPA8823-5VA4 Manual de ServicioDokument16 SeitenChassis Sanyo Con UOC TMPA8823-5VA4 Manual de ServicioRobert Vicuña100% (1)

- sc7001q Ay 961Dokument18 Seitensc7001q Ay 961r2c1Noch keine Bewertungen

- H-V Sync To Comp SyncDokument9 SeitenH-V Sync To Comp SyncAzmi PlgNoch keine Bewertungen

- Cxa 2150 QDokument90 SeitenCxa 2150 QGraciela TorresNoch keine Bewertungen

- Tda 6103Dokument16 SeitenTda 6103Ondrej LomjanskiNoch keine Bewertungen

- Manual de Servicio Lider 25 29 y 34 TMPA8859Dokument14 SeitenManual de Servicio Lider 25 29 y 34 TMPA8859Joel Roberto MolinaNoch keine Bewertungen

- Sanyo TVS-2542MDokument15 SeitenSanyo TVS-2542MMartin Antonio Bautista CastilloNoch keine Bewertungen

- BLF6G22-180PN 2Dokument11 SeitenBLF6G22-180PN 2mihai315300100% (1)

- Optimize Video Processing with TB1245N ICDokument101 SeitenOptimize Video Processing with TB1245N ICHanif Rathore PrinceNoch keine Bewertungen

- Iraudamp15: 35W/4 X 2 Channel Class D Audio Power Amplifier Using The IR4311Dokument13 SeitenIraudamp15: 35W/4 X 2 Channel Class D Audio Power Amplifier Using The IR4311Megosah SagemegosNoch keine Bewertungen

- TEA5114A: RGB Switching CircuitDokument4 SeitenTEA5114A: RGB Switching Circuitahm_adNoch keine Bewertungen

- TA1310BN: TentativeDokument102 SeitenTA1310BN: TentativeBilly Dela PeñaNoch keine Bewertungen

- TA1270BF: Pal / NTSC Video Chroma and Sync Processing System For Pip / Pop / PapDokument39 SeitenTA1270BF: Pal / NTSC Video Chroma and Sync Processing System For Pip / Pop / PapAzmi PlgNoch keine Bewertungen

- Linear - 16-Bit, Ultra Precise, Fast Settling VOUT DACDokument16 SeitenLinear - 16-Bit, Ultra Precise, Fast Settling VOUT DACAtakan OzturKNoch keine Bewertungen

- DatasheetDokument13 SeitenDatasheetkishore kumarNoch keine Bewertungen

- NTE1570 (NPN Tuner) & NTE1572 (FET Tuner) Integrated Circuit TV Video IF, Sound IFDokument5 SeitenNTE1570 (NPN Tuner) & NTE1572 (FET Tuner) Integrated Circuit TV Video IF, Sound IFAbel RodriguezNoch keine Bewertungen

- mc1377 PDFDokument18 Seitenmc1377 PDFAndres CamachoiNoch keine Bewertungen

- AN8806SB: Three-Beam Method Head Amplifier IC For CD PlayerDokument10 SeitenAN8806SB: Three-Beam Method Head Amplifier IC For CD PlayeraldoNoch keine Bewertungen

- Fan 7316Dokument21 SeitenFan 7316sontuyet82Noch keine Bewertungen

- LCT B85TDU22H Service ManualDokument59 SeitenLCT B85TDU22H Service ManualCristina NistorNoch keine Bewertungen

- CXA1585Q - RGB Decoder PDFDokument20 SeitenCXA1585Q - RGB Decoder PDFVehid ParićNoch keine Bewertungen

- Snva 397 ADokument15 SeitenSnva 397 AAriel NavarreteNoch keine Bewertungen

- Data Sheet: TDA1558QDokument11 SeitenData Sheet: TDA1558QMarco Tulio Da SilvaNoch keine Bewertungen

- TDA 6106qDokument12 SeitenTDA 6106qqwertyuiNoch keine Bewertungen

- Tx-20la5p SMDokument28 SeitenTx-20la5p SMАнатоли АнгеловNoch keine Bewertungen

- STV 9302Dokument15 SeitenSTV 9302krish8717Noch keine Bewertungen

- Adc 10158Dokument26 SeitenAdc 10158Felipe LorenziNoch keine Bewertungen

- Circuit Explanation of LCD Models for Latin AmericaDokument78 SeitenCircuit Explanation of LCD Models for Latin AmericaAntonio ChavezNoch keine Bewertungen

- Datasheet NECDokument20 SeitenDatasheet NECPham Trung KienNoch keine Bewertungen

- SG6105 Datasheet, Pinout, Application Circuits Power Supply Supervisor Regulator PWMDokument13 SeitenSG6105 Datasheet, Pinout, Application Circuits Power Supply Supervisor Regulator PWMBeatrizEstevesNoch keine Bewertungen

- SANYO CE26 32LC D8120TV20 Training Brochure 72Dokument16 SeitenSANYO CE26 32LC D8120TV20 Training Brochure 72romeo1966Noch keine Bewertungen

- Adc0801 PDFDokument36 SeitenAdc0801 PDFroi_sihombingNoch keine Bewertungen

- AD723Dokument20 SeitenAD723Andres CamachoiNoch keine Bewertungen

- bd8160 PDFDokument19 Seitenbd8160 PDFCiudadano ComunNoch keine Bewertungen

- Quad Low Side Driver: DescriptionDokument17 SeitenQuad Low Side Driver: DescriptionDan EsentherNoch keine Bewertungen

- Energy Metering Ic With Pulse Output: DescriptionDokument7 SeitenEnergy Metering Ic With Pulse Output: DescriptionvungocduongNoch keine Bewertungen

- Tea2025b, D ST PDFDokument10 SeitenTea2025b, D ST PDFblueword66Noch keine Bewertungen

- LCD221SD Service ManualDokument41 SeitenLCD221SD Service Manual1cvbnmNoch keine Bewertungen

- TDA8366Dokument48 SeitenTDA8366Rigoberto Martinez LopezNoch keine Bewertungen

- Fet Controller Type 3Ch System Power Supply IcsDokument16 SeitenFet Controller Type 3Ch System Power Supply IcsRohit SinghNoch keine Bewertungen

- 1395Dokument14 Seiten1395Aurel-LucianNedaNoch keine Bewertungen

- BF998Dokument15 SeitenBF998almantino2Noch keine Bewertungen

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsVon EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNoch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- 110 Waveform Generator Projects for the Home ConstructorVon Everand110 Waveform Generator Projects for the Home ConstructorBewertung: 4 von 5 Sternen4/5 (1)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Von EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Bewertung: 4.5 von 5 Sternen4.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Bewertung: 2.5 von 5 Sternen2.5/5 (3)

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsVon EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsNoch keine Bewertungen

- 4 - Kama - Kde 6500 TWDokument2 Seiten4 - Kama - Kde 6500 TWJavadNoch keine Bewertungen

- Motorcycle CatalogDokument24 SeitenMotorcycle CatalogCarsten JakobsenNoch keine Bewertungen

- 1FL6034 2AF21 1LB1 Datasheet enDokument1 Seite1FL6034 2AF21 1LB1 Datasheet enRamesh PeddagoudNoch keine Bewertungen

- Microwave Oven Owner's ManualDokument38 SeitenMicrowave Oven Owner's ManualjoseaurelianoNoch keine Bewertungen

- Energetics QuestionsDokument2 SeitenEnergetics QuestionsBrandeice BarrettNoch keine Bewertungen

- Eurosun2014-Proceedings - ImportentDokument1.524 SeitenEurosun2014-Proceedings - ImportentAkhileshkumar PandeyNoch keine Bewertungen

- LR HAZID Study For LNG Fuel SupplyDokument116 SeitenLR HAZID Study For LNG Fuel SupplyMatteo ConciNoch keine Bewertungen

- Steam Generator HDokument2 SeitenSteam Generator HNoor NoorNoch keine Bewertungen

- Project ProposalDokument4 SeitenProject ProposalRoyNoch keine Bewertungen

- Thyristor 3 Phase InverterDokument31 SeitenThyristor 3 Phase InverterjorgeNoch keine Bewertungen

- Material Spec 1.4571Dokument2 SeitenMaterial Spec 1.4571Vishal GoelNoch keine Bewertungen

- Gorenje K33 - 2Dokument8 SeitenGorenje K33 - 2Nikola TušekNoch keine Bewertungen

- Behaviour of Continuous Pipeline Subject To Transverse PGD: Xuejie Liu S and Michael J. O'RourketDokument15 SeitenBehaviour of Continuous Pipeline Subject To Transverse PGD: Xuejie Liu S and Michael J. O'RourketMarcelo Andrés Rojas GonzálezNoch keine Bewertungen

- Lecture 7 8 Synchronous MotorDokument19 SeitenLecture 7 8 Synchronous MotorCHATHURA MADURANGANoch keine Bewertungen

- Machakos Strategic Plan DraftDokument42 SeitenMachakos Strategic Plan DraftPrince AliNoch keine Bewertungen

- ComputationDokument13 SeitenComputationLester MuscaNoch keine Bewertungen

- Advanced Theoretical Physics A HistoricaDokument523 SeitenAdvanced Theoretical Physics A HistoricaJorge Lopez100% (4)

- India-Iran Relations Progress Problems and ProspecDokument53 SeitenIndia-Iran Relations Progress Problems and Prospecمريم جاسمNoch keine Bewertungen

- Hatz ManualDokument53 SeitenHatz ManualCubi Masinska ObradaNoch keine Bewertungen

- DeforestationDokument4 SeitenDeforestationPeggopoulouNoch keine Bewertungen

- Varsani JayDokument33 SeitenVarsani JayBHAVESH KERAI100% (1)

- Chapter Fluid MachineryDokument50 SeitenChapter Fluid MachineryWan AimanNoch keine Bewertungen

- SANY RSC45 Container Reach Stacker Maintenance Manual PDFDokument29 SeitenSANY RSC45 Container Reach Stacker Maintenance Manual PDFejaz100% (6)

- Gel Content & Peel Test: Benjamin Lippke, Romain PénidonDokument14 SeitenGel Content & Peel Test: Benjamin Lippke, Romain PénidonKarthikeyanKarthikNoch keine Bewertungen

- Control Major Accidents CausesDokument22 SeitenControl Major Accidents CausesJahid HasanNoch keine Bewertungen

- Northside-Southside TOD StudyDokument265 SeitenNorthside-Southside TOD StudynextSTL.comNoch keine Bewertungen

- Caie As Level Geography 9696 Core Model Answers v1Dokument31 SeitenCaie As Level Geography 9696 Core Model Answers v1kgethilwemakgotsoNoch keine Bewertungen

- Optimal Design of Cooling Water Systems: August 2011Dokument23 SeitenOptimal Design of Cooling Water Systems: August 2011Hansraj RahulNoch keine Bewertungen

- Garnituri DIN 2697Dokument12 SeitenGarnituri DIN 2697Dumitru SorinaNoch keine Bewertungen

- Secondary Infobook ActivitiesDokument36 SeitenSecondary Infobook Activitiesapi-231516879100% (1)