Beruflich Dokumente

Kultur Dokumente

Cse477 19 Timing

Hochgeladen von

Mahmoud Abd El LatifOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Cse477 19 Timing

Hochgeladen von

Mahmoud Abd El LatifCopyright:

Verfügbare Formate

CSE477 VLSI Digital Circuits Fall 2002 Lecture 19: Timing Issues; Introduction to Datapath Design

Mary Jane Irwin ( www.cse.psu.edu/~mji ) www.cse.psu.edu/~cg477

[Adapted from Rabaeys Digital Integrated Circuits, 2002, J. Rabaey et al.]

CSE477 L19 Timing Issues; Datapaths.1 Irwin&Vijay, PSU, 2002

Review: Sequential Definitions

Use two level sensitive latches of opposite type to build one master-slave flipflop that changes state on a clock edge (when the slave is transparent) Static storage

q

static uses a bistable element with feedback to store its state and thus preserves state as long as the power is on

- Loading new data into the element: 1) cutting the feedback path (mux based); 2) overpowering the feedback path (SRAM based)

Dynamic storage

q q

dynamic stores state on parasitic capacitors so the state held for only a period of time (milliseconds); requires periodic refresh dynamic is usually simpler (fewer transistors), higher speed, lower power but due to noise immunity issues always modify the circuit so that it is pseudostatic

CSE477 L19 Timing Issues; Datapaths.2

Irwin&Vijay, PSU, 2002

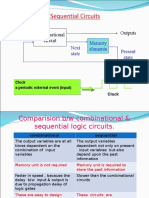

Timing Classifications

Synchronous systems

q

All memory elements in the system are simultaneously updated using a globally distributed periodic synchronization signal (i.e., a global clock signal) Functionality is ensure by strict constraints on the clock signal generation and distribution to minimize

- Clock skew (spatial variations in clock edges) - Clock jitter (temporal variations in clock edges)

Asynchronous systems

q q

Self-timed (controlled) systems No need for a globally distributed clock, but have asynchronous circuit overheads (handshaking logic, etc.)

Hybrid systems

q q

Synchronization between different clock domains Interfacing between asynchronous and synchronous domains

Irwin&Vijay, PSU, 2002

CSE477 L19 Timing Issues; Datapaths.3

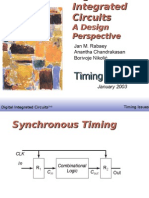

Review: Synchronous Timing Basics

R1 In D Q tclk1 tc-q , tsu , thold , tcdreg Combinational logic R2 D Q tclk2 tplogic , tcdlogic

clk

Under ideal conditions (i.e., when tclk1 = tclk2 )

T tc-q + tplogic + tsu thold tcdlogic + tcdreg

Under real conditions, the clock signal can have both spatial (clock skew) and temporal (clock jitter) variations

q

skew is constant from cycle to cycle (by definition); skew can be positive (clock and data flowing in the same direction) or negative (clock and data flowing in opposite directions) jitter causes T to change on a cycle-by-cycle basis

Irwin&Vijay, PSU, 2002

CSE477 L19 Timing Issues; Datapaths.4

Sources of Clock Skew and Jitter in Clock Network

4 power supply 3 interconnect

clock 1 generation

6 capacitive load 7 capacitive

PLL

2 clock drivers

coupling

5 temperature

Skew

q q q

Jitter

q q q

manufacturing device variations in clock drivers interconnect variations environmental variations (power supply and temperature)

clock generation capacitive loading and coupling environmental variations (power supply and temperature)

Irwin&Vijay, PSU, 2002

CSE477 L19 Timing Issues; Datapaths.5

Positive Clock Skew

Clock and data flow in the same direction

R1 In clk D Q tclk1

T

1

R2 Combinational logic delay

3

D Q tclk2

>0

2

T+

+ thold

T: thold :

CSE477 L19 Timing Issues; Datapaths.6

Irwin&Vijay, PSU, 2002

Positive Clock Skew

Clock and data flow in the same direction

R1 In clk D Q tclk1

T

1

R2 Combinational logic delay

3

D Q tclk2

>0

2

T+

+ thold

T: thold :

T + tc-q + tplog ic + tsu so T tc-q + tplog ic + tsu - thold + tcdlog ic + tcdreg so thold tcdlog ic + tcdreg -

> 0: Improves performance, but makes thold harder to meet. If

thold is not met (race conditions), the circuit malfunctions independent of the clock period!

CSE477 L19 Timing Issues; Datapaths.7

Irwin&Vijay, PSU, 2002

Negative Clock Skew

Clock and data flow in opposite directions

R1 In D Q tclk1 delay

T

1 2

R2 Combinational logic D Q tclk2 clk

T+

4

<0

T: thold :

CSE477 L19 Timing Issues; Datapaths.8

Irwin&Vijay, PSU, 2002

Negative Clock Skew

Clock and data flow in opposite directions

R1 In D Q tclk1 delay

T

1 2

R2 Combinational logic D Q tclk2 clk

T+

4

<0

T: thold :

T + tc-q + tplog ic + tsu so T tc-q + tplog ic + tsu - thold + tcdlog ic + tcdreg so thold tcdlog ic + tcdreg -

< 0: Degrades performance, but thold is easier to meet

(eliminating race conditions)

CSE477 L19 Timing Issues; Datapaths.9

Irwin&Vijay, PSU, 2002

Clock Jitter

Jitter causes T to vary on a cycle-bycycle basis

R1 In clk tclk

T

Combinational logic

-tjitter

+tjitter

T:

CSE477 L19 Timing Issues; Datapaths.10

Irwin&Vijay, PSU, 2002

Clock Jitter

Jitter causes T to vary on a cycle-bycycle basis

R1 In clk tclk

T

Combinational logic

-tjitter

+tjitter

T:

T - 2tjitter tc-q + tplog ic + tsu so T tc-q + tplog ic + tsu + 2tjitter

Jitter directly reduces the performance of a sequential circuit

CSE477 L19 Timing Issues; Datapaths.11

Irwin&Vijay, PSU, 2002

Combined Impact of Skew and Jitter

Constraints on the minimum clock period ( > 0)

R1 In D Q tclk1

1

R2 Combinational logic

T T+ >0

6 12

D Q tclk2

-tjitter

T tc-q + tplog ic + tsu - + 2tjitter

thold tcdlog ic + tcdreg 2tjitter

> 0 with jitter: Degrades performance, and makes thold

even harder to meet. (The acceptable skew is reduced by jitter.)

CSE477 L19 Timing Issues; Datapaths.12 Irwin&Vijay, PSU, 2002

Clock Distribution Networks

Clock skew and jitter can ultimately limit the performance of a digital system, so designing a clock network that minimizes both is important

q q

In many high-speed processors, a majority of the dynamic power is dissipated in the clock network. To reduce dynamic power, the clock network must support clock gating (shutting down (disabling the clock) units)

Clock distribution techniques

q

Balanced paths (H-tree network, matched RC trees)

- In the ideal case, can eliminate skew - Could take multiple cycles for the clock signal to propagate to the leaves of the tree

Clock grids

- Typically used in the final stage of the clock distribution network - Minimizes absolute delay (not relative delay)

CSE477 L19 Timing Issues; Datapaths.13

Irwin&Vijay, PSU, 2002

H-Tree Clock Network

If the paths are perfectly balanced, clock skew is zero

Clock

Can insert clock gating at multiple levels in clock tree Can shut off entire subtree if all gating conditions are satisfied Idle condition Clock Gated clock

CSE477 L19 Timing Issues; Datapaths.14

Irwin&Vijay, PSU, 2002

DEC Alpha 21164 (EV5)

300 MHz clock (9.3 million transistors on a 16.5x18.1 mm die in 0.5 micron CMOS technology)

q

single phase clock

3.75 nF total clock load

q

Extensive use of dynamic logic

20 W (out of 50) in clock distribution network Two level clock distribution

q q

Single 6 stage driver at the center of the chip Secondary buffers drive the left and right sides of the clock grid in m3 and m4

Total equivalent driver size of 58 cm !!

CSE477 L19 Timing Issues; Datapaths.15

Irwin&Vijay, PSU, 2002

Clock Drivers

CSE477 L19 Timing Issues; Datapaths.16

Irwin&Vijay, PSU, 2002

Clock Skew in Alpha Processor

Absolute skew smaller than 90 ps

The critical instruction and execution units all see the clock within 65 ps

Irwin&Vijay, PSU, 2002

CSE477 L19 Timing Issues; Datapaths.17

Dealing with Clock Skew and Jitter

To minimize skew, balance clock paths using H-tree or matched-tree clock distribution structures. If possible, route data and clock in opposite directions; eliminates races at the cost of performance. The use of gated clocks to help with dynamic power consumption make jitter worse. Shield clock wires (route power lines VDD or GND next to clock lines) to minimize/eliminate coupling with neighboring signal nets. Use dummy fills to reduce skew by reducing variations in interconnect capacitances due to interlayer dielectric thickness variations. Beware of temperature and supply rail variations and their effects on skew and jitter. Power supply noise fundamentally limits the performance of clock networks.

Irwin&Vijay, PSU, 2002

CSE477 L19 Timing Issues; Datapaths.18

Major Components of a Computer

Processor Control Datapath

Devices Memory Input Output

Modern processor architecture styles (CSE 431)

q q q q

Pipelined, single issue (e.g., ARM) Pipelined, hardware controlled multiple issue superscalar Pipelined, software controlled multiple issue VLIW Pipelined, multiple issue from multiple process threads multithreaded

Irwin&Vijay, PSU, 2002

CSE477 L19 Timing Issues; Datapaths.19

Basic Building Blocks

Datapath

q

Execution units

- Adder, multiplier, divider, shifter, etc.

q q

Register file and pipeline registers Multiplexers, decoders

Control

q

Finite state machines (PLA, ROM, random logic)

Interconnect

q

Switches, arbiters, buses

Memory

q

Caches, TLBs, DRAM, buffers

CSE477 L19 Timing Issues; Datapaths.20

Irwin&Vijay, PSU, 2002

MIPS 5-Stage Pipelined (Single Issue) Datapath

Fetch

1 0

Add 4 Shift left 2

Decode

Execute

Memory

WriteBack

Add

pipeline stage isolation register

I$

Read Address

Read Addr 1

Exec/Mem

Mem/WB

Write Addr Write Data

File

Dec/Exec

IF/Dec

Data 1 Read Addr 2

Register Read

ALU

Address

D$

Read Data

PC

Read Data 2

1 0

0 1

Write Data

Icache precharge

16

Sign Extend

32

Dcache precharge

RegWrite

clk

Irwin&Vijay, PSU, 2002

CSE477 L19 Timing Issues; Datapaths.21

Datapath Bit-Sliced Organization

Control Flow

Pipeline Register

Pipeline Register Multiplexer

Pipeline Register

Pipeline Register Multiplexer

Register File

Bit 3 Bit 2 Bit 1 Bit 0

From I$

Data Flow

Shifter

Adder

To/From D$

Tile identical bit-slice elements

CSE477 L19 Timing Issues; Datapaths.22 Irwin&Vijay, PSU, 2002

Next Lecture and Reminders

Next lecture

q

Adder design

- Reading assignment Rabaey, et al, 11.3

Reminders

q q q q q q

Pick up second half of the new edition of the book from Sue in 202 Pond Lab Project final reports due December 5th HW4 due today HW5 due November 19th Final grading negotiations/correction (except for the final exam) must be concluded by December 10th Final exam scheduled

- Monday, December 16th from 10:10 to noon in 118 and 121 Thomas

CSE477 L19 Timing Issues; Datapaths.23

Irwin&Vijay, PSU, 2002

Das könnte Ihnen auch gefallen

- Cse477-17 StaticseqDokument33 SeitenCse477-17 StaticseqHitesh GahlawatNoch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- Clock BuffersDokument29 SeitenClock Buffersnaveen silveri100% (2)

- Electronic Systems: Study Topics in Physics Book 8Von EverandElectronic Systems: Study Topics in Physics Book 8Bewertung: 5 von 5 Sternen5/5 (1)

- ChapterDokument80 SeitenChapterAshish VermaNoch keine Bewertungen

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsVon EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsBewertung: 1 von 5 Sternen1/5 (1)

- Flip FlopsDokument25 SeitenFlip FlopsNagul MeeraNoch keine Bewertungen

- Clocking Part 2Dokument4 SeitenClocking Part 2Dmitry LeyzerovichNoch keine Bewertungen

- Advanced Electric Drives: Analysis, Control, and Modeling Using MATLAB / SimulinkVon EverandAdvanced Electric Drives: Analysis, Control, and Modeling Using MATLAB / SimulinkNoch keine Bewertungen

- Clocking and Latches: Notes For EEC180B Spring 1999 University of California DavisDokument18 SeitenClocking and Latches: Notes For EEC180B Spring 1999 University of California Davisrvs_093Noch keine Bewertungen

- Timing Issues in Digital ASIC DesignDokument101 SeitenTiming Issues in Digital ASIC Designnsai_vs1513Noch keine Bewertungen

- Digital Mobile Communications and the TETRA SystemVon EverandDigital Mobile Communications and the TETRA SystemBewertung: 5 von 5 Sternen5/5 (1)

- Setup1 1210Dokument32 SeitenSetup1 1210Akhila PurushothamanNoch keine Bewertungen

- Microprocessor System Design: A Practical IntroductionVon EverandMicroprocessor System Design: A Practical IntroductionNoch keine Bewertungen

- CSE477 VLSI Digital Circuits Fall 2002 Lecture 26: Low Power Techniques in Microarchitectures and MemoriesDokument22 SeitenCSE477 VLSI Digital Circuits Fall 2002 Lecture 26: Low Power Techniques in Microarchitectures and MemoriessusantNoch keine Bewertungen

- Beginning Digital Electronics through ProjectsVon EverandBeginning Digital Electronics through ProjectsBewertung: 5 von 5 Sternen5/5 (1)

- Clock and Data Recovery For Serial Digital CommunicationDokument60 SeitenClock and Data Recovery For Serial Digital CommunicationJeffrey LiuNoch keine Bewertungen

- Power Electronics Applied to Industrial Systems and Transports, Volume 2: Power Converters and their ControlVon EverandPower Electronics Applied to Industrial Systems and Transports, Volume 2: Power Converters and their ControlBewertung: 5 von 5 Sternen5/5 (1)

- Experiment No. 3.1Dokument5 SeitenExperiment No. 3.1Harshal AmbatkarNoch keine Bewertungen

- 110 Waveform Generator Projects for the Home ConstructorVon Everand110 Waveform Generator Projects for the Home ConstructorBewertung: 4 von 5 Sternen4/5 (1)

- Timing Analysis: Elec 326 Sequential Circuit TimingDokument43 SeitenTiming Analysis: Elec 326 Sequential Circuit TimingArpit KapoorNoch keine Bewertungen

- Simulation of PMSM Vector Control System Based On Non-Linear PID and Its Easy DSP RealizationDokument5 SeitenSimulation of PMSM Vector Control System Based On Non-Linear PID and Its Easy DSP RealizationHarshali WavreNoch keine Bewertungen

- Chapter 7Dokument60 SeitenChapter 7Sunil KumarNoch keine Bewertungen

- Negative and Positive Clock SkewDokument27 SeitenNegative and Positive Clock SkewSupriya AggarwalNoch keine Bewertungen

- Chapter 17: Low-Power Design: Keshab K. Parhi and Viktor OwallDokument34 SeitenChapter 17: Low-Power Design: Keshab K. Parhi and Viktor OwallGowtham Gntupallii GNoch keine Bewertungen

- Chapter 6 Speed Independent Control CircuitsDokument90 SeitenChapter 6 Speed Independent Control CircuitsemailparacadastroNoch keine Bewertungen

- Sequential LogicDokument68 SeitenSequential LogicbabahussainNoch keine Bewertungen

- Lacture 6Dokument44 SeitenLacture 6Ali KhanNoch keine Bewertungen

- Digital Integrated CircuitsDokument60 SeitenDigital Integrated CircuitsSara SaleemNoch keine Bewertungen

- Topic 6 - Clocking & Met A StabilityDokument9 SeitenTopic 6 - Clocking & Met A Stabilityanish1988100% (1)

- Notes 326 Set12 PDFDokument17 SeitenNotes 326 Set12 PDFEswaran SamyNoch keine Bewertungen

- DS1302 Trickle-Charge Timekeeping ChipDokument13 SeitenDS1302 Trickle-Charge Timekeeping ChipPravin MevadaNoch keine Bewertungen

- DS1320Dokument13 SeitenDS1320Annelise Grottker de OliveiraNoch keine Bewertungen

- Introduction To Digital Systems 8 - Sequential NetworksDokument65 SeitenIntroduction To Digital Systems 8 - Sequential NetworksJesna KaNoch keine Bewertungen

- EE 459/500 - HDL Based Digital Design With Programmable Logic Timing and Clock IssuesDokument23 SeitenEE 459/500 - HDL Based Digital Design With Programmable Logic Timing and Clock Issuessneha96669Noch keine Bewertungen

- Understanding Sequential Circuit TimingDokument8 SeitenUnderstanding Sequential Circuit Timingchuku7Noch keine Bewertungen

- Gditechnology 151220144934Dokument80 SeitenGditechnology 151220144934bharath kishore reddyNoch keine Bewertungen

- Real-Time DC Motor Position Control by Fuzzy Logic and PID Controllers Using LabviewDokument6 SeitenReal-Time DC Motor Position Control by Fuzzy Logic and PID Controllers Using Labviewvikalp guptaNoch keine Bewertungen

- FlipflopsDokument80 SeitenFlipflopsvikramkolanuNoch keine Bewertungen

- An, Improved Successive-Approximation Register Design For Use in A/D ConvertersDokument5 SeitenAn, Improved Successive-Approximation Register Design For Use in A/D ConvertersOmer KhanNoch keine Bewertungen

- M. Garcia, A. Barreiro STABILITY OF A NETWORKED CONTROL SYSTEM USINGDokument6 SeitenM. Garcia, A. Barreiro STABILITY OF A NETWORKED CONTROL SYSTEM USINGFelix GamarraNoch keine Bewertungen

- SN1-2223-Lab3 1-2 EngDokument4 SeitenSN1-2223-Lab3 1-2 EngBoualem MestafaNoch keine Bewertungen

- Clock and Data Recovery For Serial Digital CommunicationDokument79 SeitenClock and Data Recovery For Serial Digital Communicationquail36Noch keine Bewertungen

- Chapter - 7 (Compatibility Mode)Dokument32 SeitenChapter - 7 (Compatibility Mode)Imran HayderNoch keine Bewertungen

- InverterDokument231 SeitenInverterMaitrik Shah100% (1)

- Repetitive ControlDokument22 SeitenRepetitive ControlShri KulkarniNoch keine Bewertungen

- MCGG OcrDokument14 SeitenMCGG OcrAgus BuchariNoch keine Bewertungen

- Motor Drive 5Dokument14 SeitenMotor Drive 5setsindiaNoch keine Bewertungen

- Chip Level Timing: ECE124 Digital Circuits and SystemsDokument18 SeitenChip Level Timing: ECE124 Digital Circuits and SystemspdnoobNoch keine Bewertungen

- Clock Domain Crossing: Issues and Solutions: Udit Kumar, DCG Sakshi Gupta, TRND Bhanu Prakash, DCGDokument53 SeitenClock Domain Crossing: Issues and Solutions: Udit Kumar, DCG Sakshi Gupta, TRND Bhanu Prakash, DCGSiddharth Sabharwal60% (5)

- EE141 - Fall 2003 Digital Integrated CircuitsDokument26 SeitenEE141 - Fall 2003 Digital Integrated CircuitscanilreddyNoch keine Bewertungen

- Abt ManualDokument39 SeitenAbt ManualAbhinav Tewari100% (1)

- Lect17 SeqDokument18 SeitenLect17 SeqorengeneralNoch keine Bewertungen

- Racid 1mdu07006-EnDokument36 SeitenRacid 1mdu07006-Enhey_frindNoch keine Bewertungen

- Telefunken+TF LED50S10T2+K PL L01Dokument4 SeitenTelefunken+TF LED50S10T2+K PL L01Andres AlegriaNoch keine Bewertungen

- DVD2 JNTU Set1 SolutionsDokument12 SeitenDVD2 JNTU Set1 Solutionsకిరణ్ కుమార్ పగడాలNoch keine Bewertungen

- Design and Analysis of Fs-Tspc-Det Flip-Flop For Iot ApplicationsDokument9 SeitenDesign and Analysis of Fs-Tspc-Det Flip-Flop For Iot ApplicationsVikas BalikaiNoch keine Bewertungen

- Shoshana Bulka PragmaticaDokument17 SeitenShoshana Bulka PragmaticaJessica JonesNoch keine Bewertungen

- Collins Ks3 Science Homework Book 3Dokument5 SeitenCollins Ks3 Science Homework Book 3g3pz0n5h100% (1)

- Pizza Restaurant PowerPoint TemplatesDokument49 SeitenPizza Restaurant PowerPoint TemplatesAindrila BeraNoch keine Bewertungen

- Operator's ManualDokument110 SeitenOperator's ManualAdam0% (1)

- Writing About Graphs, Tables and DiagramsDokument68 SeitenWriting About Graphs, Tables and DiagramsLangers BastasaNoch keine Bewertungen

- High Speed Power TransferDokument33 SeitenHigh Speed Power TransferJAYKUMAR SINGHNoch keine Bewertungen

- Maskote WB Zinc Stop-OffDokument7 SeitenMaskote WB Zinc Stop-OffbondsivamaniNoch keine Bewertungen

- GST RATE LIST - pdf-3Dokument6 SeitenGST RATE LIST - pdf-3Niteesh KumarNoch keine Bewertungen

- 3E Hand Over NotesDokument3 Seiten3E Hand Over NotesAshutosh MaiidNoch keine Bewertungen

- Nationalism, Feminism, and Modernity in PalestineDokument26 SeitenNationalism, Feminism, and Modernity in PalestinebobandjoerockNoch keine Bewertungen

- Performance Task 2Dokument3 SeitenPerformance Task 2Edrose WycocoNoch keine Bewertungen

- Embedded Software Development ProcessDokument34 SeitenEmbedded Software Development ProcessAmmar YounasNoch keine Bewertungen

- LAB REPORT - MGCLDokument5 SeitenLAB REPORT - MGCLKali stringsNoch keine Bewertungen

- Project Report For Tunnel ExcavationDokument19 SeitenProject Report For Tunnel ExcavationAbhishek Sarkar50% (2)

- What Is The Difference Between Newtonian and Non-Newtonian Fluid and Give Example For Each Case?Dokument11 SeitenWhat Is The Difference Between Newtonian and Non-Newtonian Fluid and Give Example For Each Case?MOHAMED ABD ELGHANYNoch keine Bewertungen

- The Limits of The Sectarian Narrative in YemenDokument19 SeitenThe Limits of The Sectarian Narrative in Yemenهادي قبيسيNoch keine Bewertungen

- Class InsectaDokument4 SeitenClass InsectaLittle Miss CeeNoch keine Bewertungen

- Kaun Banega Crorepati Computer C++ ProjectDokument20 SeitenKaun Banega Crorepati Computer C++ ProjectDhanya SudheerNoch keine Bewertungen

- Department of Education: Republic of The PhilippinesDokument2 SeitenDepartment of Education: Republic of The PhilippinesISMAEL KRIS DELA CRUZNoch keine Bewertungen

- Shelly Cashman Series Microsoft Office 365 Excel 2016 Comprehensive 1st Edition Freund Solutions ManualDokument5 SeitenShelly Cashman Series Microsoft Office 365 Excel 2016 Comprehensive 1st Edition Freund Solutions Manualjuanlucerofdqegwntai100% (10)

- Volcanoes Sub-topic:Volcanic EruptionDokument16 SeitenVolcanoes Sub-topic:Volcanic EruptionVhenz MapiliNoch keine Bewertungen

- Dummy 13 Printable Jointed Figure Beta FilesDokument9 SeitenDummy 13 Printable Jointed Figure Beta FilesArturo GuzmanNoch keine Bewertungen

- MSDS Leadframe (16 Items)Dokument8 SeitenMSDS Leadframe (16 Items)bennisg8Noch keine Bewertungen

- NCERT Solutions For Class 10 Maths Chapter 5 Arithmetic Progression (Ex 5.1) Exercise 5.1Dokument8 SeitenNCERT Solutions For Class 10 Maths Chapter 5 Arithmetic Progression (Ex 5.1) Exercise 5.1Akash DasNoch keine Bewertungen

- Review Course 2 (Review On Professional Education Courses)Dokument8 SeitenReview Course 2 (Review On Professional Education Courses)Regie MarcosNoch keine Bewertungen

- Unit 3: Theories and Principles in The Use and Design of Technology Driven Learning LessonsDokument5 SeitenUnit 3: Theories and Principles in The Use and Design of Technology Driven Learning Lessons서재배Noch keine Bewertungen

- 1.classification of Reciprocating PumpsDokument8 Seiten1.classification of Reciprocating Pumpsgonri lynnNoch keine Bewertungen

- 3DS 2017 GEO GEMS Brochure A4 WEBDokument4 Seiten3DS 2017 GEO GEMS Brochure A4 WEBlazarpaladinNoch keine Bewertungen

- Catalogue - Central Battery SystemDokument12 SeitenCatalogue - Central Battery SystemarifzakirNoch keine Bewertungen

- CBC DrivingDokument74 SeitenCBC DrivingElonah Jean ConstantinoNoch keine Bewertungen